DDR SDRAM

DDR SDRAM stacked 512Mb E-die (x4/x8)

Rev. 1.0 July. 2003

Stacked 512Mb E-die DDR SDRAM Specification

Revision 1.0

(x4/x8)

DDR SDRAM

DDR SDRAM stacked 512Mb E-die (x4/x8)

Rev. 1.0 July. 2003

st. 512Mb E-die Revision History

Revision 1.0 (July, 2003)

- First version release.

DDR SDRAM

DDR SDRAM stacked 512Mb E-die (x4/x8)

Rev. 1.0 July. 2003

∑ Double-data-rate architecture; two data transfers per clock cycle

∑ Bidirectional data strobe DQS

∑ Four banks operation

∑ Differential clock inputs(CK and CK)

∑ DLL aligns DQ and DQS transition with CK transition

∑ MRS cycle with address key programs

-. Read latency 2, 2.5 (clock)

-. Burst length (2, 4, 8)

-. Burst type (sequential & interleave)

∑ All inputs except data & DM are sampled at the positive going edge of the system clock(CK)

∑ Data I/O transactions on both edges of data strobe

∑ Edge aligned data output, center aligned data input

∑ DM for write masking only (x4, x8)

∑ Auto & Self refresh

∑ 7.8us refresh interval(8K/64ms refresh)

∑ Maximum burst refresh cycle : 8

∑ 66pin TSOP II package

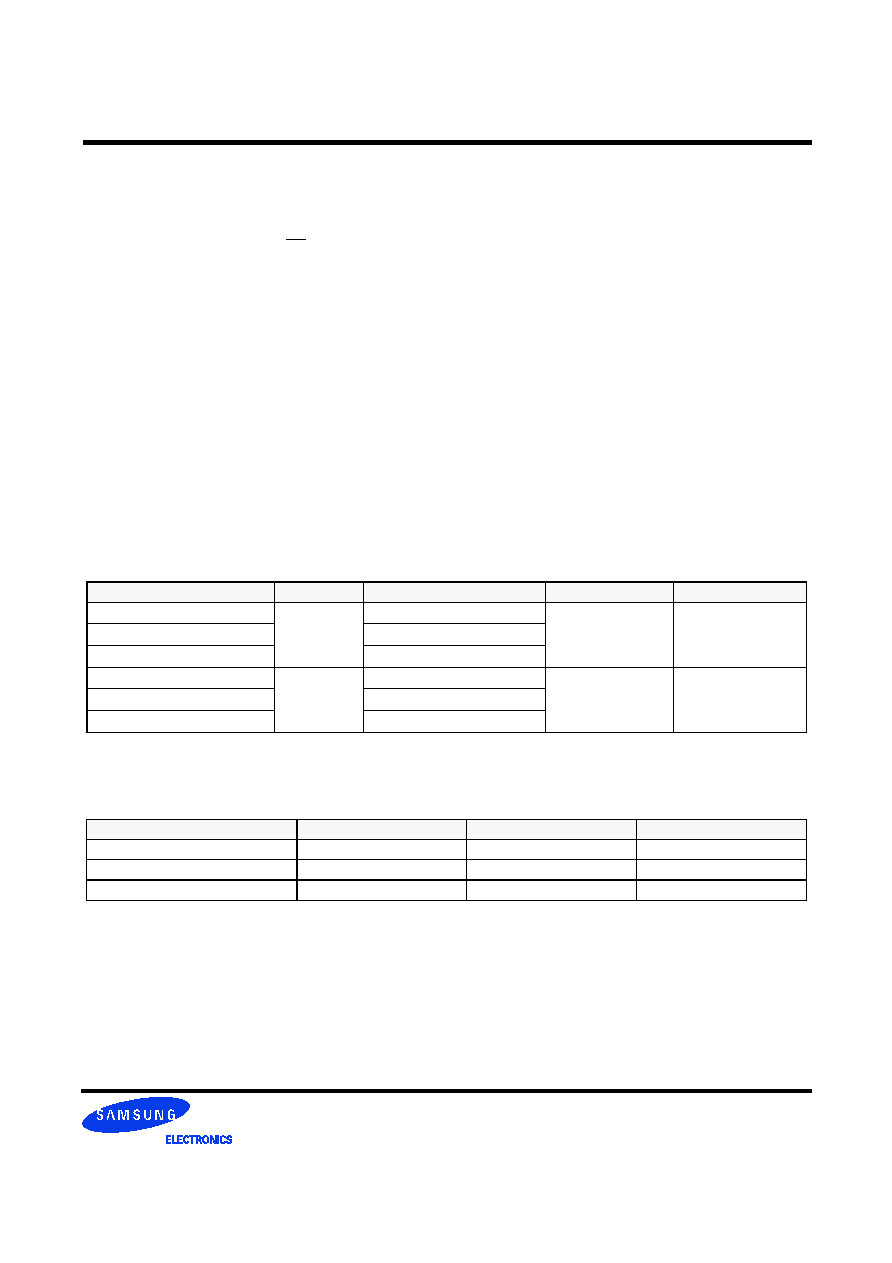

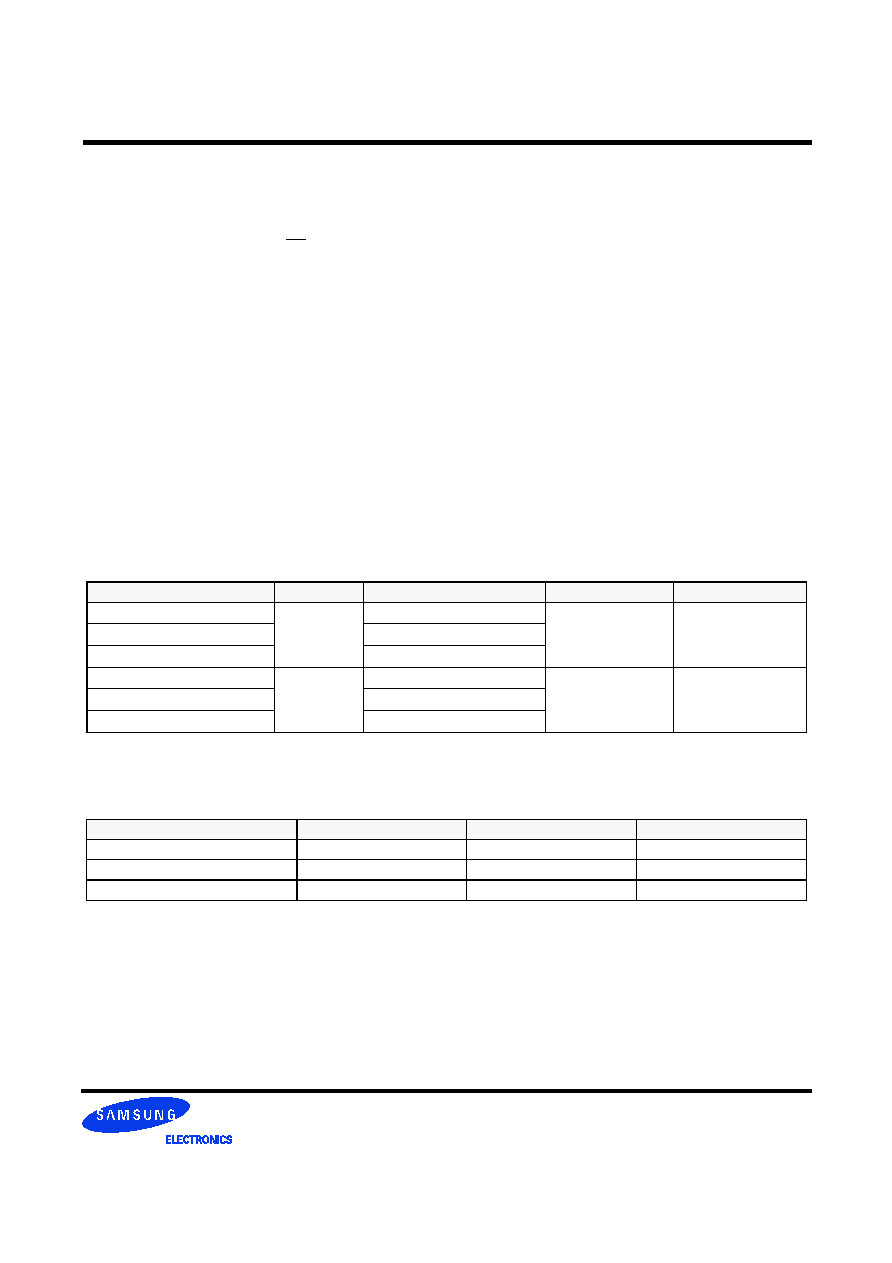

Ordering Information

Part No.

Org.

Max Freq.

Interface

Package

K4H510638E-TC/LAA

st.128M x 4

AA(DDR266@CL=2)

SSTL2

66pin TSOP II

K4H510638E-TC/LA2

A2(DDR266@CL=2)

K4H510638E-TC/LB0

B0(DDR266@CL=2.5)

K4H510738E-TC/LAA

st.64M x 8

AA(DDR266@CL=2)

SSTL2

66pin TSOP II

K4H510738E-TC/LA2

A2(DDR266@CL=2)

K4H510738E-TC/LB0

B0(DDR266@CL=2.5)

Key Features

*CL : CAS Latency

Operating Frequencies

AA(DDR266@CL=2.0)

A2(DDR266@CL=2.0)

B0(DDR266@CL=2.5)

Speed @CL2

133MHz

133MHz

100MHz

Speed @CL2.5

133MHz

133MHz

133MHz

CL-tRCD-tRP

2-2-2

2-3-3

2.5-3-3

DDR SDRAM

DDR SDRAM stacked 512Mb E-die (x4/x8)

Rev. 1.0 July. 2003

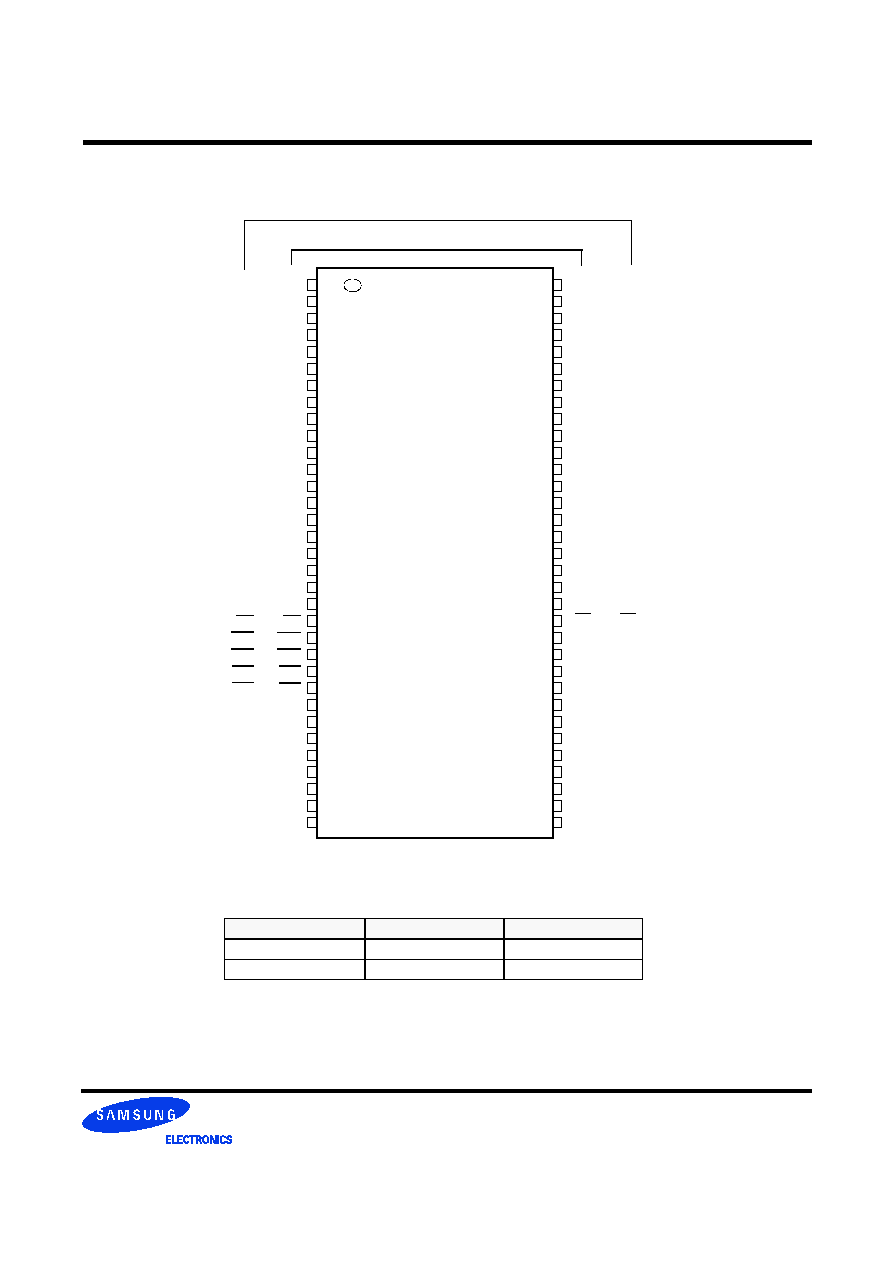

Pin Description

DM is internally loaded to match DQ and DQS identically.

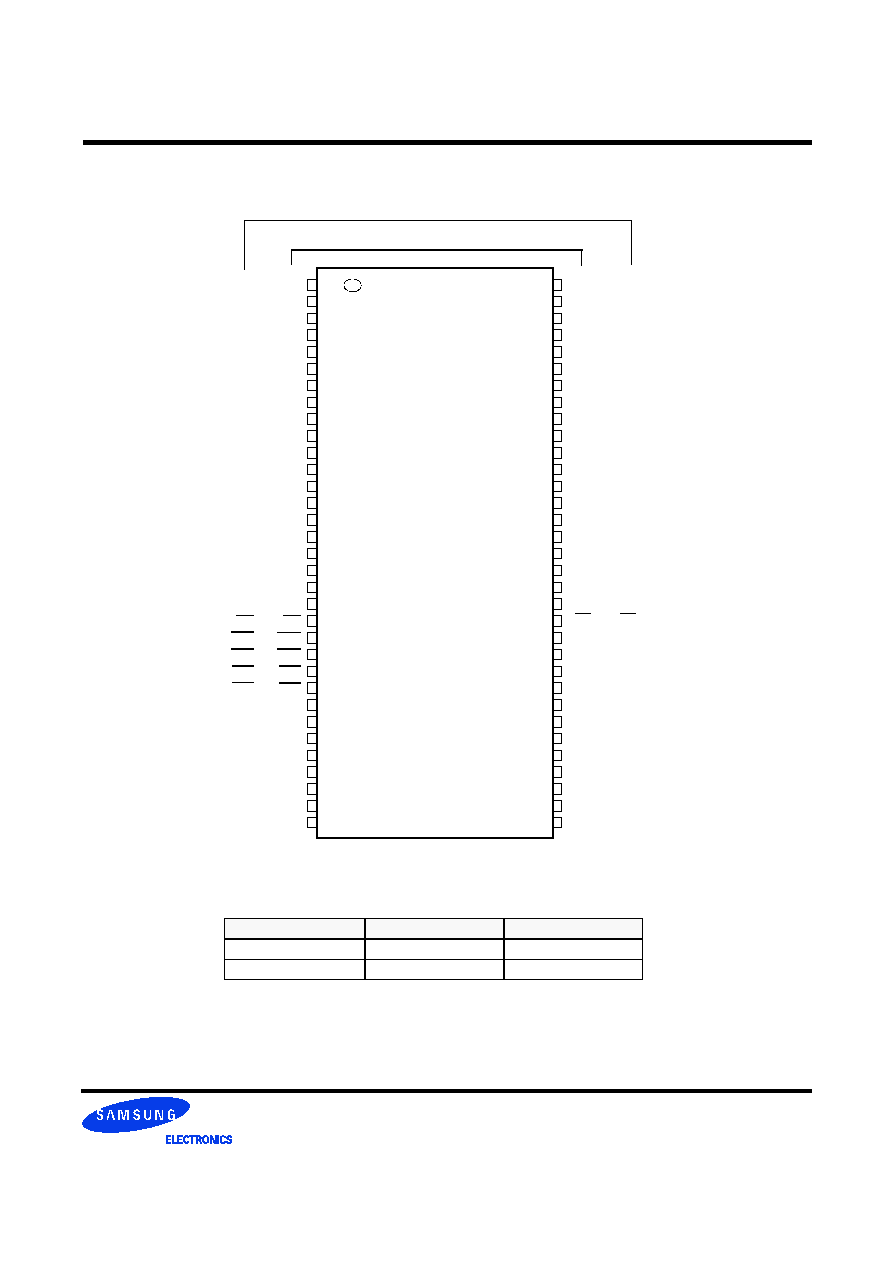

stacked 512Mb TSOP-II Package Pinout

Row & Column address configuration

V

DD

1

66Pin TSOPII

(400mil x 875mil)

DQ

0

2

V

DDQ

3

NC

4

DQ

1

5

V

SSQ

6

NC

7

DQ

2

8

V

DDQ

9

NC

10

DQ

3

11

V

SSQ

12

BA

0

20

CS0

19

RAS

18

CAS

17

WE

16

NC

15

V

DDQ

14

NC

13

V

DD

27

A

3

26

A

2

25

A

1

24

A

0

23

AP/A

10

22

BA

1

21

V

SS

54

DQ

7

53

V

SSQ

52

NC

51

DQ

6

50

V

DDQ

49

NC

48

DQ

5

47

V

SSQ

46

NC

45

DQ

4

44

V

DDQ

43

A

11

35

36

CKE0

37

CK

38

DM

39

V

REF

40

V

SSQ

41

NC

42

V

SS

55

A

4

56

A

5

57

A

6

58

A

7

59

A

8

60

A

9

34

(0.65mm Pin Pitch)

33

32

31

30

29

28

61

62

63

64

65

66

NC

NC

NC

NC

CS1

V

DD

NC

DQS

NC

V

SS

CK

CKE1

A

12

V

SS

NC

V

SSQ

NC

DQ

3

V

DDQ

NC

NC

V

SSQ

NC

DQ

2

V

DDQ

A

11

CKE0

CK

DM

V

REF

V

SSQ

NC

V

SS

A

4

A

5

A

6

A

7

A

8

A

9

NC

DQS

NC

V

SS

CK

CKE1

A

12

V

DD

NC

V

DDQ

NC

DQ

0

V

SSQ

NC

NC

V

DDQ

NC

DQ

1

V

SSQ

BA

0

CS0

RAS

CAS

WE

NC

V

DDQ

NC

V

DD

A

3

A

2

A

1

A

0

AP/A

10

BA

1

NC

NC

NC

NC

CS1

V

DD

Bank Address

BA0~BA1

Auto Precharge

A10

Organization

Row Address

Column Address

st.128Mx4

A0~A12

A0-A9, A11

st.64Mx8

A0~A12

A0-A9

st.128Mb x 4

st.64Mb x 8

DDR SDRAM

DDR SDRAM stacked 512Mb E-die (x4/x8)

Rev. 1.0 July. 2003

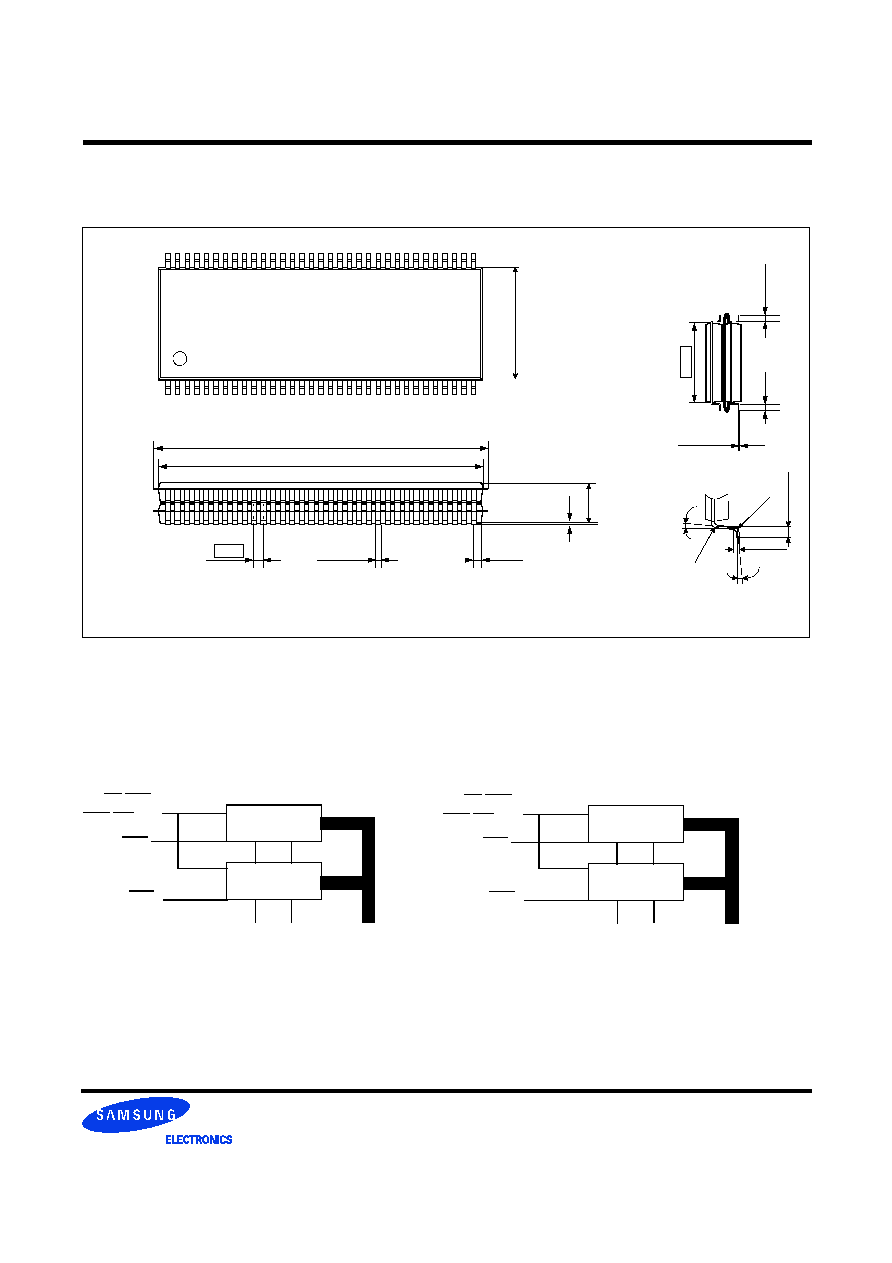

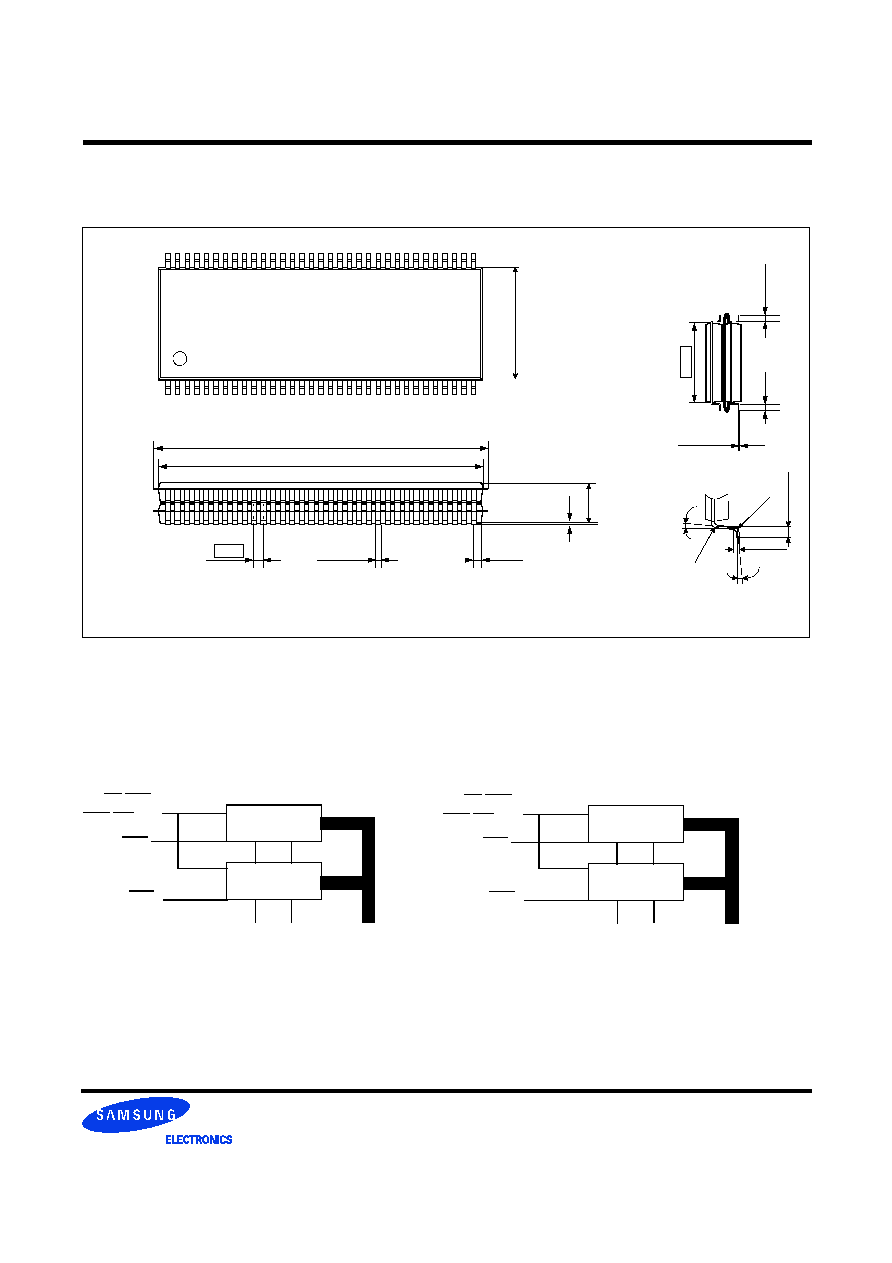

Units : Millimeters

NOTE

1. ( ) IS REFERENCE

2. [ ] IS ASS

'

Y OUT QUALITY

66pin TSOPII / Package dimension

Package Physical Dimension

Block Diagram

64Mx4

64Mx4

CK,CK,CAS

RAS,WE,DM

CKE1,CS1

CKE0,CS0

I/O0-I/O3,DQS

A0-A12,BA0,BA1

32Mx8

32Mx8

CK,CK,CAS

RAS,WE,DM

CKE1,CS1

CKE0,CS0

I/O 0 ~ I/O 3, DQS A0-A12, BA0,BA1

st.128Mb x 4

st.64Mb x 8

10.16

(0.50)

0.45~0.75

0.125

+

0.075

-

0.035

0

◊

~8

◊

(4

◊

)

(R

0.

25

)

(R

0.2

5)

0.45

~

0

.7

5

0.25TYP

22.62MAX

22.22

±

0.10

(0.71)

0.25

±

0.08

0.65

2.54(max)

0.05(min)

11

.

7

6

±

0.20

#1

#33

#66

#34