200pin DDR SDRAM SODIMM

M470L6423CK0

Rev. 0.2 Jan. 2002

512MB DDR SDRAM MODULE

200pin SODIMM

(64Mx64 based on DDP 64Mx 8 DDR SDRAM)

64bit Non-ECC/Parity

Revision 0.2

Jan. 2002

This is to advise Samsung customers that, until August 1, 2003, in accordance with certain terms of an agreement, Samsung is prohibited

from selling any DRAM products configured in "Multi-Die Plastic" format for use as components in general and scientific computers, such as

mainframes, servers, work stations or desk top personal computers (hereinafter "Prohibited Computer Use"). Applications such as mobile,

including cell phones, telecom, including televisions and display monitors, or non-desktop computer systems, including laptops, notebook

computers, are, however, permissible. "Multi-Die Plastic" is defined as two or more Dram die encapsulated within a single plastic leaded

package

200pin DDR SDRAM SODIMM

M470L6423CK0

Rev. 0.2 Jan. 2002

Revision History

Revision 0.0 (August 2001)

1. First release.

Revision 0.1 (Dec. 2001)

- Add derating values for the specifications if the single-ended clock skew rate is less than 1.0V/ns in page 47.

- Revised "Absolute maximum rating" table in page 38.

. Changed "Voltage on VDDQ supply relative to VSS" value from -0.5~3.6V to -1~3.6V

. Changed "power dissipation" value from 1.0W to 1.5W.

- Revised AC parameter table

- Deleted typical current in IDD spec. table

- Included address and control input setup/hold time(tIS/tIH) at slow slew rate in DDR200/266 AC specification

- Deleted Exit self refresh to write command(tXSW) in DDR200/266 AC specification

- Rename tXSA(exit self refresh to bank active command) to tXSNR(exit self refresh to non read command) at DDR200/266

- Rename tXSR(exit self refresh to read command) to tXSRD at DDR200/266

- Rename tWPREH(DQS in hold time) to tWPRE at DDR200/266

- Rename tREF(Refresh interval time) to tREFI at DDR200/266

- Changed tWR value from 2tCK to 15ns.

--Rename tCDLR(Write data out to Read command) t0 tWTR

- Added tDAL(tWR+tRP)

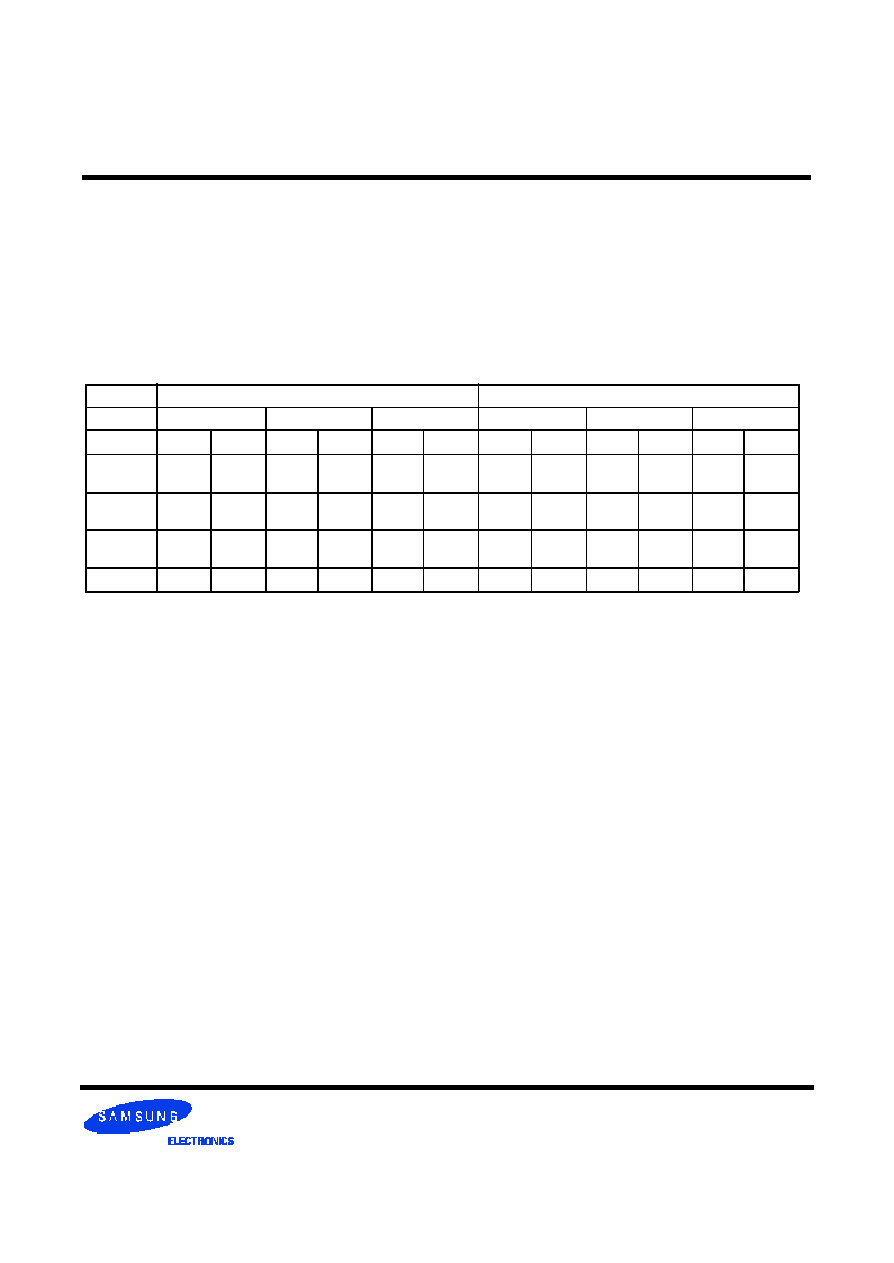

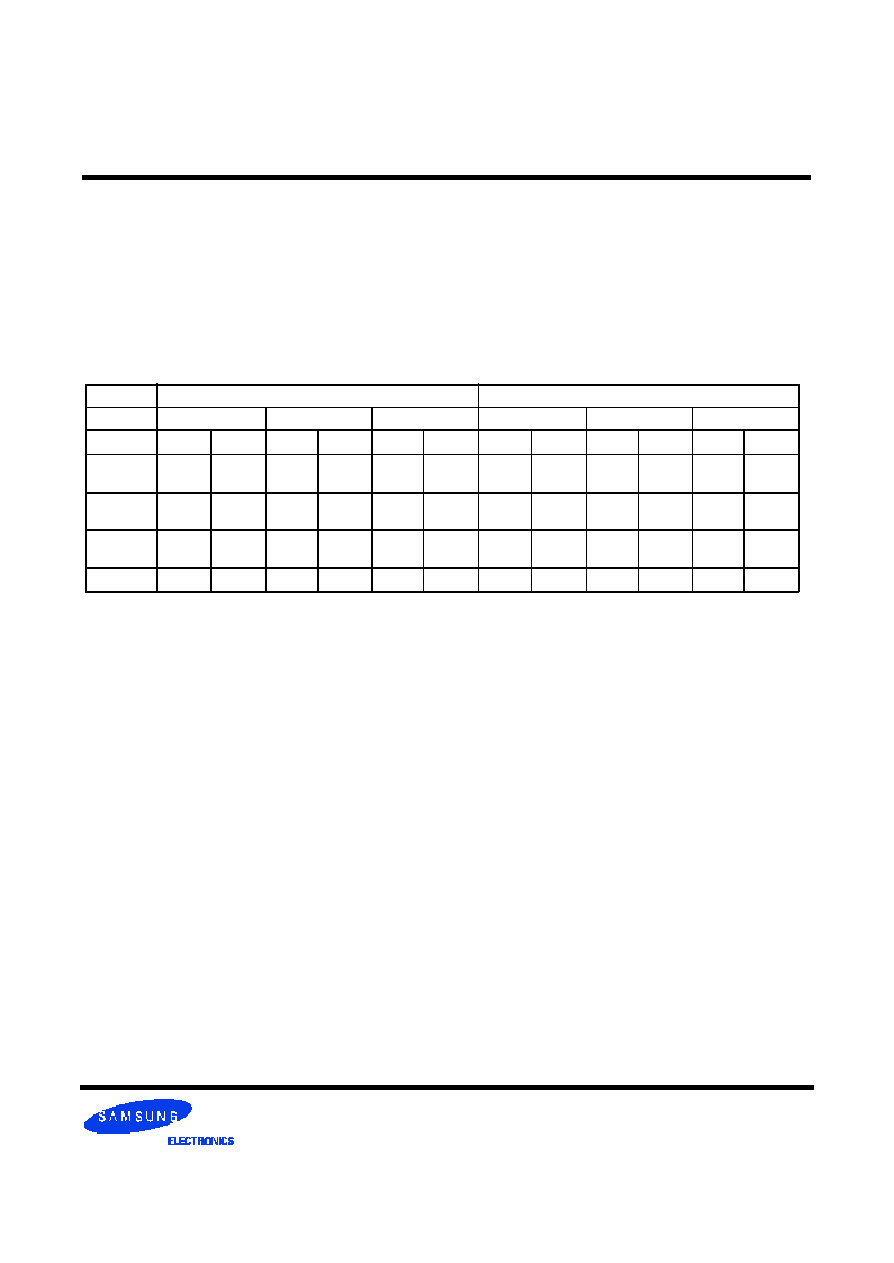

Revision 0.2 (Jan, 2002)

1. Added tRAP(Active to Read w/ autoprecharge command)

From

To

DDR266A

DDR266B

DDR200

DDR266A

DDR266B

DDR200

Min.

Max.

Min.

Max.

Min.

Max.

Min.

Max.

Min.

Max.

Min.

Max.

tHZ

tACmin

-400ps

tACmax

-400ps

tACmin

-400ps

tACmax

-400ps

tACmin

-400ps

tACmax

-400ps

-0.75

+0.75

-0.75

+0.75

-0.8

+0.8

tLZ

tACmin

-400ps

tACmax

-400ps

tACmin

-400ps

tACmax

-400ps

tACmin

-400ps

tACmax

-400ps

-0.75

+0.75

-0.75

+0.75

-0.8

+0.8

tWPST

(tCK)

0.25

0.25

0.25

0.4

0.6

0.4

0.6

0.4

0.6

tPDEX

10ns

10ns

10ns

7.5ns

7.5ns

10ns

200pin DDR SDRAM SODIMM

M470L6423CK0

Rev. 0.2 Jan. 2002

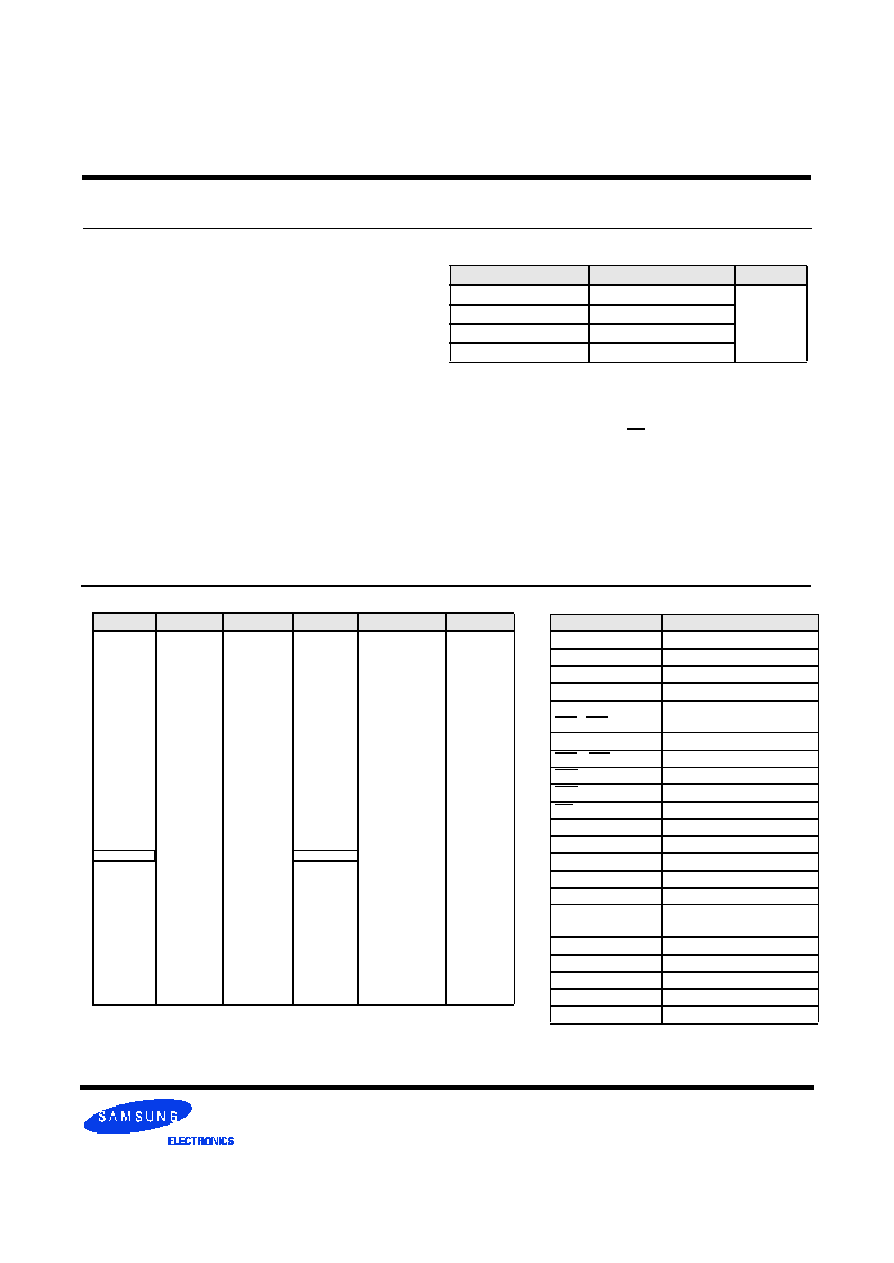

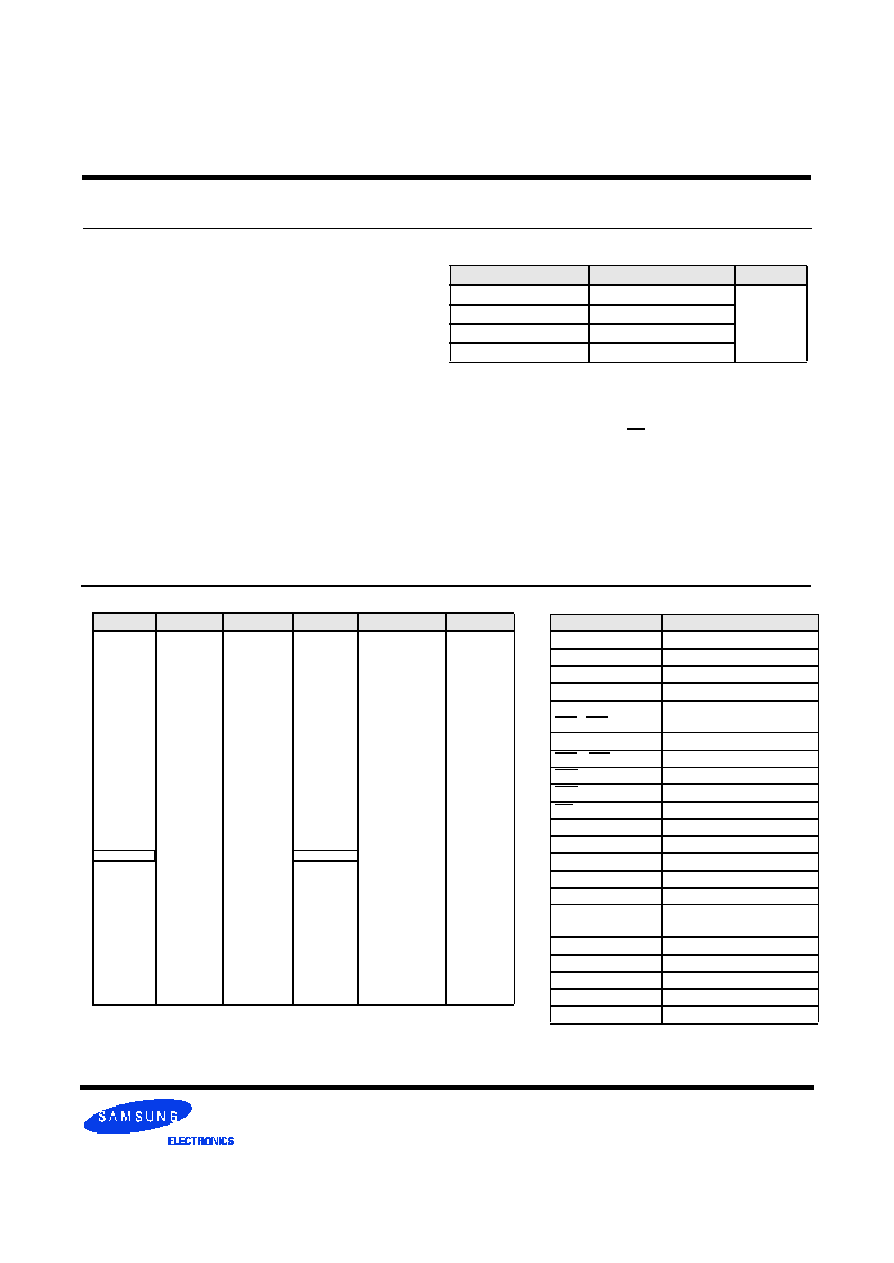

GENERAL DESCRIPTION

PIN DESCRIPTION

* These pins are not used in this module.

Pin Name

Function

A0 ~ A12

Address input (Multiplexed)

BA0 ~ BA1

Bank Select Address

DQ0 ~ DQ63

Data input/output

DQS0 ~ DQS7

Data Strobe input/output

CK0~ CK2,

CK0 ~ CK2

Clock input

CKE0 ~ CKE1

Clock enable input

CS0 ~ CS1

Chip select input

RAS

Row address strobe

CAS

Column address strobe

WE

Write enable

DM0 ~ DM7

Data - in mask

VDD

Power supply (2.5V)

VDDQ

Power Supply for DQS(2.5V)

VSS

Ground

VREF

Power supply for reference

VDDSPD

Serial EEPROM Power

Supply ( 2.3V to 3.6V)

SDA

Serial data I/O

SCL

Serial clock

SA0 ~ 2

Address in EEPROM

VDDID

VDD identification flag

NC

No connection

SAMSUNG ELECTRONICS CO., Ltd. reserves the right to change products and specifications without notice.

M470L6423CK0 200pin DDR SDRAM SODIMM

64Mx64 200pin DDR SDRAM SODIMM based on DDP 64Mx8

The Samsung M470L6423CK0 is 64M bit x 64 Double Data

Rate SDRAM high density memory modules.

The Samsung M470L6423CK0 consists of eight CMOS DDP

64M x 8 bit with 4banks Double Data Rate SDRAMs in 54pin

TSOP-II(400mil) packages mounted on a 200pin glass-epoxy

substrate. Four 0.1uF decoupling capacitors are mounted on

the printed circuit board in parallel for each DDR SDRAM.

The M470L6423CK0 is Dual In-line Memory Modules and

intended for mounting into 200pin edge connector sockets.

Synchronous design allows precise cycle control with the use

of system clock. Data I/O transactions are possible on both

edges of DQS. Range of operating frequencies, programmable

latencies and burst lengths allow the same device to be useful

for a variety of high bandwidth, high performance memory sys-

tem applications.

∑ Performance range

∑ Power supply : Vdd: 2.5V

±

0.2V, Vddq: 2.5V

±

0.2V

∑

Double-data-rate architecture; two data transfers per clock cycle

∑ Bidirectional data strobe(DQS)

∑ Differential clock inputs(CK and CK )

∑ DLL aligns DQ and DQS transition with CK transition

∑ Programmable Read latency 2, 2.5 (clock)

∑ Programmable Burst length (2, 4, 8)

∑ Programmable Burst type (sequential & interleave)

∑ Edge aligned data output, center aligned data input

∑ Auto & Self refresh, 7.8us refresh interval(8K/64ms refresh)

∑ Serial presence detect with EEPROM

∑ PCB : Height 1250 mil, double sided component

Part No.

Max Freq.

Interface

M470L6423CK0-C(L)B3 166MHz(6ns@CL=2.5)

SSTL_2

M470L6423CK0-C(L)A2 133MHz(7.5ns@CL=2)

M470L6423CK0-C(L)B0 133MHz(7.5ns@CL=2.5)

M470L6423CK0-C(L)A0 100MHz(10ns@CL=2)

FEATURE

PIN CONFIGURATIONS (Front side/back side)

Pin

Front

Pin

Front

Pin

Front

Pin

Back

Pin

Back

Pin

Back

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

VREF

VSS

DQ0

DQ1

VDD

DQS0

DQ2

VSS

DQ3

DQ8

VDD

DQ9

DQS1

VSS

DQ10

DQ11

VDD

CK0

/CK0

VSS

DQ16

DQ17

VDD

DQS2

DQ18

VSS

DQ19

DQ24

VDD

DQ25

DQS3

VSS

DQ26

67

69

71

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

DQ27

VDD

CB0

CB1

VSS

DQS8

CB2

VDD

CB3

DU

VSS

CK2

/CK2

VDD

CKE1

DU

A12

A9

VSS

A7

A5

A3

A1

VDD

A10/AP

BA0

/WE

/S0

DU(A13)

VSS

DQ32

DQ33

VDD

DQS4

135

137

139

141

143

145

147

149

151

153

155

157

159

161

163

165

167

169

171

173

175

177

179

181

183

185

187

189

191

193

195

197

199

DQ34

VSS

DQ35

DQ40

VDD

DQ41

DQS5

VSS

DQ42

DQ43

VDD

VDD

VSS

VSS

DQ48

DQ49

VDD

DQS6

DQ50

VSS

DQ51

DQ56

VDD

DQ57

DQS7

VSS

DQ58

DQ59

VDD

SDA

SCL

VDDSPD

VDDID

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

VREF

VSS

DQ4

DQ5

VDD

DM0

DQ6

VSS

DQ7

DQ12

VDD

DQ13

DM1

VSS

DQ14

DQ15

VDD

VDD

VSS

VSS

DQ20

DQ21

VDD

DM2

DQ22

VSS

DQ23

DQ28

VDD

DQ29

DM3

VSS

DQ30

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

DQ31

VDD

CB4

CB5

VSS

DM8

CB6

VDD

CB7

DU/(RESET)

VSS

VSS

VDD

VDD

CKE0

DU(BA2)

A11

A8

VSS

A6

A4

A2

A0

VDD

BA1

/RAS

/CAS

/S1

DU

VSS

DQ36

DQ37

VDD

DM4

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

DQ38

VSS

DQ39

DQ44

VDD

DQ45

DM5

VSS

DQ46

DQ47

VDD

/CK1

CK1

VSS

DQ52

DQ53

VDD

DM6

DQ54

VSS

DQ55

DQ60

VDD

DQ61

DM7

VSS

DQ62

DQ63

VDD

SA0

SA1

SA2

D U

Key

Key

200pin DDR SDRAM SODIMM

M470L6423CK0

Rev. 0.2 Jan. 2002

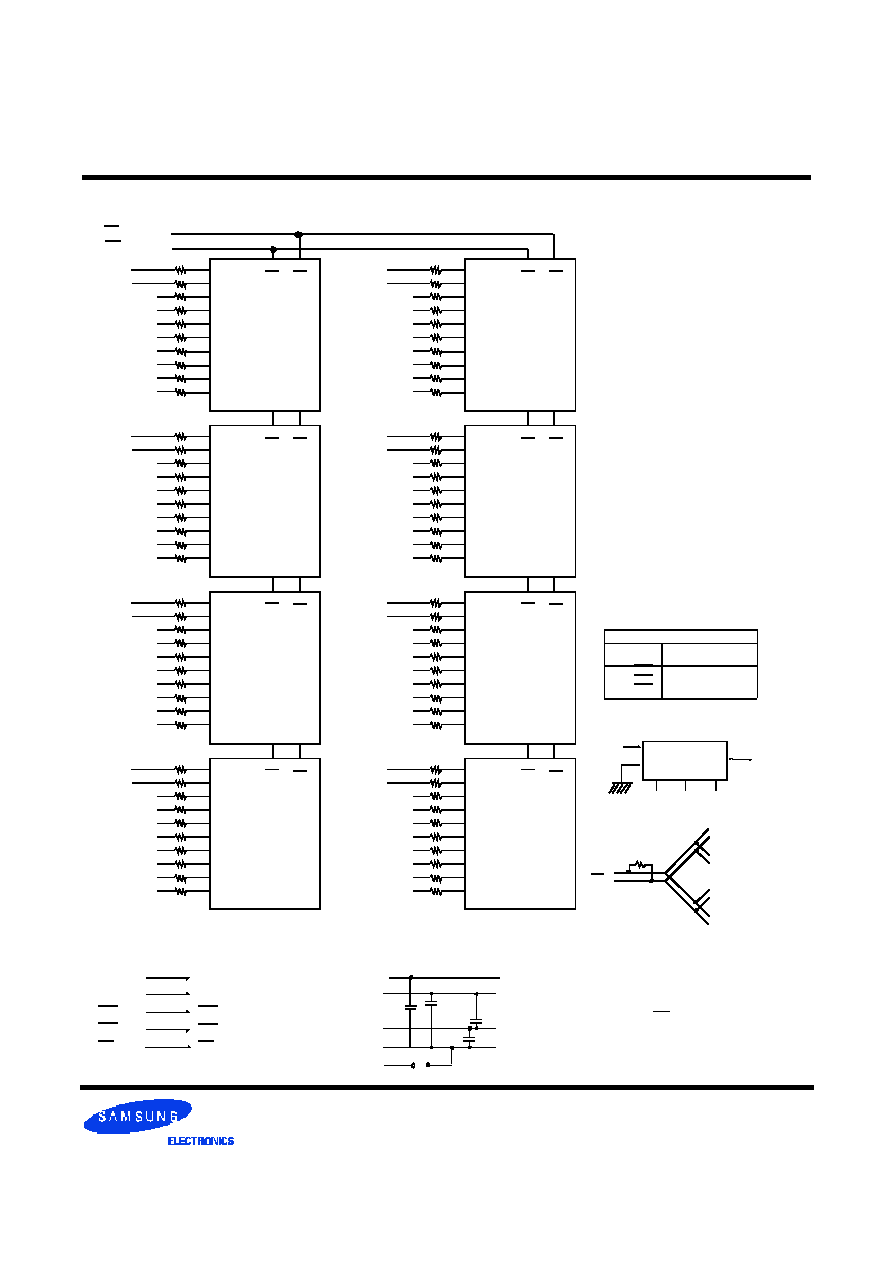

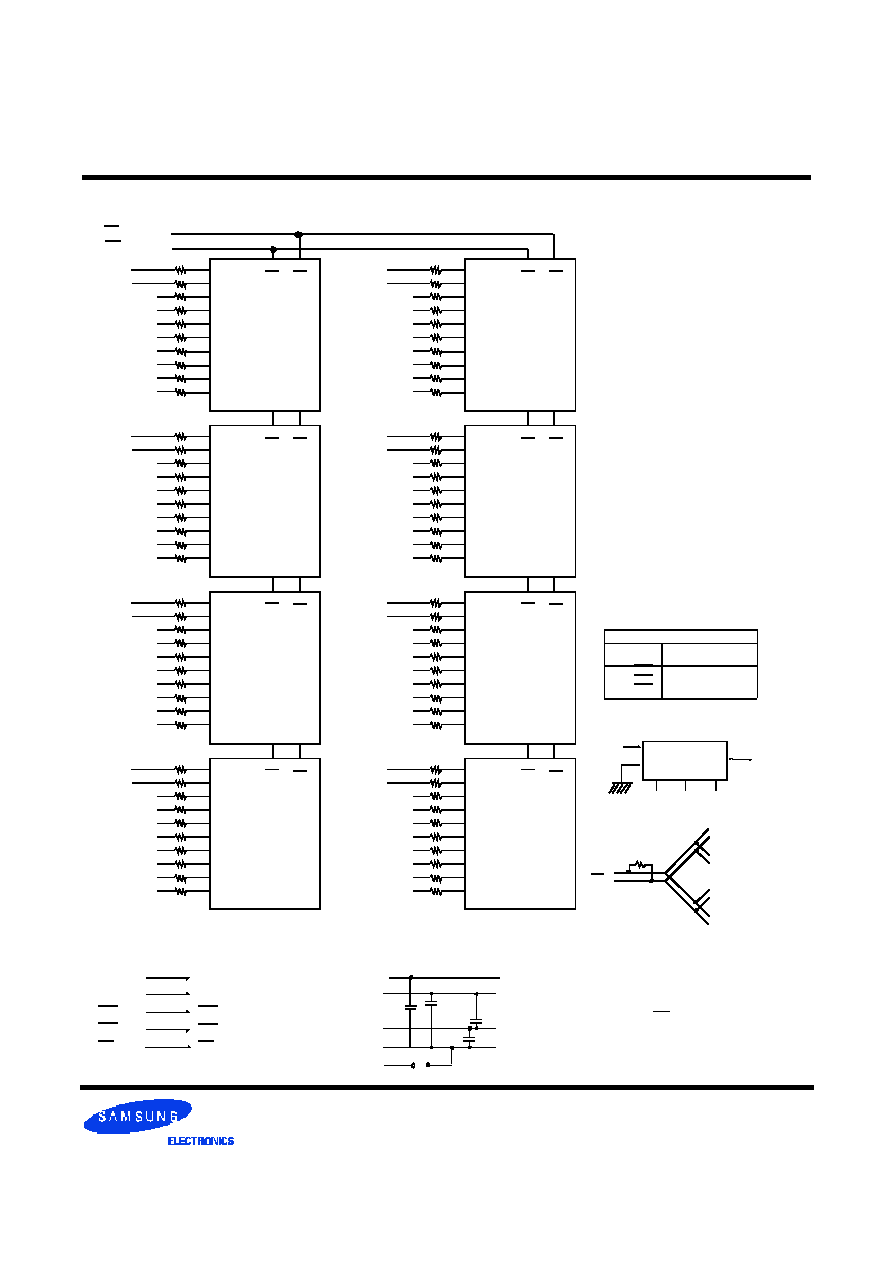

CKE0

I/0 0

I/0 1

I/0 2

I/0 3

I/0 4

I/0 5

I/0 6

I/0 7

D0

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQS

S0

A0 - A13

A0-A13: DDR SDRAMs D0 - D7

BA0 - BA1

BA0-BA1: DDR SDRAMs D0 - D7

RAS

RAS: SDRAMs D0 - D7

CAS

CAS: SDRAMs D0 - D7

WE

WE: SDRAMs D0 - D7

A0

Serial PD

A1

A2

SA0

SA1

SA2

SCL

SDA

WP

V

S S

D0 - D7

D0 - D7

V

DD

/V

DDQ

D0 - D7

D0 - D7

VREF

V

DDID

Strap: see Note 4

V

DDSPD

SPD

Clock Wiring

Clock

Input

SDRAMs

CK0/ CK0

CK1/ CK1

CK2/ CK2

4 SDRAMs

4 SDRAMs

NC

DM

DQS0

DM0

*Clock Net Wiring

Card

Edge

Dram1

Dram2

R=120

±

5%

CK

CK

Dram3

Dram4

I/0 0

I/0 1

I/0 2

I/0 3

I/0 4

I/0 5

I/0 6

I/0 7

D4

DQS

S0

DM

DQS4

DM4

I/0 0

I/0 1

I/0 2

I/0 3

I/0 4

I/0 5

I/0 6

I/0 7

D1

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQS

S1

DM

DQS1

DM1

I/0 0

I/0 1

I/0 2

I/0 3

I/0 4

I/0 5

I/0 6

I/0 7

D5

DQS

S1

DM

DQS5

DM5

I/0 0

I/0 1

I/0 2

I/0 3

I/0 4

I/0 5

I/0 6

I/0 7

D2

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQS

S0

DM

DQS2

DM2

I/0 0

I/0 1

I/0 2

I/0 3

I/0 4

I/0 5

I/0 6

I/0 7

D6

DQS

S0

DM

DQS6

DM6

I/0 0

I/0 1

I/0 2

I/0 3

I/0 4

I/0 5

I/0 6

I/0 7

D3

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQS

S1

DM

DQS3

DM3

I/0 0

I/0 1

I/0 2

I/0 3

I/0 4

I/0 5

I/0 6

I/0 7

D7

DQS

S1

DM

DQS7

DM7

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

CKE1

S1

S1

S0

S0

S1

S1

S0

S0

S0

S1

CKE0 CKE1

CKE0 CKE1

CKE1 CKE0

CKE1 CKE0

CKE0 CKE1

CKE0 CKE1

CKE1 CKE0

CKE1 CKE0

Notes:

1. DQ-to-I/O wiring is shown as recom-

mended but may be changed.

2. DQ/DQS/DM/CKE/CS relationships must

be maintained as shown.

3. DQ, DQS, DM/DQS resistors: 22 Ohms.

FUNCTIONAL BLOCK DIAGRAM

200pin DDR SDRAM SODIMM

M470L6423CK0

Rev. 0.2 Jan. 2002

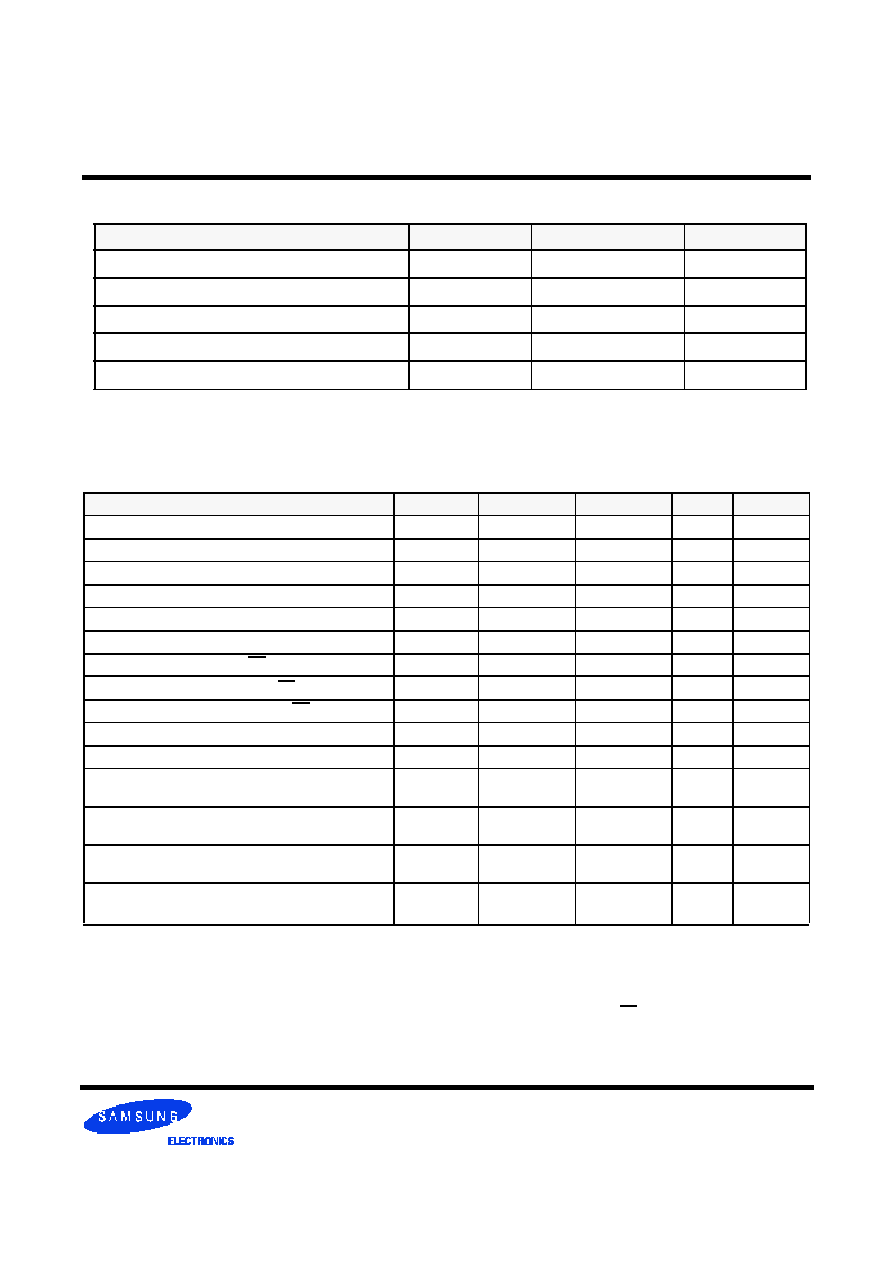

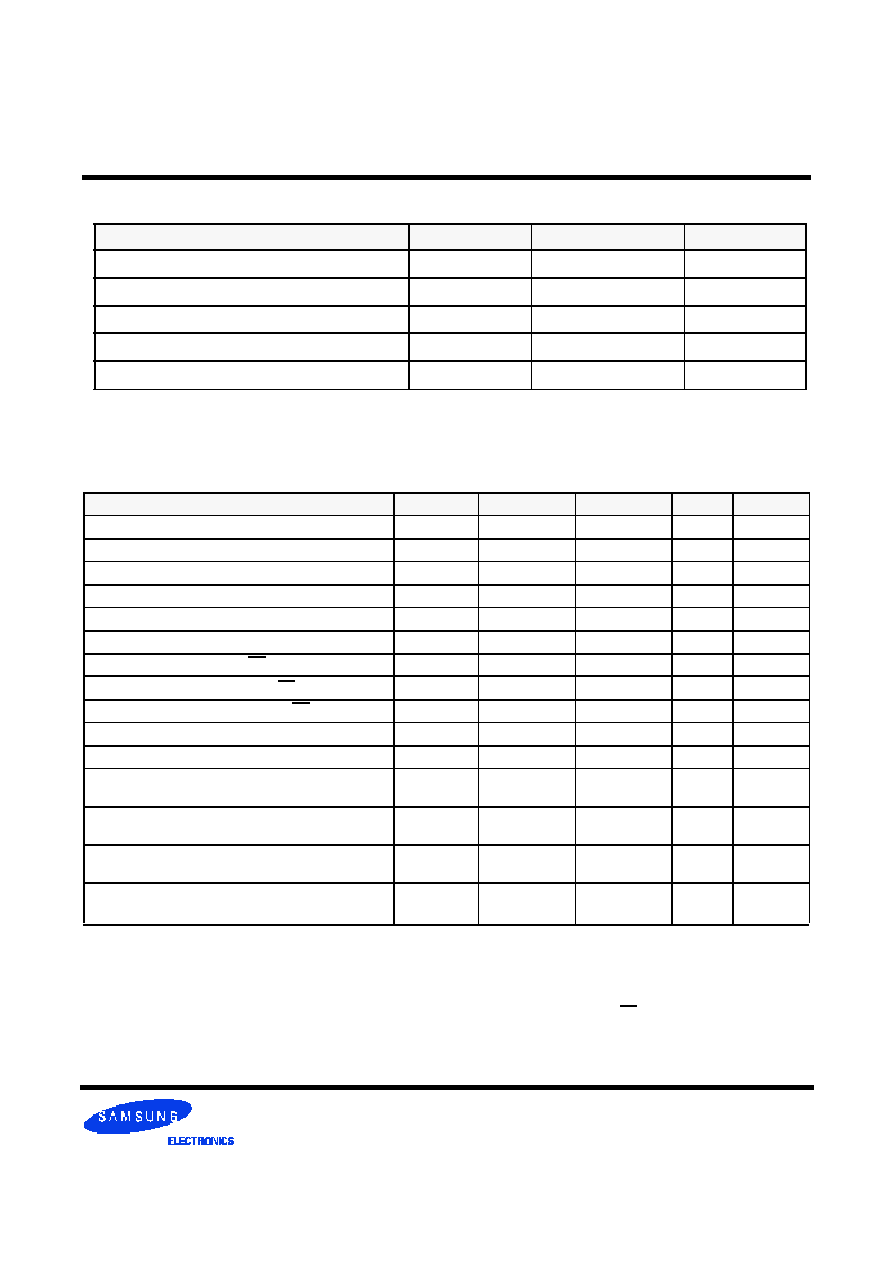

Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded.

Functional operation should be restricted to recommended operating condition.

Exposure to higher than recommended voltage for extended periods of time could affect device reliability.

Note :

POWER & DC OPERATING CONDITIONS (SSTL_2 In/Out)

Notes 1. Includes

±

25mV margin for DC offset on V

REF

, and a combined total of

±

50mV margin for all AC noise and DC offset on V

REF

,

bandwidth limited to 20MHz. The DRAM must accommodate DRAM current spikes on V

REF

and internal DRAM noise coupled

TO V

REF

, both of which may result in V

REF

noise. V

REF

should be de-coupled with an inductance of

3nH.

2.V

TT

is not applied directly to the device. V

T T

is a system supply for signal termination resistors, is expected to be set equal to

V

REF

, and must track variations in the DC level of V

REF

3. V

I D

is the magnitude of the difference between the input level on CK and the input level on CK.

4. These parameters should be tested at the pin on actual components and may be checked at either the pin or the pad in

simulation. The AC and DC input specifications are relative to a VREF envelop that has been bandwidth limited to 200MHZ.

5. The value of V

IX

is expected to equal 0.5*V

DDQ

of the transmitting device and must track variations in the dc level of the same.

6. These charactericteristics obey the SSTL-2 class II standards.

Recommended operating conditions(Voltage referenced to V

SS

=0V, T

A

=0 to 70

∞

C)

Parameter

Symbol

Min

Max

Unit

Note

Supply voltage(for device with a nominal V

DD

of 2.5V)

V

DD

2.3

2.7

I/O Supply voltage

V

DDQ

2.3

2.7

V

I/O Reference voltage

V

REF

VDDQ/2-50mV

VDDQ/2+50mV

V

1

I/O Termination voltage(system)

V

TT

V

REF

-0.04

V

REF

+0.04

V

2

Input logic high voltage

V

I H

(DC)

V

REF

+0.15

V

DDQ

+0.3

V

4

Input logic low voltage

V

IL

(DC)

-0.3

V

REF

-0.15

V

4

Input Voltage Level, CK and CK inputs

V

I N

(DC)

-0.3

V

DDQ

+0.3

V

Input Differential Voltage, CK and CK inputs

V

I D

(DC)

0.3

V

DDQ

+0.6

V

3

Input crossing point voltage, CK and CK inputs

V

IX

(DC)

1.15

1.35

V

5

Input leakage current

I

I

-2

2

uA

Output leakage current

I

O Z

-5

5

uA

Output High Current(Normal strengh driver)

;V

OUT

= V

T T

+ 0.84V

I

OH

-16.8

mA

Output High Current(Normal strengh driver)

;V

OUT

= V

T T

- 0.84V

I

OL

16.8

mA

Output High Current(Half strengh driver)

;V

OUT

=

V

T T

+ 0.45V

I

OH

-9

mA

Output High Current(Half strengh driver)

;V

OUT

= V

T T

- 0.45V

I

OL

9

mA

Parameter

Symbol

Value

Unit

Voltage on any pin relative to V

SS

V

IN

, V

OUT

-0.5 ~ 3.6

V

Voltage on V

DD

& V

DDQ

supply relative to V

SS

V

DD

, V

DDQ

-1.0 ~ 3.6

V

Storage temperature

T

STG

-55 ~ +150

∞

C

Power dissipation

P

D

24

W

Short circuit current

I

OS

50

mA

Absolute Maximum Rate