DDR SDRAM

512MB Unbuffered SODIMM(based on sTSOP)

Rev. 1.3 March. 2004

DDR SDRAM Unbuffered SODIMM

200pin Unbuffered SODIMM based on 256Mb E-die (x8)

with 64-bit Non ECC

Revision 1.3

March. 2004

DDR SDRAM

512MB Unbuffered SODIMM(based on sTSOP)

Rev. 1.3 March. 2004

Revision History

Revision 1.0 (May, 2003)

- First release

Revision 1.1 (August, 2003)

- Corrected typo.

Revision 1.2 (December, 2003)

- Corrected typo.

Revision 1.3 (March, 2004)

- Corrected package dimension

.

DDR SDRAM

512MB Unbuffered SODIMM(based on sTSOP)

Rev. 1.3 March. 2004

SAMSUNG ELECTRONICS CO., Ltd. reserves the right to change products and specifications without notice.

200Pin Unbuffered SODIMM based on 256Mb E-die (x8)

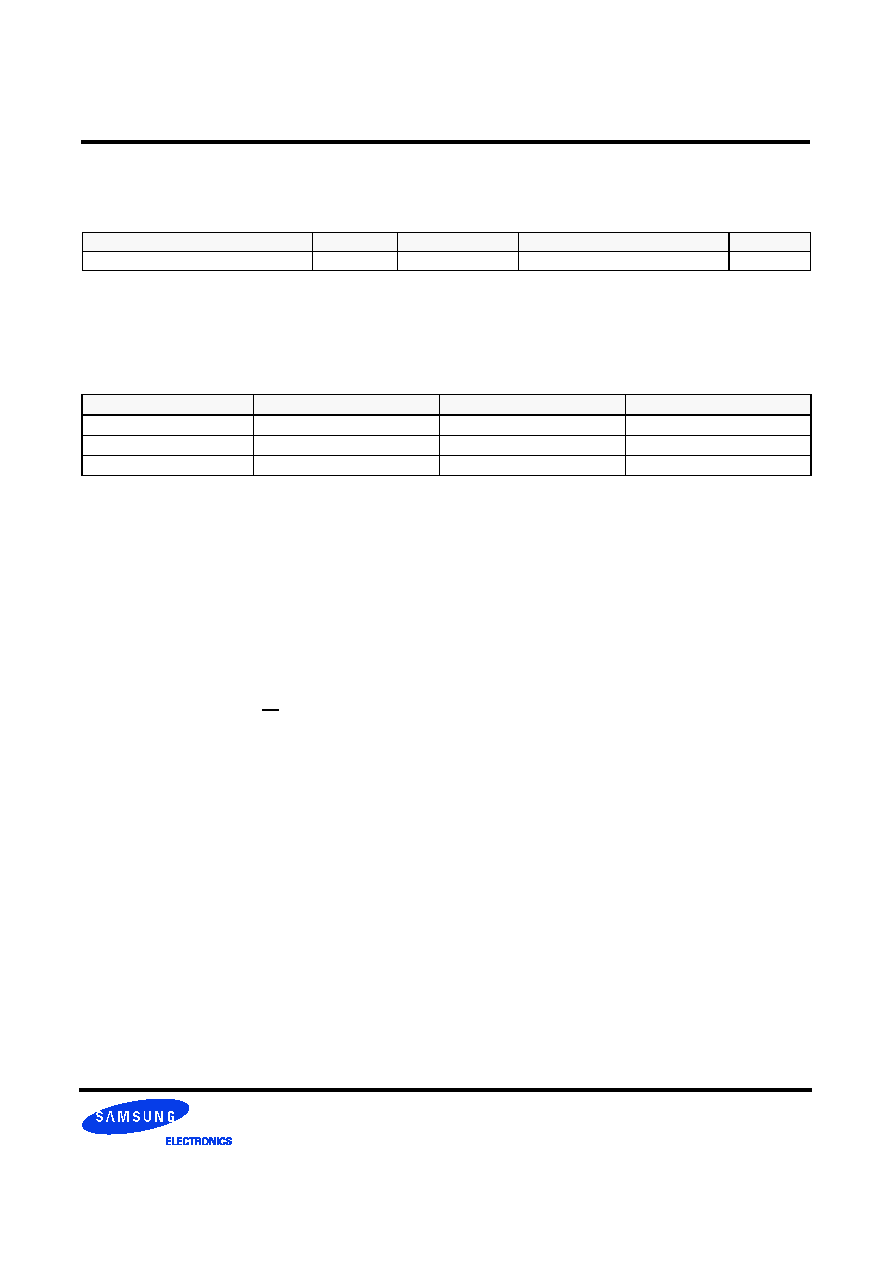

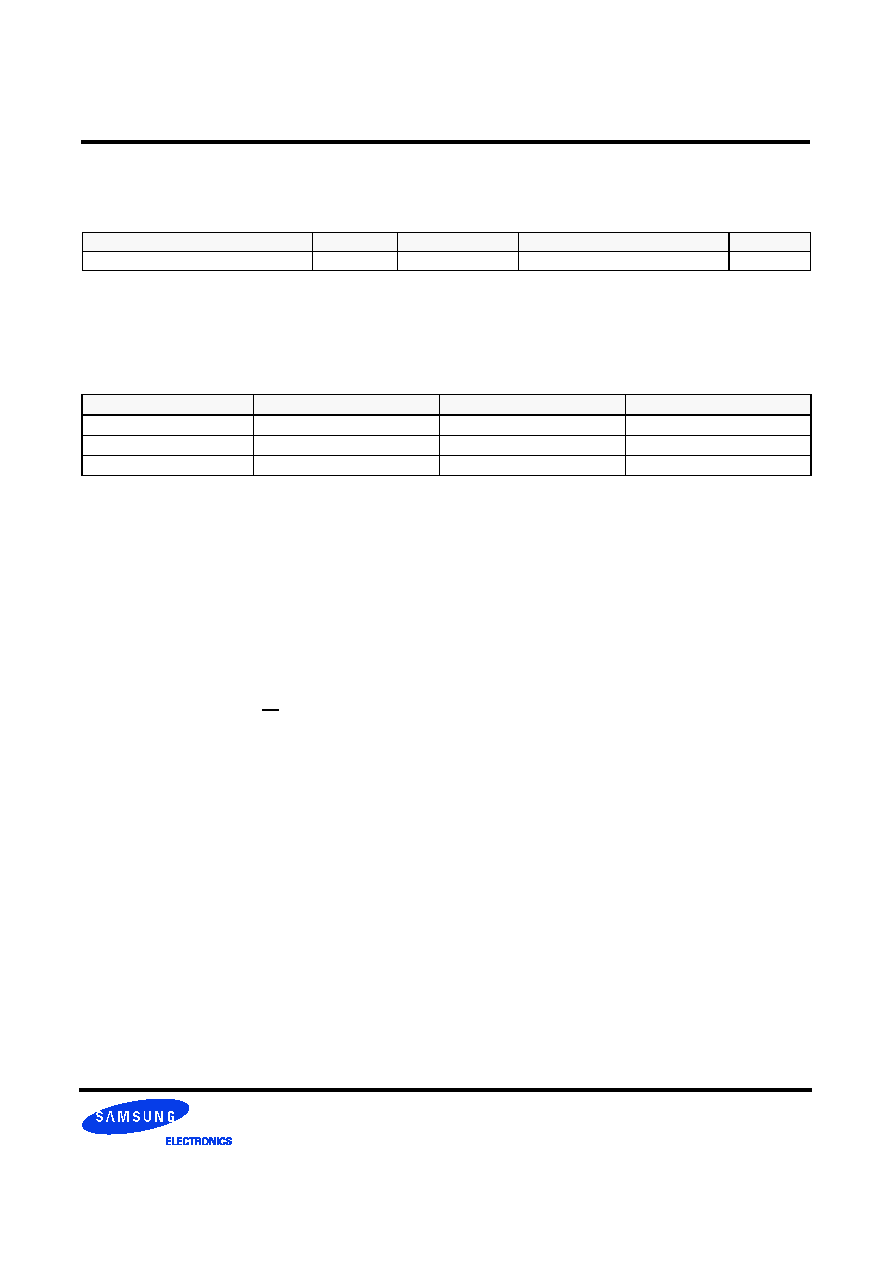

Ordering Information

Operating Frequencies

Part Number

Density

Organization

Component Composition

Height

M470L6423EN0-C(L)B3/A2/B0

512MB

64M x 64

32Mx8 (K4H560838E) * 16EA

1,250mil

B3(DDR333@CL=2.5)

A2(DDR266@CL=2)

B0(DDR266@CL=2.5)

Speed @CL2

133MHz

133MHz

100MHz

Speed @CL2.5

166MHz

133MHz

133MHz

CL-tRCD-tRP

2.5-3-3

2-3-3

2.5-3-3

Feature

∑ Power supply : Vdd: 2.5V

±

0.2V, Vddq: 2.5V

±

0.2V

∑ Double-data-rate architecture; two data transfers per clock cycle

∑ Bidirectional data strobe(DQS)

∑ Differential clock inputs(CK and CK)

∑ DLL aligns DQ and DQS transition with CK transition

∑ Programmable Read latency 2, 2.5 (clock)

∑ Programmable Burst length (2, 4, 8)

∑ Programmable Burst type (sequential & interleave)

∑ Edge aligned data output, center aligned data input

∑ Auto & Self refresh, 7.8us refresh interval(8K/64ms refresh)

∑ Serial presence detect with EEPROM

∑ PCB : Height 1,250 (mil), double (512MB) sided

∑

SSTL_2 Interface

∑ 54pin sTSOP(II)-300 package

DDR SDRAM

512MB Unbuffered SODIMM(based on sTSOP)

Rev. 1.3 March. 2004

KEY

KEY

Pin Configurations (Front side/back side)

Note 1. * : These pins are not used in this module.

2. Pins 71, 72, 73, 74, 77, 78, 79, 80, 83, 84 are reserved for x72 module, and are not used on x64 module.

Pin 95,122 are NC for 8Mx16 based module & used for 16Mx8 based module.

3. Pins 89, 91 are reserved for x72 modules.

Pin

Front

Pin

Front

Pin

Front

Pin

Back

Pin

Back

Pin

Back

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

VREF

VSS

DQ0

DQ1

VDD

DQS0

DQ2

VSS

DQ3

DQ8

VDD

DQ9

DQS1

VSS

DQ10

DQ11

VDD

CK0

/CK0

VSS

DQ16

DQ17

VDD

DQS2

DQ18

VSS

DQ19

DQ24

VDD

DQ25

DQS3

VSS

DQ26

67

69

*71

*73

75

*77

*79

81

*83

85

87

*89

*91

93

*95

97

99

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

DQ27

VDD

CB0

CB1

VSS

DQS8

CB2

VDD

CB3

DU

VSS

CK2

/CK2

VDD

CKE1

DU

A12

A9

VSS

A7

A5

A3

A1

VDD

A10/AP

BA0

/WE

/CS0

*DU(A13)

VSS

DQ32

DQ33

VDD

DQS4

135

137

139

141

143

145

147

149

151

153

155

157

159

161

163

165

167

169

171

173

175

177

179

181

183

185

187

189

191

193

195

197

199

DQ34

VSS

DQ35

DQ40

VDD

DQ41

DQS5

VSS

DQ42

DQ43

VDD

VDD

VSS

VSS

DQ48

DQ49

VDD

DQS6

DQ50

VSS

DQ51

DQ56

VDD

DQ57

DQS7

VSS

DQ58

DQ59

VDD

SDA

SCL

VDDSPD

VDDID

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

VREF

VSS

DQ4

DQ5

VDD

DM0

DQ6

VSS

DQ7

DQ12

VDD

DQ13

DM1

VSS

DQ14

DQ15

VDD

VDD

VSS

VSS

DQ20

DQ21

VDD

DM2

DQ22

VSS

DQ23

DQ28

VDD

DQ29

DM3

VSS

DQ30

68

70

*72

*74

76

*78

*80

82

*84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

*122

124

126

128

130

132

134

DQ31

VDD

CB4

CB5

VSS

DM8

CB6

VDD

CB7

*DU/(RESET)

VSS

VSS

VDD

VDD

CKE0

DU(BA2)

A11

A8

VSS

A6

A4

A2

A0

VDD

BA1

/RAS

/CAS

/CS1

DU

VSS

DQ36

DQ37

VDD

DM4

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

DQ38

VSS

DQ39

DQ44

VDD

DQ45

DM5

VSS

DQ46

DQ47

VDD

/CK1

CK1

VSS

DQ52

DQ53

VDD

DM6

DQ54

VSS

DQ55

DQ60

VDD

DQ61

DM7

VSS

DQ62

DQ63

VDD

SA0

SA1

SA2

DU

Pin Description

Pin Name

Function

Pin Name

Function

A0 ~ A12

Address input (Multiplexed)

DM0 ~ 7

Data - in mask

BA0 ~ BA1

Bank Select Address

VDD

Power supply (2.5V)

DQ0 ~ DQ63

Data input/output

VDDQ

Power Supply for DQS(2.5V)

DQS0 ~ DQS7

Data Strobe input/output

VSS

Ground

CK0,CK0 ~ CK1, CK1

Clock input

VREF

Power supply for reference

CKE0 ~ CKE1

Clock enable input

VDDSPD

Serial EEPROM Power

CS0 ~ CS1

Chip select input

SDA

Serial data I/O

RAS

Row address strobe

SCL

Serial clock

CAS

Column address strobe

SA0 ~ 2

Address in EEPROM

WE

Write enable

NC

No connection

DDR SDRAM

512MB Unbuffered SODIMM(based on sTSOP)

Rev. 1.3 March. 2004

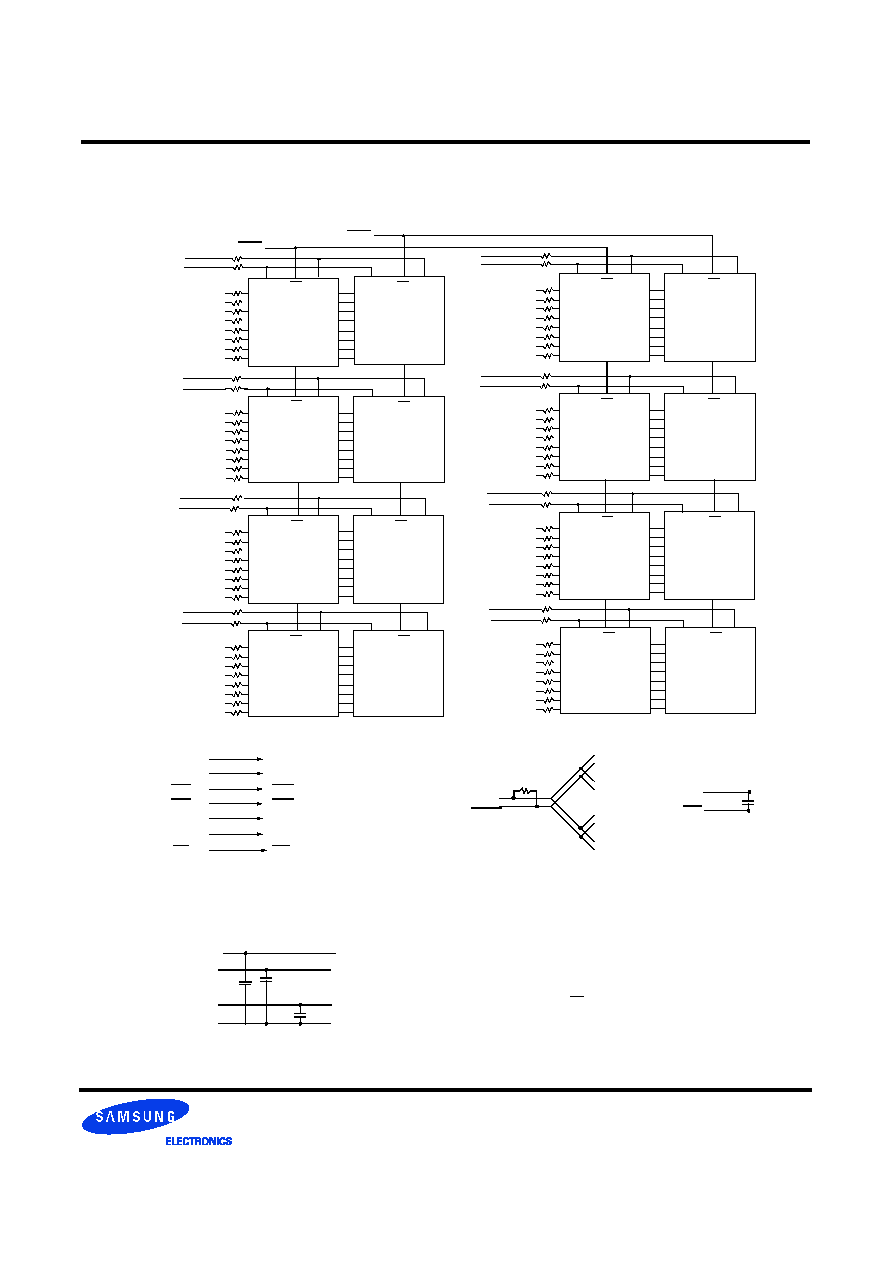

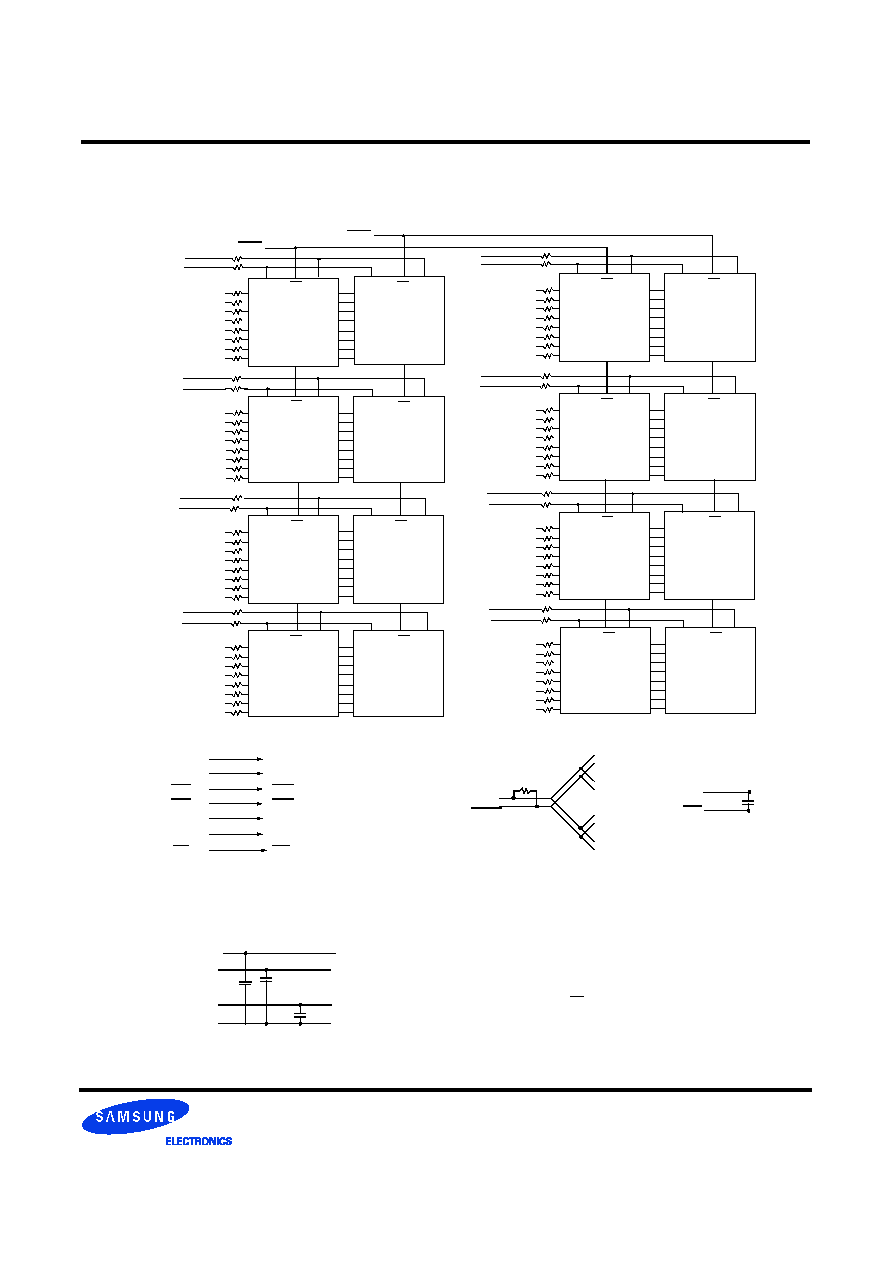

FUNCTIONAL BLOCK DIAGRAM

DQ4

DQ5

DQ6

DQ7

DQ0

DQ1

DQ2

DQ3

DM

I/O 7

I/O 6

I/O 1

I/O 0

D0

DM0

DM

D8

I/O 5

I/O 4

I/O 3

I/O 2

I/O 0

I/O 1

I/O 6

I/O 7

I/O 2

I/O 3

I/O 4

I/O 5

DQ12

DQ13

DQ14

DQ8

DQ9

DQ10

DQ11

DM

I/O 7

I/O 6

I/O 1

I/O 0

D1

DM

D9

I/O 5

I/O 4

I/O 3

I/O 0

I/O 1

I/O 6

I/O 7

I/O 2

I/O 3

I/O 4

DM1

DQ20

DQ21

DQ22

DQ23

DQ16

DQ17

DQ18

DQ19

DM

I/O 7

I/O 6

I/O 1

I/O 0

D2

DM

D10

I/O 5

I/O 4

I/O 3

I/O 2

I/O 0

I/O 1

I/O 6

I/O 7

I/O 2

I/O 3

I/O 4

I/O 5

DM2

DQ28

DQ29

DQ30

DQ31

DQ24

DQ25

DQ26

DQ27

DM

I/O 7

I/O 6

I/O 1

I/O 0

D3

DM

D11

I/O 5

I/O 4

I/O 3

I/O 2

I/O 0

I/O 1

I/O 6

I/O 7

I/O 2

I/O 3

I/O 4

I/O 5

DM3

DQ36

DQ37

DQ38

DQ39

DQ32

DQ33

DQ34

DQ35

DM

I/O 7

I/O 6

I/O 1

I/O 0

D4

DM4

DM

D12

I/O 5

I/O 4

I/O 3

I/O 2

I/O 0

I/O 1

I/O 6

I/O 7

I/O 2

I/O 3

I/O 4

I/O 5

DQ44

DQ45

DQ46

DQ47

DQ40

DQ41

DQ42

DQ43

DM

I/O 7

I/O 6

I/O 1

I/O 0

D5

DM

D13

I/O 5

I/O 4

I/O 3

I/O 2

I/O 0

I/O 1

I/O 6

I/O 7

I/O 2

I/O 3

I/O 4

I/O 5

DM5

DQ52

DQ53

DQ54

DQ55

DQ48

DQ49

DQ50

DQ51

DM

I/O 7

I/O 6

I/O 1

I/O 0

D6

DM

D14

I/O 5

I/O 4

I/O 3

I/O 2

I/O 0

I/O 1

I/O 6

I/O 7

I/O 2

I/O 3

I/O 4

I/O 5

DQ60

DQ61

DQ62

DQ63

DQ56

DQ57

DQ58

DQ59

DM

I/O 7

I/O 6

I/O 1

I/O 0

D7

DM

D15

I/O 5

I/O 4

I/O 3

I/O 2

I/O 0

I/O 1

I/O 6

I/O 7

I/O 2

I/O 3

I/O 4

I/O 5

DM7

A0 - A12

A0-A12 : DDR SDRAMs D0 - D15

RAS

RAS : DDR SDRAMs D0 - D15

CAS

CAS : DDR SDRAMs D0 - D15

CKE0

CKE : DDR SDRAMs D0 - D7

WE

WE : DDR SDRAMs D0 - D15

CS0

CS1

CS

CS

CS

CS

CS

CS

CS

CS

CS

CS

CS

CS

CS

CS

CS

CS

CKE1

CKE : DDR SDRAMs D8 - D15

BA0 - BA1

BA0-BA1: DDR SDRAMs D0 - D15

DQS0

DQS

DQS4

DQS1

DQS5

DQS

DQS

DQS2

DQS

DQS

DQS3

DQS

DQS

DM6

DQS6

DQS7

DQ15

I/O 2

I/O 5

DQS

DQS

DQS

DQS

DQS

DQS

DQS

DQS

DQS

V

SS

D0 - D15

D0 - D15

V

DD

/V

DDQ

D0 - D15

D0 - D15

VREF

V

DDSPD

SPD

*Clock Net Wiring

Card

Edge

D0,D8 / D4,D12

D1,D9 / D5,D13

R=120

±

5%

CK0 / 1

CK0 / 1

D2,D10/ D6,D14

D3,D11/ D7,D15

Notes :

1. DQ-to-I/O wiring is shown as recommended but may be changed.

2. DQ/DQS/DM/CKE/CS relationships must be maintained as shown

3. DQ, DQS, DM/DQS resistors: 22 Ohm.

CK2

CK2

10pF