Cool Solutions for Wireless Connectivity

XEMICS SA

∑

e-mail: info@xemics.com

∑

web: www.xemics.com

Datasheet XE88LC02 Sensing

Machine Data Acquisition MCU

with Zooming ADC and LCD driver

XE88LC02

Sensing Machine

Data Acquisition MCU with

16 + 10 bit ZoomingADC and LCD driver

General Description

The XE88LC02 is a data acquisition ultra low-

power low-voltage microcontroller unit (MCU) with

extremely high efficiency, allowing for 1 MIPS at

300uA and 2.4 V, and 8 x 8 bits multiplying in one

clock cycle at 1.2 V.

XE88LC02 includes a high resolution acquisition

path with the 16+10 bits ZoomingADC and an

LCD driver for up to 120 segments. The LCD lines

can be used as additional IOs.

XE88LC02 is available with on chip ROM or Multi-

ple-Time-Programmable (MTP) program memory.

Applications

∑

Portable, battery operated instruments

∑

RF system supervisor

∑

Remote

control

∑

HVAC

control

∑

Metering

∑

Sports watches, wrist instruments

Key product Features

∑

Low-power, high resolution ZoomingADC

∑

0.5 to 1000 gain with offset cancellation

∑

up to 16 bits ADC

∑

up to 13 input multiplexer

∑

4 low power comparators

∑

Low-voltage

low-power controller operation

∑

2 MIPS with 2.4 V to 5.5 V operation

∑

300 µA at 1 MIPS over voltage range

∑

up to 7 MIPS in ROM

∑

1.2 V operation in ROM

∑

22 kByte (8 kInstruction) MTP

∑

1032 Byte RAM data memory

∑

RC and crystal oscillators

∑

5 reset, 22 interrupt, 8 event sources

∑

120 segments LCD driver

∑

can be used as extra IO

∑

100 years MTP Flash retention at 55∞C

Ordering Information

Product Temperature

range

Memory

type

Package

XE88LC02MI000

-40∞C to 85 ∞C

MTP

die

XE88LC02MI035

-40∞C to 85 ∞C

MTP

LQFP100

D0309-134

Datasheet XE88LC02 Sensing

Machine Data Acquisition MCU

with Zooming ADC and LCD driver

TABLE OF CONTENTS

Chapter 1

XE88LC02 Overview

Chapter 2

XE88LC02 Performance

Chapter 3

XE88LC02 CPU

Chapter 4

XE88LC02 Memory

Chapter 5

Low power modes

Chapter 6

Reset generator

Chapter 7

Clock generation

Chapter 8

Interrupt handler

Chapter 9

Event handler

Chapter 10

Low power RAM

Chapter 11

Port A

Chapter 12

Port B

Chapter 13

Port D

Chapter 14

Universal Asynchronous Receiver/Transmitter (UART)

Chapter 15

Universal Synchronous Receiver/Transmitter (USRT)

Chapter 16

Serial Peripheral Interface (SPI)

Chapter 17

Acquisition chain

Chapter 18

Voltage multiplier

Chapter 19

LCD driver

Chapter 20

Counters/PWM

Chapter 21

The Voltage Level Detector

Chapter 22

Low Power Comparators

Chapter 23

XE88LC02 Dimensions

1-2

D0309-134

Datasheet XE88LC02 Sensing

Machine Data Acquisition MCU

with Zooming ADC and LCD driver

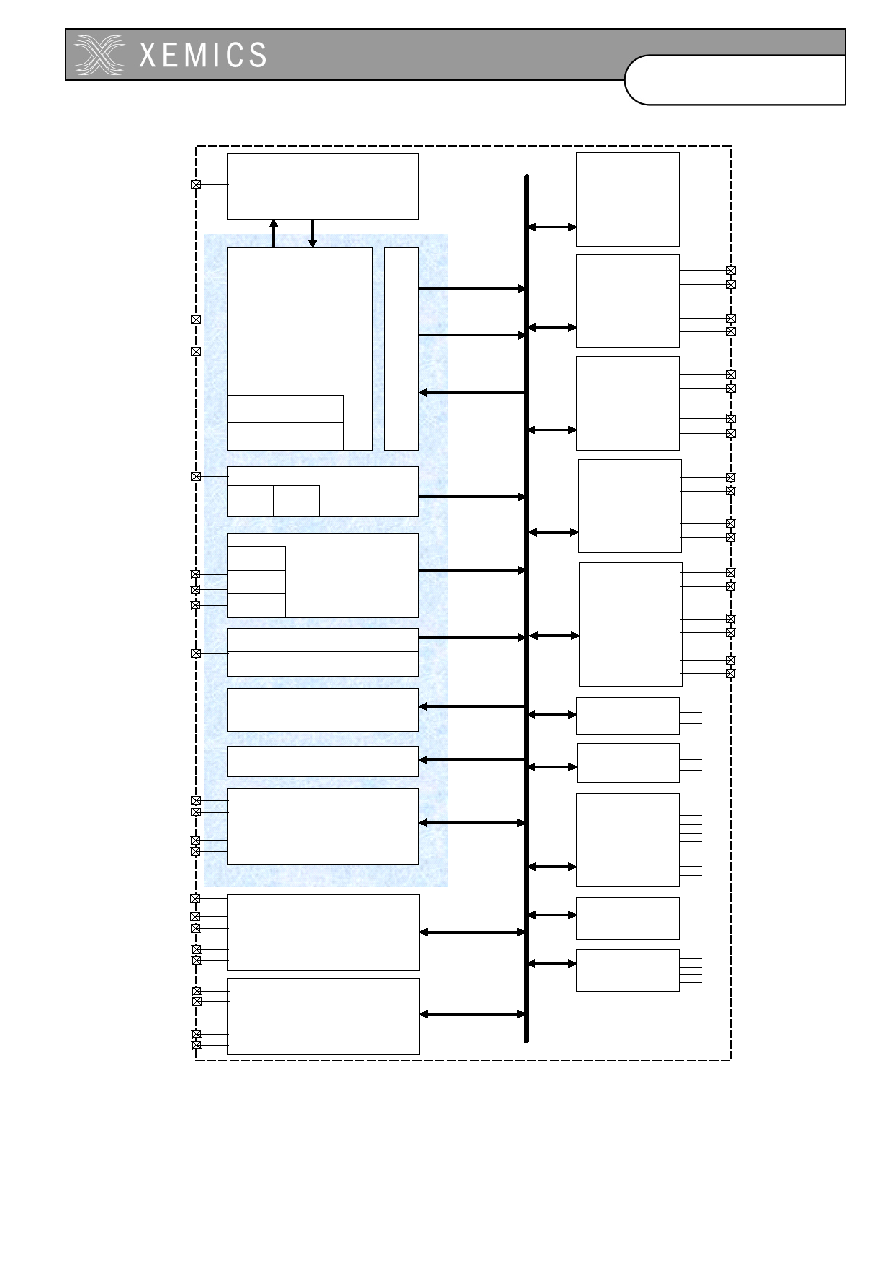

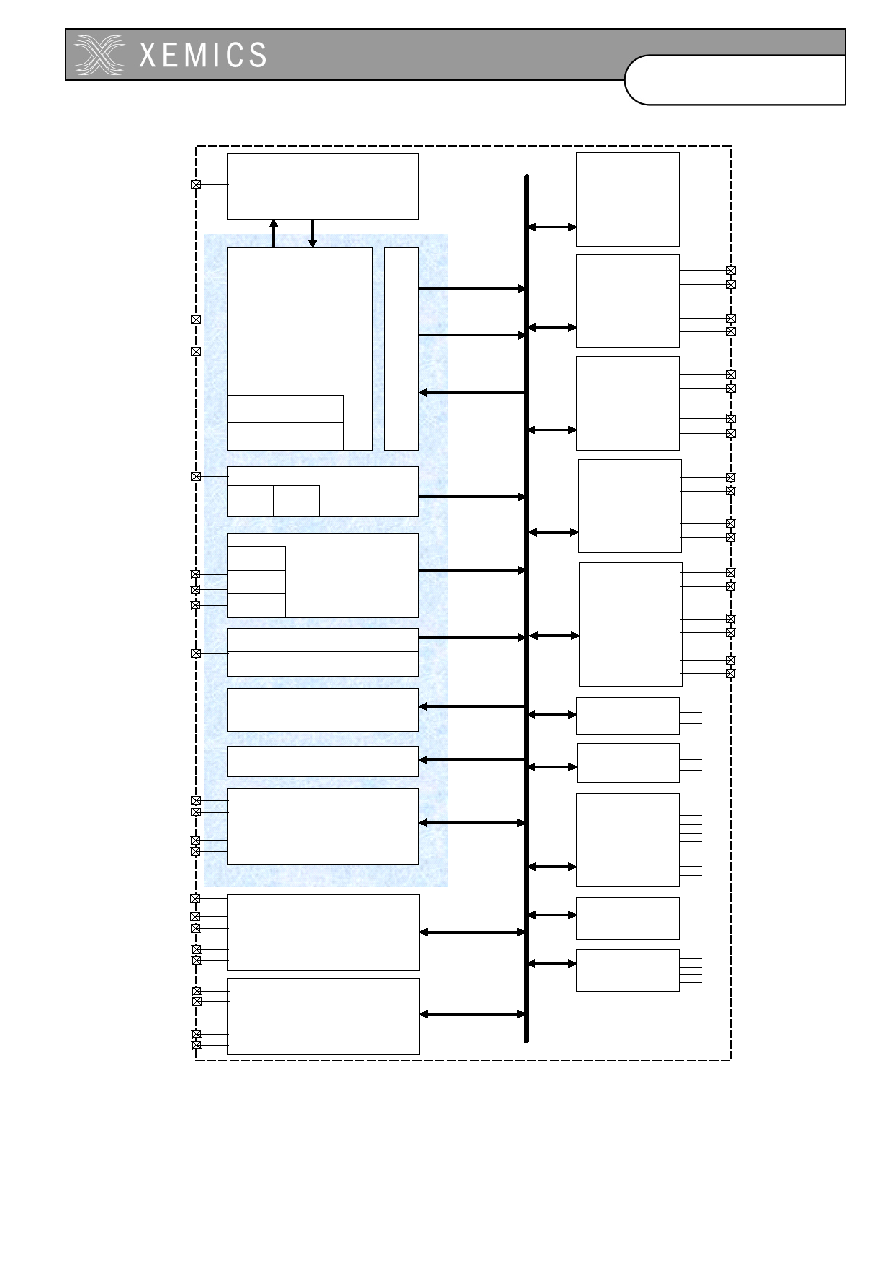

1.1 Top schematic

The top-level block schematic of the circuit is shown in Figure 1-1. The heart of the circuit consists of

the Coolrisc816 CPU core. This core includes an 8x8 multiplier and 16 internal registers.

The bus controller generates all control signals for access to all data registers other than the CPU

internal registers.

The reset block generates the adequate reset signals for the rest of the circuit as a function of the set-

up contained in its control registers. Possible reset sources are the power-on-reset (POR), the

external pin NRESET, the watchdog (WD), a bus error detected by the bus controller or a

programmable pattern on Port A. Different low power modes are implemented.

The clock generation and power management block sets up the clock signals and generates internal

supplies for different blocks. The clock can be generated from the RC oscillator (this is the start-up

condition), the crystal oscillator (XTAL) or an external clock source (given on the XIN pin).

The test controller generates all set-up signals for different test modes. In normal operation, it is used

as a set of 8 low power data registers. If power consumption is important for the application, the

variables that need to be accessed frequently should be stored in these registers rather than in the

RAM.

The IRQ handler routes the interrupt signals of the different peripherals to the IRQ inputs of the CPU

core. It allows masking of the interrupt sources and it flags which interrupt source is active.

Events are generally used to restart the processor after a HALT period without jumping to a specified

address, i.e. the program execution resumes with the instruction following the HALT instruction. The

EVN handler routes the event signals of the different peripherals to the EVN inputs of the CPU core. It

allows masking of the interrupt sources and it flags which interrupt source is active.

The Port B is an 8 bit parallel IO port with analog capabilities. The URST, UART, PWM and CMPD

block also make use of this port.

The instruction memory is a 22-bit wide flash or ROM memory depending on the circuit version. In

case of the ROM version, the VPP pin is not used. Flash and ROM versions have both 8k instruction

memory.

The data memory on this product is a 1024 byte SRAM.

The Acquisition Chain is a high-resolution acquisition path with the 16+10 bits ZoomingADC

. The

VMULT (voltage multiplier) powers a part of the Acquisition Chain.

The SPI is a serial interface with a master or slave configuration capability. When unused, the 4 SPI

pads can be used as 4-bit wide general-purpose I/O port.

The port A is an 8 bit parallel input port. It can also generate interrupts, events or a reset. It can be

used to input external clocks for the timer/counter/PWM block.

The Port D1 and the Port D2 are two general-purpose 8 bit parallel I/O ports.

The LCD driver can support a direct drive display (up to 32 segments), or multiplex 1/2, 1/3, 1/4

displays (up to 120 segments). The driver contains an on chip low-power voltage generation device

VGEN. The LCD lines can be used as additional I/O pins.

The USRT (universal synchronous receiver/transmitter) contains some simple hardware functions in

order to simplify the software implementation of a synchronous serial link.

1-3

D0309-134

Datasheet XE88LC02 Sensing

Machine Data Acquisition MCU

with Zooming ADC and LCD driver

INSTRUCTION MEMORY

B

U

S

C

O

N

T

R

O

L

L

E

R

TEST

CONTROLLER

RESET

BLOCK

WD

CLOCK

GENERATION/

POWER

MANAGEMENT

VREG

XTAL

RC

CPU

COOLRISC816

8

X

8

MULTIPLIER

16

CPU

REGISTERS

IRQ HANDLING

EVN HANDLING

PORT B

8 DATA REGISTERS

PORT A

USRT

PORT D1

address

control

datain

dataout

reset

control

clocks

test

control

irq

evn

VPP

VBAT

VSS

NRESET

XIN

XOUT

VREG

TEST

PB(7:0)

VMULT

AC_R(3:0)

AC_A(7:0)

SPI(3:0)

PA(7:0)

PD1(7:0)

PD2(7:0)

LCD_IO(31:0)

LCD_COM(1:0)

VGEN_Vx(4:0)

DATA

MEMORY

UART

COUNTERS

TIMERS

PWM

VLD

CMPD

PB(5:

4

)

P

B

(7

:

6

)

PA

(3

:

0

)

PB

(1

:0

)

PB(7:

4

)

POR

PORT D2

ACQUISITION CHAIN

VMULT

(ZoomingADC)

LCD Driver

VGEN

SPI

Figure 1-1. Block schematic of the XE88LC02 circuit.