| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: 65-0211 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

SVC/SVC-64

Speaker Verification Controller

DATA SHEET

© 2003 Sensory Inc.

P/N 80-0252-A

1

General Description

The SVC/SVC-64, from the Interactive Speech

TM

family of products, is designed specifically for

biometric password applications in consumer

electronic products.

The SVC/SVC-64 combines an 8-bit processor with

Sensory's new Voice LockTM text-dependent

speaker verification algorithms to provide high-

quality password biometrics. The chip also

supports speech synthesis and application system

control. This CMOS device includes on-chip

microphone pre-amplifier, analog-to-digital and

digital-to-analog converters, RAM, 16 general-

purpose I/O lines, a 4-MIPS dedicated processor

and optional 64K on-chip ROM (SVC-64). The SVC

has no on-chip ROM and is designed for cost

savings in off-chip ROM applications.

In addition to providing the horsepower needed to

perform speaker verification and speech synthesis,

the processor has sufficient cycles available for

general-purpose application control. The

SVC/SVC-64 Development Kit allows developers to

create custom applications. The Development Kit

includes an assembler, linker, simulator, hardware

development platform, and Voice LockTM

Technology library of object code.

The highly integrated nature of this chip reduces

external parts count. A complete system may be

built with only a few passive components in addition

to a battery, speaker, and microphone. Low power

requirements and low-voltage operation make the

SVC/SVC-64 an ideal solution for battery-powered

and hand-held devices.

Voice LockTM Technology uses word-spotting

techniques to perform noise-robust, text-dependent

speaker verification for password biometrics, while

high-quality speech synthesis is achieved using a

time-domain compression scheme that improves on

conventional ADPCM. Automatic Gain Control can

compensate for people not optimally positioned with

respect to the microphone or for people who speak

too softly or loudly when saying their password.

Features

Voice LockTM Speaker Verification and Synthesis

New noise-robust, text-dependent speaker

verification technology

Synthesis data rates from 5,000-33,000 bits

per second - useful for guiding training and

using passwords, reducing the need for

users manual, etc.

Highly-Integrated Single-Chip Solution

Can store 6 speaker verification words on-

chip

4-MIPS performance at 14.32 MHz

Internal 64 KBytes of ROM (SVC-64 only)

2.5 KBytes of RAM

Audio ADC (analog to digital converter)

Microphone pre-amplifier and AGC

Audio DAC (digital to analog converter) and

PWM for high quality and low cost speech

Interrupts, timers and counters

16 configurable, general purpose I/O lines

Separate 16-bit address and 8-bit data buses

- compatible with common memory

components

Separate code and data address spaces and

memory strobes

Fully static operation; clock rate: DC to 14.32

MHz

Low Power Requirements

Requires single 2.85V to 5.25V power supply

~10mA operating current at 3V

Low power 32kHz oscillator

Power-down current less than 5

µA

Full Suite of Development Tools

Assembler/Linker & Simulator

Sensory technology library

Hardware development platform

Quick Synthesis Tool for push-button

synthesis compression

SVC/SVC-64

Data Sheet

2

P/N 80-0252-A

© 2003 Sensory Inc.

Table of Contents

General Description................................................................................................................................................. 1

Features .................................................................................................................................................................. 1

Table of Contents .................................................................................................................................................... 2

Introduction.............................................................................................................................................................. 3

SVC/SVC-64 Hardware Specifications ................................................................................................................... 4

Using the SVC/SVC-64 ........................................................................................................................................... 5

Memory Organization .............................................................................................................................................. 6

Memory Map............................................................................................................................................................ 7

General Purpose I/O ............................................................................................................................................... 8

Interrupts ................................................................................................................................................................. 8

Reset and Clocks .................................................................................................................................................... 9

Timers and Counters............................................................................................................................................. 10

Power Down and Wake-Up Operation .................................................................................................................. 10

Analog Outputs...................................................................................................................................................... 11

Hardware Debug Features .................................................................................................................................... 11

Design Considerations .......................................................................................................................................... 12

Omni-Directional Microphone................................................................................................................................ 13

Power Consumption and Power Supply Considerations ...................................................................................... 15

Die Bond Pad and QFP Pin Descriptions.............................................................................................................. 16

Die Pad Ring ......................................................................................................................................................... 17

SVC/SVC-64 Die Bonding Pad Locations............................................................................................................. 18

Absolute Maximum Ratings................................................................................................................................... 19

D.C. Characteristics ............................................................................................................................................. 19

Vdd vs. Idd............................................................................................................................................................ 19

A.C. Characteristics (External Memory Accesses) .............................................................................................. 20

Timing Diagrams ................................................................................................................................................... 20

SVC/SVC-64 Instruction Set ................................................................................................................................. 21

SVC/SVC-64 Special Function Register (SFR) Summary .................................................................................... 23

Quality and Reliability............................................................................................................................................ 37

Packaging.............................................................................................................................................................. 38

Ordering Information ............................................................................................................................................. 39

The Interactive SpeechTM Product Line ................................................................................................................ 40

Data Sheet

SVC/SVC-64

© 2003 Sensory Inc.

P/N 80-0252-A

3

Introduction

The SVC/SVC-64 is the newest member in a family of high-performance 8-bit microprocessors featuring a high

level of integration targeted to high-accuracy, low-cost speech recognition applications. The SVC/SVC-64 and

associated Voice LockTM Technology are designed to bring high quality, text-dependent speaker verification

password solutions and system design versatility to low-cost, power-sensitive consumer applications.

A design goal of the SVC/SVC-64 was to reduce the total system cost of integrating password biometrics in a

wide variety of applications. The SVC/SVC-64 can store up to 6 passwords in on-chip RAM (and many more in

off-chip memory) Dramatic cost and power reduction are achieved by including microphone signal amplification,

data conversion, speaker verification and synthesis functionality, speech playback, RAM and ROM storage

(SVC-64 only) with a CPU core on a single chip. This allows customer applications to achieve maximum

password security at minimum cost.

The CPU core embedded in the SVC/SVC-64 is an 8-bit, variable-length-instruction microprocessor. The

instruction set is most similar to the 8051 family of microcontrollers. The SVC/SVC-64 processor avoids the

limitations of dedicated registers by having completely symmetrical source and destinations for all instructions.

Of the 2.5 Kbytes of internal SRAM, 2 Kbytes are organized as a Data Space, and 0.5 Kbytes is for register

space. All arithmetic operation instructions may be applied to any register. Any pair of adjacent registers (at an

even address) may be used as the 16-bit pointer to either the source or destination for a data movement

instruction. Instruction classes allow the pointer to access internal or external Code Space, internal Register

Space, or external Data Space.

Architecturally, the SVC/SVC-64's separate data and address buses allow use of standard EPROMs, ROMs,

and SRAMs with little or no additional decoding. A provision for separate read and write signals for each

external memory space further simplifies interfacing.

Creating applications using the SVC/SVC-64 requires the development of electronic circuitry, software code,

and speech files. This document provides detailed information on those aspects of the SVC/SVC-64

architecture that are important to product designers and programmers. It describes the physical interface to the

chip, printed circuit board layout and other design considerations, the SVC/SVC-64's instruction set, and

memory organization. Refer to the SVC/SVC-64 Development Kit Manual for information on using Sensory's

Voice LockTM Technology code for speaker verification and speech synthesis. Refer to the Quick Synthesis

Manual for information on using Sensory's "push-button" synthesis compression technology.

Sensory offers and encourages free application design reviews by our Technical Support Group to ensure

success.

Custom Mask Capabilities of the SVC-64

The SVC provides significant and flexible expansion capabilities through the use of external RAM or ROM.

Products using the custom-mask version of the chip, the SVC-64, may save considerable per-unit cost by

avoiding the need for other active devices. Either the SVC or the SVC-64 may use on-chip RAM to store up to

6 passwords, or use EEPROM, Flash or RAM to store many more passwords off-chip. The SVC requires an

external Code Space ROM memory to contain the program instructions and synthesis data. The custom-

masked SVC-64, with no additional external memory devices, relies on the fixed internal memory for all of its

ROM and RAM requirements. The internal ROM in the SVC-64 is application specific, occupied by a

combination of user application code, speaker verification technology code and synthesis files.

The finite resources of the SVC-64 require careful crafting of the end product application. Sensory's Technical

& Service Support Groups are ready to consult with application developers to maximize the end product's

effectiveness for password biometric security functions. Sensory offers and encourages free application design

reviews by our Technical Support Group to ensure success.

SVC/SVC-64

Data Sheet

4

P/N 80-0252-A

© 2003 Sensory Inc.

SVC/SVC-64 Hardware Specifications

Architectural Overview of the

SVC/SVC-64

The SVC/SVC-64 is a highly integrated device

that combines:

∑ An 8-bit RISC microprocessor.

∑ On-chip ROM (64 KBytes, SVC-64 only),

Register RAM (448 bytes), Data RAM (2

KBytes) and the ability to address off-chip

RAM or ROM.

∑ Analog-to-digital converter, digital-to-

analog converter, and a pulse width

modulator.

∑ A microphone pre-amplifier

The SVC/SVC-64 has an external memory

interface for accessing external RAMs, ROMs

or other parallel memory devices. The SVC-

64 also has an internal ROM that can be

enabled or disabled (partially or fully) by pin

inputs (signals -XMH, -XML; See figure 4). ).

When the internal ROM of the SVC-64 is

disabled, its performance is identical to the

SVC. With the SVC-64, the entire program

must reside in the internal masked ROM.

External memory can only be used to store

data.

The 8-bit processor can directly access 448

on-chip general-purpose registers (RAM), and

32 additional Special Functions Registers

(SFRs). The instruction set accessing these registers is completely symmetrical, allowing movs, arithmetic, and

logical operations with any register as the destination. Two bi-directional ports provide 16 general-purpose I/O

pins to communicate with external devices (See page 8). The SVC/SVC-64 has a high frequency (14.32 MHz)

oscillator as well as a low frequency (32,768 Hz) oscillator. The processor clock can be selected from either

source using a selectable divider value. Sensory's technology code requires the use of the 14.32 MHz clock.

There are two programmable 8-bit counters / timers, one derived from each oscillator. A variety of wait state

configurations allow fast code execution and easy interfacing to slow peripheral memories.

An inexpensive electret microphone connects directly to the microphone input of the SVC/SVC-64. The internal

preamplifier converts the tiny microphone signal to a level suitable for analog-to-digital conversion. (ADC), The

SVC/SVC-64 uses a Sample and Hold (SH) circuit and ADC converter to convert the amplified analog speech

signal into digital data. The chip may also be used with line-level inputs. The output audio signal of the

SVC/SVC-64 is derived either from a digital-to-analog converter (DAC) or a PWM (Pulse Width Modulator).

In addition to its on-chip ROM (SVC-64 only) and RAM, the SVC/SVC-64 has 8 data lines (D[7:0]) and 16

address lines (A[15:0]), along with associated control signals (-RDC, -RDD, -WRC, -WRD, -XML, -XMH) for

interfacing to external memory. The memory control signals on the SVC/SVC-64 and the processor instruction

set provide independent Code and Data spaces, allowing configuration of systems up to 192 Kbytes with no

additional hardware decoding. The SVC/SVC-64 features 16 general-purpose I/O pins (P0 & P1) for product

and memory bank control.

PRE-AMP

EXTERNAL

MEMORY

INTERFACE

CPU

TIMING AND

CONTROL

32K x 8

32K x 8

HIGH

LOW

INTERNAL ROM (SVC-64)

A[15:0]

D[7:0]

-RDC

-WRD

-RDD

-WRC

448 bytes

8 levels

-XMH

-XML

-RESET

-TE1/

PWM

STACK SPACE

REGISTER SPACE

BREAK POINT

REGISTER

AiFE1

ANALOG

CONTROL

ADC

TIMER1

TIMER2

OSC1

OSC2

PO

RT

0

I

N

T

E

RRUP

T

LO

G

I

C

DACOUT

XI1, XO1

XI2, XO2

P0.0-P0.7

P1.0-P1.7

DAC

PULSE

WIDTH

MODULATOR

PO

RT

1

AOFE3

AiN1

AOFE2

AOFE1

AiNÿ

AiFE2

PWM

BUFOUT/

FEATURE

EXTRACTION

UNIT

2K TECHNOLOGY

SRAM

Figure 1 ≠ SVC-64 Block Diagram

Data Sheet

SVC/SVC-64

© 2003 Sensory Inc.

P/N 80-0252-A

5

Using the SVC/SVC-64

Creating applications using the SVC/SVC-64 requires the development of electronic circuitry, software code,

and speech data files. Software code for the SVC/SVC-64 can be developed by Sensory or by external

programmers using the SVC/SVC-64 Development Kit. Speech data files can be created by the developer with

Sensory's Quick Synthesis tool, or by Sensory's Services Group in cases where synthesis with very low data

rates are required. For more information about development tools and services, please contact Sensory, or visit

www.SensoryInc.com. A typical product will require about $0.30 - $1.00 (in high volume) of additional

components, in addition to the SVC/SVC-64.

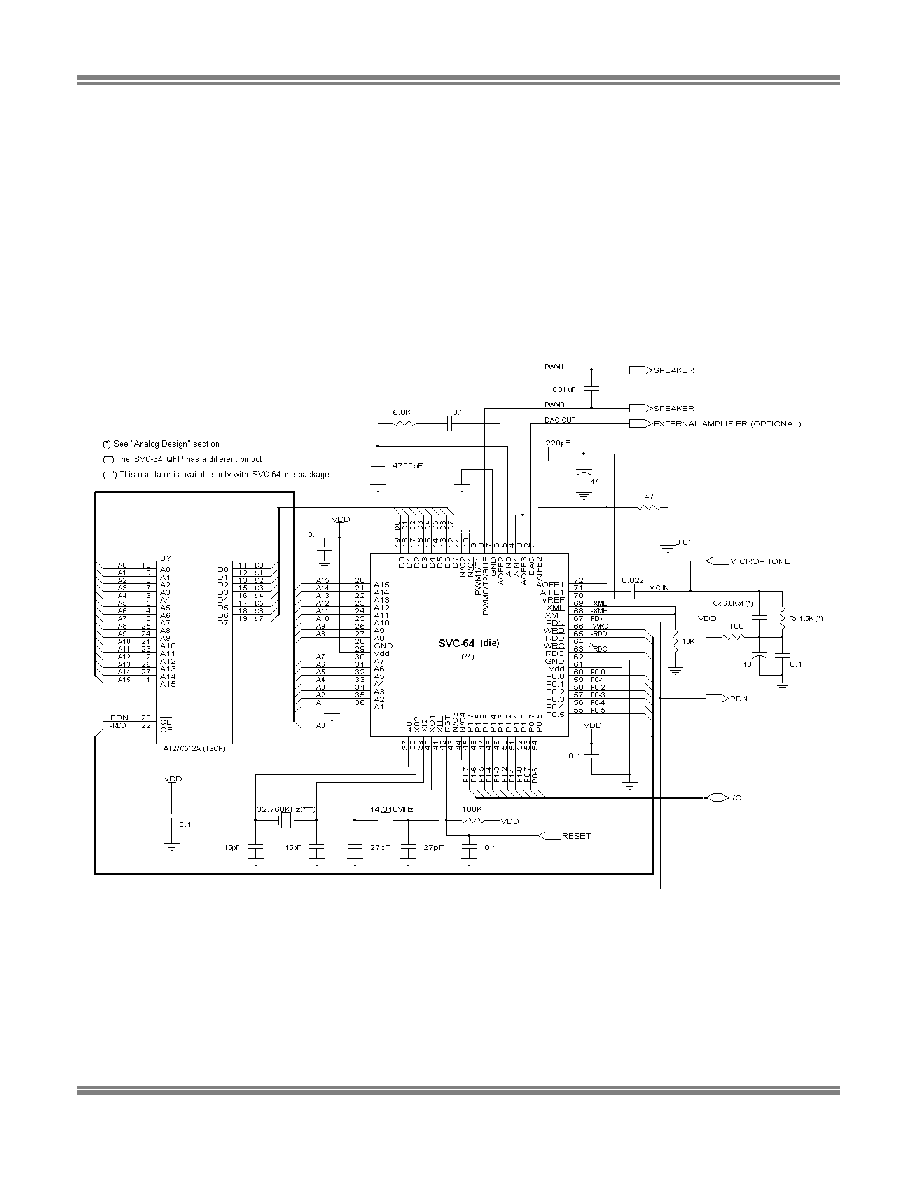

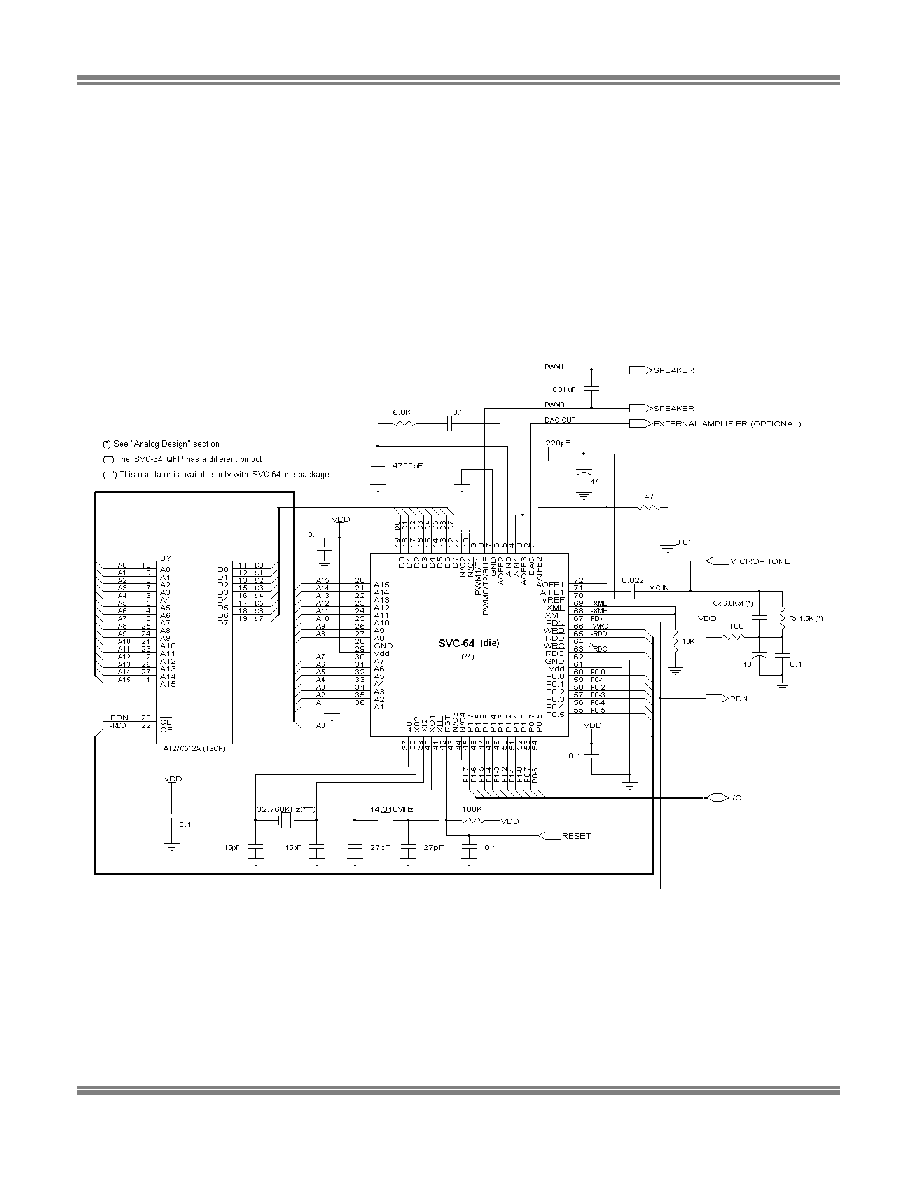

The following sample circuit provides an example of how the SVC might be used in a consumer electronic

product. The external ROM contains the application program and speech data. An application using the SVC-

64 (custom-masked ROM) would not require the separate ROM.

Figure 2 ≠ Reference Circuit

Note: Applications using the PWM output may not meet FCC or CE (such as EN55022 Class A or B) standards for radiated emissions. For

applications that must meet these standards, Sensory recommends turning off the PWM in the application software, and using an external

audio power amplifier connected to the DAC output. Please refer to Sensory's Application Note 80-0105 "DAC Output" for sample circuits

and design guidelines.