| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: LH530800A | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

LH530800A

CMOS 1M (128K

◊

8) MROM

FEATURES

∑∑

131,072 words

◊

8 bit organization

∑∑

Access time: 150 ns (MAX.)

∑∑

Power consumption:

Operating: 192.5 mW (MAX.)

Standby: 550

µ

W (MAX.)

∑∑

Static operation

∑∑

TTL compatible I/O

∑∑

Three-state outputs

∑∑

Single +5 V power supply

∑∑

Packages:

32-pin, 600-mil DIP

32-pin, 525-mil SOP

32-pin, 450-mil QFJ (PLCC)

∑∑

JEDEC standard EPROM pinout (DIP)

DESCRIPTION

The LH530800A is a mask-programmable ROM

organized as 131,072

◊

8 bits (1,048,576 bits). It is fab-

ricated using silicon-gate CMOS process technology.

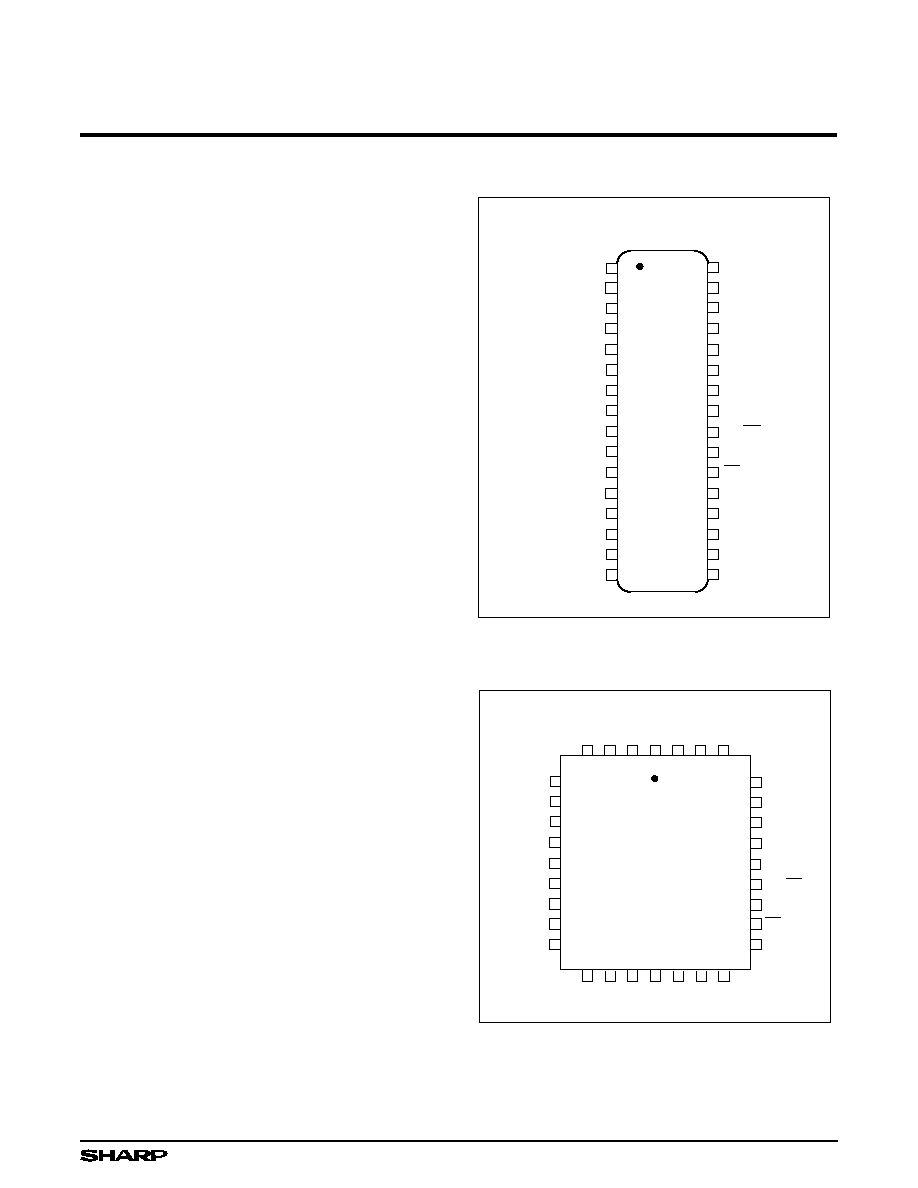

PIN CONNECTIONS

530800A-1

TOP VIEW

1

2

3

4

5

6

9

10

A

2

A

5

Vcc

28

27

26

25

24

23

20

17

A

7

A

6

7

8

A

3

A

4

22

21

A

15

A

12

GND

A

13

A

8

A

11

A

10

CE

D

7

D

6

D

3

11

12

13

32

31

30

29

NC

A

14

A

1

NC

14

15

16

19

D

5

18

D

4

D

1

D

2

A

0

D

0

A

9

A

16

OE/OE

NC

32-PIN DIP

32-PIN SOP

Figure 1. Pin Connections for DIP and

SOP Packages

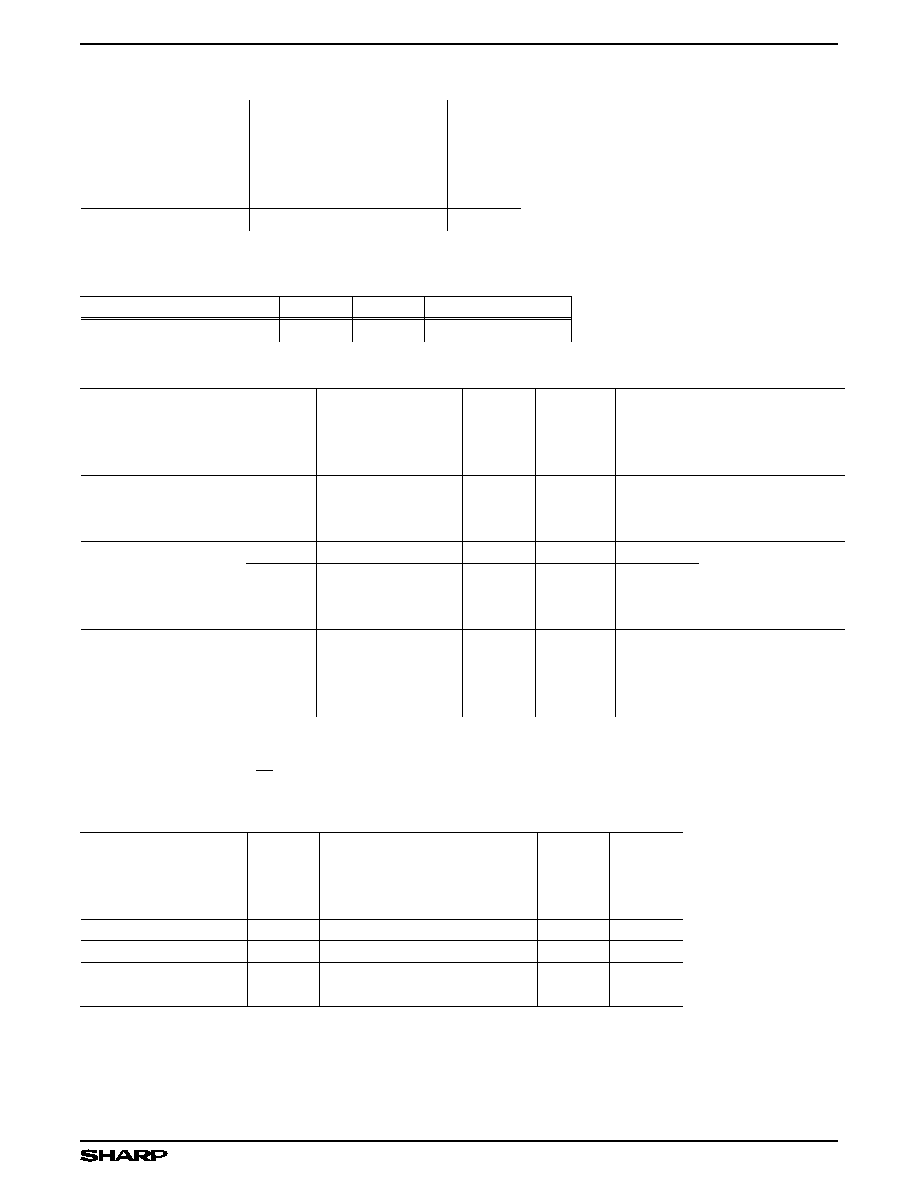

5

6

7

8

9

10

11

A

7

A

6

A

5

A

2

A

1

29

28

27

26

25

24

A

14

A

13

A

8

A

9

OE/OE

A

10

21

14 15 16

20

19

18

17

12

13

A

0

D

0

22

CE

D

7

23

D

1

1

2

3

4

32 31 30

A

12

A

15

A

16

NC

V

CC

NC

NC

32-PIN QFJ

TOP VIEW

530800A-7

A

4

A

3

A

11

D

2

GND

D

3

D

4

D

5

D

6

Figure 2. Pin Connections for QFJ

(PLCC) Package

1

NOTE:

1.

Active level of OE/OE is mask-programmable.

TRUTH TABLE

CE

OE/OE

MODE

D

0

- D

7

SUPPLY CURRENT

NOTE

H

X

Non selected

High-Z

Standby (I

SB

)

1

L

L/H

Non selected

High-Z

Operating (I

CC

)

L

H/L

Selected

D

OUT

Operating (I

CC

)

NOTE:

1.

X = H or L.

530800A-2

A

3

A

2

A

1

A

12

A

11

A

10

A

9

A

8

32

4

25

23

26

6

9

10

11

A

7

A

6

V

CC

A

4

18

19

20

13

21

D

0

MEMORY

MATRIX

(131,072 x 8)

SENSE AMPLIFIER

16

5

GND

D

1

D

2

D

3

D

4

D

5

D

6

D

7

24

17

14

15

8

27

A

5

7

A

13

28

OE/OE

ADDRESS BUFFER

CE

A

0

12

ADDRESS DECODER

COLUMN SELECTOR

CE

BUFFER

OE

BUFFER

A

14

29

A

15

3

22

TIMING

GENERATOR

A

16

2

OUTPUT BUFFER

Figure 3. LH530800A Block Diagram

PIN DESCRIPTION

SIGNAL

PIN NAME

NOTE

A

0

- A

16

Address input

D

0

- D

7

Data Output

CE

Chip enable input

1

OE/OE

Output enable input

1

SIGNAL

PIN NAME

NOTE

V

CC

Power supply (+5 V)

GND

Ground

NC

No connection

LH530800A

CMOS 1M Mask-Programmable ROM

2

ABSOLUTE MAXIMUM RATINGS

PARAMETER

SYMBOL

RATING

UNIT

Supply voltage

V

CC

≠0.3 to +7.0

V

Input voltage

V

IN

≠0.3 to V

CC

+0.3

V

Output voltage

V

OUT

≠0.3 to V

CC

+0.3

V

Operating temperature

Topr

0 to +70

∞

C

Storage temperature

Tstg

≠65 to +150

∞

C

RECOMMENDED OPERATING CONDI-

TIONS (T

A

= 0 to +70

∞

C)

PARAMETER

SYMBOL

MIN.

TYP.

MAX.

UNIT

Supply voltage

V

CC

4.5

5.0

5.5

V

DC CHARACTERISTICS (V

CC

= 5 V

±

10%, T

A

= 0 to +70

∞

C)

PARAMETER

SYMBOL

CONDITIONS

MIN.

TYP.

MAX.

UNIT

NOTE

Input `Low' voltage

V

IL

≠0.3

0.8

V

Input `High' voltage

V

IH

2.2

V

CC

+ 0.3

V

Output `Low' voltage

V

OL

I

OL

= 2.0 mA

0.4

V

Output `High' voltage

V

OH

I

OH

= ≠400

µ

A

2.4

V

Input leakage current

| I

LI

|

V

IN

= 0 V to V

CC

10

µ

A

Output leakage current

| I

LO

|

V

OUT

= 0 V to V

CC

10

µ

A

1

Operating current

I

CC1

t

RC

= 150 ns

35

mA

2

I

CC2

t

RC

= 1

µ

s

25

I

CC3

t

RC

= 150 ns

30

mA

3

I

CC4

t

RC

= 1

µ

s

20

Standby current

I

SB1

CE = V

IH

2

mA

I

SB2

CE = V

CC

- 0.2 V

100

µ

A

Input capacitance

C

IN

f = 1 MHz

T

A

= 25

∞

C

10

pF

Output capacitance

C

OUT

10

pF

NOTES:

1.

CE/OE = V

IH

or OE = V

IL

2.

V

IN

= V

IH

or V

IL

, CE = V

IL

, outputs open

3.

V

IN

= (V

CC

- 0.2 V) or 0.2 V, CE = 0.2 V, outputs open

AC CHARACTERISTICS (V

CC

= 5 V

±

10%, T

A

= 0 to +70

∞

C)

PARAMETER

SYMBOL

MIN.

TYP.

MAX.

UNIT

NOTE

Read cycle time

t

RC

150

ns

Address access time

t

AA

150

ns

Chip enable time

t

ACE

150

ns

Output enable time

t

OE

70

ns

Output hold time

t

OH

5

ns

CE to output in High-Z

t

CHZ

70

ns

1

OE to output in High-Z

t

OHZ

70

ns

NOTE:

1.

This is the time required for the output to become high-imped-

ance.

CMOS 1M Mask-Programmable ROM

LH530800A

3

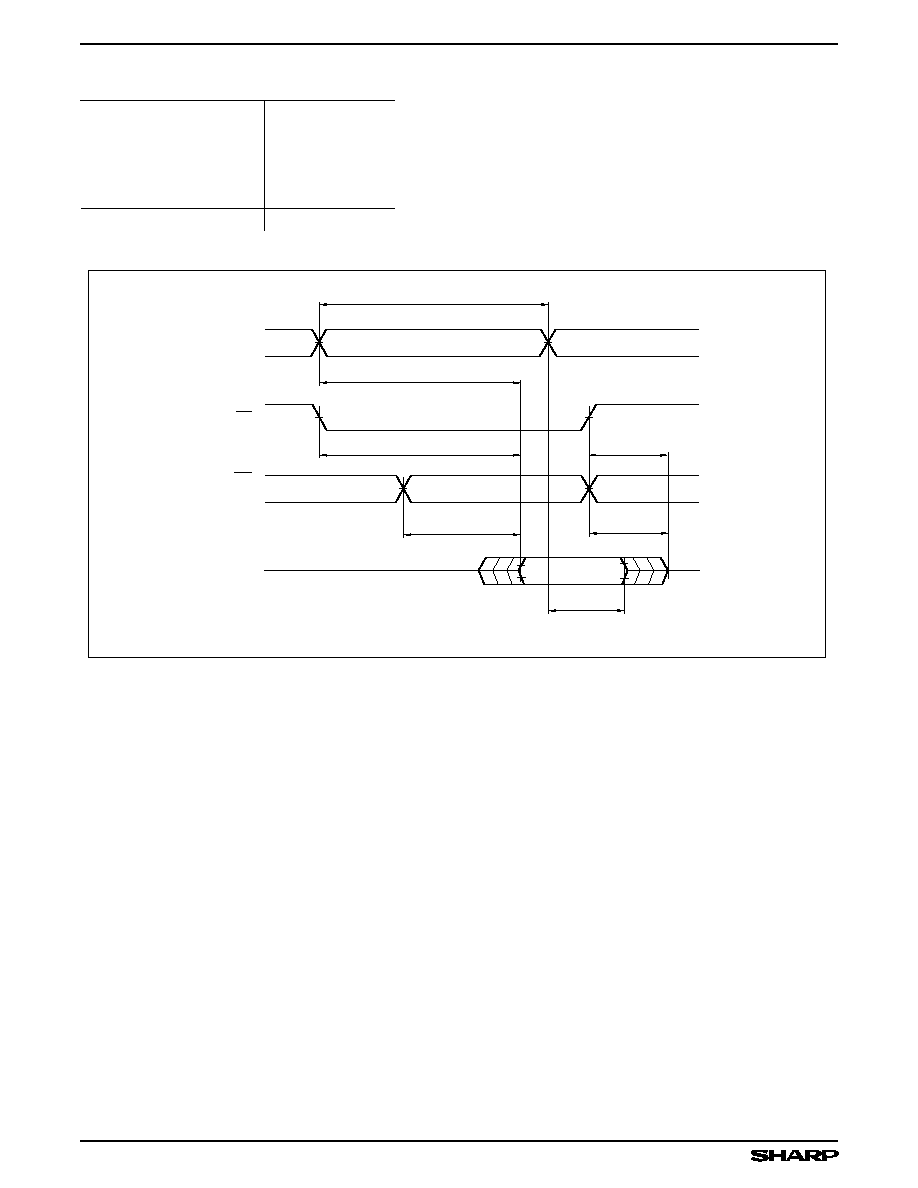

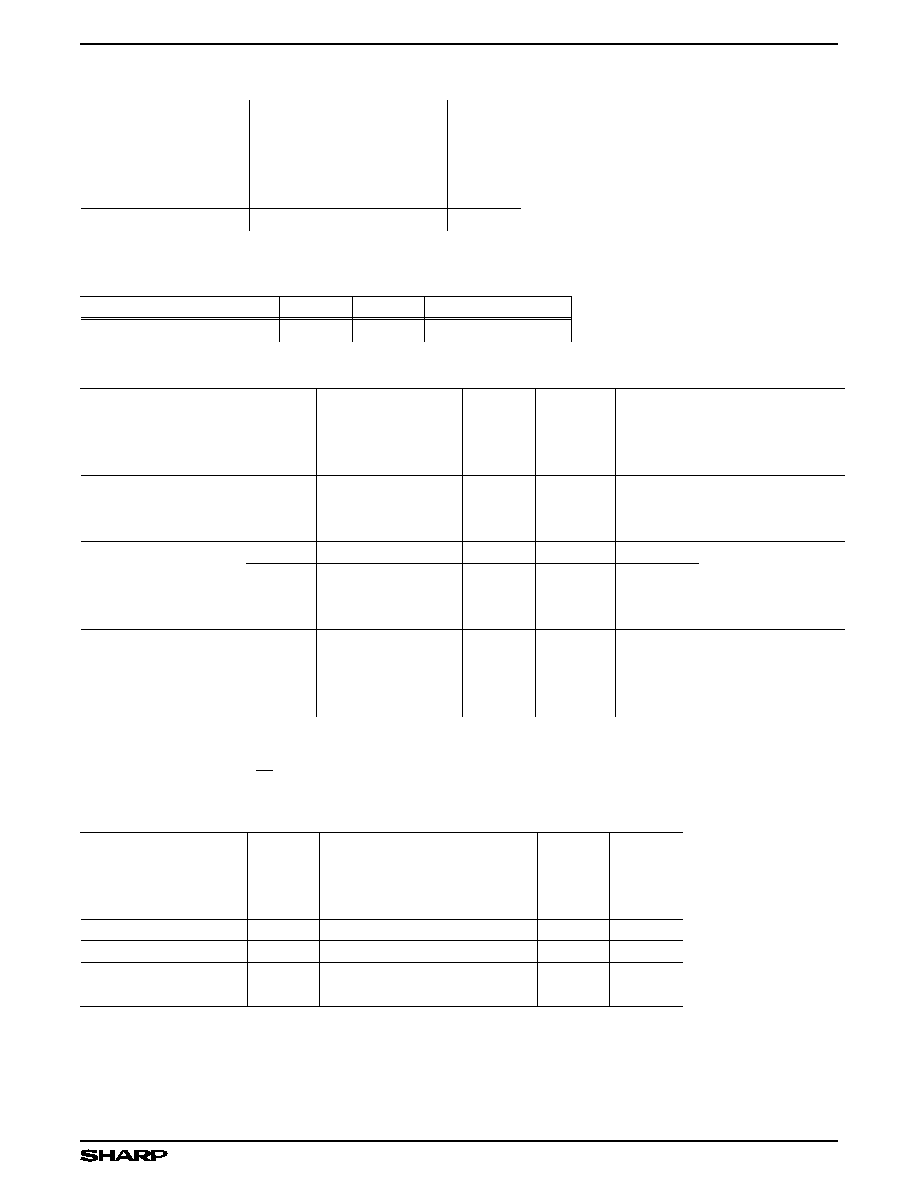

AC TEST CONDITIONS

PARAMETER

RATING

Input voltage amplitude

0.6 V to 2.4 V

Input rise/fall time

10 ns

Input reference level

1.5 V

Output reference level

0.8 V and 2.2 V

Output load condition

1TTL +100 pF

t

OE

(NOTE)

t

AA

A

0

- A

16

t

OHZ

t

CHZ

D

0

- D

7

530800A-3

t

RC

t

ACE

CE

OE

t

OH

DATA VALID

(NOTE)

(NOTE)

OE

NOTE: Data becomes valid after t

AA

, t

ACE

, and t

OE

from address

input, chip enable and output enable, respectively have been met.

Figure 4. Timing Diagram

LH530800A

CMOS 1M Mask-Programmable ROM

4

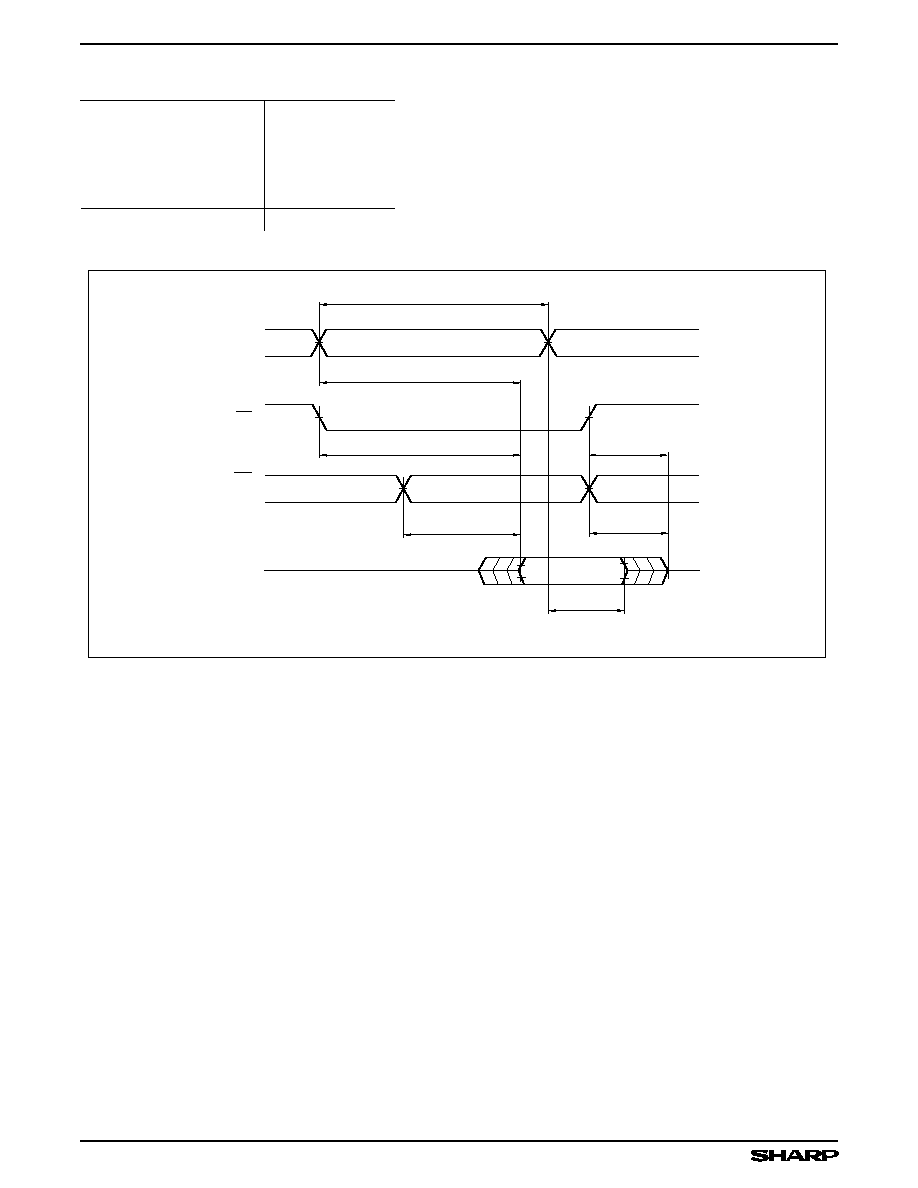

PACKAGE DIAGRAMS

13.45 [0.530]

12.95 [0.510]

0.51 [0.020] MIN.

5.20 [0.205]

5.00 [0.197]

3.50 [0.138]

3.00 [0.118]

2.54 [0.100]

TYP.

0.60 [0.024]

0.40 [0.016]

0.30 [0.012]

0.20 [0.008]

DETAIL

DIMENSIONS IN MM [INCHES]

41.30 [1.626]

40.70 [1.602]

0

∞

TO 15

∞

MAXIMUM LIMIT

MINIMUM LIMIT

4.50 [0.177]

4.00 [0.157]

15.24 [0.600]

TYP.

32DIP (DIP032-P-0600)

1

16

17

32

32DIP

32-pin, 600-mil DIP

DIMENSIONS IN MM [INCHES]

MAXIMUM LIMIT

MINIMUM LIMIT

32SOP (SOP032-P-0525)

14.50 [0.571]

13.70 [0.539]

11.50 [0.453]

11.10 [0.437]

12.50 [0.492]

20.80 [0.819]

20.40 [0.803]

0.15 [0.006]

1.275 [0.050]

0.20 [0.008]

0.00 [0.000]

1.275 [0.050]

2.90 [0.114]

2.50 [0.098]

0.20 [0.008]

0.10 [0.004]

0.50 [0.020]

0.30 [0.012]

1.27 [0.050]

TYP.

32

17

16

1

1.40 [0.055]

1.40 [0.055]

32SOP

32-pin, 525-mil SOP

CMOS 1M Mask-Programmable ROM

LH530800A

5