| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: SP6120B | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

1

Date: 5/25/04

SP6120B Low Voltage, AnyFET

TM

, Synchronous, Buck Controller © Copyright 2004 Sipex Corporation

SP6120B

Optimized for Single Supply, 3V - 5.5V Applications

High Efficiency: Greater Than 95% Possible

"AnyFET

TM"

Technology: Capable Of Switching Either

PFET Or NFET High Side Switch

Selectable Discontinuous or Continuous Conduction

Mode

Fast Transient Response from Window Comparator

16-Pin TSSOP, Small Size

Accurate 1% Reference Over Line, Load and Temperature

Accurate 10% Frequency

Accurate, Rail to Rail, 43mV, Over-Current Sensing

Resistor Programmable Frequency

Resistor Programmable Output Voltage

Low Quiescent Current: 950µA, 10µA in Shutdown

Hiccup Over-Current Protection

Capacitor Programmable Soft Start

Guaranteed Boost Voltage to Enhance High Side NFET

Low Voltage, AnyFET

TM

, Synchronous ,Buck Controller

Ideal for 2A to 10A, High Performance, DC-DC Power Converters

APPLICATIONS

DSP

Microprocessor Core

I/O & Logic

Industrial Control

Distributed Power

Low Voltage Power

DESCRIPTION

The SP6120B is a fixed frequency, voltage mode, synchronous PWM controller designed to

work from a single 5V or 3.3V input supply. Sipex's unique "AnyFET

TM"

Technology allows

the SP6120B to be used for resolving a multitude of price/performance trade-offs. It is

separated from the PWM controller market by being the first controller to offer precision,

speed, flexibility, protection and efficiency over a wide range of operating conditions.

Æ

SP6120B

NC

ENABLE

ISP

ISN

V

FB

COMP

SS

R

OSC

BST

GH

SWN

GND

PGND

GL

V

CC

PROG

Æ

Æ

NMOS High Side Drive

PROG = GND

ENABLE

CP

100pF

CZ

4.7nF

RZ

15k

C

SS

0.33µF

R

OSC

18.7k

CV

CC

2.2µF

V

IN

MBR0530

C

BST

1µF

QT

3.3V

V

IN

C

IN

330µF x 2

RS

22.1k

CS

39nF

L1

2.5µH

1.9V

1A to 8A

V

OUT

RF

5.23k

C

OUT

470µF x 3

RI

10k

QB

DS

C

B

1µF

SP6120B

NC

ENABLE

ISP

ISN

V

FB

COMP

SS

R

OSC

BST

GH

SWN

GND

PGND

GL

V

CC

PROG

Æ

Æ

PMOS High Side Drive

PROG = V

CC

ENABLE

CP

100pF

CZ

4.7nF

RZ

15k

C

SS

0.33µF

R

OSC

18.7k

CV

CC

2.2µF

V

IN

QT1

3.3V

V

IN

C

IN

330µF x 2

RS

22.1k

CS

39nF

L1

2.5µH

1.9V

1A to 8A

V

OUT

RF

5.23k

C

OUT

470µF x 3

RI

10k

QB

DS

1

2

16

15

14

13

12

11

3

4

5

6

7

8

10

9

N/C

ENABLE

ISP

ISN

V

FB

COMP

SS

R

OSC

BST

GH

SWN

GND

PGND

GL

V

CC

PROG

SP6120B

16 Pin TSSOP

QT, QB = FAIRCHILD FDS6690A

QT1 = FAIRCHILD FDS6375 (PMOS only)

L1 = PANASONIC ETQP6F2R5SFA

DS = STMICROELECTRONICS STPS2L25U

C

IN

= SANYO 6TPB330M

C

OUT

= SANYO 4TPB470M

Now Available in Lead Free Packaging

2

Date: 5/25/04

SP6120B Low Voltage, AnyFET

TM

, Synchronous, Buck Controller © Copyright 2004 Sipex Corporation

SPECIFICATIONS

Unless otherwise specified: 3.0V < V

CC

<5.5V, 3.0V < BST < 13.2V, R

OSC

= 18.7k, C

COMP

= 0.1µF, C

SS

= 0.1µF, ENABLE =

3V, CGH = CGL = 3.3nF, V

FB

= 1.25V, ISP = ISN = 1.25V, SWN = GND = PGND = 0V, -40∞C < T

AMB

<85∞C (Note 1)

ABSOLUTE MAXIMUM RATINGS

These are stress ratings only and functional operation

of the device at these ratings or any other above those

indicated in the operation sections of the specifications

below is not implied. Exposure to absolute maximum

rating conditions for extended periods of time may

affect reliability.

V

CC

............................................................................... 7V

BST ........................................................................ 13.2V

BST-SWN .................................................................... 7V

SWN .................................................................. -1V to 7V

GH ..................................................... -0.3V to BST +0.3V

GH-SWN ..................................................................... 7V

All Other Pins ....................................... -0.3V to V

CC

+0.3V

Peak Output Current < 10µs

GH, GL ........................................................................ 2A

Operating Temperature Range

SP6120C ................................................ 0∞C to +70∞C

SP6120E .............................................. -40∞C to +85∞C

Junction Temperature, T

J

...................................... +125∞C

Storage Temperature Range .................. -65∞C to +150∞C

Power Dissipation

Lead Temperature (soldering 10 sec) ................... +300∞C

ESD Rating ........................................................ 2kV HBM

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

QUIESCENT CURRENT

V

CC

Supply Current

No Switching

-

0.95

1.8

mA

V

CC

Supply Current (Disabled)

ENABLE = 0V

-

5

20

µA

BST Supply Current

No Switching, V

BST

= V

CC

-

1

20

µA

No Switching, V

CC

= 5V, V

BST

= 10V

-

100

150

µA

ERROR AMPLIFIER

Error Amplifier Transconductance

600

µs

COMP Sink Current

V

FB

= 1.35V, COMP = 0.5V, No Faults

15

35

65

µA

COMP Source Current

V

FB

= 1.15V, COMP = 1.6V

15

35

65

µA

COMP Output Impedence

3

M

V

FB

Input Bias Current

-

60

100

nA

REFERENCE

Error Amplifier Reference

Trimmed with Error Amp in Unity Gain

1.238

1.250

1.262

V

V

FB

3% Low Comparator

3

%V

REF

V

FB

3% High Comparator

3

%V

REF

OSCILLATOR & DELAY PATH

Oscillator Frequency

270

300

330

kHz

Oscillator Frequency #2

R

OSC

= 10.2k

450

500

550

kHz

Duty Ratio

Loop In Control -100% DC possible

95

%

R

OSC

Voltage

Information Only - Moves

0.65

V

with Oscillator Trim

Minimum GH Pulse Width

V

CC

> 4.5V, Ramp up COMP

120

250

ns

Voltage > 0.6V until GH starts

Switching

3

Date: 5/25/04

SP6120B Low Voltage, AnyFET

TM

, Synchronous, Buck Controller © Copyright 2004 Sipex Corporation

SPECIFICATIONS: continued

Unless otherwise specified: 3.0V < V

CC

<5.5V, 3.0V < BST < 13.2V, R

OSC

= 18.7k, C

COMP

= 0.1µF, C

SS

= 0.1µF, ENABLE =

3V, CGH = CGL = 3.3nF, V

FB

= 1.25V, ISP = ISN = 1.25V, SWN = GND = PGND = 0V, -40∞C < T

AMB

<85∞C (Note 1)

Note 1: Specifications to -40∞C are guaranteed by design, characterization and correlation with statistical process control.

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

SOFTSTART

SS Charge Current

V

SS

= 1.5V

25

50

70

µA

SS Discharge Current

V

SS

= 1.5V

2

5

7

µA

COMP Discharge Current

V

COMP

= 0.5V, Fault Initiated

200

500

-

µA

COMP Clamp Voltage

V

FB

< 1.0V, VSS = 2.5V

2.0

2.4

2.8

V

SS Ok Threshold

1.7

2.0

2.2

V

SS Fault Reset

0.2

0.25

0.3

V

SS Clamp Voltage

2.0

2.4

2.8

V

OVER CURRENT & ZERO CURRENT COMPARATORS

Over Current Comparator

Rail to Rail Common Mode Input

32

43

54

mV

Threshold Voltage

ISN, ISP Input Bias Current

-

60

250

nA

Zero Current Comparator

VISP - VISN

2

mV

Threshold

UVLO

V

CC

Start Threshold

2.75

2.85

2.95

V

V

CC

Stop Threshold

2.65

2.75

2.9

V

ENABLE

Enable Threshold

ON

1.45

OFF

0.65

V

Enable Pin Source Current

0.6

4

9

µA

GATE DRIVER

GH Rise Time

V

CC

> 4.5V

-

40

110

ns

GH Fall Time

V

CC

> 4.5V

-

40

110

ns

GL Rise Time

V

CC

> 4.5V

-

40

110

ns

GL Fall Time

V

CC

> 4.5V

-

40

110

ns

GH to GL Non-Overlap Time

V

CC

> 4.5V

0

60

140

ns

GL to GH Non-Overlap Time

V

CC

> 4.5V

0

60

140

ns

V

BST

OK Threshold

V

CC

= 3.0V, FB=1.15V, Search GL High

4.0

4.8

5.0

V

V

CC

= 5.5V, FB=1.15V, Search GL High

7.3

7.8

8.3

V

Forced GL ON

V

BST

< V

BST

OK Threshold, FB =1.15V

200

350

650

ns

4

Date: 5/25/04

SP6120B Low Voltage, AnyFET

TM

, Synchronous, Buck Controller © Copyright 2004 Sipex Corporation

PIN DESCRIPTION

NAME

FUNCTION

PIN NUMBER

1

N/C

No Connection

2

ENABLE

TTL compatible input with internal 4uA pullup. Floating or Venable> 1.5V will

enable the part, Venable < 0.65V disables part.

3

ISP

Current Sense Positive Input: Rail to Rail Input for Over-Current Detection,

43mV threshold with 10µs (typ) response time.

4

ISN

Current Sense Negative Input: Rail to Rail input for Over-Current Detection.

5

V

FB

Feedback Voltage Pin: Inverting input of the error amplifier and serves as the

output voltage feedback point for the buck converter. The output voltage is

sensed and can be adjusted through an external resistor divider.

6

COMP

Error Amplifier Compensation Pin: A lead lag network is typically connected

to this pin to compensate the feedback loop. This pin is clamped by the SS

voltage and is limited to 2.8V maximum.

7

SS

Soft Start Programming Pin: This pin sources 50µA on start-up. A 0.01µF to

1µF capacitor on this pin is typically enough capacitance to soft start a power

supply. In addition, hiccup mode timing is controlled by this pin through the

5µA discharge current. The SS voltage is clamped to 2.7V maximum.

8

R

OSC

Frequency Programming Pin: A resistor to ground is used to program

frequency. Typical values - 18,700, 300kHz; 10,200, 500kHz.

9

PROG

Programming Pin:

PROG = GND; MODE = NFET/CONTINOUS

PROG = 68k to GND; MODE = NFET/DISCONTINOUS

PROG = VCC; MODE = PFET/CONTINOUS

PROG = 68k to VCC; MODE = PFET/DISCONTINOUS

10

V

CC

I.C. Supply Pin: ESD structures also hooked to this pin. Properly bypass this

pin to PGND with a low ESL/ESR ceramic capacitor.

11

GL

Synchronous FET Driver: 1nF/20ns typical drive capability.

12

PGND

Power Ground Pin: Used for Power Stage. Connect Directly to GND at I.C.

pins for optimal performance.

13

GND

Ground Pin: Main ground pin for I.C.

14

SWN

Switch Node Reference: High side MOSFET driver reference. Can also be

tied to GND for low voltage applications.

15

GH

HIgh Side MOSFET Driver: Can be NFET or PFET depending on Program

Mode. 1nF/20ns typical drive capability. Maximum voltage rating is

referenced to SWN.

16

BST

High Side Driver Supply Pin. When V

BST

is less than V

BST

OK Threshold, GL

is forced to turn on for at least 300ns. This is intended for enough time to

charge the BST capacitor.

5

Date: 5/25/04

SP6120B Low Voltage, AnyFET

TM

, Synchronous, Buck Controller © Copyright 2004 Sipex Corporation

BLOCK DIAGRAM

APPLICATION SCHEMATIC

Figure 1. Schematic 3.3V to 1.9V Power Supply

QT, QB = FAIRCHILD FDS6690A

L1 = PANASONIC ETQP6F2R5SFA

DS = STMICROELECTRONICS STPS2L25U

+

-

+

-

-

+

-

+

-

+

-

+

-

+

+

-

Synchronous

Driver

Driver

Logic

Soft Start

& Hiccup Logic

S

Q

R

Set Dominant

Fault Latch

S

Q

R

Program

Logic

Window

Comparator

Logic

+ -

T

OFF

ENABLE

GND

V

FB

COMP

V

CC

ISP

ISN

Reference

SS

2.85 V

ON

2.75 V

OFF

430mV

3

4

2

13

5

6

10

SS

2V

V

FB

3% Low ENABLE

V

FB

1.25V

GM

Error Amplifier

V

FB

Zero crossing detect

250mV

SS

7

I

CHARGE

0.65V

12

8

PGND

R

OSC

11

14

15

16

9

Continuous/

Discontinuous

NFET/PFET

ON 100%

OFF 100%

RESET

Dominant

PWM Latch

QPWM

FAULT

F (kHz) = 5.7E6/R

OSC

()

+

-

10µs

OVC

UVLO

1V RAMP

3%

3%

- +

PROG

BST

GH

SWN

-

+

GL

x 10

C

IN

= SANYO 6TPB330M

C

OUT

= SANYO 4TPB470M

SP6120B

NC

ENABLE

ISP

ISN

V

FB

COMP

SS

R

OSC

BST

GH

SWN

GND

PGND

GL

V

CC

PROG

Æ

Æ

NMOS High Side Drive

PROG = GND

ENABLE

CP

100pF

CZ

4.7nF

RZ

15k

C

SS

0.33µF

R

OSC

18.7k

CV

CC

2.2µF

V

IN

MBR0530

C

BST

1µF

QT

3.3V

V

IN

C

IN

330µF x 2

RS

22.1k

CS

39nF

L1

2.5µH

1.9V

1A to 8A

V

OUT

RF

5.23k

C

OUT

470µF x 3

RI

10k

QB

DS

C

B

1µF

6

Date: 5/25/04

SP6120B Low Voltage, AnyFET

TM

, Synchronous, Buck Controller © Copyright 2004 Sipex Corporation

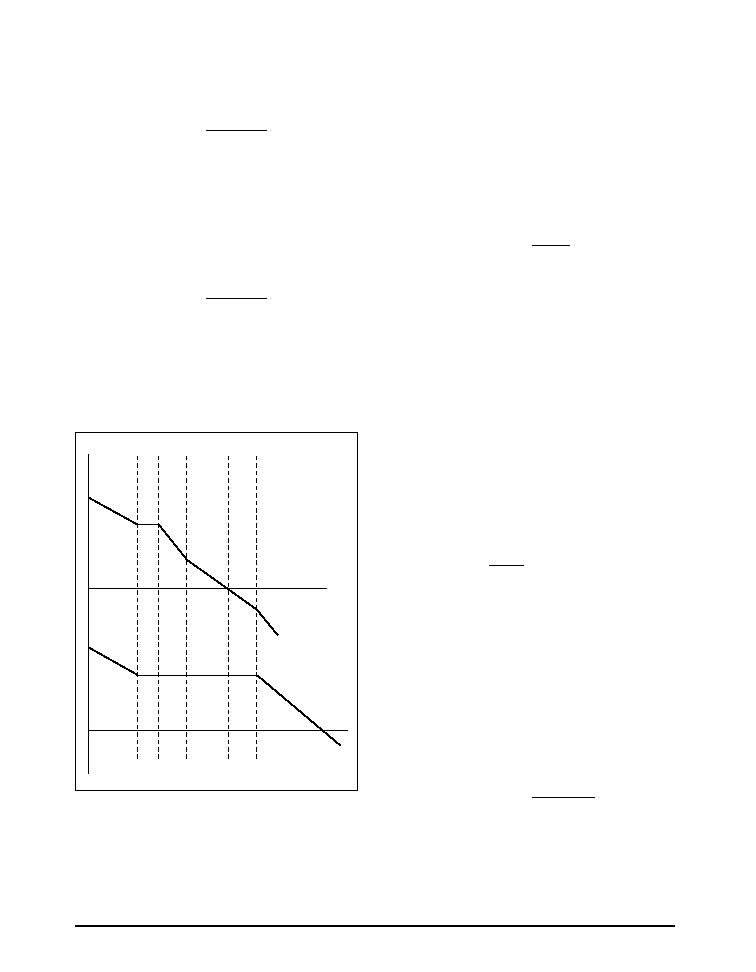

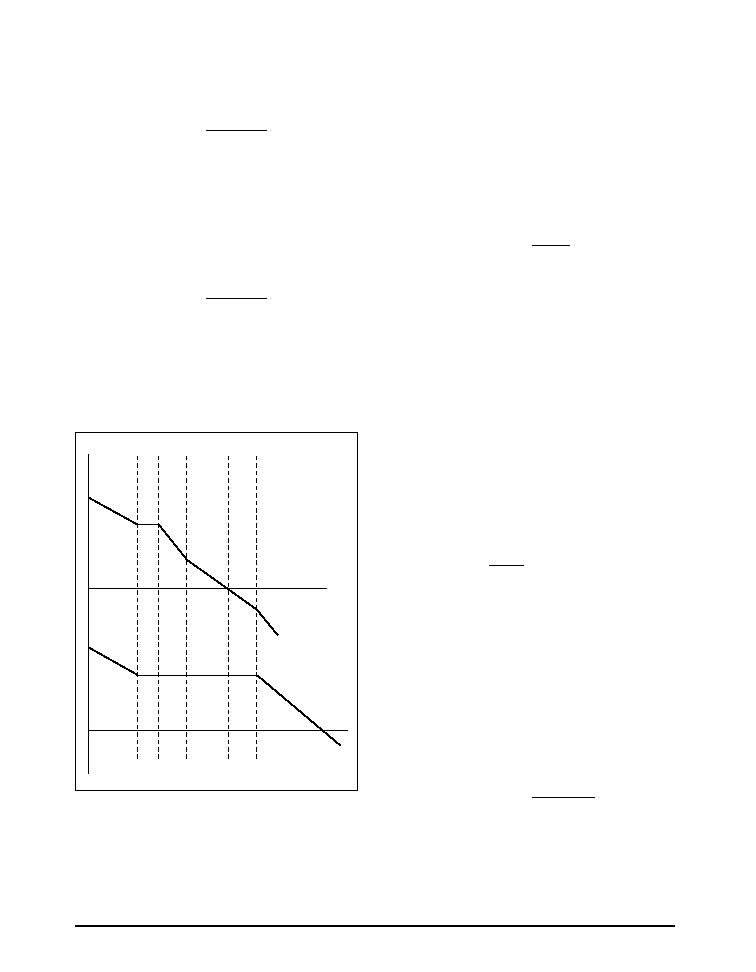

Efficiency (%)

50

60

70

80

90

100

0

2

4

6

Output Current (A)

8

10

Figure 2. Efficiency vs. Output Current

Figure 3. Load Regulation

Figure 4. Load Step Response: 0.4A to 2A

Figure 5. Load Step Response: 0.4A to 7A

Typical Performance Characteristics

Refer to circuit in Figure 1 with V

IN

= 3.3V; V

OUT

= 1.9V, R

OSC

= 18.7k, and T

AMB

= +25∞C unless otherwise noted.

Figure 6. Start-Up Response: 5A Load

1.875

1.880

1.885

1.890

1.895

1.900

1.905

1.910

1.915

1.920

1.925

0

1

2

3

4

5

Load Current (A)

V

OUT

(V)

V

OUT

Gate High

I

OUT

(1A/div)

V

OUT

Gate High

I

OUT

(5A/div)

V

OUT

V

IN

Soft Start

I

IN

(1A/div)

Figure 7. Overcurrent: 9A Load

V

OUT

V

IN

Soft Start

I

OUT

(5A/div)

7

Date: 5/25/04

SP6120B Low Voltage, AnyFET

TM

, Synchronous, Buck Controller © Copyright 2004 Sipex Corporation

Typical Performance Characteristics

Unless otherwise specified: V

CC

= BST = ENABLE = 3.3V, R

OSC

= 18.7k, C

COMP

= 0.1µF, C

SS

= 0.1µF, CGH = CGL = 3.3nF, V

FB

= 1.25V,

ISP = ISN = 1.25V, SWN = GND = PGND = 0V, T

AMB

= 25∞C.

Figure 8. Error Amplifier Reference vs. Temperature

Figure 9. Overcurrent Comparator Threshold Voltage

vs. Temperature

Figure 10. SS Charge Current vs. Temperature with

V

SS

= 1.5V

Figure 11. SS Discharge Current vs. Temperature with

V

SS

= 1.5V

Figure 12. V

FB

3% High Comparator vs. Temperature

Figure 13. V

FB

3% Low Comparator vs. Temperature

-0.20

-0.10

0.00

0.10

0.20

0.30

-40

-15

10

35

60

85

1.25V

REF

(%)

Temperature (∞C)

-47

-40

-15

10

35

60

85

SS Charge (

µ

A)

-46

-45

-44

Temperature (∞C)

5.00

5.05

5.10

5.15

5.20

5.25

-40

-15

10

35

60

85

SS Discharge (

µ

A)

Temperature (∞C)

2.6

2.8

3.0

3.2

3.4

3.6

-40

-15

10

35

60

85

Temperature (∞C)

V

FB

High (% V

REF

)

-3.2

-3.0

-2.8

-2.6

-2.4

-2.2

-40

-15

10

35

60

85

Temperature (∞C)

V

FB

Low (% V

REF

)

-40

-15

10

35

60

85

Overcurrent (mV)

40

42

44

Temperature (∞C)

46

48

38

8

Date: 5/25/04

SP6120B Low Voltage, AnyFET

TM

, Synchronous, Buck Controller © Copyright 2004 Sipex Corporation

Figure 14. V

CC

Start Threshold vs. Temperature

Figure 15. V

CC

Stop Threshold vs. Temperature

Figure 16. Oscillator Frequency vs. Temperature

Figure 17. Oscillator Frequency vs. R

OSC

with V

CC

= 5V

and CGH = CGL = Open.

2.900

-40

-15

10

35

60

85

V

CC

Start (V)

Temperature (∞C)

2.875

2.850

2.825

2.800

2.850

-40

-15

10

35

60

85

V

CC

Stop (V)

Temperature (∞C)

2.825

2.800

2.775

2.750

302

-40

-15

10

35

60

85

Frequency (kHz)

Temperature (∞C)

301

300

299

298

200

300

400

500

600

700

800

5

10

15

20

25

30

Frequency (kHz)

R

OSC

(k)

Typical Performance Characteristics

Unless otherwise specified: V

CC

= BST = ENABLE = 3.3V, R

OSC

= 18.7k, C

COMP

= 0.1µF, C

SS

= 0.1µF, CGH = CGL = 3.3nF, V

FB

= 1.25V,

ISP = ISN = 1.25V, SWN = GND = PGND = 0V, T

AMB

= 25∞C.

THEORY OF OPERATION

General Overview

The SP6120B is a constant frequency, voltage

mode PWM controller for low voltage, DC/DC

step down converters. It has a main loop where

an external resistor (R

OSC

) sets the frequency and

the driver is controlled by the comparison of an

error amp output (COMP) and a 1V ramp signal.

The error amp has a transconductance of 600

µS,

an output impedance of 3 M

, an internal pole at

2 MHz and a 1.25V reference input. Although

the main control loop is capable of 0% and 100%

duty cycle, its response time is limited by the

external component selection. Therefore, a sec-

ondary loop, including a window comparator

positioned 3% above and below the reference,

has been added to insure fast response to line and

load transients. A unique "Ripple & Frequency

Independent" algorithm, added to the secondary

loop, insures that the window comparator does

not interfere with the main loop during normal

operation. In addition to receiving driver com-

mands from the main and secondary loops, the

Driver Logic is also controlled by the Program-

ming Logic, Fault Logic and Zero Crossing

Comparator. The Programming Logic tells the

Driver Logic whether the controller is using a

PFET or NFET high side driver as well as whether

the controller is operating in continuous or dis-

continuous mode. The Fault Logic holds the high

and low side drivers off if V

CC

dips below 2.75V,

if an over current condition exists, or if the part

is disabled through the ENABLE pin. The Zero

Crossing Comparator turns the lower driver off

9

Date: 5/25/04

SP6120B Low Voltage, AnyFET

TM

, Synchronous, Buck Controller © Copyright 2004 Sipex Corporation

if the conduction current reaches zero and the

Driver Logic has made an attempt to turn the

lower driver on and the Programming Logic is

set for discontinuous mode. Lastly, the 4

driv-

ers have internal gate non-overlap circuitry and

are designed to drive MOSFETs associated with

converter designs in the 5A to 10A range. Typi-

cally the high side driver is referenced to the

SWN pin; further improving the efficiency and

performance of the converter.

ENABLE

Low quiescent mode or "Sleep Mode" is initi-

ated by pulling the ENABLE pin below 650mV.

The ENABLE pin has an internal 4

µA pull-up

current and does not require any external inter-

face for normal operation. If the ENABLE pin is

driven from a voltage source, the voltage must

be above 1.45V in order to guarantee proper

"awake" operation. Assuming that V

CC

is above

2.85V, the SP6120B transitions from "Sleep

Mode" to "Awake Mode" in about 20

µs to 30µs

and from "Awake Mode" to "Sleep Mode" in a

few microseconds. SP6120B quiescent current

in sleep mode is 20

µA maximum. During Sleep

Mode, the high side and low side MOSFETs are

turned off and the COMP and SS pins are held

low.

Bootstrap Circuit

When SP6120B is programmed to drive a high

side N channel MOSFET, a bootstrap circuit is

required to generate a voltage higher than V

IN

to

fully enhance the top MOSFET. A typical boot-

strap only requires a capacitor and diode shown

as C

BST

and D

BST

in the application circuit on the

front page. When the bottom MOSFET Q

B

is

turned on, D

BST

is forward biased and charges

the C

BST

close to V

IN

. When the top MOSFET

turn on, the switch node swings to the V

IN

voltage. Now the voltage at the BST pin is 2*V

IN

and D

BST

is reverse biased. The BST pin voltage

powers the high side MOSFET driver, and thus

the GH output goes up to 2*V

IN

to provide a V

DS

equal to V

IN

.

Under certain conditions, the bottom MOSFET

may not turn on long enough to replenish C

BST

voltage. Therefore, when the top MOSFET turns

on, the BST pin may not be high enough to fully

enhance the switch. To prevent this operation,

SP6120B monitors the BST pin voltage in refer-

ence to the V

CC

voltage. When the BST pin

voltage is less than V

BST

OK threshold, the

controller forces the GL to turn on for MINI-

MUM GL ON at the end of the switching cycle.

This provides enough time to recharge the C

BST

and ensures the proper operation of the boot-

strap circuit.

UVLO

Assuming that the ENABLE pin is either pulled

high or floating, the voltage on the V

CC

pin then

determines operation of the SP6120B. As V

CC

rises, the UVLO block monitors V

CC

and keeps

the high side and low side MOSFETs off and the

COMP and SS pins low until V

CC

reaches 2.85V.

If no faults are present, the SP6120B will initiate

a soft start when V

CC

exceeds 2.85V. Hysteresis

(about 100mV) in the UVLO comparator pro-

vides noise immunity at start-up.

Soft Start

(see figures on next page)

Soft start is required on step-down controllers to

prevent excess inrush current through the power

train during start-up. Typically this is managed

by sourcing a controlled current into a program-

ming capacitor (on the SS pin) and then using the

voltage across this capacitor to slowly ramp up

either the error amp reference or the error amp

output (COMP). The control loop creates nar-

row width driver pulses while the output voltage

is low and allows these pulses to increase to their

steady-state duty cycle as the output voltage

increases to its regulated value. As a result of

controlling the inductor volt*second product

during start-up, inrush current is also controlled.

The presence of the output capacitor creates

extra current draw during start-up. Simply stated,

dV

OUT

/dt requires an average sustained current

in the output capacitor and this current must be

considered while calculating peak inrush current

and over current thresholds. Since the SP6120B

ramps up the error amp reference voltage, an

expression for the output capacitor current can

be written as:

IC

OUT

= (C

OUT

/C

SS

) * (V

OUT

/1.25) * 50µA

General Overview: continued

10

Date: 5/25/04

SP6120B Low Voltage, AnyFET

TM

, Synchronous, Buck Controller © Copyright 2004 Sipex Corporation

TIME

3% Low

Enable Voltage

V(V

CC

)

0V

SWN

Voltage

V(V

CC

)

0V

FAULT

Reset Voltage

V(V

CC

)

0V

Inductor Current

I

LOAD

0V

Error Amplifier

Reference

Voltage

0V

1.25V

V

OUT

= V(Eamp REF)* (1+RF/RI)

SS Voltage

0V

0.25V

0.7V

2.0V

2.4V

dV

SS

/dt = 50µA/C

SS

V(ISP) - V(ISN)

0V

250mV

V(V

CC

)

0V

0V

2.0V

SS Voltage

FAULT Voltage

2.4V

43mV

As the figure shows, the SS voltage controls a

variety of signals. First, provided all the external

fault conditions are removed, the fault latch is reset

and the SS cap begins to charge. When the SS

voltage reaches around 0.3V, the error amp refer-

ence begins to track the SS voltage while maintain-

ing the 0.3V differential. As the SS voltage reaches

0.7V, the driver begins to switch the high side and

low side MOSFETs with narrow pulses in an

effort to keep the converter output regulated. As

the error amp reference ramps upward, the driver

pulses widen until a steady state value is reached.

The "bump" in the inductor current transfer curve

is indicative of excess charge current incurred due

to the finite propagation delay of the controller.

When the SS voltage reaches 2.0V, the second-

ary loop including the 3% window comparator

is enabled. Lastly, the SS voltage is clamped at

2.4V, ending the soft start charge cycle.

Hiccup Mode

When the converter enters a fault mode, the

driver holds the high side and low side MOSFETs

off for a finite period of time. Provided the part

is enabled, this time is set by the discharge of the

SS capacitor. The discharge time is roughly 10

times the charge interval thereby giving the

power supply plenty of time to cool during an

over current fault. The driver off-time is pre-

dominantly determined by the discharge time.

Restart will occur just like a normal soft start

cycle.

However, if a fault occurs during the soft start

charge cycle, the FAULT latch is immediately

set, turning off the high side and low side

MOSFETs. The MOSFETs remain off during

the remainder of the charge cycle and subse-

quent discharge cycle of the SS capacitor. Again,

provided there are no external fault conditions,

the FAULT latch will be reset when the SS

voltage reaches 250 mV.

Over Current Protection

The SP6120B over current protection scheme is

designed to take advantage of three popular

detection schemes: Sense Resistor, Trace Resis-

tor or Inductor Sense. Because the detection

threshold is only 43mV, both trace resistor and

inductor sense become attractive protection

schemes. The inductor sense scheme adds no

additional dc loss to the converter and is an

excellent alternative to Rdson based schemes;

11

Date: 5/25/04

SP6120B Low Voltage, AnyFET

TM

, Synchronous, Buck Controller © Copyright 2004 Sipex Corporation

0V

0V

0A

0V

0V

0A

Continuous

Load

Current

GH, GL

Voltage

Discontinuous

Load

Current

GH, GL

Voltage

TIME

providing continuous current sensing and flex-

ible MOSFET selection. An internal, 10

µs filter

conditions the over current signal from tran-

sients generated during load steps. In addition,

because the over current inputs, ISP and ISN, are

capable of rail to rail operation, the SP6120B

provides excellent over current protection dur-

ing conditions where V

IN

approaches V

OUT

.

Zero Crossing Detection

In some applications, it may be undesirable to

have negative conduction current in the induc-

tor. This situation happens when the ripple cur-

rent in the inductor is higher than the load cur-

rent. Therefore, the SP6120B provides an option

for "discontinuous" operation. If the Program

Logic (see next section) is set for discontinuous

mode, then the Driver Logic looks at the Zero

Crossing Comparator and the state of the lower

gate driver. If the low side MOSFET was "on"

and V(ISP)-V(ISN) < 0 then the low side

MOSFET is immediately turned off and held off

until the high side MOSFET is turned "on".

When the high side MOSFET turns "on" , the

Driver Logic is reset. The following figures

show continuous and discontinuous operation

for a converter with an NFET high side MOSFET.

Discontinuous vs. Continuous Mode

The discontinuous mode is used when better

light load efficiency is desired, for example in

portable applications. Additionally, for power

supply sequencing in some applications the DC-

DC converter output is pre-charged to a voltage

through a switch at start-up, and discontinuous

operation would be required to prevent reverse

inductor current from discharging the pre-charge

voltage. The continuous mode is preferable for

lower noise and EMI applications since the

discontinuous mode can cause ringing of the

switch node voltage when it turns both switches

off. Another example where continuous mode

could be required is one where the inductor has

an extra winding used for an over-winding regu-

lator and thus continuous conduction is neces-

sary to produce this second output voltage.

Program Logic

The Program pin (PROG) of the SP6120B adds

a new level of flexibility to the design of DC/DC

converters. A 10

µA current flows either into or

out of the Program pin depending on the initial

potential presented to the pin. If no resistor is

present, the Program Logic simply looks at the

potential on the pin, sets the mode to "continu-

ous" and programs NFET or PFET high side

drive accordingly. If the 68k

resistor is present,

the voltage drop across the resistor signals the

SP6120B to put the Driver Logic in "discontinu-

ous" mode. With one pin and a 68k

resistor, the

SP6120B can be configured for a variety of

operating modes:

Over Current Protection: continued

12

Date: 5/25/04

SP6120B Low Voltage, AnyFET

TM

, Synchronous, Buck Controller © Copyright 2004 Sipex Corporation

0V

MAX

DC Load

Current

MIN

0A

Output

Voltage

V

OUT

Reset

Set

V(V

CC

)

Main Loop

3% High

Latch On

0V

V(V

CC

)

3% Low

Latch On

.

3% High Sync.

3% High

3% Low Sync.

3% Low

1.25V Cross.

TIME

E

L

B

A

T

H

T

U

R

T

C

I

G

O

L

M

A

R

G

O

R

P

N

I

P

M

A

R

G

O

R

P

T

E

F

P

R

O

T

E

F

N

E

D

O

M

D

N

G

o

t

t

r

o

h

S

T

E

F

N

s

u

o

u

n

i

t

n

o

C

k

8

6

D

N

G

o

t

T

E

F

N

s

u

o

u

n

i

t

n

o

c

s

i

D

V

o

t

t

r

o

h

S

C

C

T

E

F

P

s

u

o

u

n

i

t

n

o

C

k

8

6

V

o

t

C

C

T

E

F

P

s

u

o

n

i

t

n

o

c

s

i

D

The NFET/PFET programmability is for the

high side MOSFET. When designing DC/DC

converters, it is not always obvious when to use

an NFET with a charge pump or a simple PFET

for the high side MOSFET. Often, the controller

has to be changed, making performance evalua-

tions difficult. This difficulty is worsened by the

limited availability of true low voltage control-

lers. In addition, by also programming the mode,

continuous or discontinuous, switch mode power

designs that are successful in bus applications

can now find homes in portable applications.

Secondary Loop (3% Window Comparator)

DSP, microcontroller and microprocessor appli-

cations have very strict supply voltage require-

ments. In addition, the current requirements to

these devices can change drastically. Linear

regulators, typically the workhorse for DC/DC

step-down, do a great job managing accuracy

and transient response at the expense of effi-

ciency. On the other hand, PWM switching

regulators typically do a great job managing

efficiency at the expense of output ripple and

line/load step response. The trick in PWM

controller design is to emulate the transient re-

sponse of the linear regulator.

Of course improving transient response should

be transparent to the power supply designer.

Very often this is not the case. Usually the very

circuitry that improves the controllers transient

response adversely interferes with the main PWM

loop or complicates the board level design of the

power converter.

The SP6120B handles line/load transient re-

sponse in a new way. First, a window compara-

Program Logic: continued

tor detects whether the output voltage is above

or below the regulated value by 3%. Then, a

proprietary "Ripple & Frequency Independent"

algorithm synchronizes the output of the win-

dow comparator with the peak and valley of the

inductor current waveform. 3% low detection is

synchronized with inductor current peak; 3%

high detection is synchronized with the inductor

current valley. However, in order to eliminate

any additional loops, the current peak and valley

are determined by the edges associated with the

on-time in the main loop. The set pulse corre-

sponding to the start of an on-time indicates a

13

Date: 5/25/04

SP6120B Low Voltage, AnyFET

TM

, Synchronous, Buck Controller © Copyright 2004 Sipex Corporation

GATE DRIVER TEST CONDITONS

5V

90%

10%

GH (GL)

2V

5V

GH (GL)

2V

NON-OVERLAP

RISE TIME

FALL TIME

90%

10%

V(BST)

0V

GH

Voltage

V(V

CC

)

0V

GL

Voltage

V(V

CC

= V

IN

)

SWN

Voltage

~0V

~V(Diode) V

~2V(V

IN

)

BST

Voltage

~V(V

IN

)

TIME

current valley and the reset pulse corresponding

to the end of an on-time indicates a current peak.

In effect, the main loop determines the status of

the secondary loop.

Notice that the output voltage appears to coast

toward the regulated value during periods where

the main loop would be telling the drivers to

switch. It is during this interval that the 3%

window comparator has taken control away from

the main loop. The main loop regains control

only if the output voltage crosses through its

regulated value. Also notice where the 3% com-

parator takes over. The output voltage is consid-

ered "high" only if the trough of the ripple is

above 3%. The output voltage is considered

"low" only if the peak of the ripple is below 3%.

By managing the secondary loop in this fashion,

the SP6120B can improve the transient response

of high performance power converters without

causing strange disturbances in low to moderate

performance systems.

Driver Logic

Signals from the PWM latch (QPWM), Fault

latch (FAULT), Program Logic, Zero Crossing

Comparator, and 3% Window Comparators all

flow into the Driver Logic. The following is a

truth table for determining the state of the GH and

GL voltages for given inputs:

E

L

B

A

T

H

T

U

R

T

C

I

G

O

L

R

E

V

I

R

D

T

L

U

A

F

1

1

0

0

0

0

0

0

0

0

r

o

M

W

P

Q

P

M

O

C

%

3

X

X

1

1

0

0

0

0

0

0

T

E

F

P

/

T

E

F

N

N

P

N

P

N

P

N

P

N

P

C

S

I

D

/

T

N

O

C

X

X

X

X

C

C

D

D

D

D

S

S

O

R

C

O

R

E

Z

X

X

X

X

X

X

0

0

1

1

H

G

0

1

1

0

0

1

0

1

0

1

L

G

0

0

0

0

1

1

1

1

0

0

The QPWM and 3% Comparators are grouped

together because 3% Low is the same as QPWM

= 1 and 3% High is the same as QPWM = 0.

Output Drivers

The driver stage consists of one high side, 4

driver, GH and one low side, 4

, NFET driver,

GL. As previously stated, the high side driver can

be configured to drive a PFET or an NFET high

side switch. The high side driver can also be

configured as a switch node referenced driver.

Due to voltage constraints, this mode is mandatory

for 5V, single supply, high side NFET applica-

tions. The following figure shows typical driver

waveforms for the 5V, high side NFET design.

As with all synchronous designs, care must be

taken to ensure that the MOSFETs are properly

chosen for non-overlap time, peak current capa-

bility and efficiency.

Secondary Loop (3% Window Comparator):

continued

14

Date: 5/25/04

SP6120B Low Voltage, AnyFET

TM

, Synchronous, Buck Controller © Copyright 2004 Sipex Corporation

APPLICATIONS INFORMATION

Inductor Selection

There are many factors to consider in selecting

the inductor including cost, efficiency, size and

EMI. In a typical SP6120B circuit, the inductor

is chosen primarily for value, saturation current

and DC resistance. Increasing the inductor value

will decrease output voltage ripple, but degrade

transient response. Low inductor values pro-

vide the smallest size, but cause large ripple

currents, poor efficiency and more output ca-

pacitance to smooth out the larger ripple cur-

rent. The inductor must also be able to handle

the peak current at the switching frequency

without saturating, and the copper resistance in

the winding should be kept as low as possible to

minimize resistive power loss. A good compro-

mise between size, loss and cost is to set the

inductor ripple current to be within 20% to 40%

of the maximum output current.

The switching frequency and the inductor oper-

ating point determine the inductor value as

follows:

( max)

(max )

(max)

)

(

OUT

r

S

IN

OUT

IN

OUT

I

K

F

V

V

V

V

L

-

=

where:

F

S

= switching frequency

K

r

= ratio of the ac inductor ripple current to

the maximum output current

The peak to peak inductor ripple current is:

L

F

V

V

V

V

I

S

I N

OUT

IN

OUT

PP

(max)

(max)

)

(

-

=

Once the required inductor value is selected, the

proper selection of core material is based on

peak inductor current and efficiency require-

ments.

The core material must be large enough not to

saturate at the peak inductor current

2

(max)

P P

OUT

PEAK

I

I

I

+

=

and provide low core loss at the high switching

frequency. Low cost powdered iron cores have

a gradual saturation characteristic but can intro-

duce considerable ac core loss, especially when

the inductor value is relatively low and the

ripple current is high. Ferrite materials, on the

other hand, are more expensive and have an

abrupt saturation characteristic with the induc-

tance dropping sharply when the peak design

current is exceeded. Nevertheless, they are pre-

ferred at high switching frequencies because

they present very low core loss and the design

only needs to prevent saturation. In general,

ferrite or molypermalloy materials are better

choice for all but the most cost sensitive appli-

cations.

The power dissipated in the inductor is equal to

the sum of the core and copper losses. To mini-

mize copper losses, the winding resistance needs

to be minimized, but this usually comes at the

expense of a larger inductor. Core losses have a

more significant contribution at low output cur-

rent where the copper losses are at a minimum,

and can typically be neglected at higher output

currents where the copper losses dominate. Core

loss information is usually available from the

magnetic vendor.

The copper loss in the inductor can be calculated

using the following equation:

WINDING

RMS

L

Cu

L

R

I

P

2

)

(

)

(

=

where I

L(RMS)

is the RMS inductor current that

can be calculated as follows:

I

L(RMS)

= I

OUT(max)

1 + 1

(

I

PP

)

2

3 I

OUT(max)

Output Capacitor Selection

The required ESR (Equivalent Series Resis-

tance) and capacitance drive the selection of the

type and quantity of the output capacitors. The

ESR must be small enough that both the resis-

tive voltage deviation due to a step change in the

load current and the output ripple voltage do not

exceed the tolerance limits expected on the

output voltage. During an output load transient,

the output capacitor must supply all the addi-

tional current demanded by the load until the

SP6120B adjusts the inductor current to the new

value. Therefore the capacitance must be large

15

Date: 5/25/04

SP6120B Low Voltage, AnyFET

TM

, Synchronous, Buck Controller © Copyright 2004 Sipex Corporation

enough so that the output voltage is held up

while the inductor current ramps up or down to

the value corresponding to the new load current.

Additionally, the ESR in the output capacitor

causes a step in the output voltage equal to the

ESR value multiplied by the change in load

current. Because of the fast transient response

and inherent 100% and 0% duty cycle capabil-

ity provided by the SP6120B when exposed to

output load transient, the output capacitor is

typically chosen for ESR, not for capacitance

value.

The output capacitor's ESR, combined with the

inductor ripple current, is typically the main

contributor to output voltage ripple. The maxi-

mum allowable ESR required to maintain a

specified output voltage ripple can be calculated

by:

PP

OUT

ESR

I

V

R

where:

V

OUT

= peak to peak output voltage ripple

I

PP

= peak to peak inductor ripple current

The total output ripple is a combination of the

ESR and the output capacitance value and can

be calculated as follows:

V

OUT

=

(

I

PP

(1 ≠ D)

)

2

+ (I

PP

R

ESR

)

2

C

OUT

F

S

where:

F

S

= switching frequency

D = duty cycle

C

OUT

= output capacitance value

Recommended capacitors that can be used ef-

fectively in SP6120B applications are: low-

ESR aluminum electrolytic capacitors, OS-CON

capacitors that provide a very high performance/

size ratio for electrolytic capacitors and low-

ESR tantalum capacitors. AVX TPS series and

Kemet T510 surface mount capacitors are popu-

lar tantalum capacitors that work well in

SP6120B applications. POSCAP from Sanyo is

a solid electrolytic chip capacitor that has low

ESR and high capacitance. For the same ESR

value, POSCAP has lower profile compared

with tantalum capacitor.

Input Capacitor Selection

The input capacitor should be selected for ripple

current rating, capacitance and voltage rating.

The input capacitor must meet the ripple current

requirement imposed by the switching current.

In continuous conduction mode, the source cur-

rent of the high-side MOSFET is approximately

a square wave of duty cycle V

OUT

/V

IN

. Most of

this current is supplied by the input bypass

capacitors. The RMS value of input capacitor

current is determined at the maximum output

current and under the assumption that the peak

to peak inductor ripple current is low, it is given

by:

I

CIN(rms)

= I

OUT(max)

D(1 - D)

The worse case occurs when the duty cycle D is

50% and gives an RMS current value equal to

I

OUT

/2. Select input capacitors with adequate

ripple current rating to ensure reliable opera-

tion.

The power dissipated in the input capacitor is:

)

(

2

)

(

CIN

ESR

rms

CIN

CIN

R

I

P

=

This can become a significant part of power

losses in a converter and hurt the overall energy

transfer efficiency.

The input voltage ripple primarily depends on

the input capacitor ESR and capacitance. Ignor-

ing the inductor ripple current, the input voltage

ripple can be determined by:

2

)

(

)

(

(max)

)

(

IN

IN

S

OUT

I N

OUT

MAX

OUT

CIN

E SR

out

IN

V

C

F

V

V

V

I

R

I

V

-

+

=

The capacitor type suitable for the output ca-

pacitors can also be used for the input capaci-

tors. However, exercise extra caution when tan-

talum capacitors are considered. Tantalum ca-

pacitors are known for catastrophic failure when

exposed to surge current, and input capacitors

16

Date: 5/25/04

SP6120B Low Voltage, AnyFET

TM

, Synchronous, Buck Controller © Copyright 2004 Sipex Corporation

are prone to such surge current when power

supplies are connected `live' to low impedance

power sources. Certain tantalum capacitors, such

as AVX TPS series, are surge tested. For ge-

neric tantalum capacitors, use 2:1 voltage derat-

ing to protect the input capacitors from surge

fall-out.

MOSFET Selection

The losses associated with MOSFETs can be

divided into conduction and switching losses.

Conduction losses are related to the on resis-

tance of MOSFETs, and increase with the load

current. Switching losses occur on each on/off

transition when the MOSFETs experience both

high current and voltage. Since the bottom

MOSFET switches current from/to a paralleled

diode (either its own body diode or a Schottky

diode), the voltage across the MOSFET is no

more than 1V during switching transition. As a

result, its switching losses are negligible. The

switching losses are difficult to quantify due to

all the variables affecting turn on/off time. How-

ever, the following equation provides an ap-

proximation on the switching losses associated

with the top MOSFET driven by SP6120B.

S

OUT

IN

rss

S H

F

I

V

C

P

(max)

(max)

(max)

12

=

where

C

rss

= reverse transfer capacitance of the top

MOSFET

Switching losses need to be taken into account

for high switching frequency, since they are

directly proportional to switching frequency.

The conduction losses associated with top and

bottom MOSFETs are determined by:

D

I

R

P

OUT

ON

DS

CH

2

(max)

)

(

(max)

=

)

1

(

2

(max)

)

(

(max)

D

I

R

P

OUT

ON

DS

CL

-

=

where

P

CH(max)

= conduction losses of the high side

MOSFET

P

CL(max)

= conduction losses of the low side

MOSFET

R

DS(ON)

= drain to source on resistance.

The total power losses of the top MOSFET are

the sum of switching and conduction losses. For

synchronous buck converters of efficiency over

90%, allow no more than 4% power losses for

high or low side MOSFETs. For input voltages

of 3.3V and 5V, conduction losses often domi-

nate switching losses. Therefore, lowering the

R

DS(ON)

of the MOSFETs always improves

efficiency even though it gives rise to higher

switching losses due to increased C

rss

.

Top and bottom MOSFETs experience unequal

conduction losses if their on time is unequal. For

applications running at large or small duty cycle,

it makes sense to use different top and bottom

MOSFETs. Alternatively, parallel multiple

MOSFETs to conduct large duty factor.

R

DS(ON)

varies greatly with the gate driver volt-

age. The MOSFET vendors often specify R

DS(ON)

on multiple gate to source voltages (V

GS

), as

well as provide typical curve of R

DS(ON)

versus

V

GS

. For 5V input, use the R

DS(ON)

specified at

4.5V V

GS

. At the time of this publication, ven-

dors, such as Fairchild, Siliconix and Interna-

tional Rectifier, have started to specify R

DS(ON)

at V

GS

less than 3V. This has provided necessary

data for designs in which these MOSFETs are

driven with 3.3V and made it possible to use

SP6120B in 3.3V only applications.

Thermal calculation must be conducted to en-

sure the MOSFET can handle the maximum

load current. The junction temperature of the

MOSFET, determined as follows, must stay

below the maximum rating.

JA

MOSFET

A

J

R

P

T

T

(max)

(max)

( max)

+

=

where

T

A(max)

= maximum ambient temperature

PMOSFET(max) = maximum power dissipa-

tion of the MOSFET

R

JA

= junction to ambient thermal resistance.

R

JA

of the device depends greatly on the board

layout, as well as device package. Significant

thermal improvement can be achieved in the

maximum power dissipation through the proper

design of copper mounting pads on the circuit

board. For example, in a SO-8 package, placing

17

Date: 5/25/04

SP6120B Low Voltage, AnyFET

TM

, Synchronous, Buck Controller © Copyright 2004 Sipex Corporation

two 0.04 square inches copper pad directly

under the package, without occupying addi-

tional board space, can increase the maximum

power from approximately 1 to 1.2W. For DPAK

package, enlarging the tap mounting pad to 1 square

inches reduces the R

JA from 96

∞C/W to 40∞C/W.

Schottky Diode Selection

When paralleled with the bottom MOSFET, an

optional Schottky diode can improve efficiency

and reduce noises. Without this Schottky diode,

the body diode of the bottom MOSFET con-

ducts the current during the non-overlap time

when both MOSFETs are turned off. Unfortu-

nately, the body diode has high forward voltage

and reverse recovery problem. The reverse re-

covery of the body diode causes additional

switching noises when the diode turns off. The

Schottky diode alleviates these noises and addi-

tionally improves efficiency thanks to its low

forward voltage. The reverse voltage across the

diode is equal to input voltage, and the diode

must be able to handle the peak current equal to

the maximum load current.

The power dissipation of the Schottky diode is

determined by

P

DIODE

= 2V

F

I

OUT

T

NOL

F

S

where

T

NOL

= non-overlap time between GH and GL.

V

F

= forward voltage of the Schottky diode.

SP6120B

Æ

Æ

C2

C1

R1

COMP

Figure 18. The RC network connected to the COMP pin

provides a pole and a zero to control loop.

Loop Compensation Design

The goal of loop compensation is to manipulate

loop frequency response such that its gain crosses

over 0db at a slope of ≠20db/dec. The SP6120B

has a transconductance error amplifier and re-

quires the compensation network to be con-

nected between the COMP pin and ground, as

shown in Figure 18.

The first step of compensation design is to pick

the loop crossover frequency. High crossover

frequency is desirable for fast transient response,

but often jeopardize the system stability. Since

the SP6120B is equipped with 3% window

comparator that takes over the control loop on

transient, the crossover frequency can be se-

lected primarily to the satisfaction of system

stability. Crossover frequency should be higher

than the ESR zero but less than 1/5 of the

switching frequency. The ESR zero is contrib-

uted by the ESR associated with the output

capacitors and can be determined by:

f

Z(ESR)

=

1

2

C

OUT

R

ESR

Crossover frequency of 20kHz is a sound first

try if low ESR tantalum capacitors or poscaps

are used at the output. The next step is to calcu-

late the complex conjugate poles contributed by

the LC output filter,

f

P(LC)

=

1

2

LC

OUT

The open loop gain of the whole system can be

divided into the gain of the error amplifier,

PWM modulator, buck converter, and feedback

resistor divider. In order to crossover at the

selected frequency fco, the gain of the error

amplifier has to compensate for the attenuation

caused by the rest of the loop at this frequency.

In the RC network shown in Figure 18, the

product of R1 and the error amplifier

transconductance determines this gain. There-

fore, R1 can be determined from the following

equation that takes into account the typical error

amplifier transconductance, reference voltage

and PWM ramp built into the SP6120B.

R

1

=

1300V

OUT

f

CO

f

Z(ESR)

V

IN

f

P(LC)

2

18

Date: 5/25/04

SP6120B Low Voltage, AnyFET

TM

, Synchronous, Buck Controller © Copyright 2004 Sipex Corporation

Current Sense

The SP6120B allows sensing current using the

inductor, PCB trace or current-sense resistor.

Inductor-sense utilizes the voltage drop across

the ESR of the inductor, while PCB trace and

current-sense resistor introduce additional re-

sistance in series with the inductor. The resis-

tance of the sense element determines the

overcurrent protection threshold as follows,

I

LIM

= 43mV

R

SEN

R

SEN

= current-sense resistance which can be

implemented as ESR of the inductor, trace or

discrete resistor.

The maximum power dissipation on the current-

sense element is:

SEN

OUT

S EN

R

I

P

2

( max)

=

For the inductor-sense scheme shown in the

application circuit, R

S

and C

S

are used to repli-

cate the signal across the ESR of the inductor. R

S

and C

S

can be looked at as a low pass filter

whose output represents the DC differential

voltage between the switch node and the output.

At steady state, this voltage happens to be the

output current times the ESR of the inductor. In

addition, if the following relationship is satisfied,

L

= R

S

C

S

ESR

the output of the RsCs filter represents the exact

voltage across the ESR, including the ripple.

Since the SP6120B's hiccup overcurrent pro-

tection scheme is intended to safeguard sus-

tained overload conditions, the DC portion of

the current signal is more of interest. Therefore,

designing the R

S

C

S

time constant higher than L/

ESR provides reliable current sense against any

premature triggering due to noise or any tran-

sient conditions. Pick Rs between 10k and 100k,

and Cs can be determined by:

C

S

= 2

L

1

ESR R

S

Here the time constant of R

S

C

S

is twice the value

of L/ESR.

In some applications, it may be desirable to

extend the current sense capability of a given

R

SEN

element (usually the inductor ESR) be-

In Figure 18, R1 and C1 provides a zero f

Z1

which needs to be placed at or below f

P(LC)

. If f

Z1

is made equal to f

P(LC)

for convenience, the

value of C1 can be calculated as

C

1

=

1

2

f

P(LC)

R

1

The optional C2 generates a pole f

P1

with R1 to

cut down high frequency noise for reliable op-

eration. This pole should be placed one decade

higher than the crossover frequency to avoid

erosion of phase margin. Therefore, the value of

the C2 can be derived from

C

2

=

1

20

f

CO

R

1

Figure 19 illustrates the overall loop frequency

response and frequency of each pole and zero.

To fine-tune the compensation, it is necessary to

physically measure the frequency response us-

ing a network analyzer.

Gain

-20db/dec

-40db/dec

-20db/dec

-20db/dec

-20db/dec

Error Amplifier

Loop

f

f

f

Z1

f

P(LC)

f

Z(ESR)

f

CO

f

P1

Figure 19. Frequency response of a stable system and its

error amplifier.

19

Date: 5/25/04

SP6120B Low Voltage, AnyFET

TM

, Synchronous, Buck Controller © Copyright 2004 Sipex Corporation

yond the limit set by the 43mV threshold.

A straight forward way to do this would be to

add a resistor R

S2

in parallel with C

S

, creating a

voltage divider with R

S

. This changes the rela-

tionship with R

S

and C

S

to be

C

S

= 2

L

1

ESR R

S

//R

S2

Using a voltage divider across the inductor, the

new relationship becomes:

I

LIM

=

43mV R

S

+ R

S2

ESR

R

S2

To calculate R

S2

, the formula becomes

R

S2

= R

S

/(

I

LIM

ESR

≠ 1

)

43mV

R

S

C

S

L

V

OUT

SWN

R

S2

ESR

ISP

ISN

Figures 21(A), a voltage divider connected to the V

FB

pin programs the output voltageand 21(B), a simple circuit using

one external voltage reference programs the output voltages to less than 1.25V.

Æ

Æ

Æ

Æ

R1

R2

R2

R1

R3

A

B

V

REF

V

FB

V

FB

V

OUT

< 1.25V

V

OUT

> 1.25V

SP6120B

SP6120B

Figure 20: Current Sensing

Output Voltage Programming

As shown in Figure 21(A), the voltage divider

connecting to the V

FB

pin programs the output

voltage according to

V

OUT

= 1.25( 1 +

R

1

)

R

2

where 1.25V is the internal reference voltage.

Select R2 in the range of 10k to 100k, and R1 can

be calculated using

R

1

=

R

2

(V

OUT

≠ 1.25)

1.25

For output voltage less than 1.25V, a simple

circuit shown in Figure 21(B) can be used in

which V

REF

is an external voltage reference

greater than 1.25V. For simplicity, use the same

resistor value for R1 and R2, then R3 is deter-

mined as follows,

R

3

=

(V

REF

≠ 1.25)R

1

2.5 ≠ V

OUT

20

Date: 5/25/04

SP6120B Low Voltage, AnyFET

TM

, Synchronous, Buck Controller © Copyright 2004 Sipex Corporation

Layout Guideline

PCB layout plays a critical role in proper func-

tion of the converters and EMI control. In switch

mode power supplies, loops carrying high di/dt

give rise to EMI and ground bounces. The goal

of layout optimization is to identify these loops

and minimize them. It is also crucial on how to

connect the controller ground such that its op-

eration is not affected by noise. The following

guideline should be followed to ensure proper

operation.

1. A ground plane is recommended for mini-

mizing noises, copper losses and maximizing

heat dissipation.

2. Connect the ground of feedback divider, com-

pensation components, oscillator resistor and

soft-start capacitor to the GND pin of the IC.

Then connect this pin as close as possible to

the ground of the output capacitor.

3. The V

CC

bypass capacitor should be right

next to the Vcc and GND pin.

4. The traces connecting to feedback resistor

and current sense components should be short

and far away from the switch node, and switch-

ing components.

5. Connect the PGND pin close to the source of

the bottom MOSFET, and the SWN pin to the

source of the top MOSFET. Minimize the

trace between GH/GL and the gates of the

MOSFETs. All of these requirements reduce

the impedance driving the MOSFETs. This is

especially important for the bottom MOSFET

that tends to turn on through its miller capaci-

tor when the switch node swings high.

6. Minimize the loop composed of input capaci-

tors, top/bottom MOSFETs and Schottky di-

ode, This loop carries high di/dt current. Also

increase the trace width to reduce copper

losses.

7. Maximize the trace width of the loop con-

necting the inductor, output capacitors,

Schottky diode and bottom MOSFET.

21

Date: 5/25/04

SP6120B Low Voltage, AnyFET

TM

, Synchronous, Buck Controller © Copyright 2004 Sipex Corporation

PACKAGE:

PLASTIC THIN SMALL

OUTLINE

(TSSOP)

DIMENSIONS

in inches (mm)

Minimum/Maximum

16≠PIN

A

A1

ÿ

L

B

e

A

A1

B

D

E1

e

E2

L

ÿ

- /0.043

(- /1.10)

0.002/0.006

(0.05/0.15)

0.007/0.012

(0.19/0.30)

0.193/0.201

(4.90/5.10)

0.169/0.177

(4.30/4.50)

0.026 BSC

(0.65 BSC)

0.126 BSC

(3.20 BSC)

0.020/0.030

(0.50/0.75)

0∞/8∞

E2

D

E1

22

Date: 5/25/04

SP6120B Low Voltage, AnyFET

TM

, Synchronous, Buck Controller © Copyright 2004 Sipex Corporation

Corporation

ANALOG EXCELLENCE

Sipex Corporation reserves the right to make changes to any products described herein. Sipex does not assume any liability arising out of the

application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.

Sipex Corporation

Headquarters and

Sales Office

22 Linnell Circle

Billerica, MA 01821

TEL: (978) 667-8700

FAX: (978) 670-9001

e-mail: sales@sipex.com

ORDERING INFORMATION

Model

Operating Temperature Range

Package Type

SP6120BCY ............................................. 0∞C to +70∞C ........................................ 16-Pin TSSOP

SP6120BCY/TR ....................................... 0∞C to +70∞C ....................................... 16-Pin TSSOP

SP6120BEY ............................................ -40∞C to +85∞C ...................................... 16-Pin TSSOP

SP6120BEY/TR ...................................... -40∞C to +85∞C ..................................... 16-Pin TSSOP

Available in lead free packaging. To order add "-L" suffix to part number.

Example: SP6120BEY/TR = standard; SP6120BEY-L/TR = lead free

/TR = Tape and Reel

Pack quantity is 1500 for TSSOP.