ST

Sitronix

ST7063C

80CH Segment Driver for Dot Matrix LCD

V1.3a

2001/08/29

1/12

!"

Functions

#"

Dot matrix LCD driver with two 40 channel

outputs

#"

Bias voltage (V1 ~ V4)

#"

input/output signals

!"

Input : Serial display data and control

pulse from controller IC

!"

Output : 40 X 2 channels waveform for

LCD driving

!"

Features

#"

Display driving bias : static to 1/5

#"

Power supply for logic : 2.7V ~ 5.5V

#"

Power supply for LCD voltage (V

DD

~V

EE

) :

3V ~ 11V

100 Pin QFP package and bare chip available

!"

Description

ST7063C is a segment driver for dot matrix type

LCD display. It features 80 channels with 40 X 2

bits bi-directional shift registers, data latches,

LCD drivers and logic control circuits. It is

fabricated by high voltage CMOS process with

low current consumption.

The ST7063C can convert serial data received

from an LCD controller, such as ST7066U, into

parallel data and send out LCD driving

waveforms to the LCD panel. The ST7063C is

designed for general purpose LCD drivers. It can

drive both static and dynamic drive LCD. The LSI

can be used as segment driver.

The ST7063C has pin function compatibility with

the KS0063(B) that allows the user to easily

replace it with an ST7063C.

ST7063C

V1.3a

2001/08/29

2/12

ST7063C Specification Revision Histo

ST7063C Specification Revision Histo

ST7063C Specification Revision Histo

ST7063C Specification Revision History

ry

ry

ry

Version Date

Description

1.1 2000/07/31

First

Edition

1.2

2000/11/14 Added QFP Pad Configuration(Page 6)

1.2a

2001/02/26 Changed Application Circuit(Page 11)

1.3 2001/05/04

1. ST7063 Transition to ST7063C

2. Moved QFP Package Dimensions Page 12 to Page 5

1.3a

2001/08/29 Added "Substrate connect to VDD"(Page 4)

ST7063C

V1.3a

2001/08/29

3/12

!"

Functional Block Diagram

SEGMENT DRIVER

SEGMENT DRIVER

BIDIRECTIONAL

SHIFTER(40bits)

BIDIRECTIONAL

SHIFTER(40bits)

DATA LATCH(40bits)

DATA LATCH(40bits)

CONTOL

V1

V2

V3

V4

CL2

CL1

M

DL1 SHL1 DR1

DL2 SHL2 DR2

V

DD

V

SS

V

EE

S1...............................S40

S41...............................S80

ST7063C

V1.3a

2001/08/29

4/12

!"

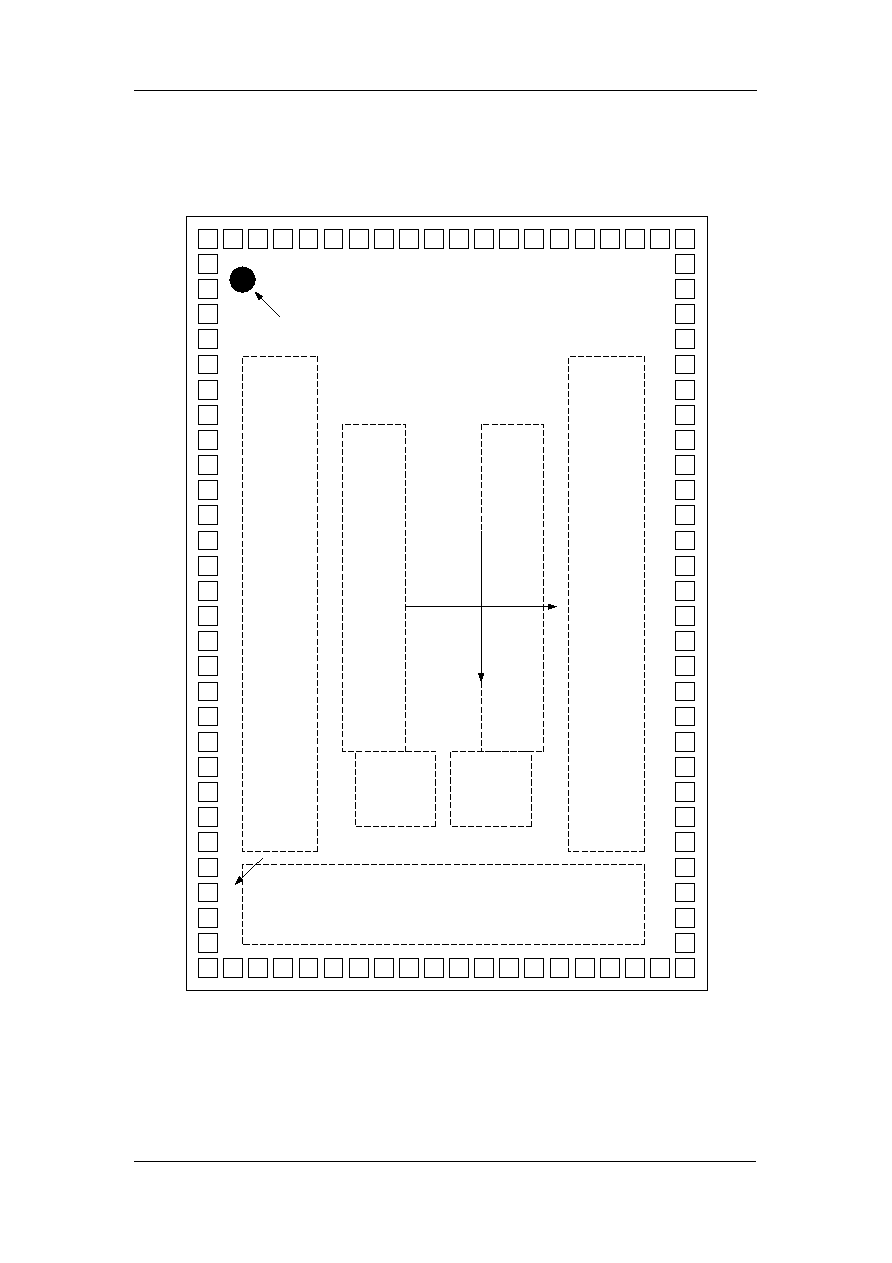

Pad Arrangement

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

96

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

31

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

Size : 3800x2600

m

Coordinate : center

Min. PAD Pitch : 120

m

PAD Size : 90x90

m

(0,0)

Circle here to find the first PAD

G793E

"G793E" Marking : Easy to find the PAD

Substrate connect to VDD.

ST7063C

V1.3a

2001/08/29

5/12

!"

Package Dimensions

ST7063C

V1.3a

2001/08/29

6/12

!"

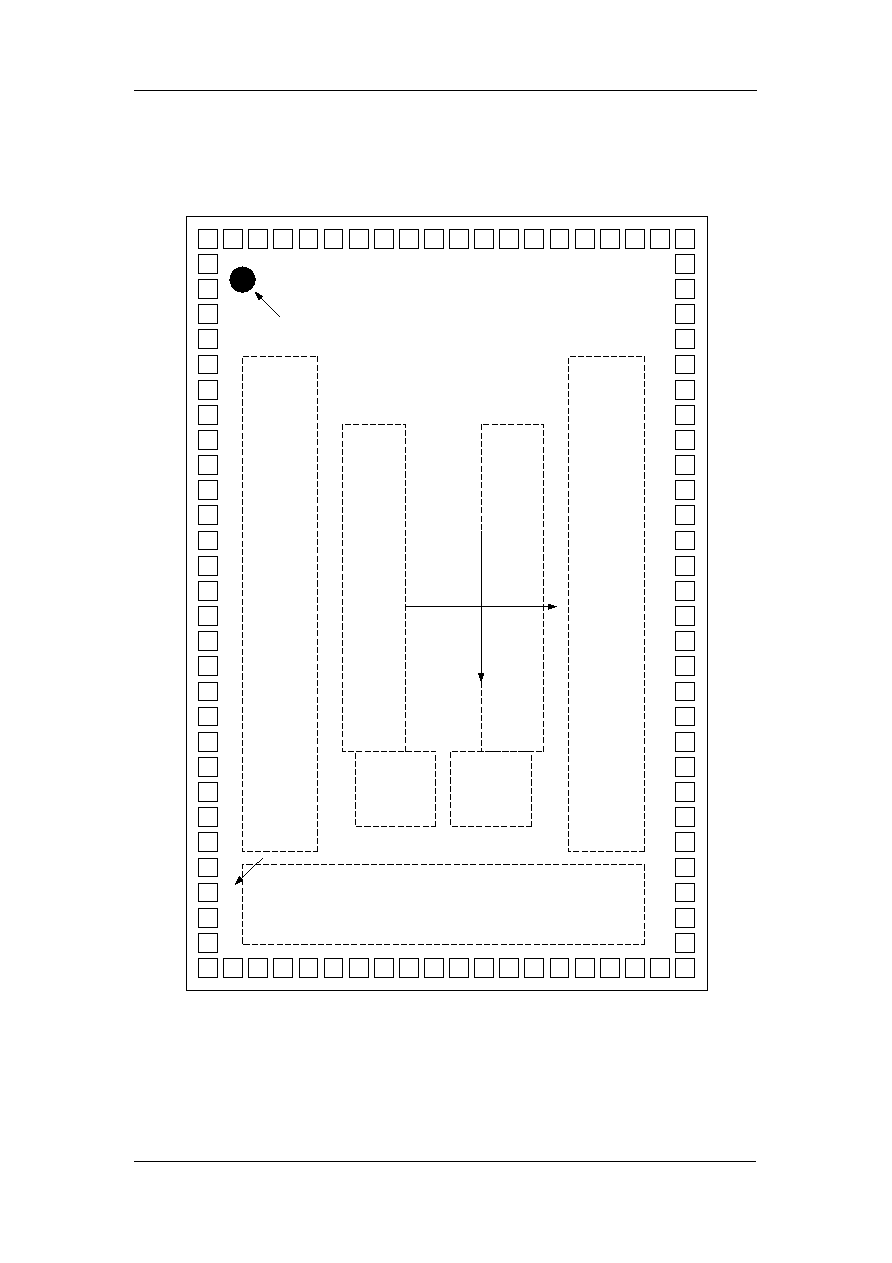

Pin Configuration(QFP 100)

S30

S29

S28

S27

S26

S25

S24

S23

S22

S21

S20

S19

S18

S17

S16

S15

S14

S13

S12

S11

S10

S09

S08

S07

S06

S05

S04

S03

S02

S01

S70

S69

S68

S67

S66

S65

S64

S63

S62

S61

S60

S59

S58

S57

S56

S55

S54

S53

S52

S51

S50

S49

S48

S47

S46

S45

S44

S43

S42

S41

S

3

1

S

3

2

S

3

3

S

3

4

S

3

5

S

3

6

S

3

7

S

3

8

S

3

9

S

4

0

S

8

0

S

7

9

S

7

8

S

7

7

S

7

6

S

7

5

S

7

4

S

7

3

S

7

2

S

7

1

V

E

E

V

1

V

2

V

3

V

4

V

S

S

C

L

1

S

H

L

1

S

H

L

2

N

C

N

C

V

D

D

C

L

2

D

L

1

D

R

1

D

L

2

D

R

2

M N

C

N

C

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

1

0

0

9

9

9

8

9

7

9

6

9

5

9

4

9

3

9

2

9

1

9

0

8

9

8

8

8

6

8

5

8

4

8

3

8

2

8

1

8

7

3

1

3

2

3

3

3

4

3

5

3

6

3

7

3

8

3

9

4

0

4

1

4

2

4

3

4

5

4

6

4

7

4

8

4

9

5

0

4

4

ST7063C

V1.3a

2001/08/29

7/12

!"

Pad Name and Coordinates

Pad No.

Pad No.

Pad No.

Pad No.

Pad

Pad

Pad

Pad

Nam

Nam

Nam

Nameeee

X

X

X

X

Y

Y

Y

Y

Pad No.

Pad No.

Pad No.

Pad No.

Pad

Pad

Pad

Pad

Name

Name

Name

Name

X

X

X

X

Y

Y

Y

Y

Pad No.

Pad No.

Pad No.

Pad No.

Pad

Pad

Pad

Pad

Name

Name

Name

Name

X

X

X

X

Y

Y

Y

Y

1 S42

-1760

-1160

33 S74

1760

-780

65 S15

-180

1160

2 S43

-1630

-1160

34 S75

1760

-660

66 S14

-300

1160

3 S44

-1500

-1160

35 S76

1760

-540

67 S13

-420

1160

4 S45

-1380

-1160

36 S77

1760

-420

68 S12

-540

1160

5 S46

-1260

-1160

37 S78

1760

-300

69 S11

-660

1160

6 S47

-1140

-1160

38 S79

1760

-180

70 S10

-780

1160

7 S48

-1020

-1160

39 S80

1760

-60

71 S9

-900

1160

8 S49

-900

-1160

40 S40

1760

60

72 S8

-1020

1160

9 S50

-780

-1160

41 S39

1760

180

73 S7

-1140

1160

10 S51

-660

-1160

42 S38

1760

300

74 S6

-1260

1160

11 S52

-540

-1160

43 S37

1760

420

75 S5

-1380

1160

12 S53

-420

-1160

44 S36

1760

540

76 S4

-1500

1160

13 S54

-300

-1160

45 S35

1760

660

77 S3

-1630

1160

14 S55

-180

-1160

46 S34

1760

780

78 S2

-1760

1160

15 S56

-60

-1160

47 S33

1760

900

79 S1

-1760

1030

16 S57

60

-1160

48 S32

1760

1030

80 VEE

-1760

900

17 S58

180

-1160

49 S31

1760

1160

81 V1

-1760

780

18 S59

300

-1160

50 S30

1630

1160

82 V2

-1760

660

19 S60

420

-1160

51 S29

1500

1160

83 V3

-1760

540

20 S61

540

-1160

52 S28

1380

1160

84 V4

-1760

420

21 S62

660

-1160

53 S27

1260

1160

85 VSS

-1760

300

22 S63

780

-1160

54 S26

1140

1160

86 CL1

-1760

180

23 S64

900

-1160

55 S25

1020

1160

87 SHL1

-1760

60

24 S65

1020

-1160

56 S24

900

1160

88 SHL2

-1760

-60

25 S66

1140

-1160

57 S23

780

1160

89 VDD

-1760

-180

26 S67

1260

-1160

58 S22

660

1160

90 CL2

-1760

-300

27 S68

1380

-1160

59 S21

540

1160

91 DL1

-1760

-420

28 S69

1500

-1160

60 S20

420

1160

92 DR1

-1760

-540

29 S70

1630

-1160

61 S19

300

1160

93 DL2

-1760

-660

30 S71

1760

-1160

62 S18

180

1160

94 DR2

-1760

-780

31 S72

1760

-1030

63 S17

60

1160

95 M

-1760

-900

32 S73

1760

-900

64 S16

-60

1160

96 S41

-1760

-1030

ST7063C

V1.3a

2001/08/29

8/12

!"

Pin Description

Pin Name

Pin Name

Pin Name

Pin Name Purpose

Purpose

Purpose

Purpose Description

Description

Description

Description I/O

I/O

I/O

I/O

VDD POWER

for

logic

N/A

VSS GROUND

for

logic

N/A

VEE

LCD GND

for LCD driving voltage

N/A

V1 V2

LCD output

used as select voltage level

I

V3 V4

LCD output

used as non select voltage level

I

S1-S40

segment

LCD driver output for part 1

O

SHL1

direction

direction control for part 1 segments

I

DL1, DR1

data in /out

If SHL1 = 1 then DL1=out, DR1=in

If SHL1 = 0 then DL1=in, DR1=out

I/O

S41-S80

segment

LCD driver output for part 2

O

SHL2

direction

direction control for part 2 segments

I

DL2, DR2

data in/out

If SHL2 = 1 then DL2=out, DR2=in

If SHL2 = 0 then DL2=in, DR2=out

I/O

M

alternation

Alternate the LCD driving waveform

I

CL1

latch clock

latch the data after shift is completed

I

CL2

shift clock

shift the data into the segments

I

ST7063C

V1.3a

2001/08/29

9/12

!"

Functional Description

Clock

The CL1 is the clock to latch data on the falling edge. It latches the data input from

the bi-directional shift register at the falling edge of CL1 and transfers its outputs to

the LCD driver circuit. The CL2 is the clock to shift data on the falling edge. It shifts

the serial data at the falling of CL2 and transfers the output of each bit of the register

to the latch circuit.

Shift Registers And Data I/O

The

ST7063C

supplies two sets of 40-bit shift register, which controls the shift

direction by SHL1 & SHL2. The SHL1 controls the 1st 40-bit shift register, and SHL2

controls the 2nd 40-bit shift register. When SHL1 is connected to VDD, the 1st shift

direction is from S40 to S1; when SHL1 is connected to VSS, the shift direction

changes from S1 to S40. When SHL2 is connected to VDD, the 2nd shift direction is

from S80 to S41; when SHL2 is connected to VSS, the shift direction changes from

S41 to S80.

The DL1, DR1, DL2, DR2 are data input or output option function.

Shift Direction of Channel 1

Shift Direction of Channel 1

Shift Direction of Channel 1

Shift Direction of Channel 1

SHL1 Shift

Direction DL1

DR1

0 S1

$ S40

IN

OUT

1 S40

$ S1

OUT

IN

Shift Direction of Channel 2

Shift Direction of Channel 2

Shift Direction of Channel 2

Shift Direction of Channel 2

SHL2 Shift

Direction DL2

DR2

0 S41

$ S80

IN

OUT

1 S80

$ S41

OUT

IN

ST7063C

V1.3a

2001/08/29

10/12

!"

LCD Output Waveforms

!"

Timing Characteristics

Output of LATCH

(DATA)

M

Output

(S1 ~ S80)

V1 V1

V2

V3

V4

V2

V3

V4

CL2

Data in

(DL1, DL2)

(DR1, DR2)

Data out

(DL1, DL2)

(DR1, DR2)

CL1

M

V

IH

V

IL

T

R

T

WCKH

T

F

T

WCKL

T

DH

T

SU

T

D

V

OH

V

OL

T

SL

T

LS

T

LS

T

WCKH

T

R

T

SU

ST7063C

V1.3a

2001/08/29

11/12

!"

D.C Characteristics

Symbol

Symbol

Symbol

Symbol Parameter

Parameter

Parameter

Parameter Test

Condition

Test Condition

Test Condition

Test Condition Min.

Min.

Min.

Min. Typ.

Typ.

Typ.

Typ. Ma

Ma

Ma

Max.

x.

x.

x. Unit

Unit

Unit

Unit Applicable

pin

Applicable pin

Applicable pin

Applicable pin

VDD Operating

Voltage

-

2.7 - 5.5 V

-

VLCD

Driver Supply Voltage

VDD-VEE

3

-

11

V

-

VIH

Input High Voltage

-

0.7

VDD

- VDD V

VIL

Input Low Voltage

-

0

-

0.3

VDD

V

ILKG

Input Leakage Current

VIN =0 ~ VDD

-5

-

5

uA

CL1,CL2,M,SHL1,SHL

2

DL1,DL2,DR1,DR2

VOH

Output High Voltage

IOH = -0.4mA

VDD

-0.4

- - V

VOL

Output Low Voltage

IOL = +0.4mA

-

-

0.4

V

DL1,DL2,DR1,DR2

V1~V4, S1~S80

IDD

Operating Current

FCL2 = 400KHZ

-

100

300

uA

VDD,VEE

IV

Leakage Current

VIN =VDD ~ VEE -10

-

10

uA

V1 ~ V4

!"

A.C Characteristics

Symbol

Symbol

Symbol

Symbol Parameter

Parameter

Parameter

Parameter Test

Condition

Test Condition

Test Condition

Test Condition Min.

Min.

Min.

Min. Max.

Max.

Max.

Max. Unit

Unit

Unit

Unit Applicable

pin

Applicable pin

Applicable pin

Applicable pin

FCL

Data Shift Frequency

-

-

400

KHZ

CL2

TWCKH

Clock High Level Width

-

800

-

ns

CL1,CL2

TWCKL

Clock Low Level Width

-

800

-

ns

CL2

TSL

Clock Set-up Time

CL2 $ CL1

500

-

ns

CL1,CL2

TLS

Clock Set-up Time

CL1 $ CL2

500

-

ns

CL1,CL2

TR/TF

Clock Rise/Fall Time

-

-

200

ns

CL1,CL2

TSU

Data Set-up Time

-

300

-

ns

DL1,DL2,DR1,DR2

TDH

Data Hold Time

-

300

-

ns

DL1,DL2,DR1,DR2

TD

Data Delay Time

CL = 15 PF

-

500

ns

DL1,DL2,DR1,DR2

!"

Maximum Absolute Ratings

Symbol

Symbol

Symbol

Symbol Parameters

Parameters

Parameters

Parameters Min.

Min.

Min.

Min. Max.

Max.

Max.

Max. Unit

Unit

Unit

Unit

VDD Supply

Voltage -0.3

7

V

TOPR Operating

Temperature -20 75

TSTG Storage

Temperature -55 125

ST7063C

V1.3a

2001/08/29

12/12

!"

Application Circuit : (2Line x 40Word)

ST7066U

ST7063C

ST7063C

Dot Matrix LCD Panel

-V or GND

Vcc(+5V)

Regsister

R

egsister

R

egsister

R

egsister

R

egsister

V

R

DB0-DB7

To MPU

V5

V4

V3

V2

V1

M

CL1

CL2

GND

VCC

Seg 1-40

Com 1-16

VEE

VSS

SHL2

SHL1

VDD

DL1

V1

V2

V3

V4

V1

V2

V3

V4

VEE

VSS

SHL2

SHL1

VDD

DL1

M

CL2

CL1

DR1

DL2

DR2

M

CL2

CL1

DR1

DL2

DR2

Seg 1-80

Seg 1-80

Note:

Regsister=2.2K~10K ohm

VR=10K~30Kohm

D