| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: LAN83C180 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

SMSC DS ≠ LAN83C180

Rev. 08/24/2001

LAN83C180

PRELIMINARY

10/100 Fast Ethernet PHY Transceiver

FEATURES

Single Chip 100Base-TX/10Base-T Ethernet

Physical Layer (PHY) Solution

Dual Speed ≠ 10/100 Mbps

Full MII Interface for a Glueless MAC Connection

MI Interface for Configuration and Status

Half Duplex and Full Duplex in Both 10BASE-T and

100BASE-TX

Repeater

Mode

Extended Register Set

Integrated 10BASE-T Transceivers and

Receive/Transmit Filters

Integrated Adaptive Equalizer and Base Line

Wander Correction

Full Auto Negotiation Support for 10BASE-T and

100BASE-TX Both Half and Full Duplex

Parallel Detection for Supporting Non Auto

Negotiation Legacy in Link Partners

Low

Current

Low Power Mode

Internal Power on Reset

Single Magnetics for 10BASE-T and 100BASE-TX

Operation for a Single RJ45 Connector

Support for IEEE-802.3x Flow Control Specification

5 Integrated Status LED Drivers

-

Full

Duplex

-

10/100

-

Activity

-

Collision

-

Link

Low External Component Count

64 Pin TQFP Package (1.0 mm Body Thickness)

GENERAL DESCRIPTION

The LAN83C180 is a single chip CMOS physical layer (PHY) solution providing all necessary functions between the

Media Independent Interface (MII) and the magnetics connected to Category 5 twisted pair media. It is designed for

10BASE-T and 100BASE-TX Ethernet, and is based on the IEEE 802.3 specifications.

The LAN83C180 is compatible with the Auto Negotiation section of IEEE 802.3u and provides all the support needed

for the IEEE 802.3x Full Duplex specification. The LAN83C180 can operate in adapter mode or repeater/switch

modes.

ORDERING INFORMATION

Order Number: LAN83C180 TQFP

64 Pin TQFP Package

SMSC DS ≠ LAN83C180

Page 2

Rev. 08/24/2001

© 2000 STANDARD MICROSYSTEMS CORPORATION (SMSC)

80 Arkay Drive

Hauppauge, NY 11788

(631) 435-6000

FAX (631) 273-3123

Standard Microsystems is a registered trademark of Standard Microsystems Corporation, and SMSC is a trademark of Standard Microsystems

Corporation. Product names and company names are the trademarks of their respective holders. Circuit diagrams utilizing SMSC products are included

as a means of illustrating typical applications; consequently complete information sufficient for construction purposes is not necessarily given. Although

the information has been checked and is believed to be accurate, no responsibility is assumed for inaccuracies. SMSC reserves the right to make

changes to specifications and product descriptions at any time without notice. Contact your local SMSC sales office to obtain the latest specifications

before placing your product order. The provision of this information does not convey to the purchaser of the semiconductor devices described any

licenses under the patent rights of SMSC or others. All sales are expressly conditional on your agreement to the terms and conditions of the most

recently dated version of SMSC's standard Terms of Sale Agreement dated before the date of your order (the "Terms of Sale Agreement"). The product

may contain design defects or errors known as anomalies which may cause the product's functions to deviate from published specifications. Anomaly

sheets are available upon request. SMSC products are not designed, intended, authorized or warranted for use in any life support or other application

where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an

Officer of SMSC and further testing and/or modification will be fully at the risk of the customer. Copies of this document or other SMSC literature, as well

as the Terms of Sale Agreement, may be obtained by visiting SMSC's website at http://www.smsc.com.

SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL IMPLIED WARRANTIES

OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT, AND ANY AND ALL WARRANTIES

ARISING FROM ANY COURSE OF DEALING OR USAGE OF TRADE.

IN NO EVENT SHALL SMSC BE LIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES;

OR FOR LOST DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND; REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON

CONTRACT; TORT; NEGLIGENCE OF SMSC OR OTHERS; STRICT LIABILITY; BREACH OF WARRANTY; OR OTHERWISE; WHETHER OR

NOT ANY REMEDY IS HELD TO HAVE FAILED OF ITS ESSENTIAL PURPOSE, AND WHETHER OR NOT SMSC HAS BEEN ADVISED OF THE

POSSIBILITY OF SUCH DAMAGES.

SMSC DS ≠ LAN83C180

Page 3

Rev. 08/24/2001

TABLE OF CONTENTS

FEATURES ................................................................................................................................................................... 1

GENERAL DESCRIPTION............................................................................................................................................ 1

PIN CONFIGURATION ................................................................................................................................................. 4

DESCRIPTION OF PIN FUNCTIONS ........................................................................................................................... 5

FUNCTIONAL DESCRIPTION...................................................................................................................................... 7

25MHz Reference Clock ............................................................................................................................................ 7

10BASE-T OPERATION ............................................................................................................................................... 7

10Mb/s Data Transfer on the MII ............................................................................................................................... 7

RX10 Clock Recovery................................................................................................................................................ 7

100MHz Synthesizer.................................................................................................................................................. 7

TX10 Pulse Shaper & Filter ....................................................................................................................................... 7

TX10 Latency............................................................................................................................................................. 7

RX10 Filter & RX10 Signal Detect ............................................................................................................................. 7

RX10 Latency ............................................................................................................................................................ 8

100BASE-TX OPERATION........................................................................................................................................... 8

100Mb/s Data Exchange on the MII Interface............................................................................................................ 8

125MHz Synthesizer.................................................................................................................................................. 8

TX100 PISO, Encoder and Scrambler ....................................................................................................................... 8

TX100 Driver.............................................................................................................................................................. 8

TX100 Latency........................................................................................................................................................... 8

RX100 Equalizer & Base-line Wander Correction ..................................................................................................... 8

RX100 Clock Recovery.............................................................................................................................................. 8

RX100 SIPO, Decoder and Descrambler .................................................................................................................. 9

RX100 Latency .......................................................................................................................................................... 9

100Mb/s Transmit Errors ........................................................................................................................................... 9

100Mb/s Receive Errors ............................................................................................................................................ 9

CONTROLS ................................................................................................................................................................ 10

Initialization (nRESET)............................................................................................................................................. 10

Reset Mode ............................................................................................................................................................. 10

Low-Power Mode ..................................................................................................................................................... 10

Loopback Mode ....................................................................................................................................................... 10

Repeater Mode ........................................................................................................................................................ 10

ICFG - Interrupt........................................................................................................................................................ 11

Auto-Negotiation Enable (ANEN)............................................................................................................................. 11

MII Management Interface ....................................................................................................................................... 11

MANAGEMENT .......................................................................................................................................................... 13

MAC Access to PHY Management Registers .......................................................................................................... 13

RESISTER SET ....................................................................................................................................................... 13

OPERATING CONDITIONS........................................................................................................................................ 18

MAXIMUM GUARANTEED RATINGS*.................................................................................................................... 18

DC ELECTRICAL CHARACTERISTICS .................................................................................................................. 18

DIFFERENTIAL OUTPUT........................................................................................................................................ 18

AC ELECTRICAL CHARACTERISTICS .................................................................................................................. 19

REFCLK................................................................................................................................................................... 19

RX_CLK................................................................................................................................................................... 19

TX_CLK ................................................................................................................................................................... 19

MDC......................................................................................................................................................................... 19

EXTERNAL COMPONENTS....................................................................................................................................... 20

Connecting an External 25MHz Reference.............................................................................................................. 20

nRESET Pull-up Resistor......................................................................................................................................... 20

RX Input Decoupling................................................................................................................................................ 20

Crystal Oscillator...................................................................................................................................................... 20

PACKAGE DETAILS .................................................................................................................................................. 21

LAN83C180 REVISIONS ............................................................................................................................................ 22

SMSC DS ≠ LAN83C180

Page 4

Rev. 08/24/2001

PIN CONFIGURATION

FIGURE 1 ≠ SYSTEM BLOCK DIAGRAM

RXGND1

RX

I

P

RXI

N

R

X

VDD1

RPTR

AN

E

N

IC

F

G

T

X

VDD1

TX

ON

TX

O

P

T

X

GND1

T

X

GND2

PA

2

PA

1

PA

0

SUB

V

DD

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

TX_ER

TX

D

3

TXD2

TX

D

1

TXD0

RX

_

E

R

RXD

3

RXD2

RXD

1

RXD0

D

V

DD2

DGND2

RX

_

C

L

K

RX_D

V

CR

S

COL

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

LAN83C180

64 Pin TQFP

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

RXEN

DVDD3

MDC

MDIO

DGND3

RefCLK

OSCVDD

XTAL1

XTAL2

OSCGND

TXGND4

TXVDD4

TXVDD3

TXGND3

TxRef100

TxRef10

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

TX_CLK

DGND1

TX_EN

FDST

LNKST

SPDST

ACTST/MINT

COLST/MINT

DVDD1

RXGND3

RXVDD3

PA4

nRESET

RXVDD2

RXGND2

PA3

LAN83C180

Isolation

Magnetics

RJ45

Fast Ethernet MAC

(LAN91C100FD, LAN91C110,

LAN83C171, or other MII compliant MAC)

SMSC DS ≠ LAN83C180

Page 5

Rev. 08/24/2001

DESCRIPTION OF PIN FUNCTIONS

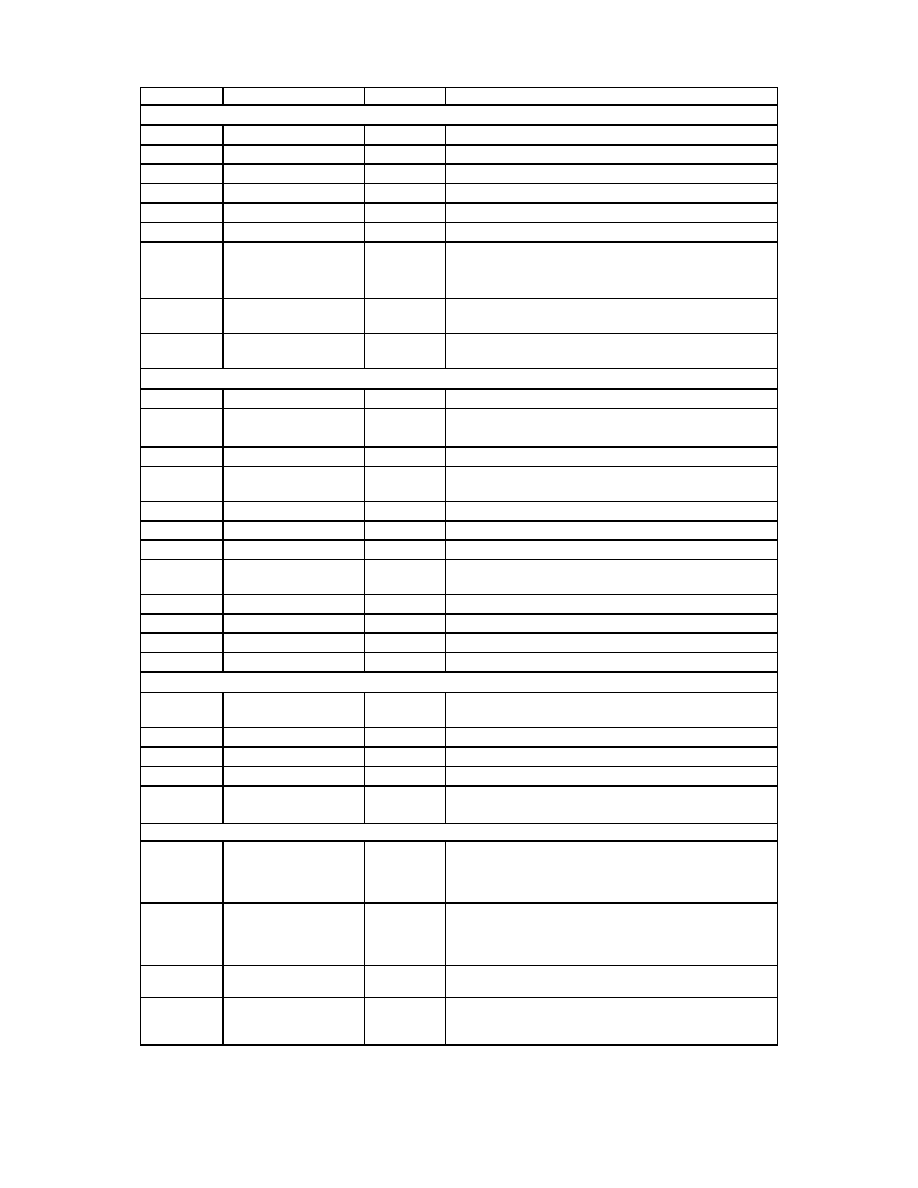

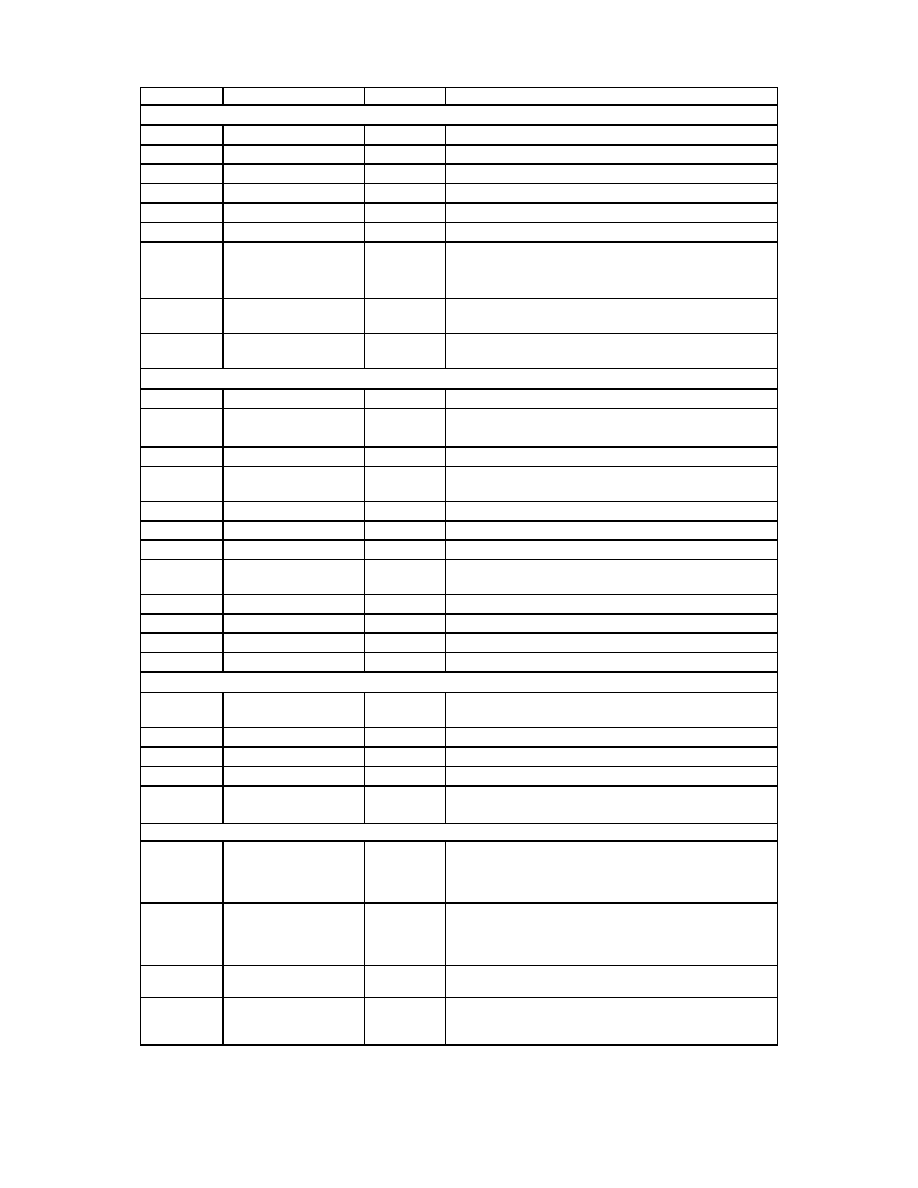

PIN #

NAME

TYPE

DESCRIPTION

MD INTERFACE

19

RXIN

Diff. Input

Differential receive pair from magnetics (-)

18

RXIP

Diff. Input

Differential receive pair from magnetics (+)

25

TXON

Diff. Output 100 Differential transmit pair to magnetics (-)

26

TXOP

Diff. Output 100 Differential transmit pair to magnetics (+)

33

TXREF10

Input

10BASE-T transmitter current setting pin

34

TXREF100

Input

100BASE-TX transmitter current setting pin

13

nRESET

Input/

Output

Active low, power-on reset output and external reset

input.

41

XTAL1

Input

25MHz crystal input. This signal should be pulled

high when using REFCLK.

40

XTAL2

Input

25MHz crystal input. This signal should be left

unconnected when using REFCLK.

MII INTERFACE

46

MDC

Input

Management interface clock (up to 2.5MHz)

45

MDIO

Input/

OUTPUT

Management data

52

RX_CLK

Output

Receive clock (2.5MHz for 10, 25MHz for 100)

55,56,57,5

8

RXD0,RXD1,RXD2,

RXD3

Output

Receive data MII interface

51

RX_DV

Output

Receive data valid. Active high

59

RX_ER

Output

Receive error. Active high. (RXD4 in symbol mode)

1

TX_CLK

Output

Transmit clock (2.5MHz for 10, 25MHz for 100)

60,61,62,6

3

TXD0,TXD1,TXD2,T

XD3

Input

Transmit Data MII interface

3

TX_EN

Input

Transmit Enable. Active high

64

TX_ER

Input

Transmit Error. Active high. (TXD4 in symbol mode)

50

CRS

Output

Carrier sense signal. Active high

49

COL

Output

Collision signal. Active high

MISCELLANEOUS

43

REFCLK

Input

Reference clock. This signal should be pulled high

when using crystal.

22

ANEN

Input

Auto Negotiation enable. Active high

48

RXEN

Input

Receive enable. Active high

21

RPTR

Input

Repeater enable. Active high

31,30,29,1

6,12

PA0,PA1,

PA2,PA3,PA4

Input

PHY address

MISCELLANEOUS/LED

4

FDST

Input/

OUTPUT

Full duplex LED status indication when nRESET

high. Active low. Input when nRESET is low. High

input means the LAN83C180 advertises full duplex

capability

6

SPDST

Input

Speed (10/100) LED status indication when

nRESET high. High for 100Mb/s mode. Input when

nRESET is low. Low input will cause the

LAN83C180 to advertise 100Mb/s capability.

23

ICFG

Input

Interrupt configuration. MINT on pin 8 when High,

on pin 7 when Low.

7

ACTST/MINT

Output

Receive/Transmit activity LED status indication

(Active Low) if ICFG = 1. If ICFG = 0, output is

MINT and activity is indicated on the LNKST output.