i

TABLE OF CONTENTS

1

GENERAL DESCRIPTION................................................................................................................. 1

2

FEATURES ........................................................................................................................................ 2

2.1

Integrated Display Buffer ......................................................................................................... 2

2.2

CPU Interface............................................................................................................................. 2

2.3

Display Support......................................................................................................................... 2

2.4

Display Modes........................................................................................................................... 2

2.5

Display Features ....................................................................................................................... 2

2.6

Clock Source ............................................................................................................................. 3

2.7

Miscellaneous............................................................................................................................ 3

2.8

Package...................................................................................................................................... 3

3

ORDERING INFORMATION.............................................................................................................. 3

4

BLOCK DIAGRAM............................................................................................................................. 4

4.1

PIN ARRANGEMENT................................................................................................................. 5

4.1.1

100 pin TQFP ...................................................................................................................... 5

4.1.2

100 pin TFBGA ................................................................................................................... 7

5

PIN DESCRIPTION ............................................................................................................................ 9

5.1

Host Interface .......................................................................................................................... 10

5.2

LCD Interface........................................................................................................................... 12

5.3

Clock Input............................................................................................................................... 13

5.4

Miscellaneous.......................................................................................................................... 13

5.5

Power and Ground .................................................................................................................. 13

5.6

Summary of Configuration Options...................................................................................... 14

5.7

Host Bus Interface Pin Mapping............................................................................................ 14

5.8

LCD Interface Pin Mapping .................................................................................................... 15

5.9

Data Bus Organization ........................................................................................................... 16

ii

6

FUNCTIONAL BLOCK DESCRIPTIONS ........................................................................................ 17

6.1

MCU Interface .......................................................................................................................... 17

6.2

Control Register ...................................................................................................................... 17

6.3

Display Output......................................................................................................................... 17

6.4

Display Buffer.......................................................................................................................... 17

6.5

PWM Clock and CV Pulse Control......................................................................................... 17

6.6

Clock Generator ...................................................................................................................... 17

7

REGISTERS ..................................................................................................................................... 18

7.1

Register Mapping.................................................................................................................... 18

7.2

Register Descriptions............................................................................................................. 18

7.2.1

Read-Only Configuration Registers............................................................................... 18

7.2.2

Clock Configuration Registers ....................................................................................... 19

7.2.3

Look-Up Table Registers ................................................................................................ 20

7.2.4

Panel Configuration Registers ....................................................................................... 24

7.2.5

Display Mode Registers .................................................................................................. 37

7.2.6

Main Window Registers .................................................................................................. 40

7.2.7

Floating Window Registers............................................................................................. 41

7.2.8

Miscellaneous Registers................................................................................................. 47

7.2.9

General IO Pins Registers............................................................................................... 48

7.2.10

Pulse Width Modulation (PWM) Clock and Contrast Voltage (CV) Pulse

Configuration Registers................................................................................................................. 52

7.2.11

Cursor Mode Registers ................................................................................................... 55

8

MAXIMUM RATINGS ....................................................................................................................... 66

9

DC CHARACTERISTICS ................................................................................................................. 67

10

AC CHARACTERISTICS ................................................................................................................. 67

10.1

Clock Timing............................................................................................................................ 68

10.1.1

Input Clocks ..................................................................................................................... 68

10.1.2

Internal Clocks ................................................................................................................. 69

10.2

CPU Interface Timing.............................................................................................................. 70

10.2.1

Generic #1 Interface Timing............................................................................................ 70

10.2.2

Generic #2 Interface Timing (e.g. ISA) ........................................................................... 72

iii

10.2.3

Motorola MC68K #1 Interface Timing (e.g. MC68000) .................................................. 74

10.2.4

Motorola DragonBall Interface Timing with DTACK# (e.g. MC68EZ328/MC68VZ328)

76

10.2.5

Motorola DragonBall Interface Timing without DTACK# (e.g.

MC68EZ328/MC68VZ328) ............................................................................................................... 78

10.2.6

Hitachi SH-3 Interface Timing (e.g. SH7709A) .............................................................. 80

10.2.7

Hitachi SH-4 Interface Timing (e.g. SH7751) ................................................................. 82

10.3

LCD Power Sequencing ......................................................................................................... 84

10.3.1

Passive/TFT Power-On Sequence.................................................................................. 84

10.3.2

Passive/TFT Power-Off Sequence.................................................................................. 85

10.3.3

Power Saving Status ....................................................................................................... 86

10.4

Display Interface ..................................................................................................................... 87

10.4.1

Generic STN Panel Timing.............................................................................................. 88

10.4.2

Monochrome 4-Bit Panel Timing.................................................................................... 90

10.4.3

Monochrome 8-Bit Panel Timing.................................................................................... 93

10.4.4

Color 4-Bit Panel Timing ................................................................................................. 96

10.4.5

Color 8-Bit Panel Timing (Format stripe) ...................................................................... 99

10.4.6

Generic TFT Panel Timing ............................................................................................ 102

10.4.7

9/12/18-Bit TFT Panel Timing........................................................................................ 103

10.4.8

160x160 Sharp HR-TFT Panel Timing (e.g. LQ031B1DDxx) ...................................... 107

10.4.9

Generic HR-TFT Panel Timing ...................................................................................... 111

10.4.10

160x234 Analog TFT Panel Timing (e.g. UP025D10)................................................. 113

11

CLOCKS......................................................................................................................................... 115

11.1

Clock Descriptions ............................................................................................................... 115

11.1.1

BCLK ............................................................................................................................... 115

11.1.2

MCLK............................................................................................................................... 116

11.1.3

PCLK ............................................................................................................................... 116

11.1.4

PWMCLK.........................................................................................................................118

11.2

Clocks versus Functions ..................................................................................................... 118

12

POWER SAVING MODE................................................................................................................ 119

13

FRAME RATE CALCULATION ..................................................................................................... 119

14

DISPLAY DATA FORMATS .......................................................................................................... 120

iv

15

LOOK-UP TABLE ARCHITECTURE............................................................................................. 121

15.1

Monochrome Modes ............................................................................................................. 121

15.1.1

1 Bit-per-pixel Monochrome Mode............................................................................... 121

15.1.2

2 Bit-per-pixel Monochrome Mode............................................................................... 121

15.1.3

4 Bit-per-pixel Monochrome Mode............................................................................... 122

15.1.4

8 Bit-per-pixel Monochrome Mode............................................................................... 122

15.1.5

16 Bit-Per-Pixel Monochrome Mode ............................................................................ 122

15.2

Color Modes .......................................................................................................................... 123

15.2.1

1 Bit-Per-Pixel Color ...................................................................................................... 123

15.2.2

2 Bit-Per-Pixel Color ...................................................................................................... 124

15.2.3

4 Bit-Per-Pixel Color ...................................................................................................... 125

15.2.4

8 Bit-per-pixel Color Mode ............................................................................................ 126

15.2.5

16 Bit-Per-Pixel Color Mode.......................................................................................... 127

16

ANALOG TFT INTERFACE ........................................................................................................... 127

17

BIG-ENDIAN BUS INTERFACE .................................................................................................... 127

17.1

Byte Swapping Bus Data...................................................................................................... 127

17.1.1

16 Bpp Color Depth ....................................................................................................... 129

17.1.2

1/2/4/8 Bpp Color Depth ................................................................................................ 129

18

VIRTUAL DISPLAY MODE............................................................................................................ 130

19

DISPLAY ROTATE MODE............................................................................................................. 131

19.1

90� Display Rotate Mode ...................................................................................................... 131

19.1.1

Register Programming .................................................................................................. 131

19.2

180� Display Rotate Mode .................................................................................................... 132

19.2.1

Register Programming .................................................................................................. 132

19.3

270� Display Rotate Mode .................................................................................................... 133

19.3.1

Register Programming .................................................................................................. 133

20

FLOATING WINDOW MODE......................................................................................................... 134

20.1

With Display Rotate Mode Enabled..................................................................................... 135

20.1.1

Display Rotate Mode 90� ............................................................................................... 135

20.1.2

Display Rotate Mode 180� ............................................................................................. 135

20.1.3

Display Rotate Mode 270� ............................................................................................. 136

v

21

HARDWARE CURSOR MODE...................................................................................................... 137

21.1

With Display Rotate Mode Enabled..................................................................................... 138

21.1.1

Display Rotate Mode 90

�

�

�

� ............................................................................................... 138

21.1.2

Display Rotate Mode 180

�

�

�

� ............................................................................................. 139

21.1.3

Display Rotate Mode 270

�

�

�

� ............................................................................................. 139

21.2

Pixel format (Normal orientation mode) ............................................................................. 139

21.2.1

4/8/16 Bit-per-pixel......................................................................................................... 140

21.3

Pixel format (90� Display Rotate Mode) .............................................................................. 140

21.3.1

4 Bit-per-pixel ................................................................................................................. 140

21.3.2

8 Bit-per-pixel ................................................................................................................. 141

21.3.3

16 Bit-per-pixel ............................................................................................................... 141

21.4

Pixel format (180� Display Rotate Mode) ............................................................................ 142

21.4.1

4 Bit-per-pixel ................................................................................................................. 142

21.4.2

8 Bit-per-pixel ................................................................................................................. 142

21.4.3

16 Bit-per-pixel ............................................................................................................... 143

21.5

Pixel format (270� Display Rotate Mode) ............................................................................ 143

21.5.1

4 Bit-per-pixel ................................................................................................................. 143

21.5.2

8 Bit-per-pixel ................................................................................................................. 144

21.5.3

16 Bit-per-pixel ............................................................................................................... 144

22

APPLICATION EXAMPLES .......................................................................................................... 145

23

APPENDIX ..................................................................................................................................... 151

23.1

Package Mechanical Drawing for 100 pins TQFP.............................................................. 151

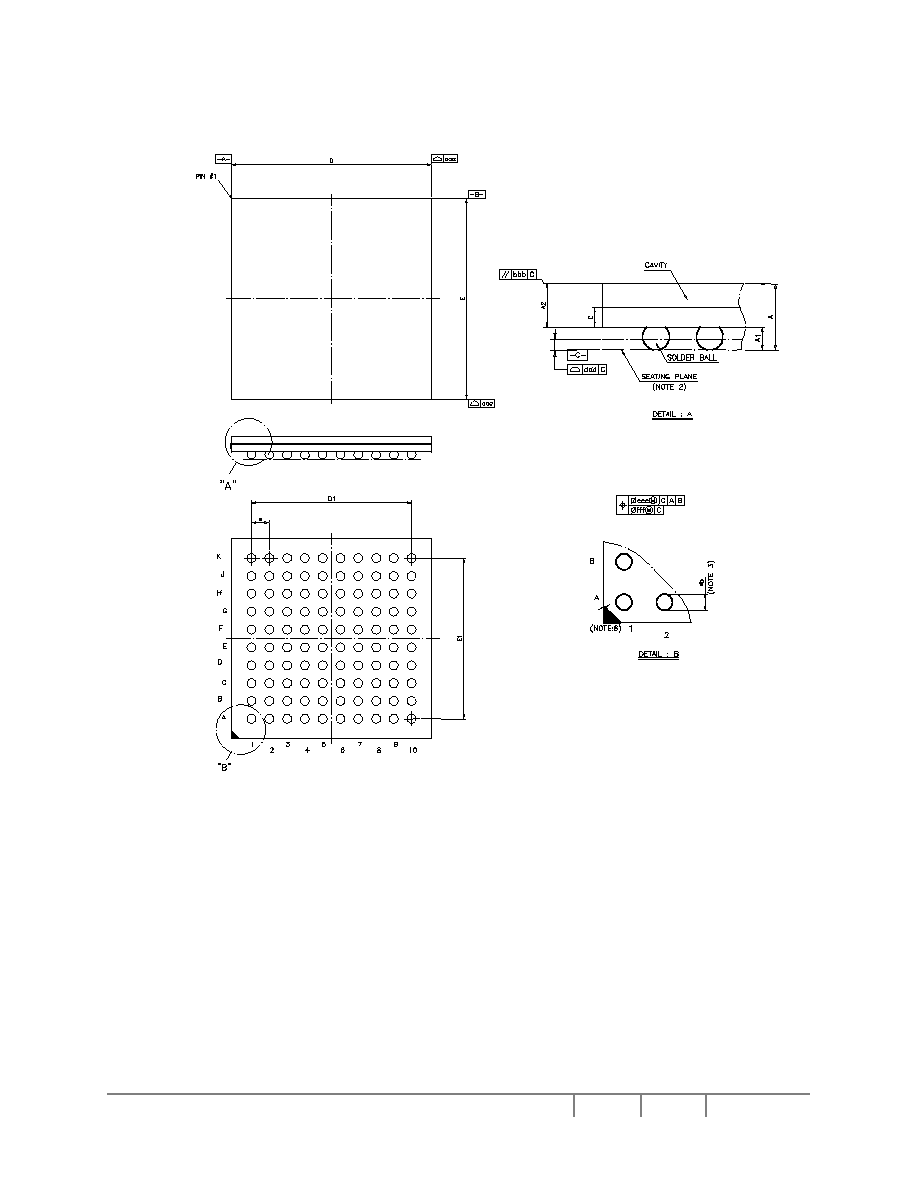

23.2

Package Mechanical Drawing for 100 pins TFBGA........................................................... 152

23.3

Register Table ....................................................................................................................... 154

vi

List of Figures

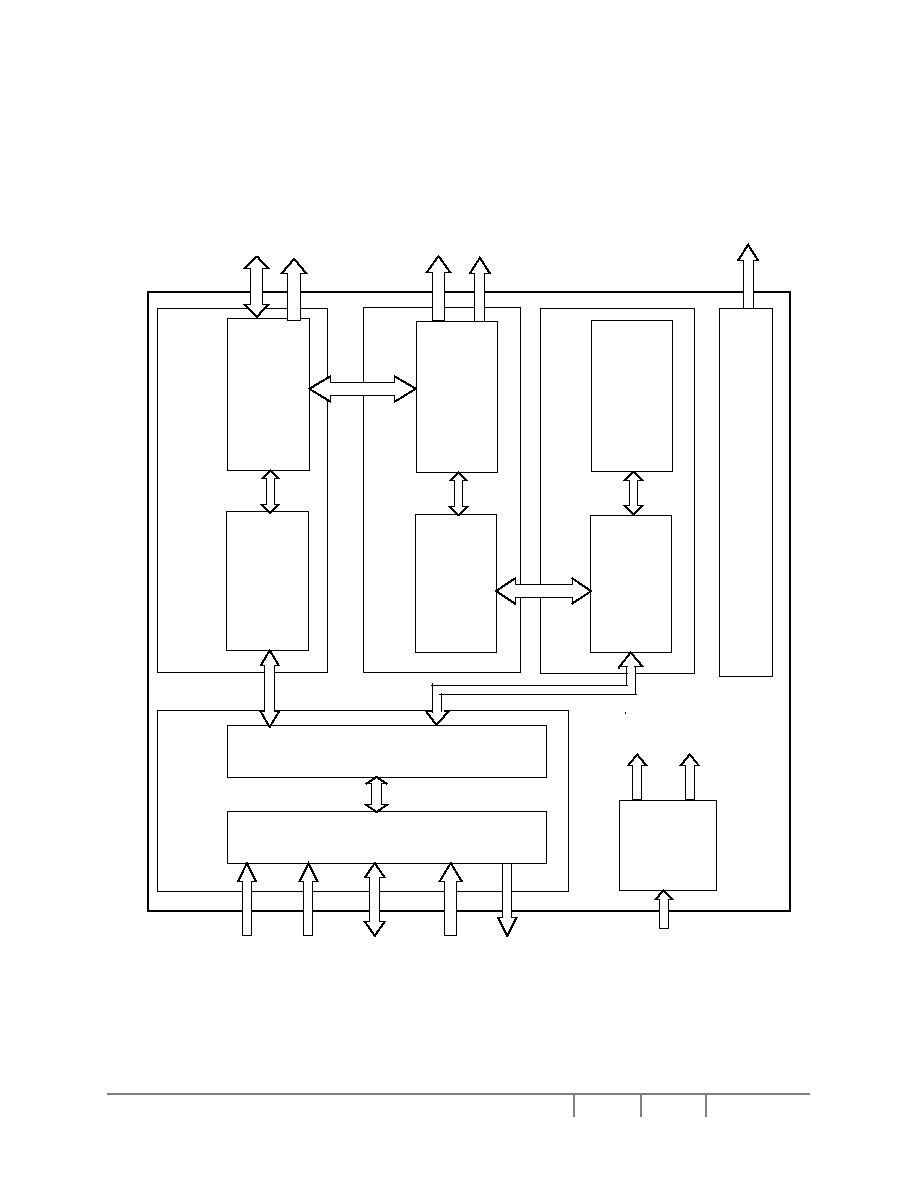

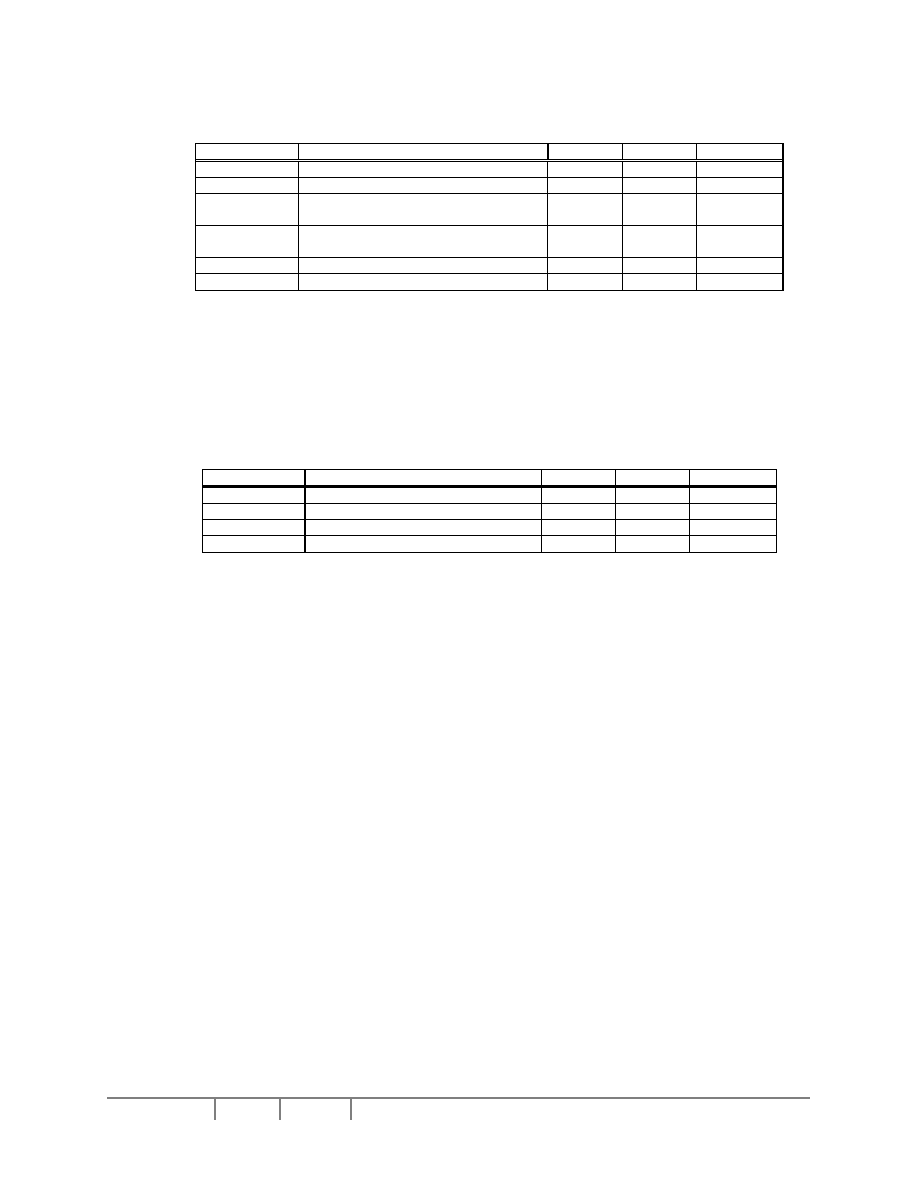

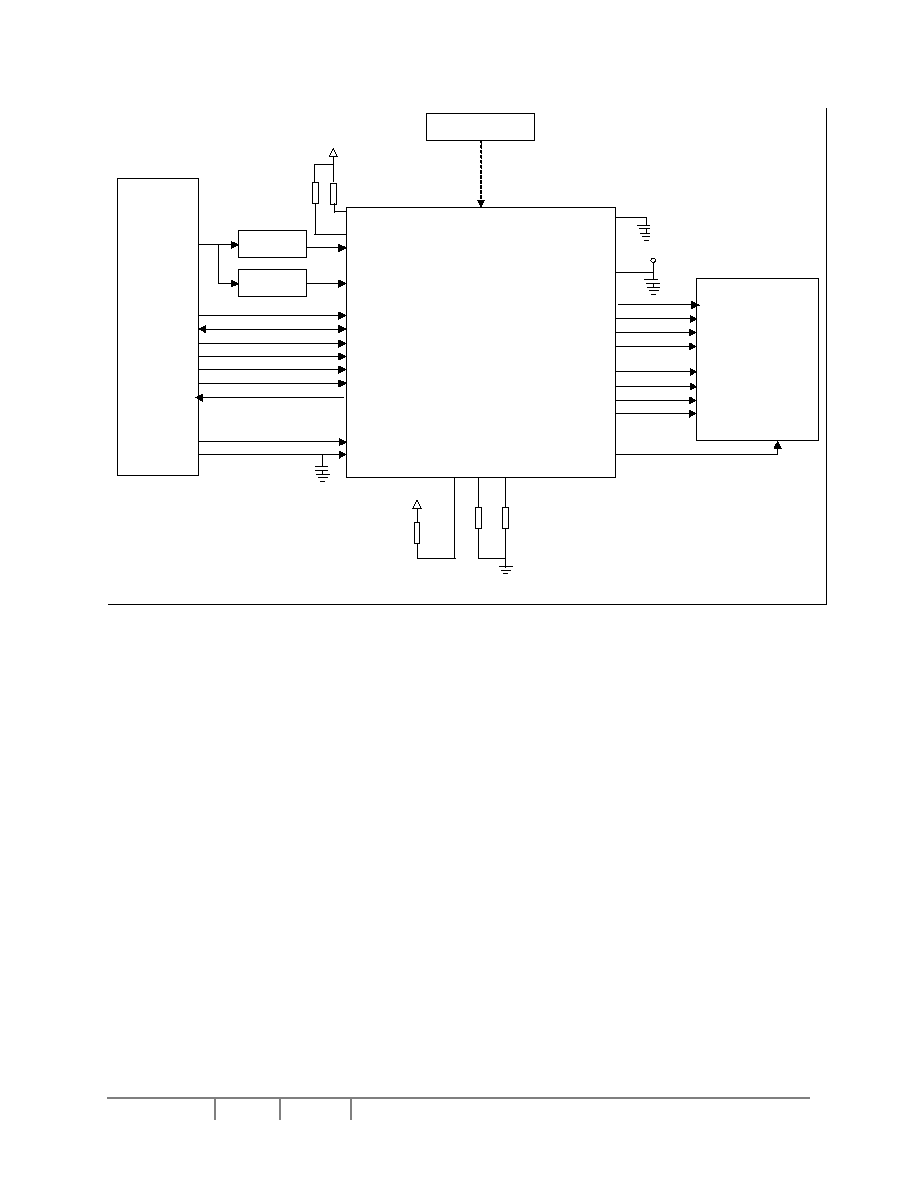

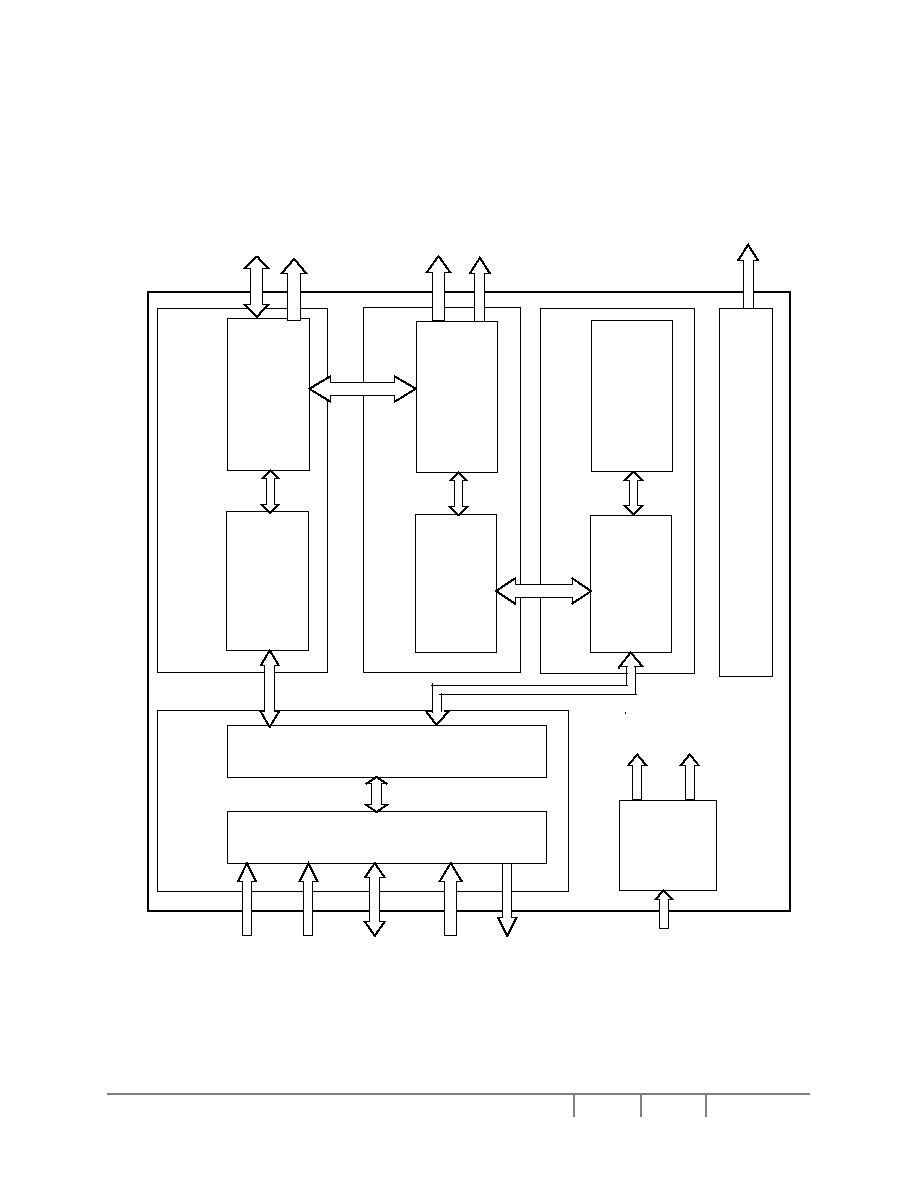

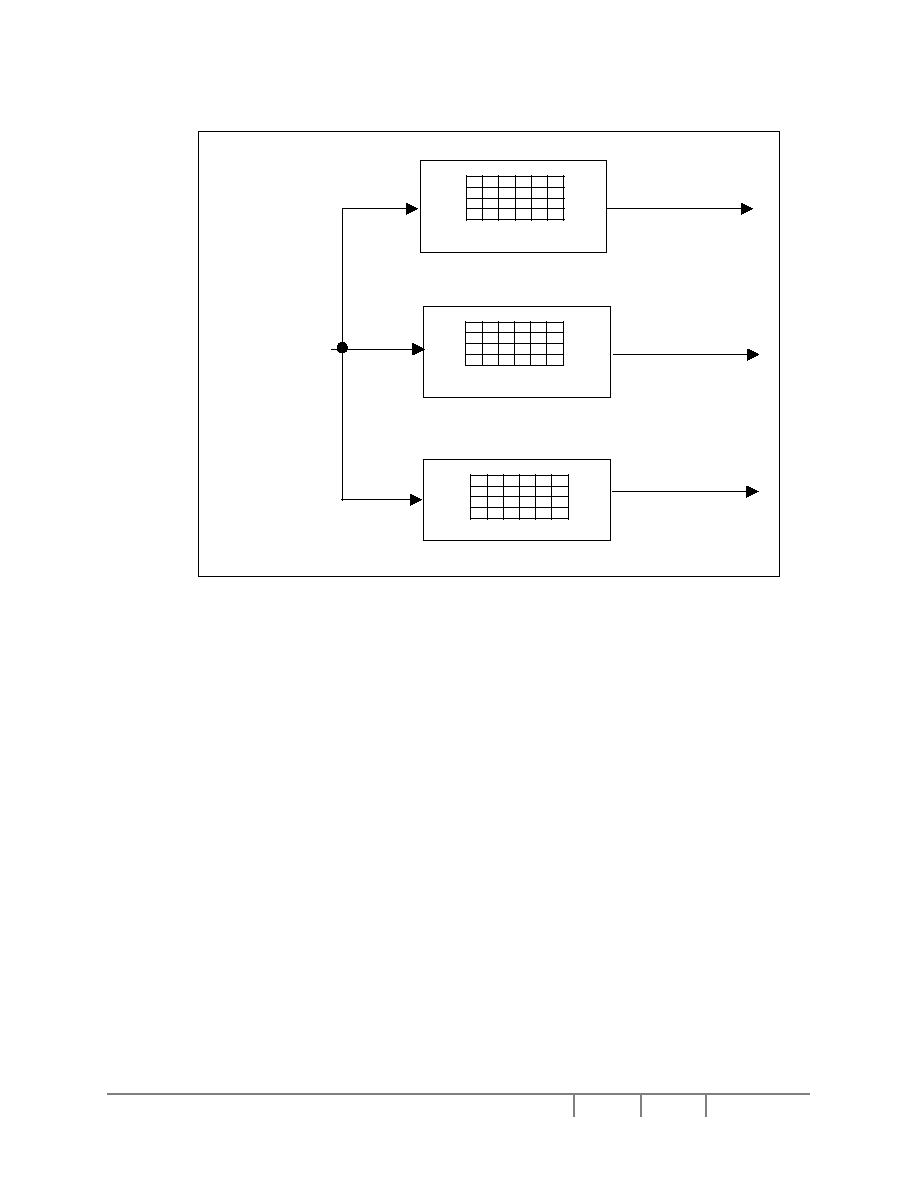

Figure 4-1 : Block Diagram ........................................................................................................................... 4

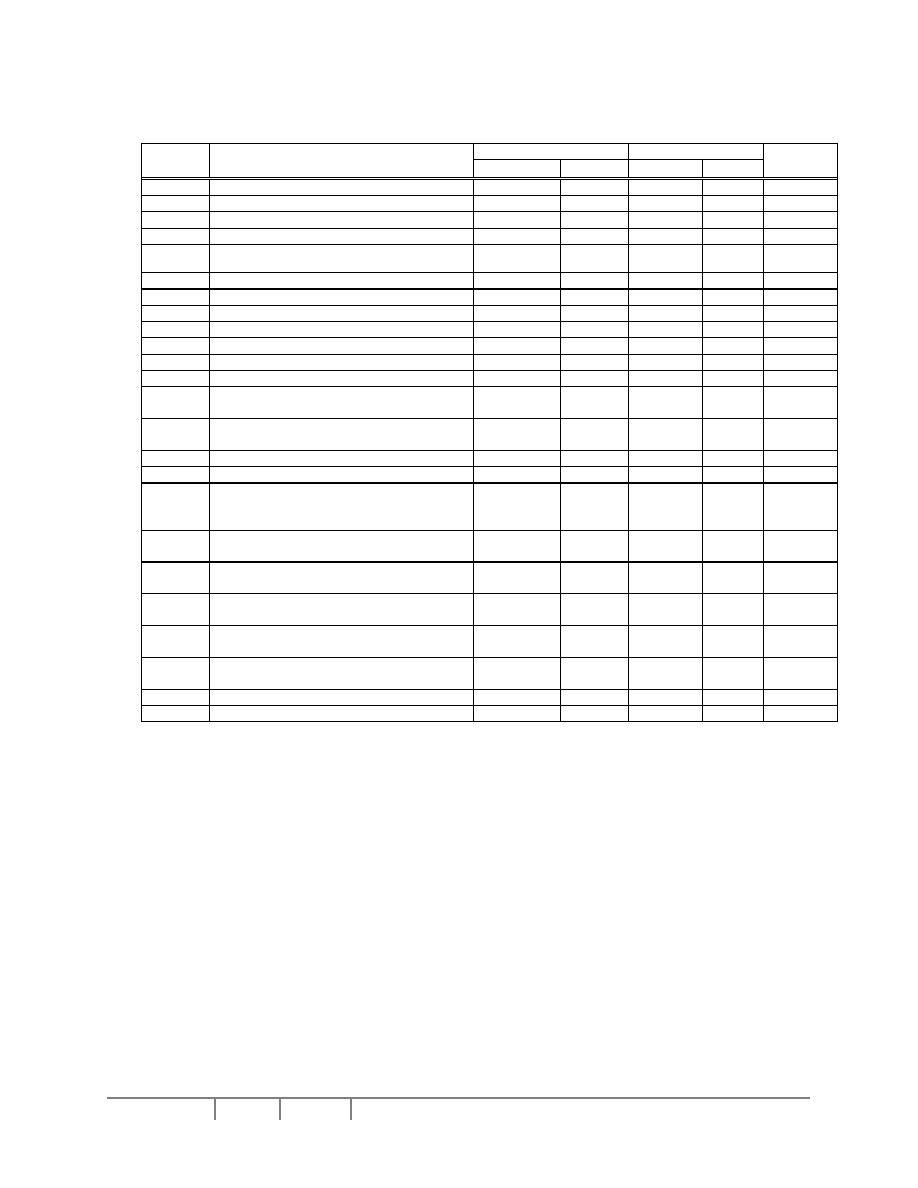

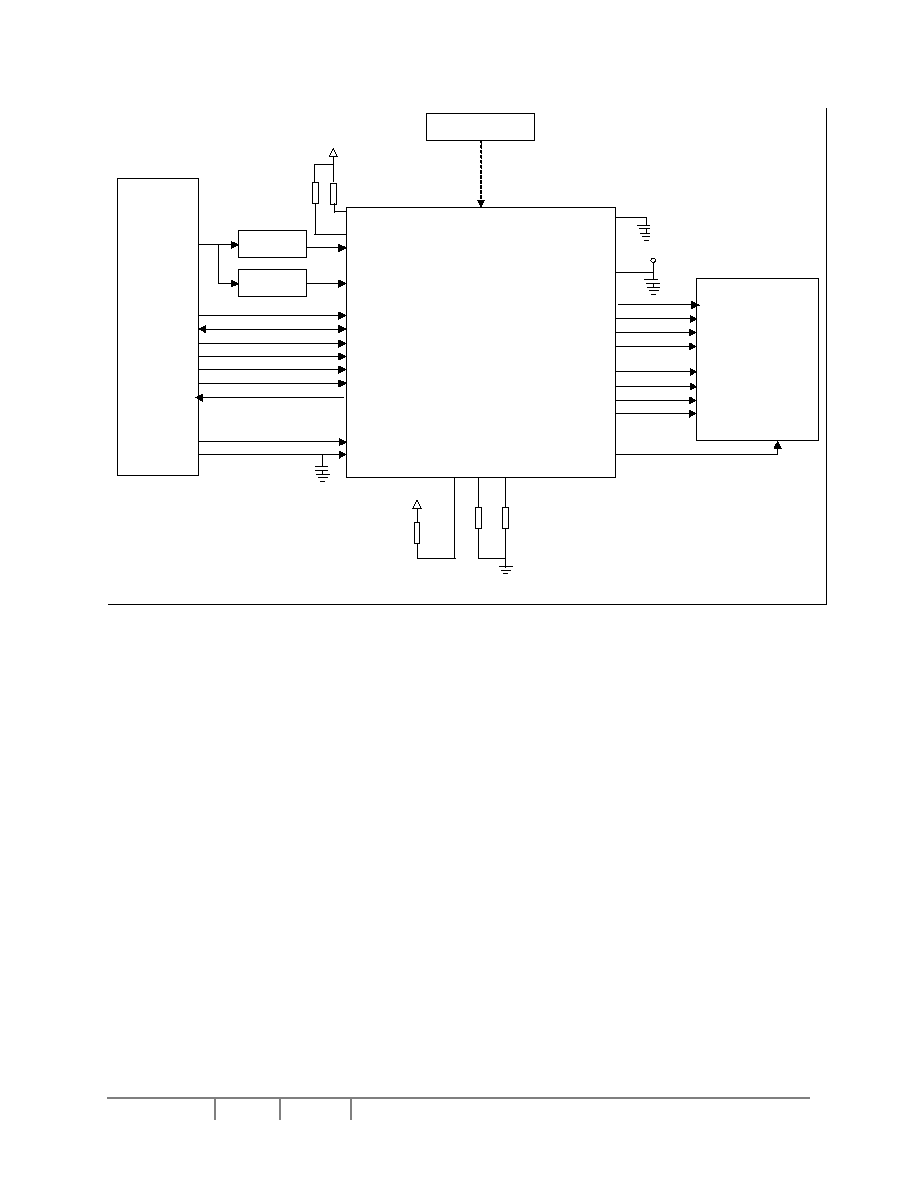

Figure 4-2 : Pinout Diagram � 100 pin TQFP ............................................................................................... 5

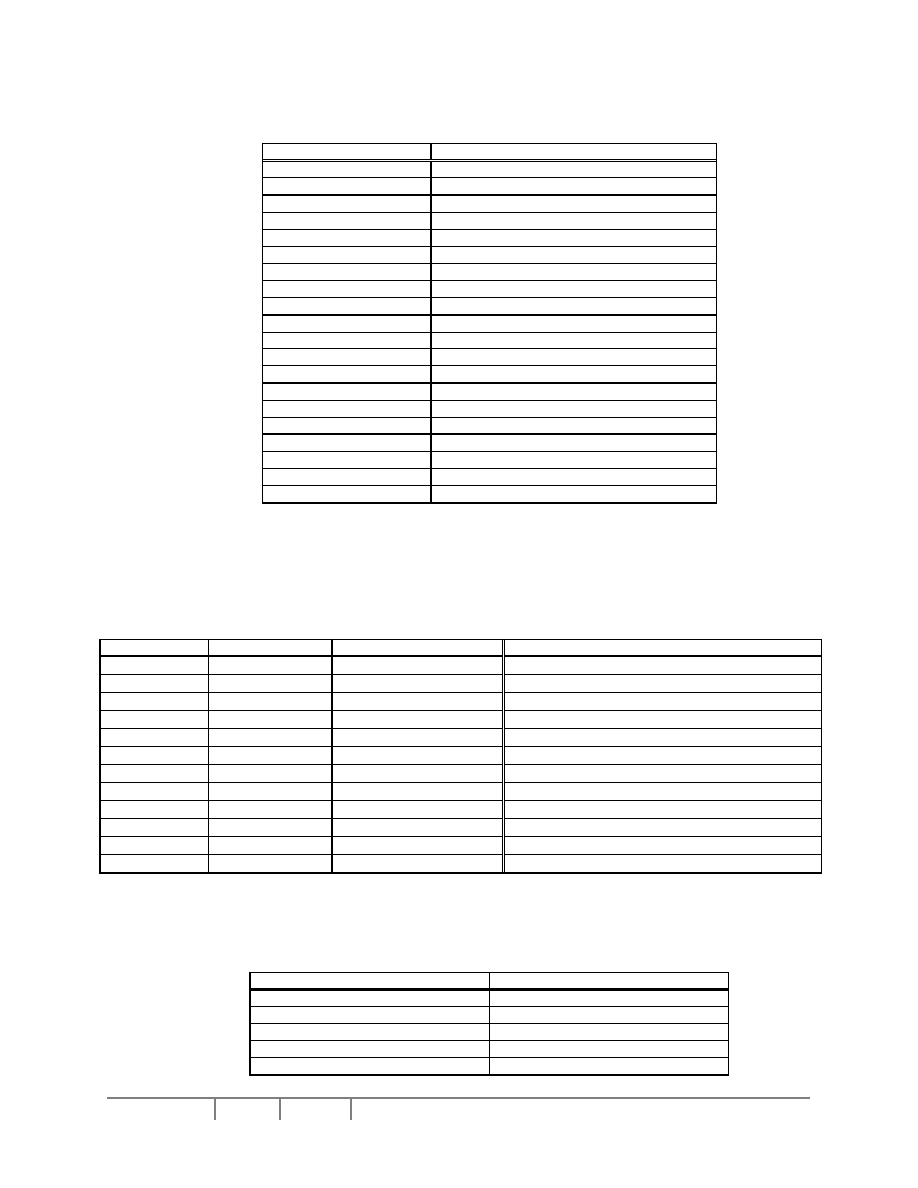

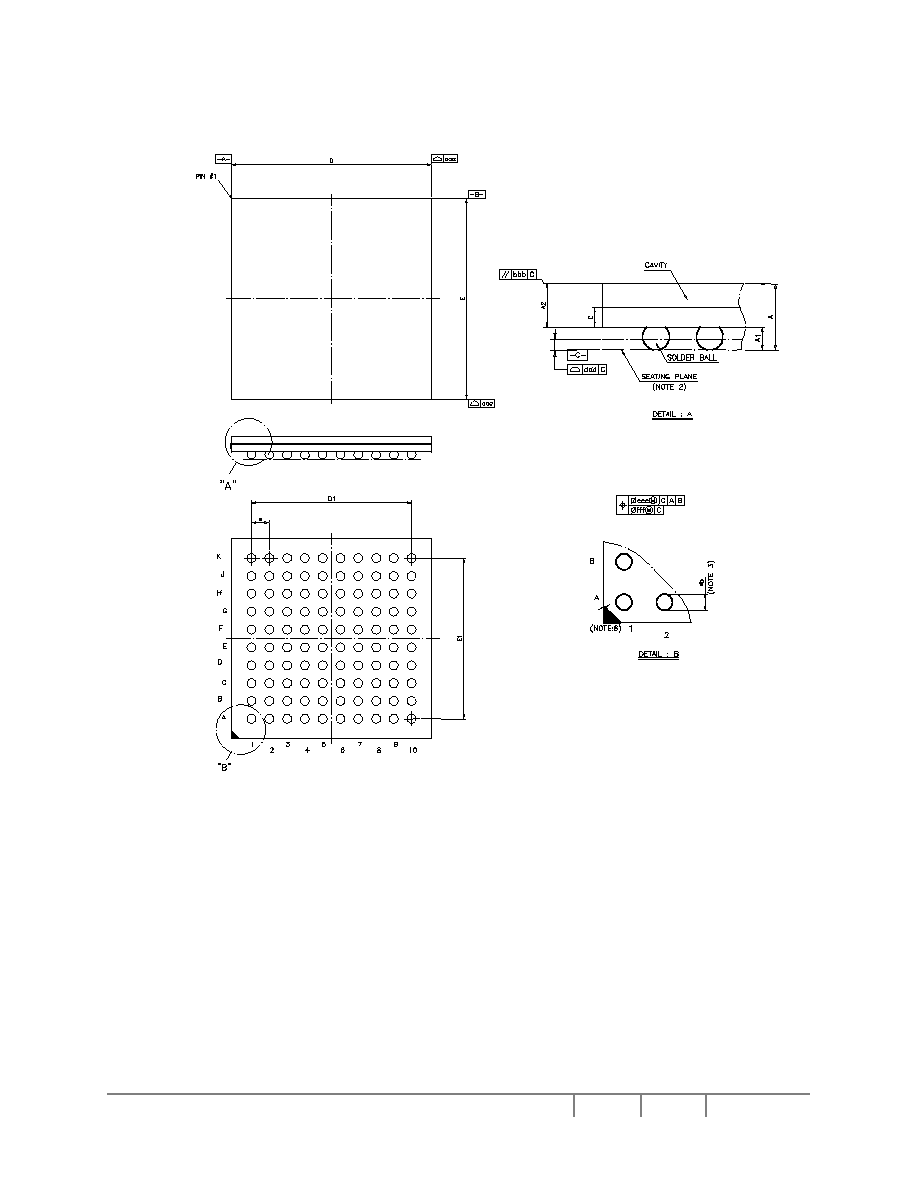

Figure 4-3 : Pinout Diagram � 100 pin TFBGA ............................................................................................. 7

Figure 7-1 : LDEN offset for Analog TFT .................................................................................................... 34

Figure 7-2 : GPIO offset for 320x240 HR-TFT............................................................................................ 35

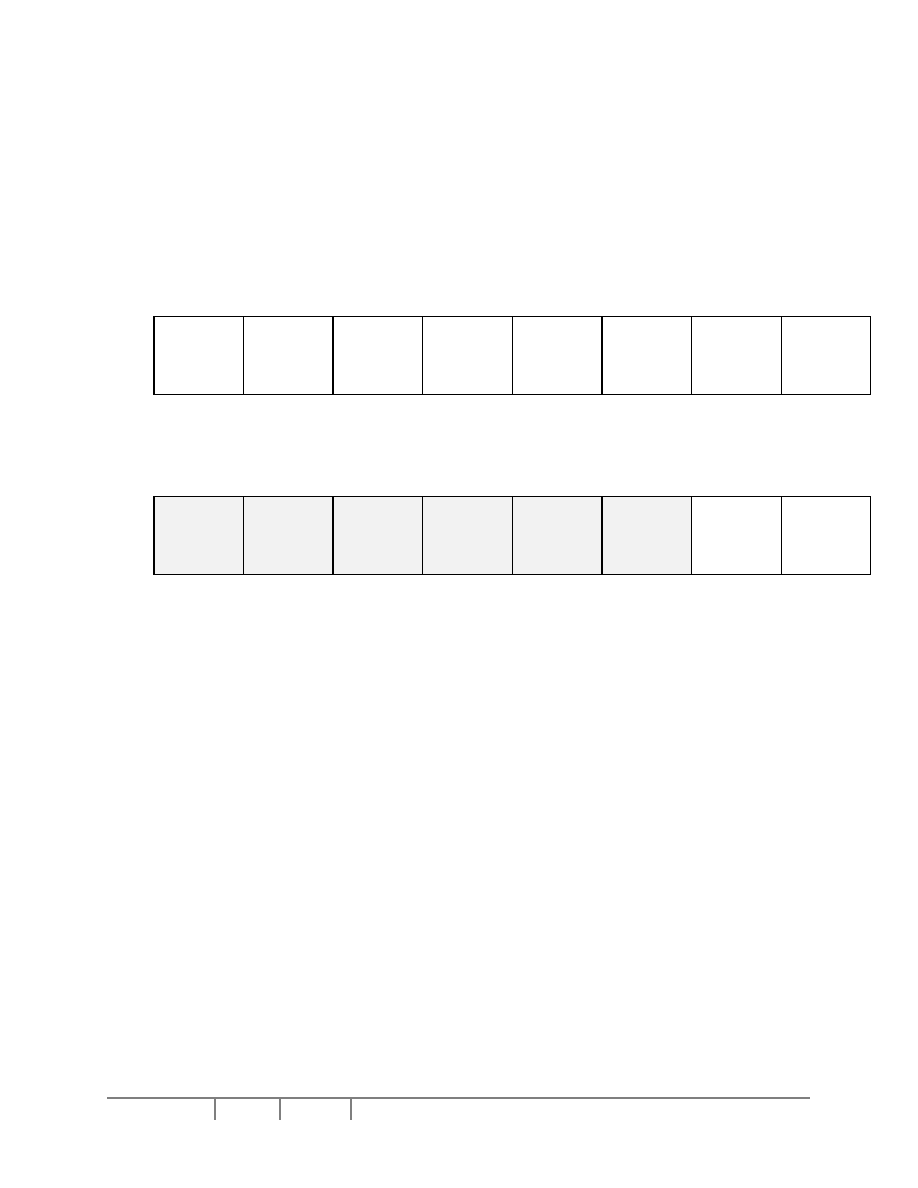

Figure 7-3 : Display Data Byte/Word Swap ................................................................................................ 39

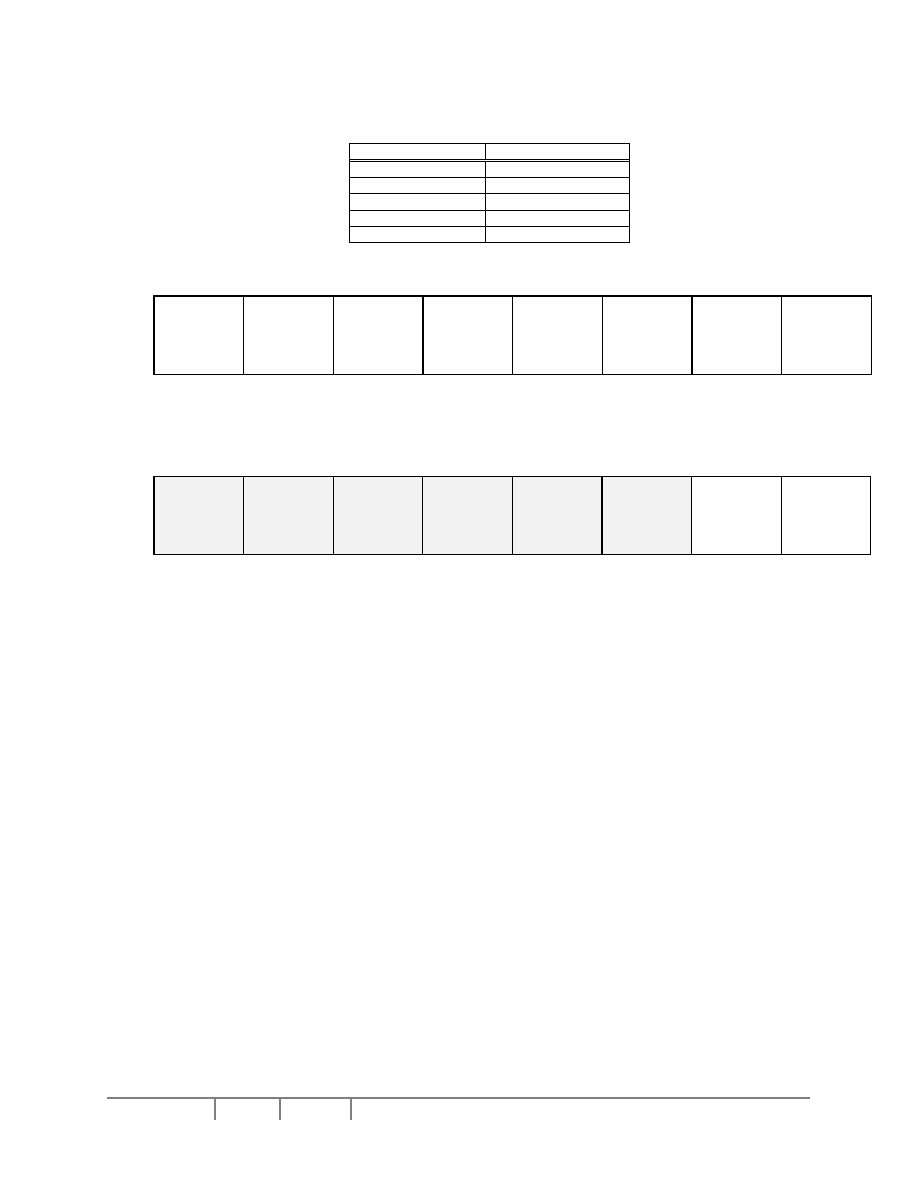

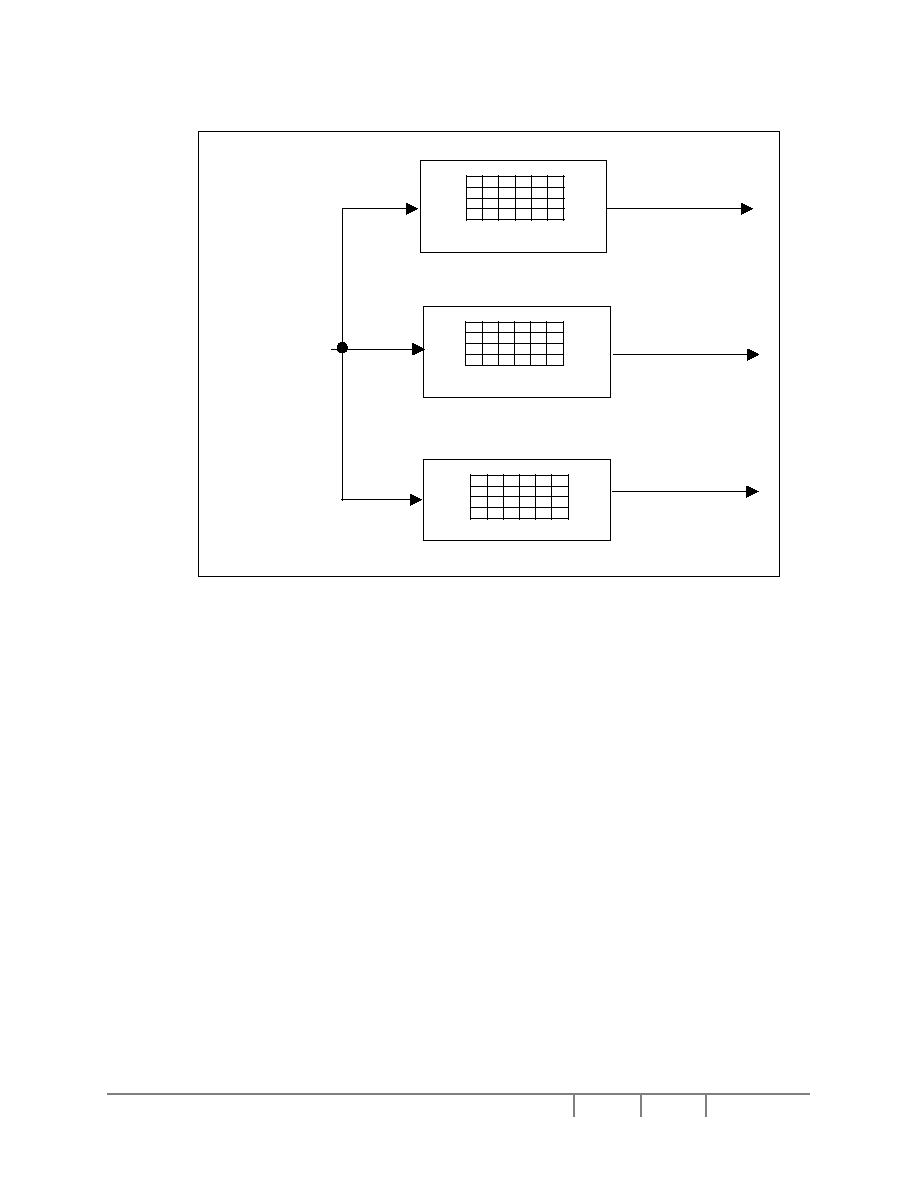

Figure 7-4 : PWM Clock/CV Pulse Block Diagram ..................................................................................... 52

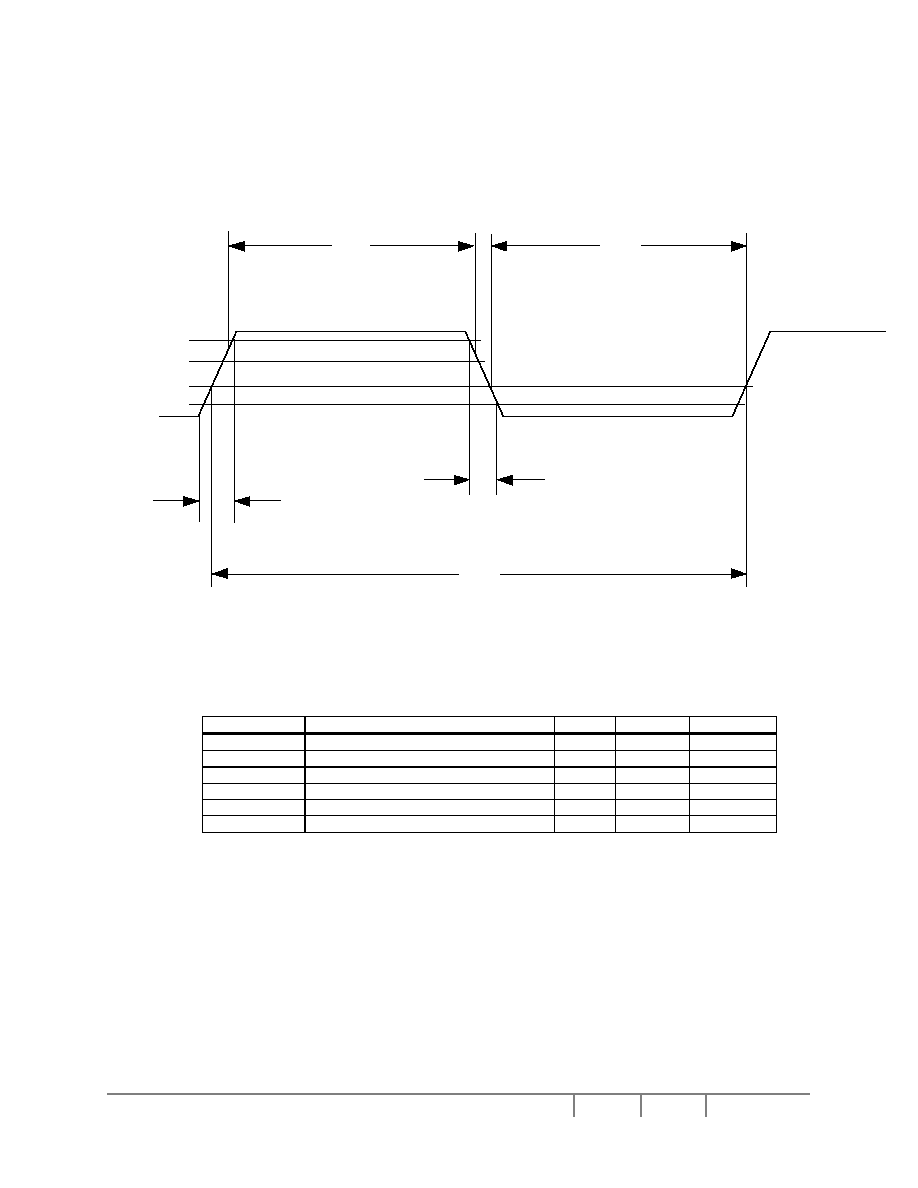

Figure 10-1 : Clock Input Requirements ..................................................................................................... 68

Figure 10-2 : Generic #1 Interface Timing .................................................................................................. 70

Figure 10-3 : Generic #2 Interface Timing .................................................................................................. 72

Figure 10-4 : Motorola MC68K #1 Interface Timing.................................................................................... 74

Figure 10-5 : Motorola DragonBall Interface with DTACK# Timing ............................................................ 76

Figure 10-6 : Motorola DragonBall Interface without DTACK# Timing ....................................................... 78

Figure 10-7 : Hitachi SH-3 Interface Timing................................................................................................ 80

Figure 10-8 : Hitachi SH-4 Interface Timing................................................................................................ 82

Figure 10-9 : Passive/TFT Power-On Sequence Timing ............................................................................ 84

Figure 10-10 : Passive/TFT Power-Off Sequence Timing .......................................................................... 85

Figure 10-11 : Power Saving Status Timing ............................................................................................... 86

Figure 10-12 :

Panel Timing Parameters

................................................................................................ 87

Figure 10-13 :

Generic STN Panel Timing

............................................................................................. 88

Figure 10-14 :

Monochrome 4-Bit Panel Timing

.................................................................................... 90

Figure 10-15 :

Monochrome 4-Bit Panel A.C. Timing

........................................................................... 91

Figure 10-16 :

Monochrome 8-Bit Panel Timing

.................................................................................... 93

Figure 10-17 :

Monochrome 8-Bit Panel A.C. Timing

........................................................................... 94

Figure 10-18 :

Color 4-Bit Panel Timing

.................................................................................................. 96

Figure 10-19 :

Color 4-Bit Panel A.C. Timing

......................................................................................... 97

Figure 10-20 :

Color 8-Bit Panel Timing (Format stripe)

...................................................................... 99

Figure 10-21 :

Color 8-Bit Panel A.C. Timing (Format stripe)

............................................................ 100

Figure 10-22 :

Generic TFT Panel Timing

............................................................................................ 102

Figure 10-23 :

12-Bit TFT Panel Timing

................................................................................................ 103

Figure 10-24 :

TFT A.C. Timing

.............................................................................................................. 105

Figure 10-25 :

160x160 Sharp HR-TFT Panel Horizontal Timing

..................................................... 107

Figure 10-26 :

160x160 Sharp HR-TFT Panel Vertical Timing

.......................................................... 109

Figure 10-27 :

HR-TFT Panel Horizontal Timing

................................................................................. 111

Figure 10-28 :

HR-TFT Panel Vertical Timing

...................................................................................... 112

Figure 10-29 : 160x234

Analog TFT A.C. Timing

................................................................................. 113

Figure 11-1 :

Clock Generator Block Diagram

..................................................................................... 115

Figure 14-1 : 1/2/4/8/16 Bit-Per-Pixel Display Data Memory Organization .............................................. 120

Figure 15-1 :

1 Bit-per-pixel Monochrome Mode Data Output Path

................................................. 121

Figure 15-2 :

2 Bit-per-pixel Monochrome Mode Data Output Path

................................................. 121

Figure 15-3 :

4 Bit-per-pixel Monochrome Mode Data Output Path

................................................. 122

Figure 15-4 :

8 Bit-per-pixel Monochrome Mode Data Output Path

................................................. 122

Figure 15-5 :

1 Bit-Per-Pixel Color Mode Data Output Path

.............................................................. 123

Figure 15-6 :

2 Bit-Per-Pixel Color Mode Data Output Path

.............................................................. 124

Figure 15-7 :

4 Bit-Per-Pixel Color Mode Data Output Path

.............................................................. 125

Figure 15-8 :

8 Bit-per-pixel Color Mode Data Output Path

............................................................... 126

Figure 16-1 : A pixel in Analog TFT panel ................................................................................................ 127

Figure 17-1 :

Byte-swapping for 16 Bpp

............................................................................................... 128

Figure 17-2 :

Byte-swapping for 1/2/4/8 Bpp

....................................................................................... 129

Figure 18-1 : Main Window inside Virtual Image Area.............................................................................. 130

vii

Figure 19-1 : Relationship Between The Screen Image and the Image Refreshed in 90

� Display Rotate

Mode. ................................................................................................................................................. 131

Figure 19-2 : Relationship Between The Screen Image and the Image Refreshed in 180

� Display Rotate

Mode. ................................................................................................................................................. 132

Figure 19-3 : Relationship Between The Screen Image and the Image Refreshed in 270

� Display Rotate

Mode. ................................................................................................................................................. 133

Figure 20-1 :

Floating Window with Display Rotate Mode disabled

................................................. 134

Figure 20-2 :

Floating Window with Display Rotate Mode 90� enabled

........................................... 135

Figure 20-3 :

Floating Window with Display Rotate Mode 180� enabled

........................................ 135

Figure 20-4

: Floating Window with Display Rotate Mode 270� enabled

........................................ 136

Figure 21-1 : Display Precedence in Hardware Cursor ............................................................................ 137

Figure 21-2 : Cursors on the main window ............................................................................................... 138

Figure 21-3 : Cursors with Display Rotate Mode 90

� enabled.................................................................. 138

Figure 21-4 : Cursors with Display Rotate Mode 180

� enabled................................................................ 139

Figure 21-5 : Cursors with Display Rotate Mode 270

� enabled................................................................ 139

Figure 22-1: Typical System Diagram (Generic #1 Bus) .......................................................................... 145

Figure 22-2 : Typical System Diagram (Generic #2 Bus) ......................................................................... 146

Figure 22-3 : Typical System Diagram (MC68K # 1, Motorola 16-Bit 68000) .......................................... 147

Figure 22-4 : Typical System Diagram (Motorola MC68EZ328/MC68VZ328 "DragonBall" Bus)............. 148

Figure 22-5 : Typical System Diagram (Hitachi SH-3 Bus)....................................................................... 149

Figure 22-6 : Typical System Diagram (Hitachi SH-4 Bus)....................................................................... 150

viii

List of Tables

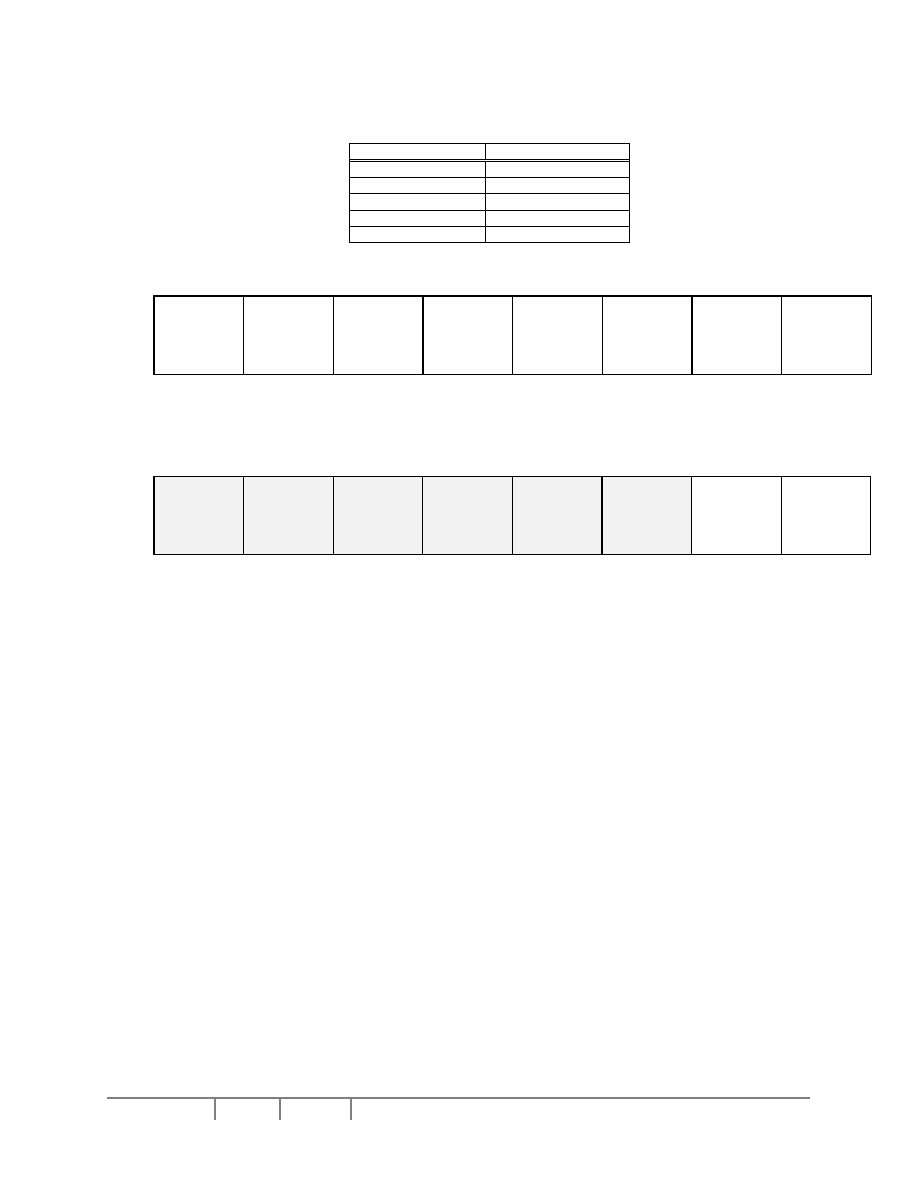

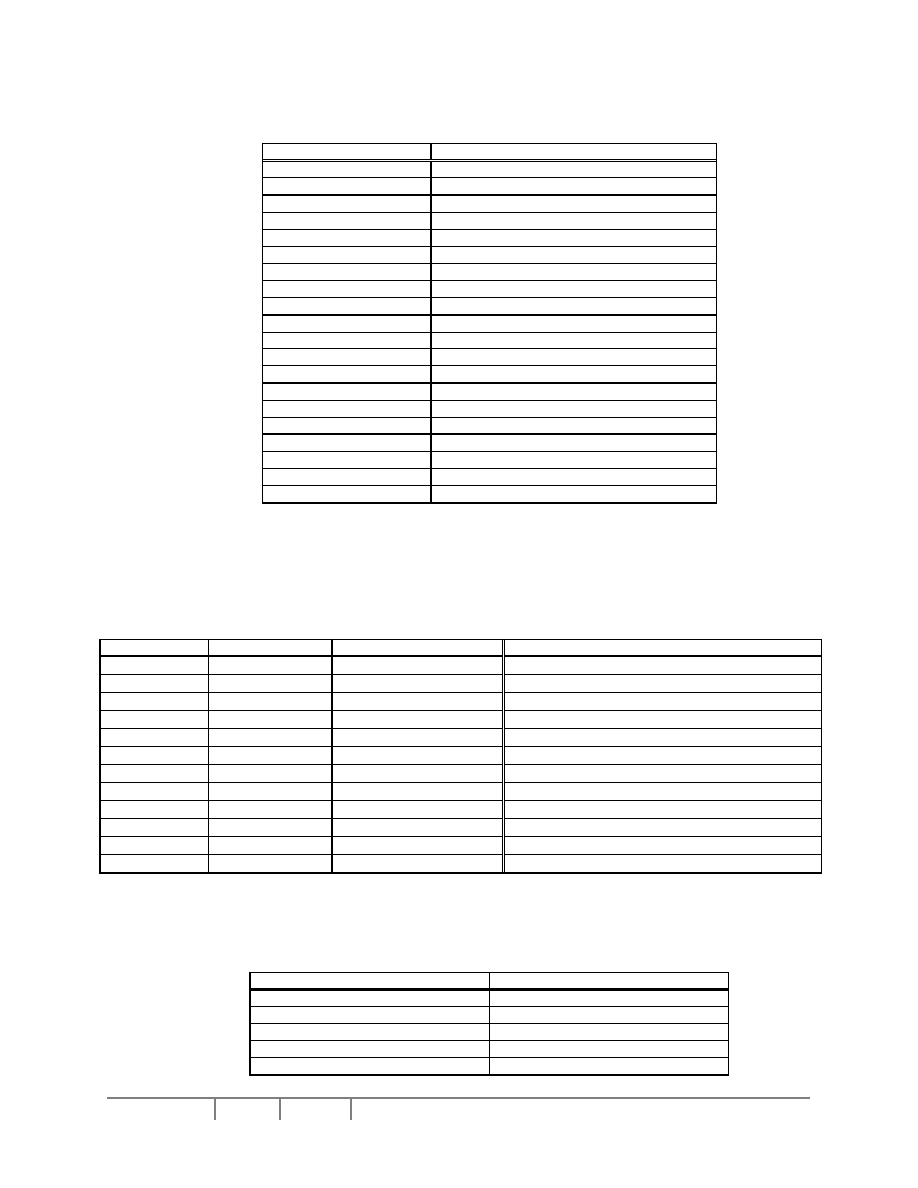

Table 3-1 : Ordering Information................................................................................................................... 3

Table 4-1 : TQFP Pin Assignment Table ...................................................................................................... 6

Table 4-2 : TFBGA Pin Assignment Table.................................................................................................... 8

Table 5-1 : Host Interface Pin Descriptions ................................................................................................ 10

Table 5-2 :

LCD Interface Pin Descriptions

............................................................................................ 12

Table 5-3 : Clock Input Pin Descriptions..................................................................................................... 13

Table 5-4 : Miscellaneous Pin Descriptions ................................................................................................ 13

Table 5-5 : Power And Ground Pin Descriptions ........................................................................................ 13

Table 5-6 : Summary of Power-On/Reset Options ..................................................................................... 14

Table 5-7 : Host Bus Interface Pin Mapping ............................................................................................... 14

Table 5-8 : LCD Interface Pin Mapping....................................................................................................... 15

Table 5-9 : Data Bus Organization.............................................................................................................. 16

Table 5-10 : Pin State Summary................................................................................................................. 16

Table 7-1 : MCLK Divide Selection ............................................................................................................. 19

Table 7-2 : PCLK Divide Selection.............................................................................................................. 20

Table 7-3 : PCLK Source Selection ............................................................................................................ 20

Table 7-4 : Panel Data Width Selection ...................................................................................................... 24

Table 7-5 : Active Panel Resolution Selection ............................................................................................ 25

Table 7-6 : LCD Panel Type Selection........................................................................................................ 25

Table 7-7 : RGB Sequence Selection ......................................................................................................... 36

Table 7-8 :

Color Invert Mode Options

.................................................................................................... 37

Table 7-9 :

LCD Bit-per-pixel Selection

.................................................................................................. 38

Table 7-10 : Display Rotate Mode Select Options ...................................................................................... 39

Table 7-11 : 32-bit Address X Increments for Various Color Depths.......................................................... 44

Table 7-12 : 32-bit Address Y Increments for Various Color Depths.......................................................... 45

Table 7-13 : 32-bit Address X Increments for Various Color Depths.......................................................... 46

Table 7-14 : 32-bit Address Y Increments for Various Color Depths.......................................................... 47

Table 7-15 : PWM Clock Control................................................................................................................. 52

Table 7-16 : CV Pulse Control .................................................................................................................... 53

Table 7-17 : PWM Clock Divide Select Options.......................................................................................... 53

Table 7-18 : CV Pulse Divide Select Options ............................................................................................. 54

Table 7-19 : LPWMOUT Duty Cycle Select Options................................................................................... 55

Table 7-20 : X Increment Mode for Various Color Depths.......................................................................... 58

Table 7-21 : Y Increment Mode for Various Color Depths.......................................................................... 59

Table 8-1 : Absolute Maximum Ratings ...................................................................................................... 66

Table 8-2 : Recommended Operating Conditions ...................................................................................... 66

Table 9-1 : Electrical Characteristics for IOV

DD

= 3.3V typical.................................................................... 67

Table 10-1 : Clock Input Requirements for CLKI ........................................................................................ 68

Table 10-2 : Clock Input Requirements for AUXCLK.................................................................................. 69

Table 10-3 : Internal Clock Requirements .................................................................................................. 69

Table 10-4 : Generic #1 Interface Timing ................................................................................................... 71

Table 10-5 : Generic #2 Interface Timing ................................................................................................... 73

Table 10-6 : Motorola MC68K #1 Interface Timing..................................................................................... 75

Table 10-7 : Motorola DragonBall Interface with DTACK# Timing ............................................................. 77

Table 10-8 : Motorola DragonBall Interface without DTACK# Timing ........................................................ 79

Table 10-9 : Hitachi SH-3 Interface Timing................................................................................................. 81

Table 10-10 : Hitachi SH-4 Interface Timing............................................................................................... 83

Table 10-11 : Passive/TFT Power-On Sequence Timing ........................................................................... 84

Table 10-12 : Passive/TFT Power-Off Sequence Timing ........................................................................... 85

Table 10-13 : Power Saving Status Timing................................................................................................. 86

Table 10-14 : Panel Timing Parameter Definition and Register Summary................................................. 87

Table 10-15 : Monochrome 4-Bit Panel A.C. Timing .................................................................................. 92

Table 10-16 : Monochrome 8-Bit Panel A.C. Timing .................................................................................. 95

ix

Table 10-17 : Color 4-Bit Panel A.C. Timing............................................................................................... 98

Table 10-18 : Color 8-Bit Panel A.C. Timing (Format stripe) .................................................................... 101

Table 10-19 : TFT A.C. Timing.................................................................................................................. 106

Table 10-20 : 160x160 Sharp HR-TFT Horizontal Timing ........................................................................ 108

Table 10-21 : 160x160 Sharp HR-TFT Panel Vertical Timing .................................................................. 110

Table 10-22 : 320x240 HR-TFT Panel Horizontal Timing......................................................................... 112

Table 10-23 : 320x240 HR-TFT Panel Vertical Timing............................................................................. 112

Table 10-24 : 160x234 Analog TFT A.C. Timing ...................................................................................... 114

Table 11-1 : BCLK Clock Selection........................................................................................................... 115

Table 11-2 : MCLK Clock Selection .......................................................................................................... 116

Table 11-3 : PCLK Clock Selection........................................................................................................... 117

Table 11-4 : PCLK condition for Analog TFT ............................................................................................ 117

Table 11-5 : Relationship between MCLK and PCLK............................................................................... 117

Table 11-6 :

PWMCLK Clock Selection

................................................................................................ 118

Table 11-7 : SSD1908 Internal Clock Requirements................................................................................ 118

Table 12-1 : Power Saving Mode Function Summary .............................................................................. 119

Table 21-1 : Indexing scheme for Hardware Cursor ................................................................................. 137

Table 23-1 : SSD1908 Register Table (1 of 3).......................................................................................... 154

Table 23-2 : SSD1908 Register Table (2 of 3).......................................................................................... 155

Table 23-3 : SSD1908 Register Table (3 of 3).......................................................................................... 156

SOLOMON SYSTECH

SEMICONDUCTOR TECHNICAL DATA

This document contains information on a new product. Specifications and information herein are subject to

change without notice.

http://www.solomon-systech.com

SSD1908

Rev 1.0

P 1/157

Oct 2003

Copyright

2003 Solomon Systech Limited

SSD1908

Advance Information

LCD Graphics Controller

CMOS

1 GENERAL

DESCRIPTION

The SSD1908 is a graphics controller with built-in 256Kbyte SRAM display buffer, supporting color and mono LCD.

The SSD1908 can support a wide range of active and passive panels, and interface with various CPUs. The

advanced design, together with integration of memory and timing circuits make a low cost, low power, single chip

solution to meet the handheld devices or appliances market needs, such as Pocket/Palm-size PCs and mobile

communication devices.

The SSD1908 supports most of the resolutions commonly used in portable applications, and is featured with

hardware display rotation, covering different form factor needs. The controller also features Virtual Display,

Floating Window (variable size Overlay Window) and two Cursors to reduce the software manipulation. The

SSD1908 provides horizontal resolution doubling for Analog TFT panel. The 32-bit internal data path provides

high bandwidth display memory for fast screen updates. The SSD1908 also provides the advantage of a single

power supply.

The SSD1908 features low-latency CPU access, which supports microprocessors without READY/WAIT#

handshaking signals. This controller impartiality to CPU type or operating system makes it an ideal display solution

for a wide variety of applications. The SSD1908 is available in 100 pin TQFP & TFBGA packages.

Solomon Systech

Oct 2003

P 2/2

Rev 1.0

SSD1908

2 FEATURES

2.1 Integrated Display Buffer

� Embedded 256K byte SRAM display buffer.

2.2 CPU

Interface

� Directly interfaces to :

Generic #1 bus interface with WAIT# signal

Generic #2 bus interface with WAIT# signal

Intel StrongARM / XScale

Motorola MX1 Dragonball

Motorola MC68K

Motorola MC68EZ328/MC68VZ328 DragonBall

Hitachi SH-3

Hitachi SH-4

� 8-bit processor support with "glue logic".

� "Fixed" and low-latency CPU access times.

� Registers are memory-mapped which dedicated M/R# input selects between memory and

register address space.

� The contiguous 256K byte display buffer is directly accessible through the 18-bit address bus.

2.3 Display

Support

� 4/8-bit monochrome STN interface.

� 4/8-bit color STN interface.

� 9/12/18-bit Active Matrix TFT interface.

� Direct support for 18-bit Sharp HR-TFT interface (160x160, 320x240).

� Support for Analog TFT interface (160x234).

2.4 Display

Modes

� 1/2/4/8/16 bit-per-pixel (bpp) color depths.

� Up to 64 gray shades using Frame Rate Control (FRC) and dithering on monochrome passive

LCD panels.

� Up to 256k colors on passive STN panels.

� Up to 256k colors on active matrix LCD panels.

� Resolution examples :

320x320 at a color depth of 16 bpp

160x160 at a color depth of 16 bpp

160x240 at a color depth of 16 bpp

2.5 Display

Features

� Display Rotate Mode : 90�, 180�, 270� counter-clockwise hardware rotation of display image.

� Virtual display support : displays image larger than the panel size through the use of panning

and scrolling.

� Floating Window Mode : displays a variable size window overlaid on background image.

� 2 Hardware Cursors (for 4/8/16 bpp) : simultaneously displays two cursors overlaid on

background image.

SSD1908

Rev 1.0

P 3/3

Oct 2003

Solomon Systech

� Double Buffering/Multi-pages: provides smooth animation and instantaneous screen updates.

� Horizontal Resolution Doubling: The image can be shrunk horizontally by half and displayed in

panel. This function is only available in Analog TFT panel.

2.6 Clock

Source

� Two clock inputs: CLKI and AUXCLK. It is possible to use one clock input only.

� Bus clock (BCLK) is derived from CLKI, can be internally divided by 2, 3, or 4.

� Memory clock (MCLK) is derived from BCLK. It can be internally divided by 2, 3, or 4.

� Pixel clock (PCLK) can be derived from CLKI, AUXCLK, BCLK, or MCLK. It can be internally

divided by 2, 3, 4, or 8.

2.7 Miscellaneous

� Hardware/Software Color Invert

� Software Power Saving mode

� General Purpose Input / Output pins available

� Single Supply Operation : 3.0V � 3.6V

2.8 Package

� 100-pin TQFP package

� 100-pin TFBGA package

3 ORDERING

INFORMATION

Table 3-1 : Ordering Information

Ordering Part Number

Package Form

SSD1908QT2 100

TQFP

SSD1908BT14 100

TFBGA

Solomon Systech

Oct 2003

P 4/4

Rev 1.0

SSD1908

4 BLOCK

DIAGRAM

CONT

ROL

R

E

G

I

STER

S

G

P

IO

&

L

O

O

K

U

P

TABL

E (L

U

T

)

CONT

ROL

RE

GI

S

T

E

R

& GP

I

O

D

I

SP

L

AY D

A

TA

PR

EF

ETC

H

U

N

I

T

FR

C

/

TFT C

O

N

T

R

O

L

S

&

D

I

SPL

AY D

A

TA FO

R

M

AT

CONV

E

R

T

I

ON

DI

S

P

L

AY

OUT

P

UT

ME

MOR

Y

R

/

W

CO

NT

RO

L

D

I

SPL

AY M

E

M

O

R

Y

W

I

T

H

CONT

ROL

DI

S

P

L

AY

BUF

F

E

R (2

5

6

KB)

READ/WRITE

DECODE

MCU

INTERFACE

M

CU I

N

T

E

RF

ACE

CL

OCK

GE

NE

RA

T

O

R

I

N

T

E

RNA

L

CL

OCK

S

G

P

IO

[6

:0

]

GP

O

LF

R

A

M

E

,

LLI

N

E

,

LS

H

I

F

T

,

LD

E

N

,

LD

A

T

A

[

17:

0]

W

E

0#,

W

E

1#,

RD/

W

R

#

,

RD#

,

BS#

,C

S#

;

R

ESET#

,

M

/

R

#

A

[

17:

0]

D

[

15:

0]

C

F

[7

:0

]

WAIT

#

C

L

KI, AU

XC

L

K

P

U

L

S

E

W

I

DT

H M

O

DUL

A

T

I

O

N CL

OCK

A

ND

C

O

N

T

R

AST VO

L

T

AG

E PU

L

SE C

O

N

T

R

O

L

LP

W

M

O

U

T

,

LC

V

O

U

T

Figure 4-1 : Block Diagram

SSD1908

Rev 1.0

P 5/5

Oct 2003

Solomon Systech

4.1 PIN

ARRANGEMENT

4.1.1 100 pin TQFP

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

VSS

IOVDD

LDEN

CORE

V

D

D

LFRA

M

E

LLI

NE

LSH

I

FT

LDA

T

A

0

LDA

T

A

1

LDA

T

A

2

LDA

T

A

3

LDA

T

A

4

LDA

T

A

5

LDA

T

A

6

VSS

IO

VD

D

LDA

T

A

7

LDA

T

A

8

LDA

T

A

9

LDA

T

A

10

LDA

T

A

11

LDA

T

A

12

LDA

T

A

13

LDA

T

A

14

LDA

T

A

15

LDA

T

A

16

LDA

T

A

17

VSS

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

IOVDD

AUXCLK

CF7

CF6

CF5

CF4

CF3

CF2

CF1

CF0

A17

A16

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

VSS

VSS

D9

D10

D11

D12

D13

D14

D15

WA

I

T

#

IO

VD

D

CLK

I

VSS

R

ESET

#

RD/

W

R

#

WE

1

#

WE

0

#

RD

#

BS

#

M/R

#

CS

#

A0

A1

A2

A3

CORE

V

D

D

SSD1908

GPO

LCVOUT

GPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

LPWMOUT

IOVDD

VSS

D0

D1

D2

D3

D4

D5

D6

D7

D8

IOVDD

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

Figure 4-2 : Pinout Diagram � 100 pin TQFP

Note

CoreVDD is an internal regulator output pin. 0.1

�F capacitor to V

SS

must be required on each CoreVDD pin.

Solomon Systech

Oct 2003

P 6/6

Rev 1.0

SSD1908

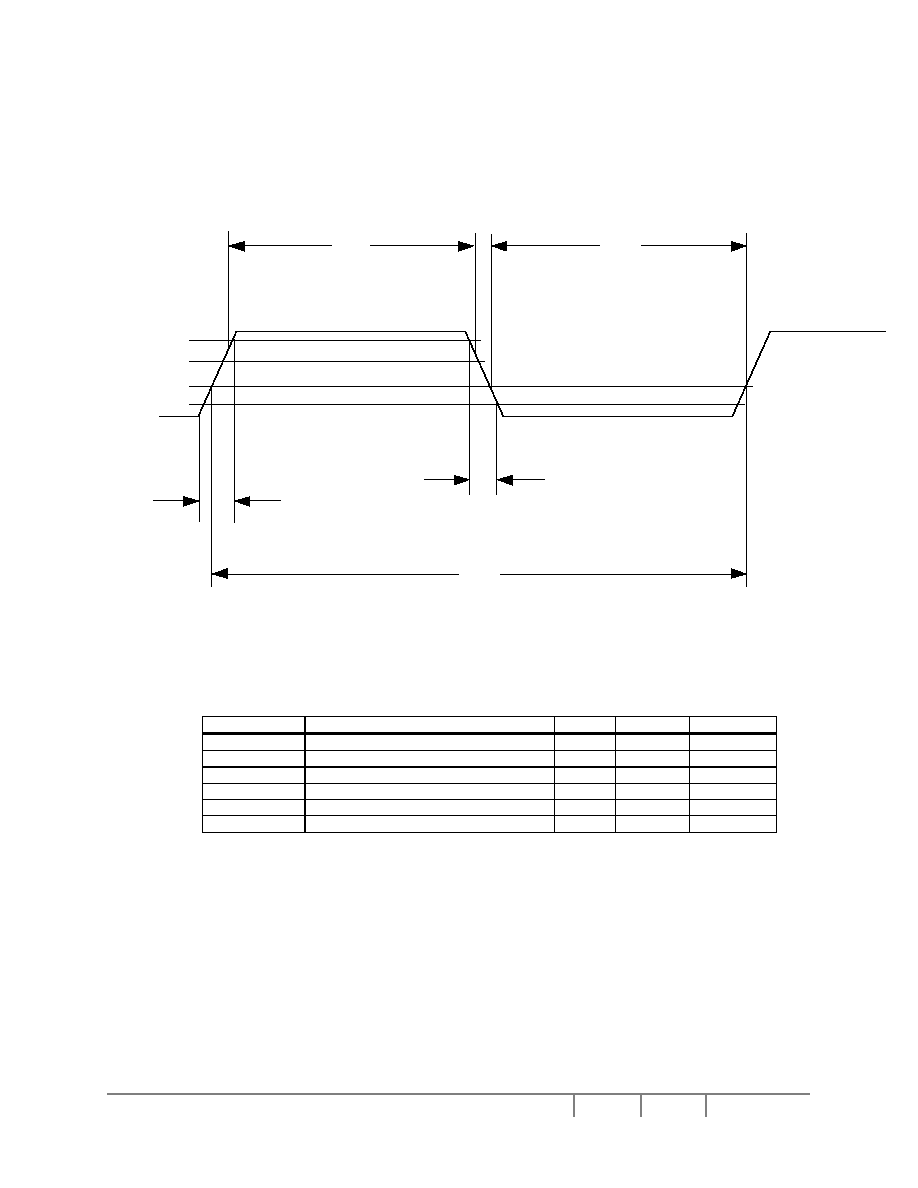

Table 4-1 : TQFP Pin Assignment Table

Pin #

Signal Name

Pin #

Signal Name

Pin #

Signal Name

Pin #

Signal Name

1 COREVDD 26 IOVDD 51 COREVDD 76

IOVDD

2 A3 27 D8 52

LFRAME

77

AUXCLK

3 A2 28 D7 53

LLINE

78 CF7

4 A1 29 D6 54

LSHIFT

79 CF6

5 A0 30 D5 55

LDATA0

80 CF5

6 CS# 31 D4 56

LDATA1

81 CF4

7 M/R#

32 D3 57

LDATA2

82 CF3

8 BS# 33 D2 58

LDATA3

83 CF2

9 RD# 34 D1 59

LDATA4

84 CF1

10

WE0#

35 D0 60

LDATA5

85 CF0

11 WE1# 36 V

SS

61

LDATA6

86 A17

12 RD/WR# 37 IOVDD 62

V

SS

87 A16

13 RESET# 38

LPWMOUT

63 IOVDD 88 A15

14 V

SS

39

GPIO6

64

LDATA7

89 A14

15 CLKI 40

GPIO5

65

LDATA8

90 A13

16 IOVDD 41 GPIO4 66 LDATA9

91 A12

17 WAIT# 42 GPIO3 67

LDATA10

92 A11

18 D15 43

GPIO2

68

LDATA11

93 A10

19 D14 44

GPIO1

69

LDATA12

94 A9

20 D13 45

GPIO0

70

LDATA13

95 A8

21 D12 46

LCVOUT

71

LDATA14

96 A7

22 D11 47 GPO 72

LDATA15

97 A6

23 D10 48 LDEN 73

LDATA16

98 A5

24 D9 49

IOVDD

74

LDATA17

99 A4

25 V

SS

50 V

SS

75 V

SS

100 V

SS

SSD1908

Rev 1.0

P 7/7

Oct 2003

Solomon Systech

4.1.2 100 pin TFBGA

K

J

H

G

F

E

D

C

B

A

BOTTOM VIEW

1 2 3 4 5 6 7 8 9 10

Figure 4-3 : Pinout Diagram � 100 pin TFBGA

Note

CoreVDD is an internal regulator output pin. 0.1

�F capacitor to V

SS

must be required on each CoreVDD pin.

Solomon Systech

Oct 2003

P 8/8

Rev 1.0

SSD1908

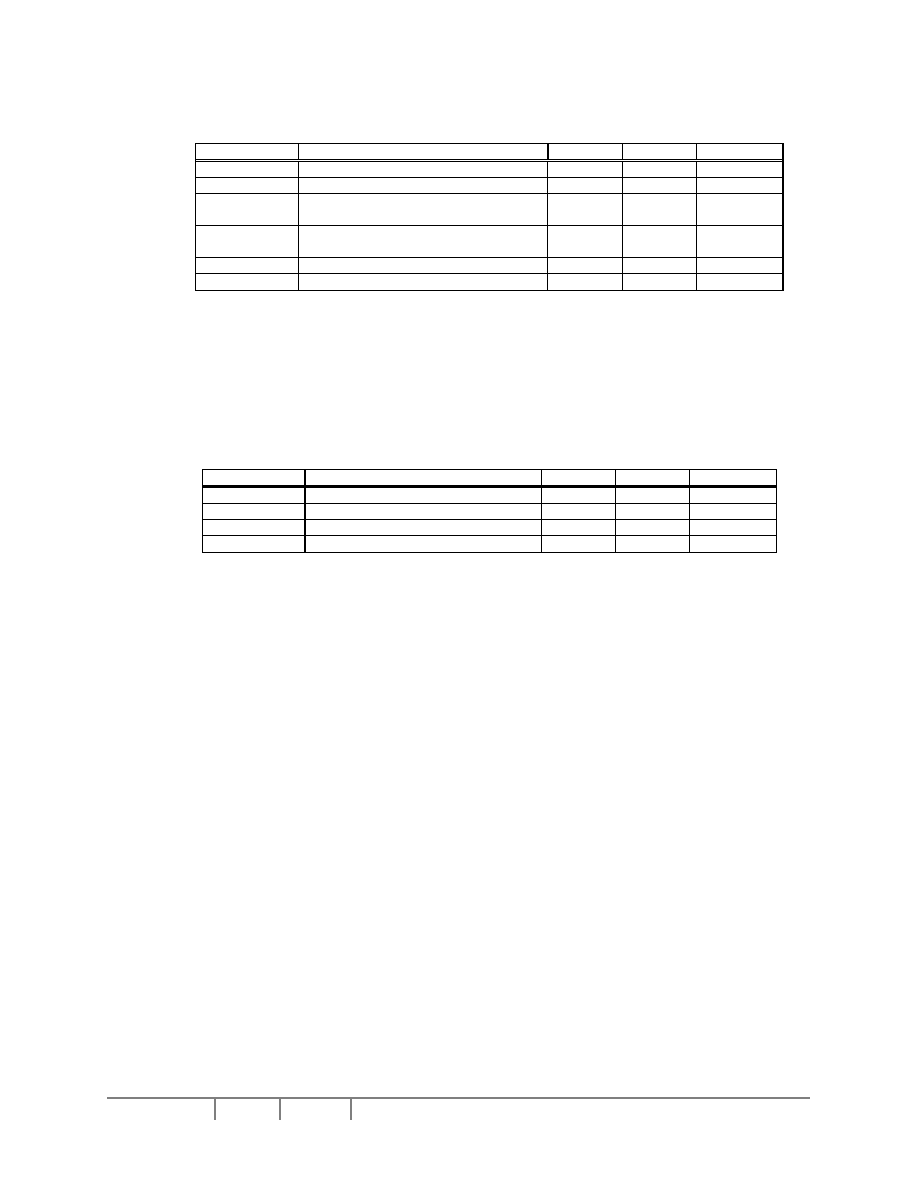

Table 4-2 : TFBGA Pin Assignment Table

Pin #

Signal

Name

Pin #

Signal

Name

Pin #

Signal

Name

Pin #

Signal

Name

Pin #

Signal

Name

A1 V

SS

C1

IOVDD

E1 CF3 G1 A12 J1 A5

A2

LDATA17

C2 CF7 E2 CF2 G2 A11 J2 A4

A3

LDATA13

C3

LDATA15

E3 CF1 G3 A10 J3 A2

A4 LDATA9 C4 LDATA11 E4 CF0 G4

A9 J4

A0

A5 LDATA6 C5 IOVDD E5 LDATA8 G5 WE0# J5 BS#

A6 LDATA2 C6 LDATA4 E6 GPIO5 G6 RD#/WR J6

V

SS

A7 LSHIFT C7 LDATA1 E7 GPIO6 G7 WAIT# J7 D14

A8 LFRAME C8 GPO E8 LPWMOUT

G8

D4

J8

D12

A9 COREVDD C9 LCVOUT E9 IOVDD G9

D5

J9

D9

A10 V

SS

C10

GPIO0 E10 V

SS

G10 D6 J10 IOVDD

B1 AUXCLK D1 CF6 F1

A17 H1

A8 K1

V

SS

B2 LDATA16 D2 CF5 F2

A16 H2

A7

K2 COREVDD

B3 LDATA14 D3 CF4 F3

A15 H3

A6

K3

A3

B4 LDATA10 D4 LDATA12 F4

A14 H4

CS# K4

A1

B5 V

SS

D5

LDATA7

F5 A13 H5 RD# K5 M/R#

B6 LDATA3 D6 LDATA5 F6 WE1# H6 RESET# K6 CLKI

B7 LDATA0 D7 GPIO1 F7

D0 H7 IOVDD K7 D15

B8 LLINE D8 GPIO2 F8 D1 H8 D11 K8 D13

B9 IOVDD D9 GPIO3 F9 D2 H9 D7 K9 D10

B10 LDEN D10 GPIO4 F10 D3 H10 D8 K10 V

SS

SSD1908

Rev 1.0

P 9/9

Oct 2003

Solomon Systech

5 PIN

DESCRIPTION

Key:

I = Input

O =Output

IO = Bi-directional (input / output)

P = Power pin

LIS = LVTTL Schmitt input

LB2 = LVTTL IO buffer (8mA/-8mA at 3.3V)

LB3 = LVTTL IO buffer (12mA/-12mA at 3.3V)

LO3 = LVTTL output buffer (12mA/-12mA at 3.3V)

LT2 = Tri-state output buffer (8mA/-8mA at 3.3V)

LT3 = Tri-state output buffer (12mA/-12mA at 3.3V)

Hi-Z = High impedance

Note : LVTTL is low voltage TTL (see Section 9 "DC CHARACTERISTICS").

Solomon Systech

Oct 2003

P 10/10

Rev 1.0

SSD1908

5.1 Host

Interface

Table 5-1 : Host Interface Pin Descriptions

Pin Name Type

TQFP

Pin #

TFBGA

Pin #

Cell

RESET#

State

Description

A0

I

5

J4 LIS

0

This input pin has multiple functions.

� For Generic #1, this pin is not used and should be

connected to V

SS

.

� For Generic #2, this is an input of system address bit 0

(A0).

� For MC68K #1, this is an input of the lower data strobe

(LDS#).

� For DragonBall, this pin is not used and should be

connected to V

SS

.

� For SH-3/SH-4, this pin is not used and should be

connected to VSS.

See Table 5-7 : Host Bus Interface Pin Mapping for summary.

A[17:1] I

2-4, 86-

99

F1-F5,

G1-G4,

H1-H3,

J1-J3,

K3-K4

LIS

0

System address bus bits 17-1.

D[15:0] IO

18-24,

27-35

F7-F10,

G8-G10,

H8-H10,

J7-J9,

K7-K9

LB2 Hi-Z

Input data from the system data bus.

� For Generic #1, these pins are connected to D[15:0].

� For Generic #2, these pins are connected to D[15:0].

� For MC68K #1, these pins are connected to D[15:0].

� For DragonBall, these pins are connected to D[15:0].

� For SH-3/SH-4, these pins are connected to D[15:0].

See Table 5-7 : Host Bus Interface Pin Mapping for summary.

WE0# I 10 G5 LIS 1

This input pin has multiple functions.

� For Generic #1, this is an input of the write enable signal

for the lower data byte (WE0#).

� For Generic #2, this is an input of the write enable signal

(WE#).

� For MC68K #1, this pin must be tied to IOV

DD

.

� For DragonBall, this is an input of the byte enable signal

for the D[7:0] data byte (LWE#).

� For SH-3/SH-4, this is input of the write enable signal for

data D[7:0].

See Table 5-7 : Host Bus Interface Pin Mapping for summary.

WE1# I 11 F6 LIS 1

This input pin has multiple functions.

� For Generic #1, this is an input of the write enable signal

for the upper data byte (WE1#).

� For Generic #2, this is an input of the byte enable signal

for the high data byte (BHE#).

� For MC68K #1, this is an input of the upper data strobe

(UDS#).

� For DragonBall, this is an input of the byte enable signal

for the D[15:8] data byte (UWE#).

� For SH-3/SH-4, this is input of the write enable signal for

data D[15:8].

See Table 5-7 : Host Bus Interface Pin Mapping for summary.

CS# I 6 H4 LIS 1

Chip select input. See Table 5-7 : Host Bus Interface Pin

Mapping for summary.

M/R# I 7 K5 LIS 0

This input pin is used to select the display buffer or internal

registers of the SSD1908. M/R# is set high to access the

display buffer and low to access the registers.

See Table 5-7 : Host Bus Interface Pin Mapping for summary.

SSD1908

Rev 1.0

P 11/11

Oct 2003

Solomon Systech

Pin

Name

Type

TQFP

Pin #

TFBGA

Pin #

Cell

RESET#

State

Description

BS# I 8 J5 LIS 1

This input pin has multiple functions.

� For Generic #1, this pin must be tied to IOV

DD

.

� For Generic #2, this pin must be tied to IOV

DD

.

� For MC68K #1, this is an input of the address strobe

(AS#).

� For DragonBall, this pin must be tied to IOV

DD

.

� For SH-3/SH-4, this is input of the bus start signal (BS#).

See Table 5-7 : Host Bus Interface Pin Mapping for summary.

RD/WR#

I

12

G6 LIS

1

This input pin has multiple functions.

� For Generic #1, this is an input of the read command for

the upper data byte (RD1#).

� For Generic #2, this pin must be tied to IOV

DD

.

� For MC68K #1, this is an input of the R/W# signal.

� For DragonBall, this pin must be tied to IOV

DD

.

� For SH-3/SH-4, this is input of the RD/WR# signal. The

SSD1905 needs this signal for early decode of the bus

cycle.

See Table 5-7 : Host Bus Interface Pin Mapping for summary.

RD#

I

9

H5 LIS

1

This input pin has multiple functions.

� For Generic #1, this is an input of the read command for

the lower data byte (RD0#).

� For Generic #2, this is an input of the read command

(RD#).

� For MC68K #1, this pin must be tied to IOV

DD

.

� For DragonBall, this is an input of the output enable

(OE#).

� For SH-3/SH-4, this is input of the read signal (RD#).

See Table 5-7 : Host Bus Interface Pin Mapping for summary.

WAIT# O 17 G7 LT2 Hi-Z

During a data transfer, this output pin is driven active to force

the system to insert wait states. It is driven inactive to indicate

the completion of a data transfer. WAIT# is released to the

high impedance state after the data transfer is complete. Its

active polarity is configurable. A pull-up or pull-down resistor

should be used to resolve any data contention issues. See

Table 5-6 : Summary of Power-On/Reset Options.

� For Generic #1, this pin outputs the wait signal (WAIT#).

� For Generic #2, this pin outputs the wait signal (WAIT#).

� For MC68K #1, this pin outputs the data transfer

acknowledge signal (DTACK#).

� For DragonBall, this pin outputs the data transfer

acknowledge signal (DTACK#).

� For SH-3 mode, this pin outputs the wait request signal

(WAIT#).

� For SH-4 mode, this pin outputs the device ready signal

(RDY#).

See Table 5-7 : Host Bus Interface Pin Mapping for summary.

RESET# I 13 H6 LIS 0

Active low input to set all internal registers to the default state

and to force all signals to their inactive states. It is

recommended to place a

0.1

�F capacitor to V

SS

.

Note : When reset state is released (RESET# = "H"),

normal operation can be started after 3 BCLK period.

Solomon Systech

Oct 2003

P 12/12

Rev 1.0

SSD1908

5.2 LCD

Interface

Table 5-2 :

LCD Interface Pin Descriptions

Pin Name

Type

TQFP

Pin #

TFBGA

Pin #

Cell

RESET#

State

Description

LDATA[17:0]

O

55-61,

64-74

A2-A6,

B2-B4,

B6-B7,

C3-C4,

C6-C7,

D4-D6,

E5

LO3

0

Panel Data bits 17-0.

LFRAME O 52 A8 LO3 0

This output pin has multiple functions.

� Frame Pulse

� SPS for Sharp HR-TFT

� VSD for Analog TFT

See Table 5-8 : LCD Interface Pin Mapping for summary.

LLINE O 53 B8

LO3 0

This output pin has multiple functions.

� Line Pulse

� LP for Sharp HR-TFT

� HSD for Analog TFT

See Table 5-8 : LCD Interface Pin Mapping for summary.

LSHIFT O 54 A7 LO3 0

This output pin has multiple functions.

� Shift Clock

� CLK for Sharp HR-TFT

� DCLK for Analog TFT

See Table 5-8 : LCD Interface Pin Mapping for summary.

LDEN O

48 B10

LO3 0

This output pin has multiple functions.

� Display enable (LDEN) for TFT panels

� LCD backplane bias signal (MOD) for all other LCD

panels

� DEN for Analog TFT

See Table 5-8 : LCD Interface Pin Mapping for summary.

GPIO0 IO 45 C10

LIS/

LT3

0

This pin has multiple functions.

� PS for Sharp HR-TFT

� General purpose IO pin 0 (GPIO0)

� Hardware Color Invert

See Table 5-8 : LCD Interface Pin Mapping for summary.

GPIO1 IO 44 D7 LB3 0

This pin has multiple functions.

� CLS for Sharp HR-TFT

� General purpose IO pin 1 (GPIO1)

See Table 5-8 : LCD Interface Pin Mapping for summary.

GPIO2 IO 43 D8 LB3 0

This pin has multiple functions.

� REV for Sharp HR-TFT

� General purpose IO pin 2 (GPIO2)

See Table 5-8 : LCD Interface Pin Mapping for summary.

GPIO3 IO 42 D9 LB3 0

This pin has multiple functions.

� SPL for Sharp HR-TFT

� General purpose IO pin 3 (GPIO3)

See Table 5-8 : LCD Interface Pin Mapping for summary.

GPIO4 IO 41 D10

LB3 0

This pin has multiple functions.

� General purpose IO pin 4 (GPIO4)

See Table 5-8 : LCD Interface Pin Mapping for summary.

GPIO5 IO

40 E6

LB3 0

This pin has multiple functions.

� General purpose IO pin 5 (GPIO5)

See Table 5-8 : LCD Interface Pin Mapping for summary.

Pin Name

Type TQFP

TFBGA

Cell

RESET#

Description

SSD1908

Rev 1.0

P 13/13

Oct 2003

Solomon Systech

Pin #

Pin #

State

GPIO6 IO

39 E7

LB3 0

This pin has multiple functions.

� General purpose IO pin 6 (GPIO6)

See Table 5-8 : LCD Interface Pin Mapping for summary.

LPWMOUT

O 38 E8

LB3 0

This output pin has multiple functions.

� PWM Clock output

� General purpose output

LCVOUT O 46 C9 LB3 0

This output pin has multiple functions.

� CV Pulse Output

� General purpose output

5.3 Clock

Input

Table 5-3 : Clock Input Pin Descriptions

Pin Name Type

TQFP

Pin #

TFBGA

Pin #

Cell

RESET#

State

Description

CLKI

I

15

K6 LIS

--

Typically used as input clock source for bus clock and

memory clock

AUXCLK I 77 B1 LIS --

This pin may be used as input clock source for pixel

clock. This input pin must be connected to V

SS

if not

used.

5.4 Miscellaneous

Table 5-4 : Miscellaneous Pin Descriptions

Pin Name Type

TQFP

Pin #

TFBGA

Pin #

Cell

RESET

# State

Description

CF[7:0] I 78-85

C2, D1-

D3, E1-

E4

LIS --

These inputs are used to configure the SSD1908 � see

Table 5-6 : Summary of Power-On/Reset Options.

Note: These pins are used for configuration of the

SSD1908 and must be connected directly to IOV

DD

or V

SS

.

GPO O 47 C8

LO3 0

General Purpose Output (possibly used for controlling

the LCD power).

5.5 Power and Ground

Table 5-5 : Power And Ground Pin Descriptions

Pin Name Type

TQFP

Pin #

TFBGA

Pin #

Cell

RESET

# State

Description

IOV

DD

P

16, 26,

37, 49,

63, 76

B9, C1,

C5, E9,

H7, J10

P --

Power supply pins. It is recommended to place a 0.1

�F

bypass capacitor close to each of these pins.

COREV

DD

P

1, 51

A9, K2

P

--

COREV

DD

pins are internal voltage regulator output

pins that is used by the internal circuitry only. They

cannot be used for driving external circuitry.

Note: It is required to place a 0.1

�

�

�

�F bypass

capacitor close to each of these pins.

V

SS

P

14, 25,

36, 50,

62, 75,

100

A1,

A10,

B5,

E10,

J6, K1,

K10

P --

Ground

pins

Solomon Systech

Oct 2003

P 14/14

Rev 1.0

SSD1908

5.6 Summary of Configuration Options

These pins are used for configuration of the SSD1908 and must be connected directly to IOV

DD

or V

SS

. The state

of CF[5:0] is latched on the rising edge of RESET# or after the software reset function is activated (REG[A2h] bit

0). Changing state at any other time has no effect.

Table 5-6 : Summary of Power-On/Reset Options

Power-On/Reset State

SSD1908

Configuration

Input

1 (Connected to IOV

DD

)

0 (Connected to V

SS

)

CF[2:0]

Select host bus interface as follows:

CF2 CF1 CF0 Host

Bus

0 0 0 SH-3/SH-4

0 0 1 MC68K

#1

0 1 0 Reserved

0 1 1 Generic#1

1 0 0 Generic#2

1 0 1 Reserved

1 1 0 DragonBall

(MC68EZ328/MC68VZ328)

1 1 1 Reserved

Note: The host bus interface is 17-bit only.

CF3

Configure GPIO pins as inputs at

power-on

Configure GPIO pins as outputs at power-on

(for use by HR-TFT when selected)

CF4

Big Endian bus interface

Little Endian bus interface

CF5

WAIT# is active high

WAIT# is active low

CF[7:6]

CLKI to BCLK divide select:

CF7 CF6 CLKI to BCLK Divide Ratio

0 0 1:1

0 1 2:1

1 0 3:1

1 1 4:1

5.7 Host Bus Interface Pin Mapping

Table 5-7 : Host Bus Interface Pin Mapping

SSD1908 Pin

Name

Generic #1

Generic #2

Motorola

MC68K #1

Motorola

MC68EZ328/

MC68VZ328

DragonBall

Hitachi

SH-3

Hitachi

SH-4

A0

Connected to

V

SS

A0 LDS#

Connected to

V

SS

Connected to

VSS

Connected to

VSS

A[17:1] A[17:1] A[17:1] A[17:1] A[17:1] A[17:1]

A[17:1]

D[15:0] D[15:0]

D[15:0]

D[15:0]

1

D[15:0] D[15:0] D[15:0]

CS# External

Decode

CSX#

CSn#

CSn#

M/R# External

Decode

CLKI BUSCLK

BUSCLK CLK CLKO CKIO

CKIO

BS#

Connected to IOV

DD

AS#

Connected to

IOV

DD

BS# BS#

RD/WR# RD1#

Connected to

IOV

DD

R/W#

Connected to

IOV

DD

RD/WR# RD/WR#

RD# RD0#

RD#

Connected to

IOV

DD

OE# RD# RD#

WE0# WE0# WE#

Connected to

IOV

DD

LWE# WE0# WE0#

WE1# WE1# BHE# UDS#

UWE#

WE1#

WE1#

WAIT# WAIT#

WAIT#

DTACK#

DTACK#

WAIT#/ RDY#

RESET# RESET# RESET# RESET# RESET# RESET#

RESET#

Note

1

If the target MC68K bus is 32-bit, then these signals should be connected to D[31:16].

SSD1908

Rev 1.0

P 15/15

Oct 2003

Solomon Systech

5.8

LCD Interface Pin Mapping

Table 5-8 : LCD Interface Pin Mapping

Pin Name

Monochrome

Passive Panel

Color Passive Panel

Color TFT Panel

Analog TFT

Panel

4-bit

8-bit

4-bit

8-bit

9-bit

12-bit

18-bit

18-bit Sharp

(format

stripe)

HR-TFT

1

LFRAME

LFRAME

SPS

VSD

LLINE

LLINE

LP

HSD

LSHIFT LSHIFT

CLK

DCLK

LDEN MOD

LDEN

Drive

0

DEN

LDATA0

Drive 0

D0

Drive 0

D0(G3)

2

R2 R3 R5 R5

D0

LDATA1

Drive 0

D1

Drive 0

D1(R3)

2

R1 R2 R4 R4

D1

LDATA2

Drive 0

D2

Drive 0

D2(B2)

2

R0 R1 R3 R3

D2

LDATA3

Drive 0

D3

Drive 0

D3(G2)

2

G2 G3 G5 G5

D3

LDATA4 D0 D4

D0(R2)

2

D4(R2)

2

G1 G2 G4 G4

D4

LDATA5 D1 D5

D1(B1)

2

D5(B1)

2

G0 G1 G3 G3

D5

LDATA6 D2 D6

D2(G1)

2

D6(G1)

2

B2 B3 B5 B5

D6

LDATA7 D3 D7

D3(R1)

2

D7(R1)

2

B1 B2 B4 B4

D7

LDATA8

Drive 0

Drive 0

Drive 0

Drive 0

B0

B1

B3

B3

Drive 0

LDATA9

Drive 0

Drive 0

Drive 0

Drive 0

Drive 0

R0

R2

R2

Drive 0

LDATA10

Drive 0

Drive 0

Drive 0

Drive 0

Drive 0

Drive 0

R1

R1

Drive 0

LDATA11

Drive 0

Drive 0

Drive 0

Drive 0

Drive 0

Drive 0

R0

R0

Drive 0

LDATA12

Drive 0

Drive 0

Drive 0

Drive 0

Drive 0

G0

G2

G2

Drive 0

LDATA13

Drive 0

Drive 0

Drive 0

Drive 0

Drive 0

Drive 0

G1

G1

Drive 0

LDATA14

Drive 0

Drive 0

Drive 0

Drive 0

Drive 0

Drive 0

G0

G0

Drive 0

LDATA15

Drive 0

Drive 0

Drive 0

Drive 0

Drive 0

B0

B2

B2

Drive 0

LDATA16

Drive 0

Drive 0

Drive 0

Drive 0

Drive 0

Drive 0

B1

B1

Drive 0

LDATA17

Drive 0

Drive 0

Drive 0

Drive 0

Drive 0

Drive 0

B0

B0

Drive 0

GPIO0 GPIO0 GPIO0 GPIO0 GPIO0 GPIO0 GPIO0 GPIO0

PS

GPIO0

GPIO1 GPIO1 GPIO1 GPIO1 GPIO1 GPIO1 GPIO1 GPIO1

CLS

GPIO1

GPIO2 GPIO2 GPIO2 GPIO2 GPIO2 GPIO2 GPIO2 GPIO2

REV

GPIO2

GPIO3 GPIO3 GPIO3 GPIO3 GPIO3 GPIO3 GPIO3 GPIO3

SPL

GPIO3

GPIO4 GPIO4 GPIO4 GPIO4 GPIO4 GPIO4 GPIO4 GPIO4

GPIO4

(output only)

GPIO4

GPIO5 GPIO5 GPIO5 GPIO5 GPIO5 GPIO5 GPIO5 GPIO5

GPIO5

(output only)

GPIO5

GPIO6 GPIO6 GPIO6 GPIO6 GPIO6 GPIO6 GPIO6 GPIO6

GPIO6

(output only)

GPIO6

GPO

GPO (General Purpose Output)

LCVOUT LCVOUT

LPWMOUT LPWMOUT

Note

1

GPIO pins must be configured as outputs (CF3 = 0 during RESET# active) when HR-TFT panels are selected.

2

These pin mappings use signal names commonly used for each panel type, however signal names may differ

between panel manufacturers. The values shown in brackets represent the color components as mapped to the

corresponding LDATAxx signals at the first valid edge of LSHIFT. For further LDATAxx to LCD interface

mapping, see Section 10.4 "Display Interface".

Solomon Systech

Oct 2003

P 16/16

Rev 1.0

SSD1908

5.9 Data Bus Organization

There are two data bus architectures, little endian and big endian. Little endian means the bytes at lower

addresses have lower significance. Big endian means the most significant byte has the lowest address.

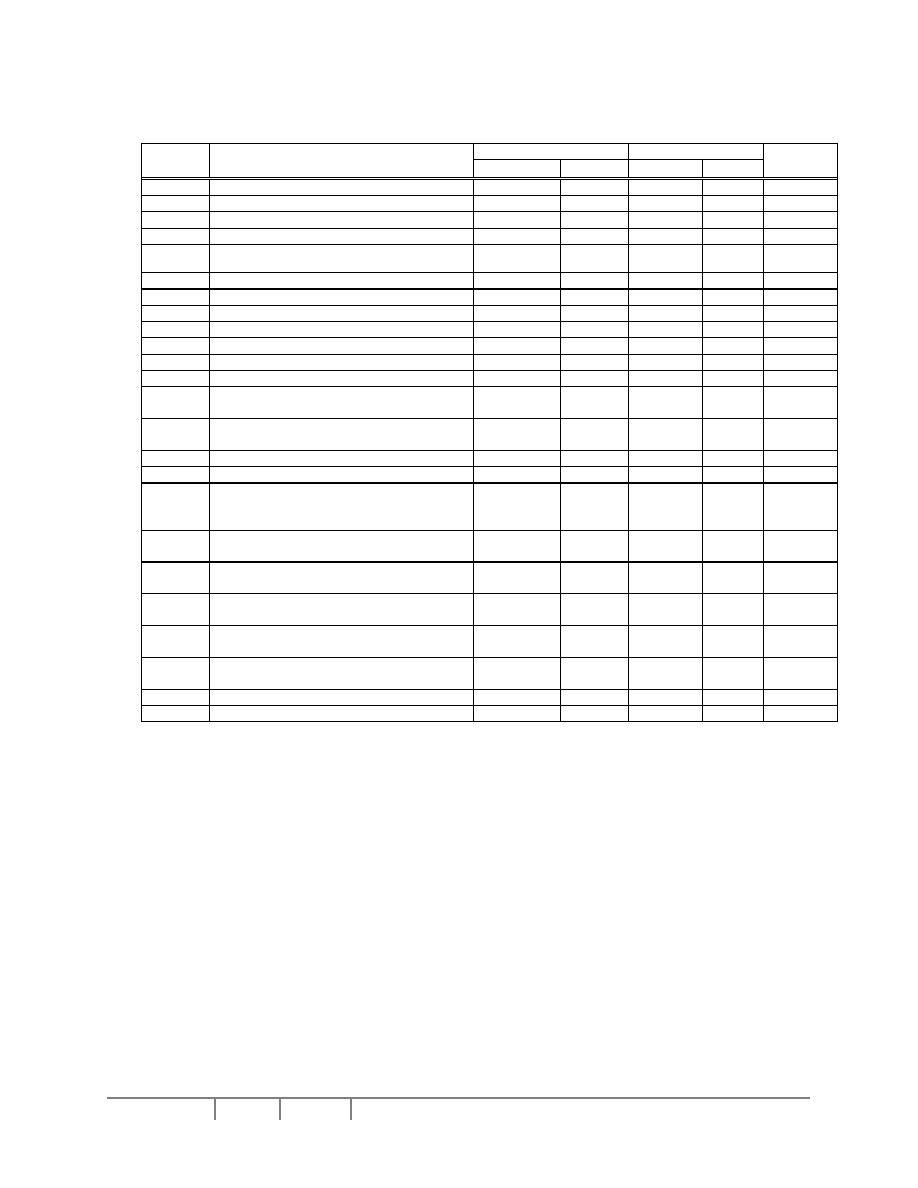

Table 5-9 : Data Bus Organization

D[15:8]

D[7:0]

Big endian

2N

2N + 1

Little endian

2N + 1

2N

N : Byte Address

Table 5-10 : Pin State Summary

MCU Mode (Endian)

A0 RD/WR# RD# WE1# WE0#

Operation

X 0 0 1 1

Word

read

X

0

1

1

1

High byte read 2N

X

1

0

1

1

Low byte read 2N+1

X 1 1 0 0

Word

write

X

1

1

0

1

High byte write 2N

Generic#1 (Big)

X

1

1

1

0

Low byte write 2N+1

X 0 0 1 1

Word

read

X

0

1

1

1

High byte read 2N+1

X

1

0

1

1

Low byte read 2N

X 1 1 0 0

Word

write

X

1

1

0

1

High byte write 2N+1

Generic#1 (Little)

X

1

1

1

0

Low byte write 2N

0 X 0 0 1

Word

read

0

X

0

1

1

High byte read 2N

1

X

0

0

1

Low byte read 2N+1

0 X 1 0 0

Word

write

0

X

1

1

0

High byte write 2N

Generic#2 (Big)

1

X

1

0

0

Low byte write 2N+1

0 X 0 0 1

Word

read

1

X

0

0

1

High byte read 2N+1

0

X

0

1

1

Low byte read 2N

0 X 1 0 0

Word

write

1

X

1

0

0

High byte write 2N+1

Generic#2 (Little)

0

X

1

1

0

Low byte write 2N

0 1 X 0 X

Word

read

1

1

X

0

X

High byte read 2N

0

1

X

1

X

Low byte read 2N+1

0 0 X 0 X

Word

write

1

0

X

0

X

High byte write 2N

MC68K#1 (Big)

0

0

X

1

X

Low byte write 2N+1

0 1 X 0 X

Word

read

0

1

X

1

X

High byte read 2N+1

1

1

X

0

X

Low byte read 2N

0 0 X 0 X

Word

write

0

0

X

1

X

High byte write 2N+1

MC68K#1 (Little)

1

0

X

0

X

Low byte write 2N

SSD1908

Rev 1.0

P 17/17

Oct 2003

Solomon Systech

MCU Mode (Endian)

A0 RD/WR# RD# WE1# WE0#

Operation

X X 0 X X

Word

read

X X 1 0 0

Word

write

X

X

1

0

1

High byte write 2N

MC68EZ328 /

MC68VZ328 (Big)

X

X

1

1

0

Low byte write 2N+1

X X 0 X X

Word

read

X X 1 0 0

Word

write

X

X

1

0

1

High byte write 2N+1

MC68EZ328 /

MC68VZ328 (Little)

X

X

1

1

0

Low byte write 2N

X X 0 1 1

Word

read

X X 1 0 0

Word

write

X

X

1

0

1

High byte write 2N

SH-3/SH-4 (Big)

X

X

1

1

0