| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: CXA1352AS | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

--1--

E91912B95-TE

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

Absolute Maximum Ratings (Ta=25 ∞C)

∑ Supply voltage

V

CC

12

V

∑ Storage temperature

Tstg

≠65 to +150

∞C

∑ Allowable power dissipation

P

D

1200

mW

Operating Conditions

∑ Supply voltage

V

CC

4.0 to 10.0

V

DV

CC

3.5 to V

CC

V

∑ Operating temperature

Topr

≠20 to +75

∞C

Description

The CXA1352AS is a bipolar IC for graphic

equalizer use. All controls are DC performed while

the addition of single-potentiometers easily

composes a 2-channel graphic equalizer.

Features

∑ Microcomputer control possible

∑ Built-in electronic volume

∑ Built-in pseudo loudness function

∑ Built-in balance function

∑ Each channel corresponds to 5 elements

∑ 2 channels of FIX OUT and LINE OUT pins

Applications

Graphic equalizer for cassette tape recorder with

radio, mobile stereo and portable stereo

Structure

Bipolar silicon monolithic IC

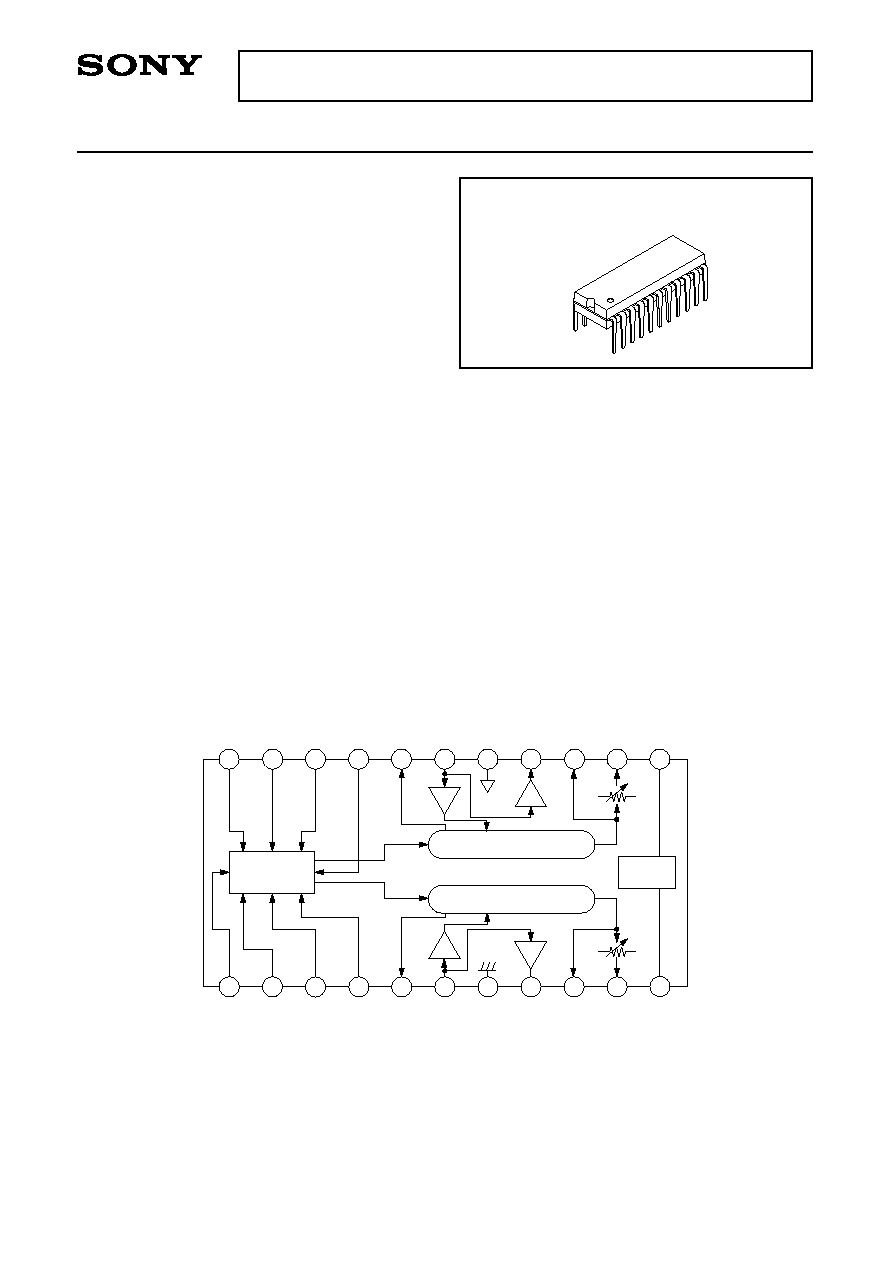

2-channel 5 Elements Graphic Equalizer IC

22 pin SDIP (Plastic)

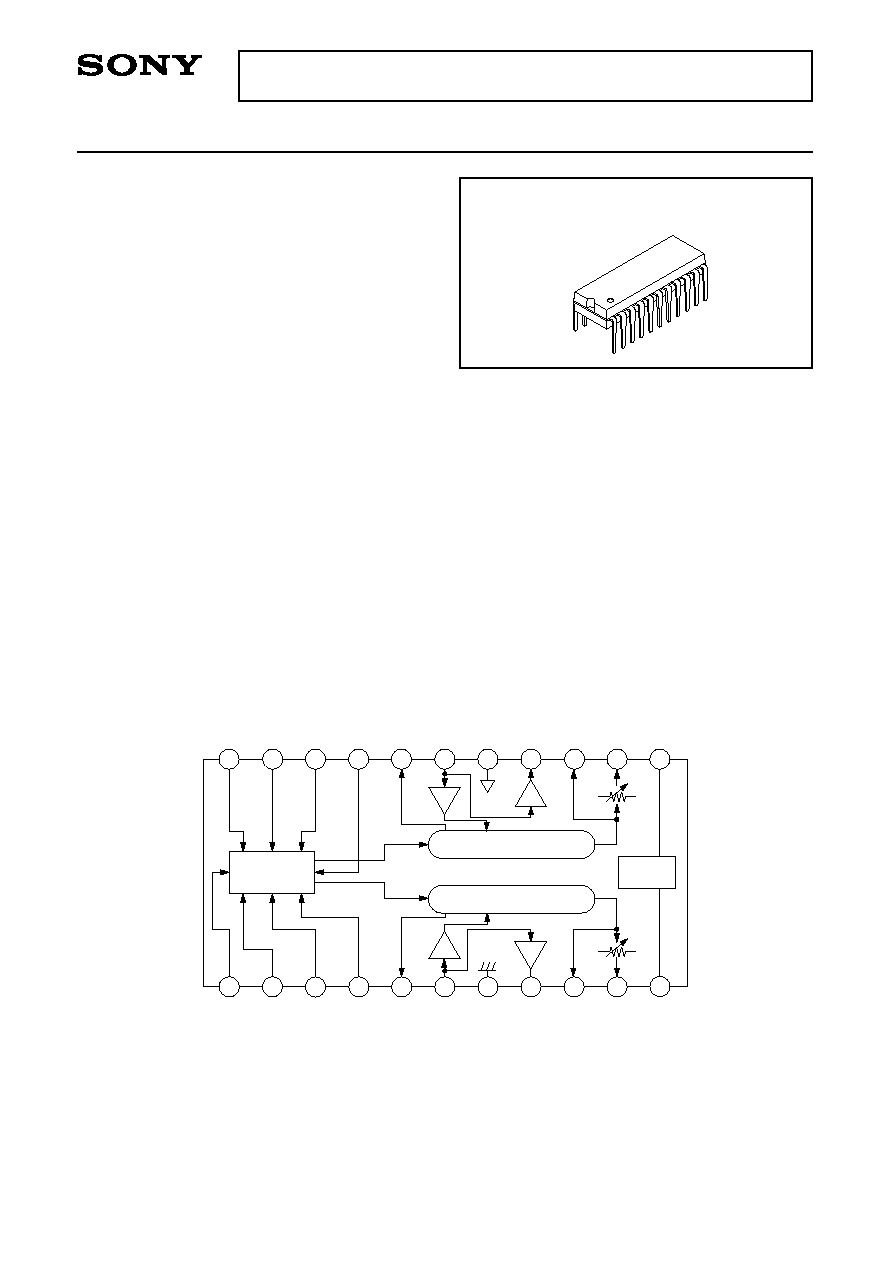

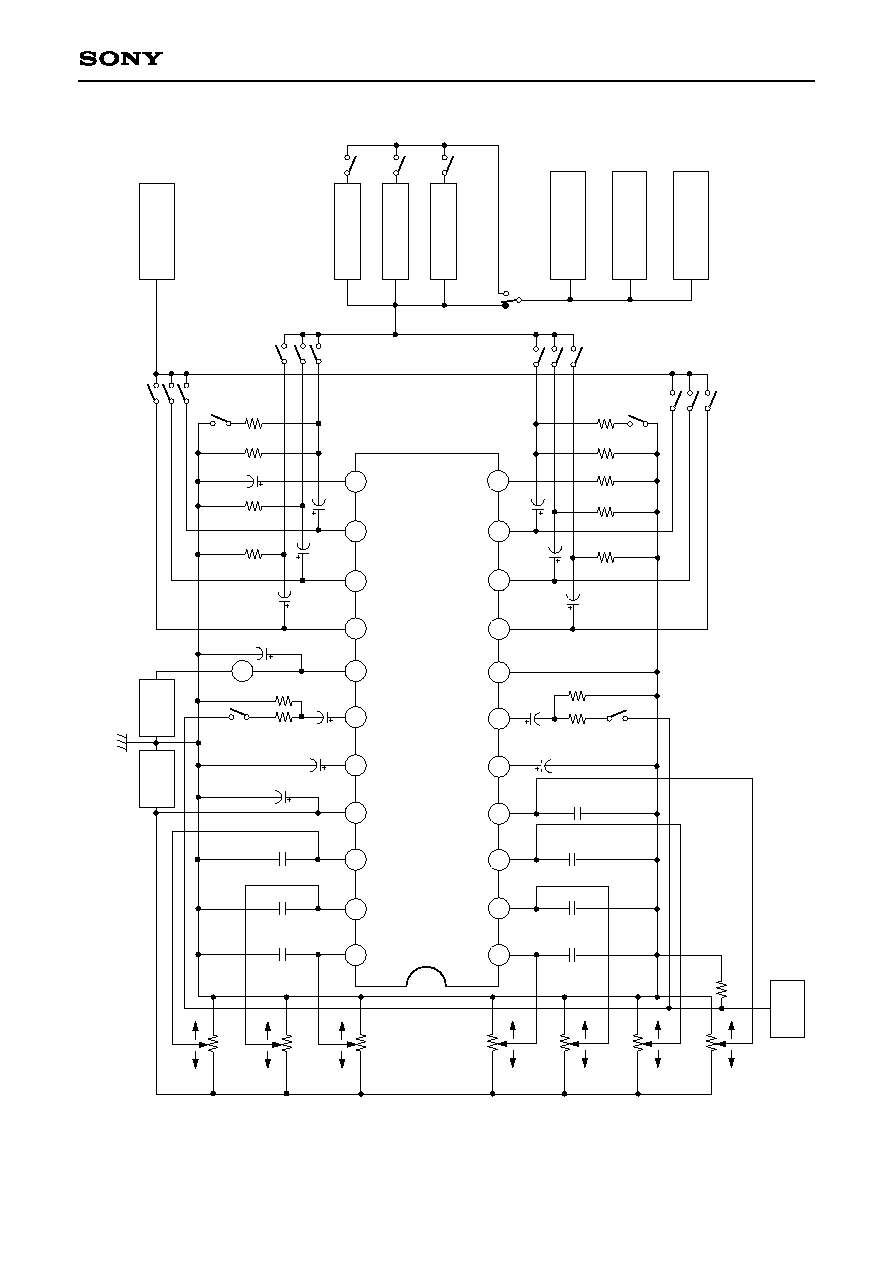

Block Diagram and Pin Configuration

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

GRAPHIC EQUALIZER

GRAPHIC EQUALIZER

BIAS

VOLUME

VOLUME

CONTROL

14dB

14dB

29dB

29dB

1kHz

400Hz

100Hz

BAL

VOL

DC1

1N1

GND

LINE

OUT1

OUT1

(Fix)

OUT1

(V

ARIABLE)

4kHz

10kHz

DC2

IN2

VG

LINE

OUT2

OUT2

(FIX)

OUT2

(V

ARIABLE)

DV

CC

V

CC

ISET

CXA1352AS

--2--

CXA1352AS

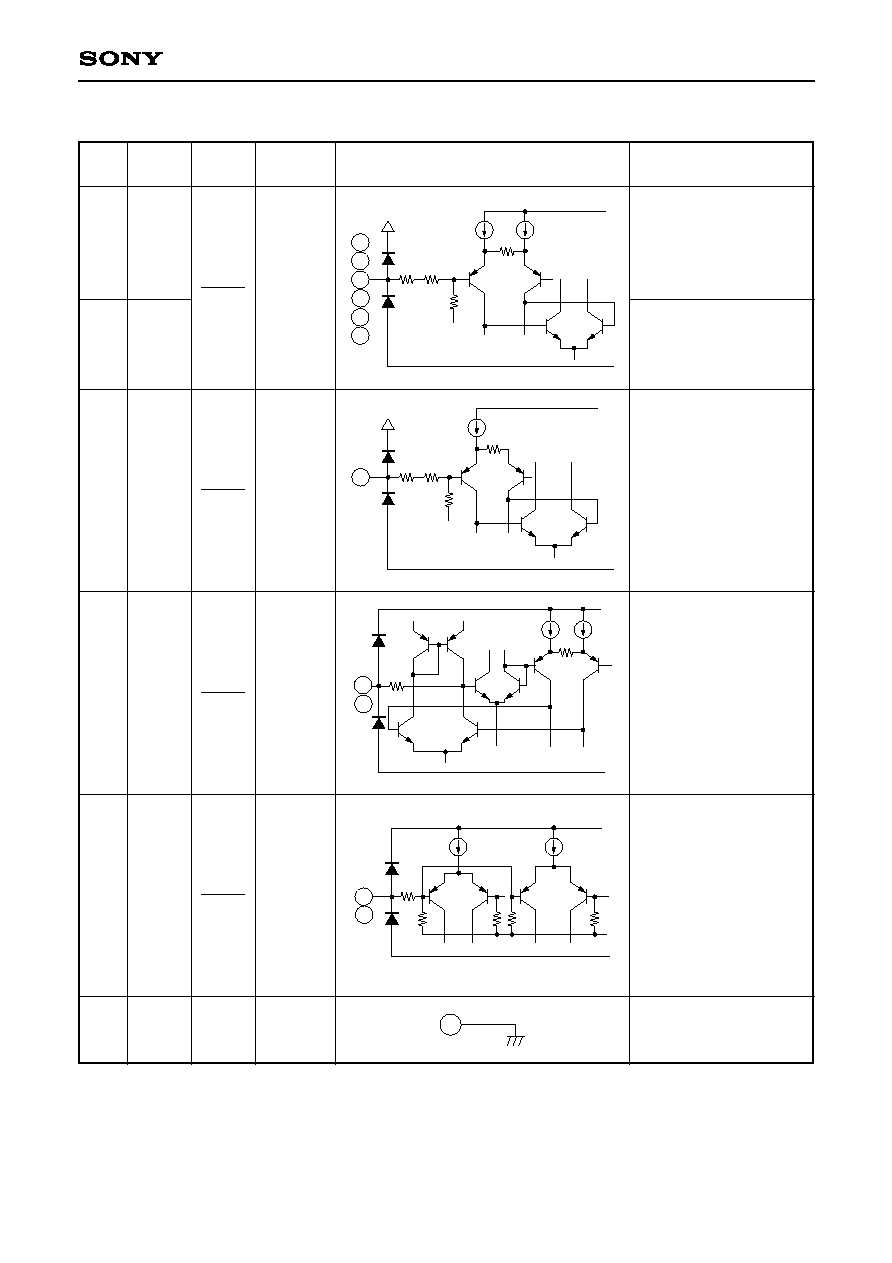

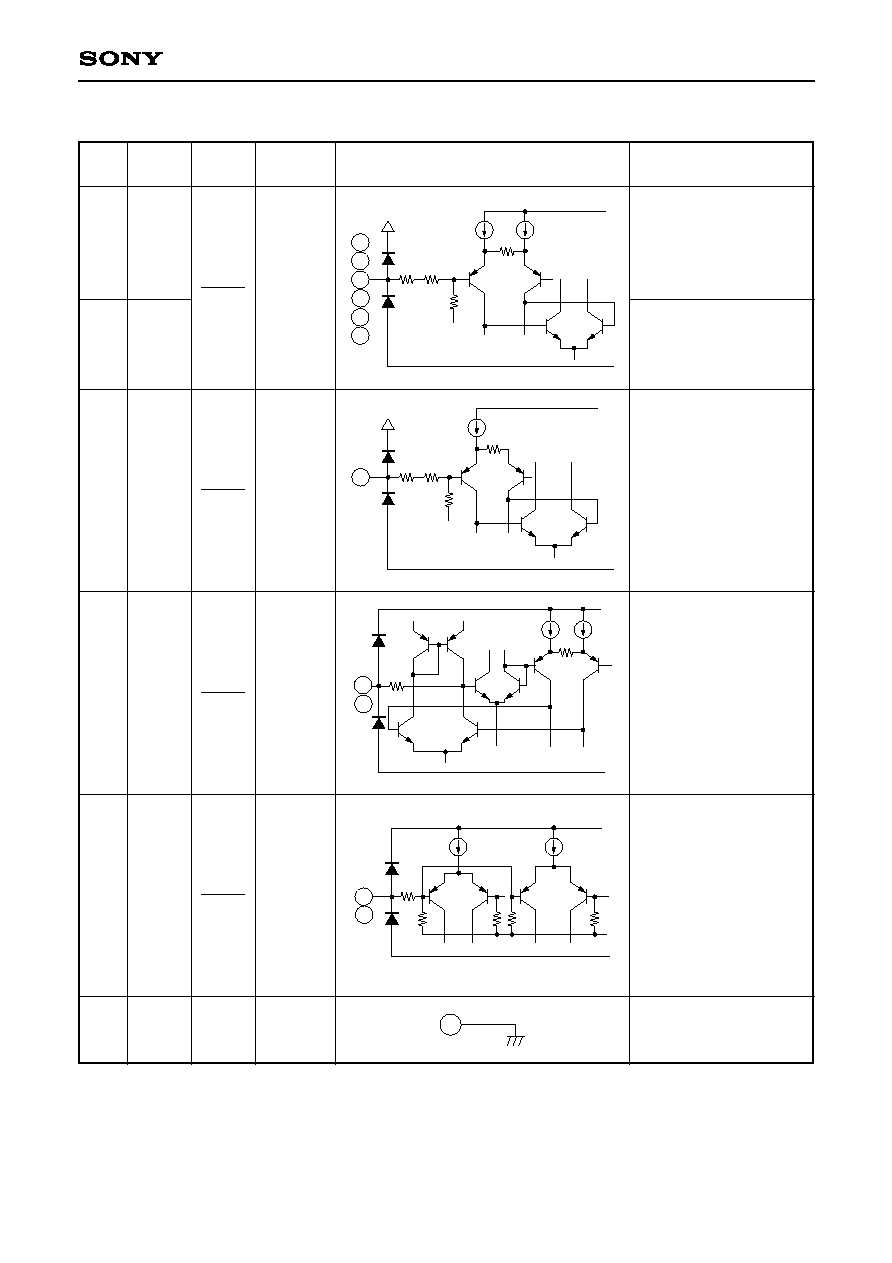

Pin Description

Pin

Symbol Voltage

I/O

Equivalent circuit

Description

No.

resistance

1

2

20

21

22

4

3

5

18

6

17

7

400 Hz

100 Hz

10 kHz

4 kHz

1 kHz

VOL

BAL

DC1

DC2

IN1

IN2

GND

DV

CC

2

DV

CC

2

V

CC

2

V

CC

2

GND

60 k

60 k

--

25 k

1

2

4

20

21

22

DV

CC

V

CC

10k

147 40k

20k

GND

DV

CC

V

CC

9k

147 40k

20k

GND

3

18

V

CC

147

30k

GND

5

6

17

V

CC

147

50k

50k

1k

5k

GND

7

Graphic equalizer control

pin

DC input

Volume control pin

DC input

Balance control pin

DC input

Connects the DC

feedback capacitor of the

LPF used in the 100 Hz

graphic equalizer

Signal input pin

GND pin

--3--

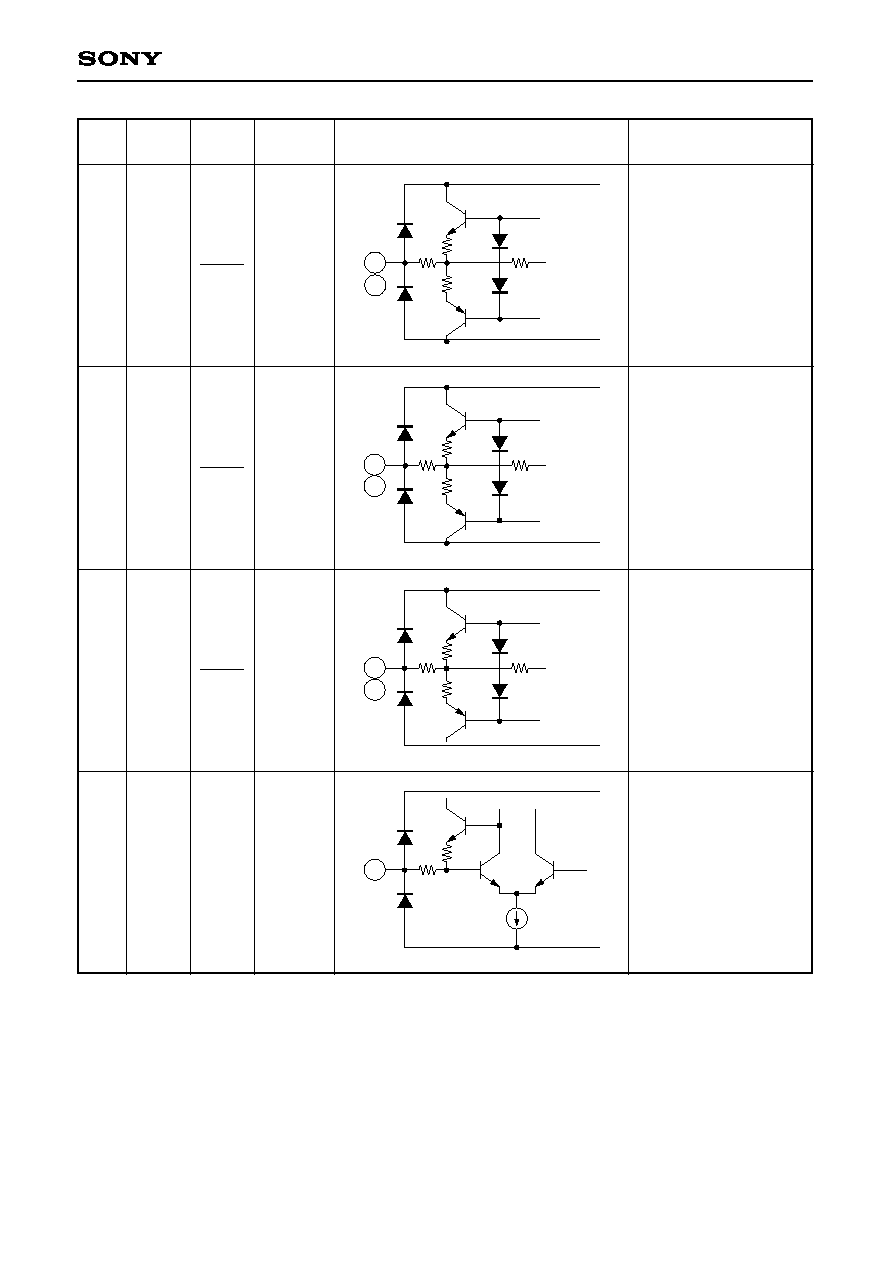

CXA1352AS

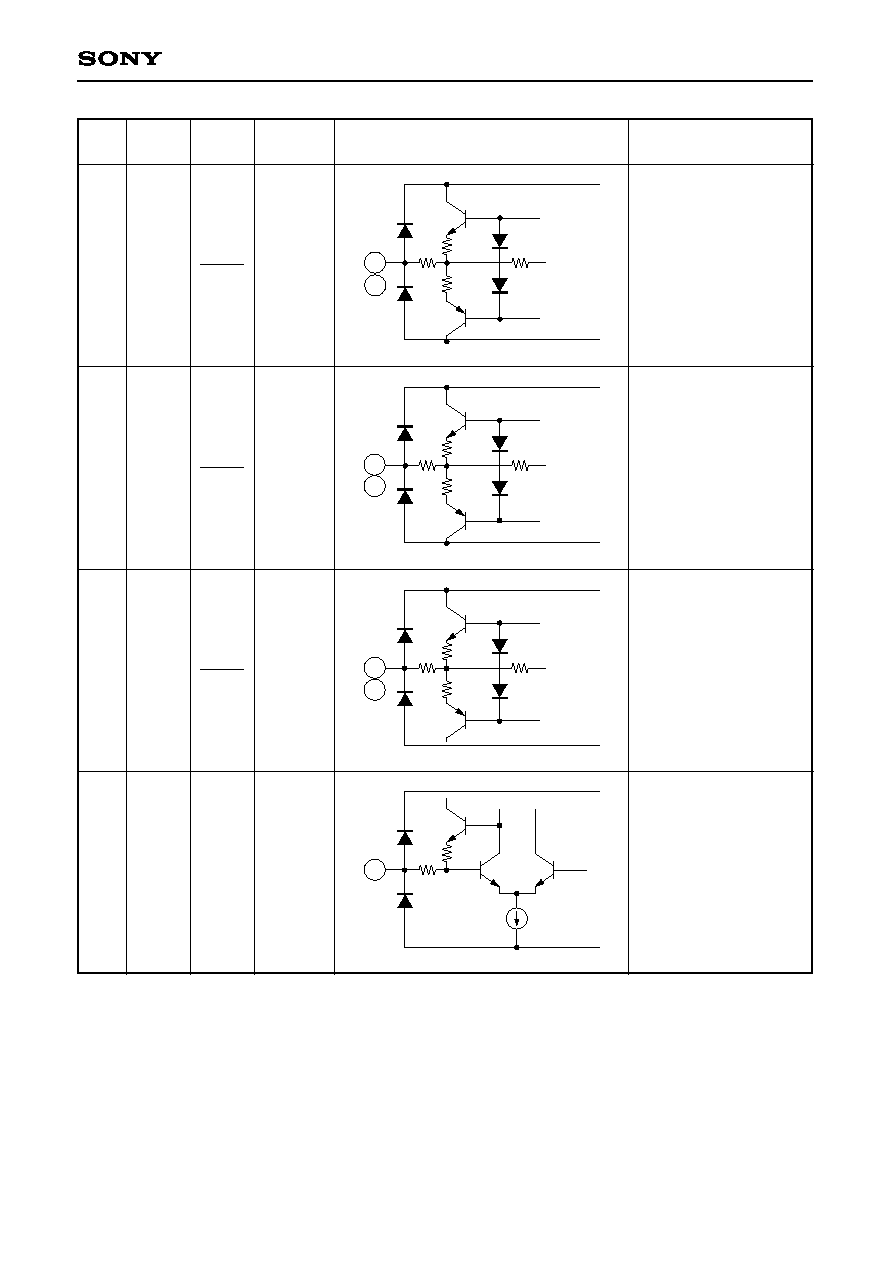

Pin

Symbol Voltage

I/O

Equivalent circuit

Description

No.

resistance

8

15

9

14

10

13

11

L OUT1

L OUT2

F OUT1

F OUT2

OUT1

OUT2

ISET

V

CC

2

V

CC

2

V

CC

2

1.3 V

0

0

0

0

V

CC

147

27k

300

300

GND

8

15

14

V

CC

147

30k

300

300

GND

9

13

V

CC

147

20k

250

250

GND

10

V

CC

147

300

GND

11

Line output pin

Fix output pin

Electronic volume output

pin

Reference current setting

pin

(for graphic equalizer)

Normally 160 k

resistor

is connected

--4--

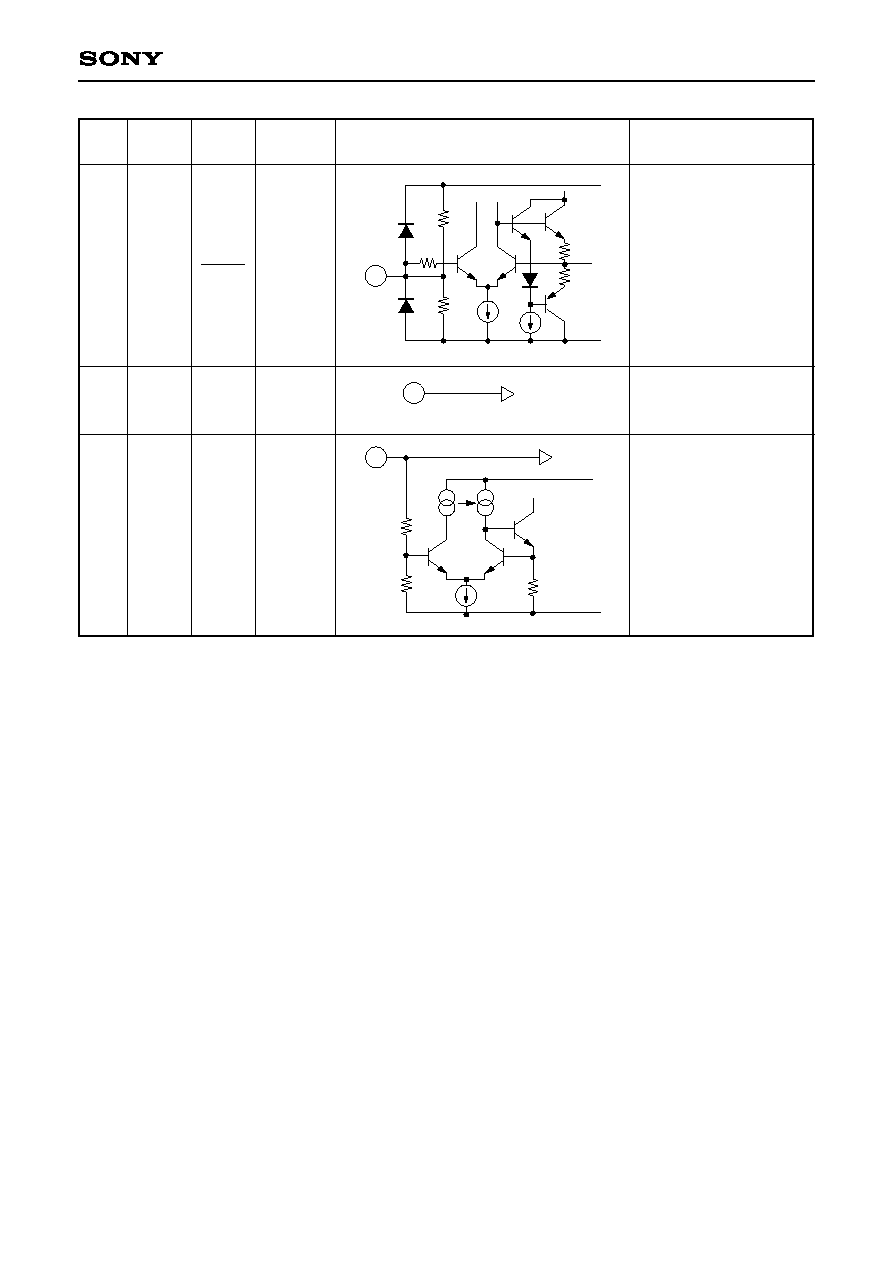

CXA1352AS

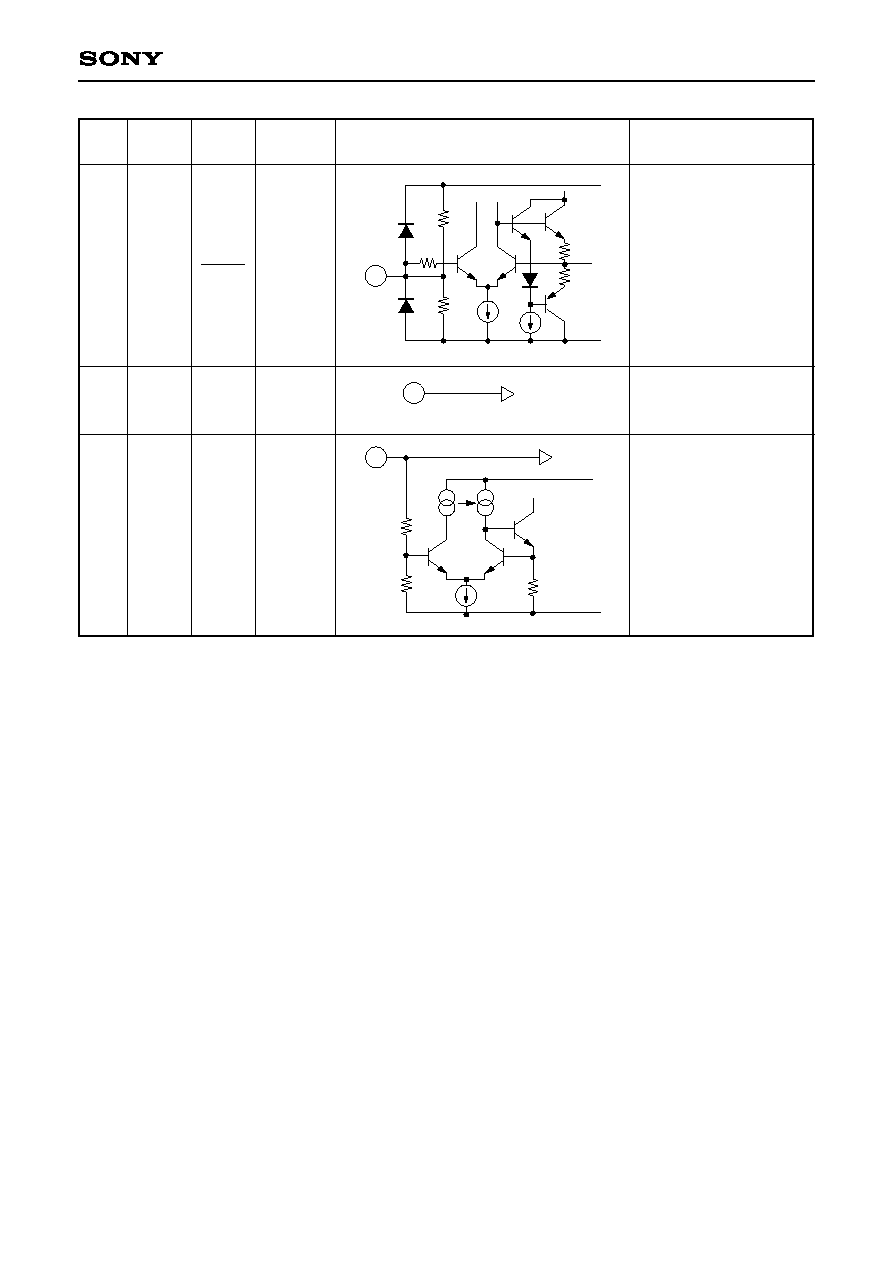

Pin

Symbol Voltage

I/O

Equivalent circuit

Description

No.

resistance

12

16

19

VG

V

CC

DV

CC

V

CC

2

V

CC

DV

CC

20 k

60 k

V

CC

147

40k

40k

300

GND

12

300

V

CC

16

V

CC

DV

CC

GND

19

30k

30k

42k

Signal reference voltage

pin

A capacitor is connected

for ripple rejection

Power supply pin

(operation)

Power supply pin (control)

--5--

CXA1352AS

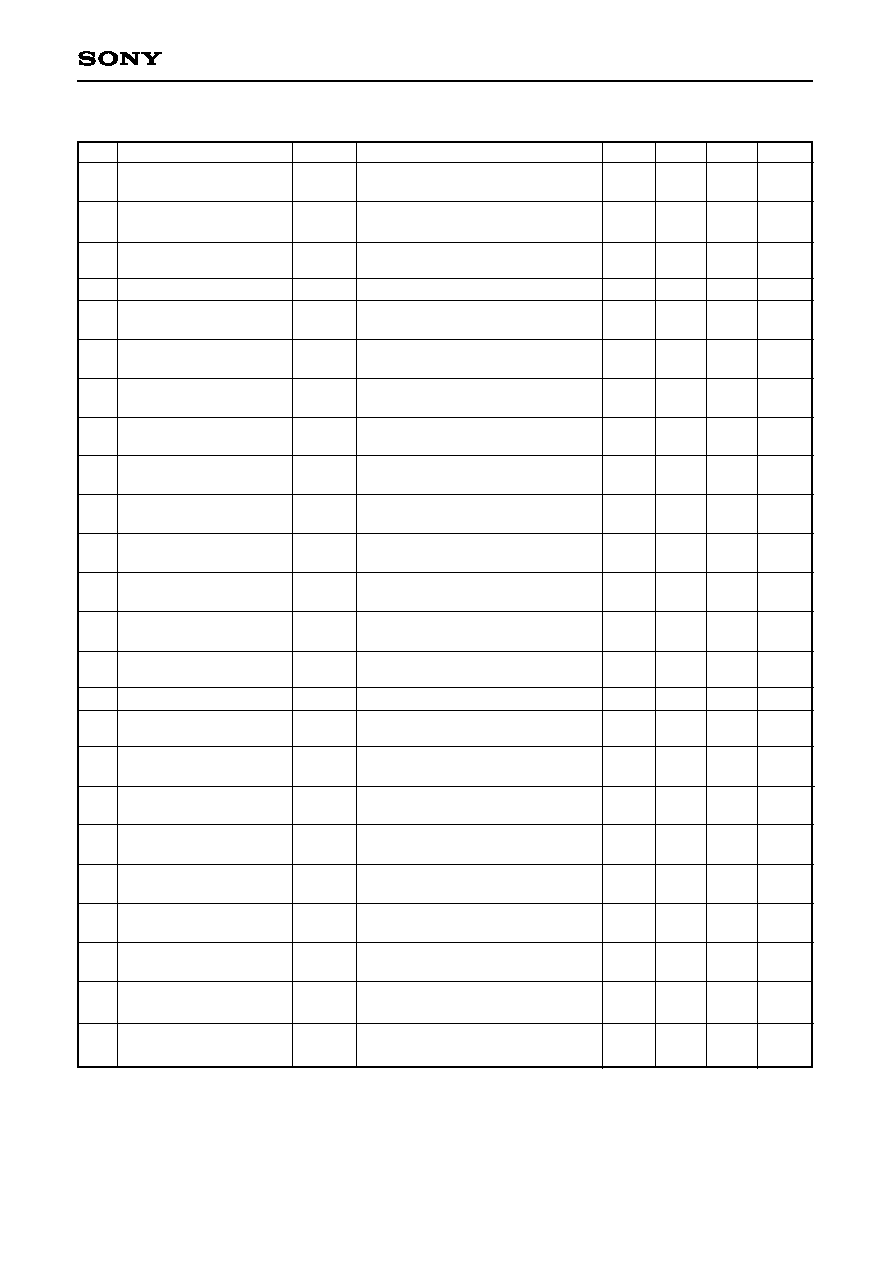

Electrical Characteristics

(Ta=25 ∞C, V

CC

=8 V, DV

CC

=5 V)

No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

Item

Supply voltage

(operation)

Supply voltage

(control)

Current consumption

Reference input level

Reference output level

Reference LINE

output level

Reference FIX

output level

Graphic equalizer

setting frequency (1)

Graphic equalizer

setting frequency (2)

Graphic equalizer

setting frequency (3)

Graphic equalizer

setting frequency (4)

Graphic equalizer

setting frequency (5)

Graphic equalizer

frequency deviation

Maximum boost (1)

Maximum boost (2)

Maximum cut (1)

Maximum cut (2)

Total harmonic

distortion

Volume attenuation (1)

Volume attenuation (2)

Balance adjustment (1)

Balance adjustment (2)

Noise level

Output offset voltage

Symbol

V

CC

DV

CC

I

CC

V

IN

V

OUT

V

LINE

V

FIX

GEQ1

GEQ2

GEQ3

GEQ4

GEQ5

EQ

GEQB1

GEQB2

GEQC1

GEQC2

THD

VOL1

VOL2

BAL1

BAL2

V

NOIS

V

OFF

Test conditions

Graphic equalizer ALL FLAT,

Volume MID

Graphic equalizer ALL FLAT,

Volume MAX, f=1 kHz

f=1 kHz

Graphic equalizer ALL FLAT,

f=1 kHz

LPF cut off frequency (≠3 dB)

BPF (1) central frequency

BPF (2) central frequency

BPF (3) central frequency

HPF cut off frequency (≠3 dB)

Cut off frequency and central

frequency deviation

f=400 Hz, 1 kHz, 4 kHz

maximum boost

f=100 Hz, 10 kHz maximum boost

f=400 Hz, 1 kHz, 4kHz

maximum cut

f=100 Hz, 10 kHz maximum cut

R

L

=2 k

, Graphic equalizer

ALL FLAT, Volume MAX, f=1 kHz,

Reference +10 dB is input

Graphic equalizer ALL FLAT,

Volume MAX, f=1 kHz

Graphic equalizer ALL FLAT,

Volume MIN, f=1 kHz

Graphic equalizer ALL FLAT,

BAL=MAX,Volume MAX, f=1kHz

Graphic equalizer ALL FLAT,

BAL=MIN, Volume MAX, f=1kHz

Rg=5 k

, Graphic equalizer ALL

FLAT, Volume MAX, "A" WTG filter

Graphic equalizer ALL FLAT,

Volume MAX

Min.

Typ.

Max.

Unit

4.0

--

10.0

V

3.5

--

V

CC

V

8.0

12.0

16.0

mA

--

≠34.0

--

dBm

≠23.0 ≠20.0 ≠17.0

dBm

≠6.5

≠4.5

≠2.5

dBm

≠23.0 ≠20.0 ≠17.0

dBm

--

200

--

Hz

--

400

--

Hz

--

1.0

--

kHz

--

4.0

--

kHz

--

8.0

--

kHz

≠20

0

20

%

9.0

11.2

14.0

dB

8.0

10.7

14.0

dB

≠13.0 ≠10.7

≠8.5

dB

≠12.0

≠9.5

≠7.0

dB

--

0.25

1.0

%

≠1.5

0

1.5

dB

--

≠94.4 ≠80.0

dB

--

0

--

dB

--

≠66

--

dB

--

≠93.1 ≠88.0

dB

3.5

4.0

4.5

V

--6--

CXA1352AS

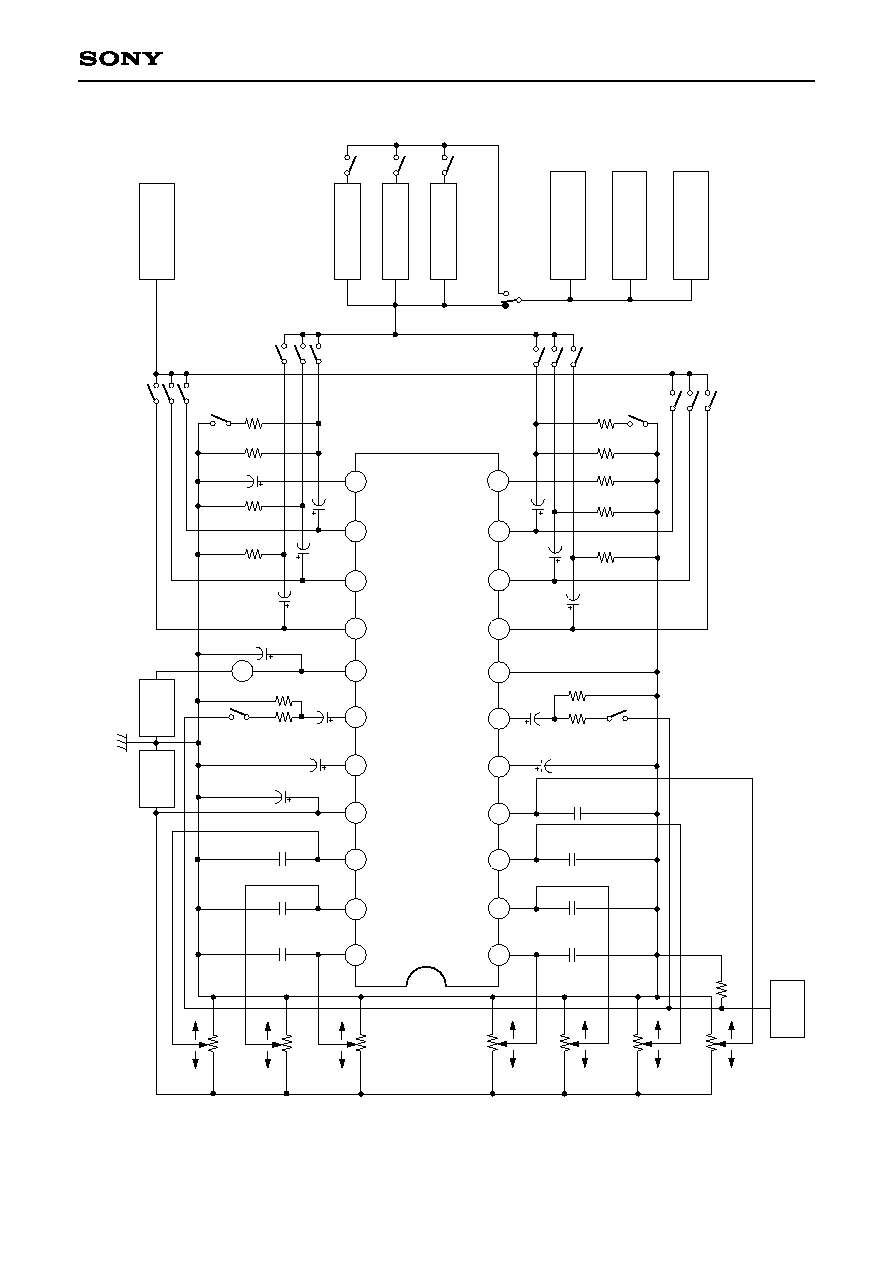

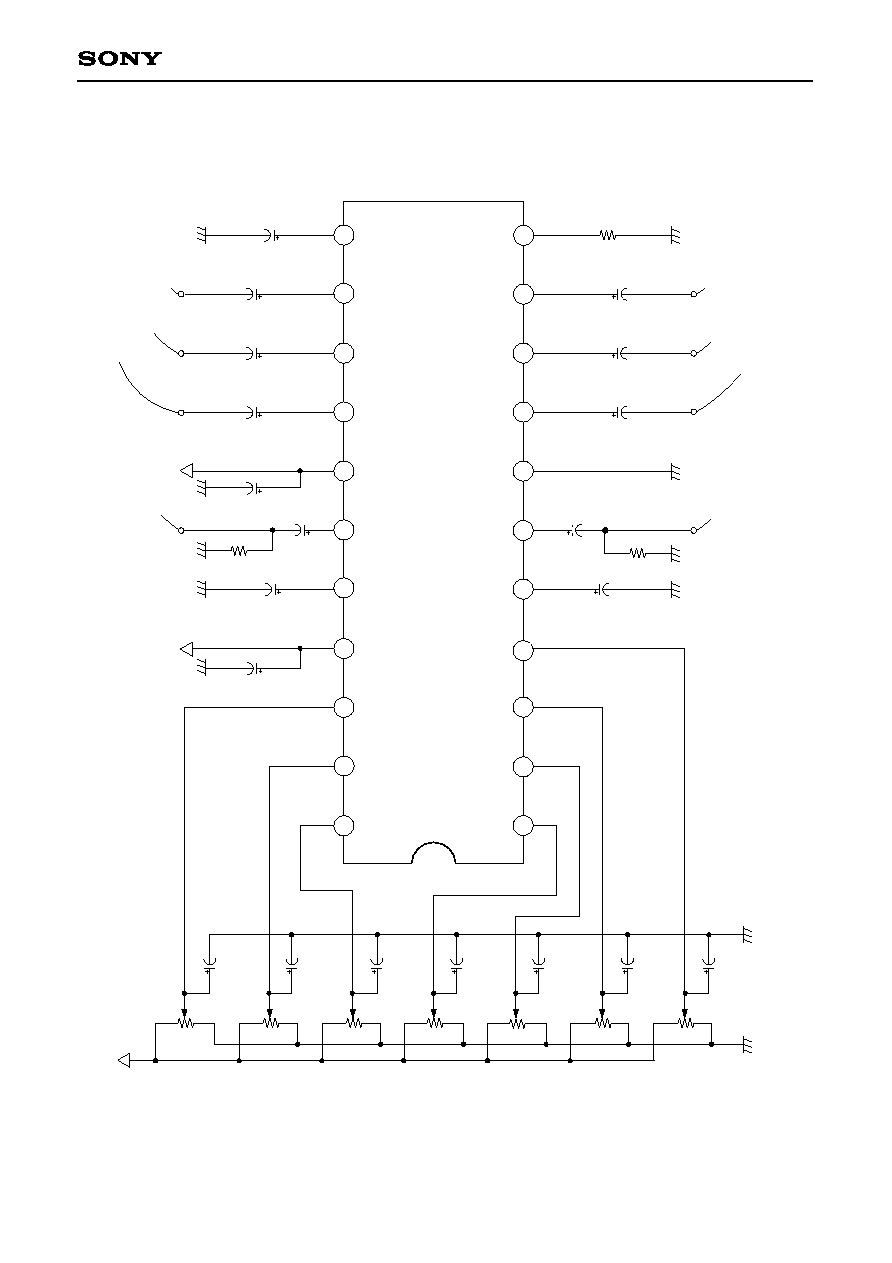

Electrical Characteristics Test Circuit

1

2

3

4

5

6

7

9

1

0

1

1

1

2

1

3

1

4

1

6

1

7

1

8

1

9

2

0

2

1

2

2

G

N

D

P

O

W

E

R

S

U

P

P

L

Y

P

O

W

E

R

S

U

P

P

L

Y

D

C

V

O

L

T

M

E

T

E

R

S

1

0

S

1

6

S

2

0

S

1

5

S

1

4

S

9

S

8

S

4

R

2

0

2

k

R

1

6

2

0

k

R

1

4

2

0

k

R

1

2

5

.

1

k

R

1

0

3

9

k

R

1

9

2

0

k

1

k

H

z

B

P

F

S

1

9

S

1

8

D

I

N

A

U

D

I

O

"

A

"

W

T

G

N

O

I

S

E

F

I

L

T

E

R

O

U

T

S

1

7

I

N

F

I

L

T

E

R

S

1

3

S

1

2

S

1

1

A

C

V

O

L

T

M

E

T

E

R

D

I

S

T

O

R

T

I

O

N

A

N

A

L

Y

Z

E

R

O

S

C

I

L

L

O

≠

S

C

O

P

E

N

O

T

E

1

.

R

E

S

I

S

T

O

R

T

O

L

E

R

A

N

C

E

2

.

C

A

P

A

C

I

T

O

R

T

O

L

E

R

A

N

C

E

C

O

U

P

L

I

N

G

C

A

P

A

C

I

T

P

R

±

5

%

±

1

%

±

5

%

±

2

%

±

1

0

%

R

2

1

2

k

R

1

8

2

0

k

R

1

7

1

6

0

k

R

1

5

2

0

k

R

1

3

2

0

k

S

3

S

7

S

6

S

5

C

1

8

4

.

7

µ

/

2

5

V

C

1

9

4

.

7

µ

/

2

5

V

C

1

6

4

.

7

µ

/

2

5

V

C

1

1

4

.

7

µ

/

2

5

V

C

1

7

4

.

7

µ

/

2

5

V

C

1

4

4

.

7

µ

/

2

5

V

C

1

5

4

.

7

µ

/

2

5

V

8

1

5

C

2

0

4

7

µ

/

2

5

V

C

1

3

1

0

0

µ

/

2

5

V

C

1

0

4

.

7

µ

/

2

5

V

C

8

1

0

0

µ

/

2

5

V

C

6

1

0

0

0

p

C

4

1

0

0

0

p

C

2

1

0

0

0

p

C

1

1

0

0

0

p

C

3

1

0

0

0

p

C

5

1

0

0

0

p

C

7

1

0

0

0

p

C

9

4

.

7

µ

/

2

5

V

C

1

2

4

.

7

µ

/

2

5

V

A

S

2

B

O

O

S

T

C

U

T

B

O

O

S

T

C

U

T

B

O

O

S

T

C

U

T

B

O

O

S

T

C

U

T

B

O

O

S

T

C

U

T

C

H

2

C

H

1

M

A

X

M

I

N

R

7

5

0

k

R

6

5

0

k

R

5

5

0

k

R

4

5

0

k

R

3

5

0

k

R

2

5

0

k

R

1

5

0

k

R

8

6

2

0

A

U

D

I

O

S

G

R

9

3

9

k

R

1

1

5

.

1

k

S

1

C

X

A

1

3

5

2

A

S

40

0H

z

10

0H

z

BA

L

VO

L

1k

Hz

4k

Hz

10

kH

z

DV

CC

DC

1

IN

1

GN

D

L O

UT

1

F O

UT

1

OU

T1

IS

ET

DC

2

IN

2

V

CC

L O

UT

2

F O

UT

2

OU

T2

VG

--7--

CXA1352AS

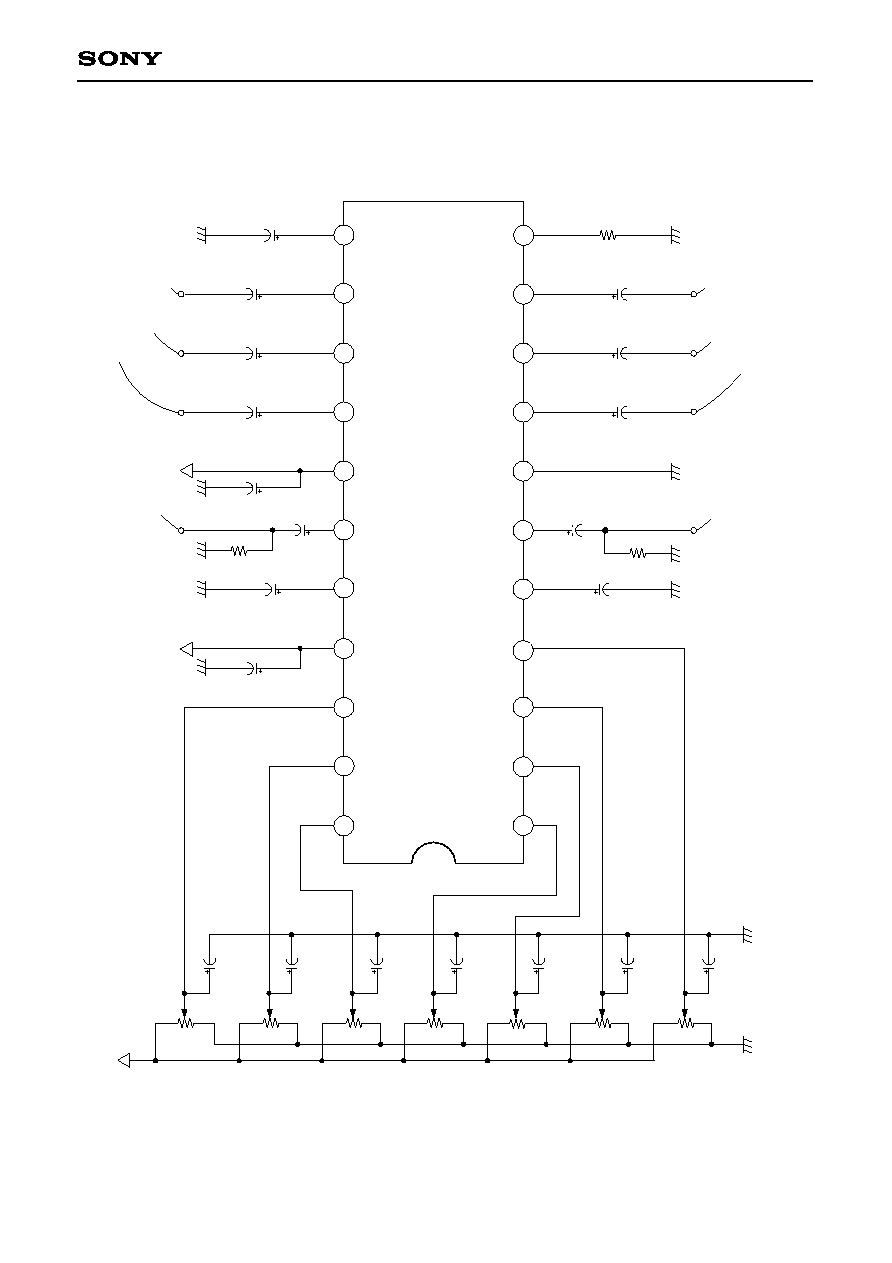

Application Circuit

2

1

2

2

1

2

1

3

1

4

1

5

1

6

1

7

1

8

1

9

2

0

1

2

3

4

5

6

7

8

9

1

0

1

1

R

7

5

0

k

R

6

5

0

k

C

7

2

.

2

µ

C

6

2

.

2

µ

R

5

5

0

k

C

5

2

.

2

µ

R

4

5

0

k

C

4

2

.

2

µ

R

3

5

0

k

C

3

2

.

2

µ

R

2

5

0

k

C

2

2

.

2

µ

R

1

5

0

k

C

1

2

.

2

µ

C

9

4

.

7

µ

C

1

1

4

.

7

µ

C

1

4

2

.

2

µ

C

1

6

2

.

2

µ

C

1

8

2

.

2

µ

R

1

0

1

6

0

k

R

8

5

.

1

k

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

V

C

C

G

N

D

S

i

g

n

a

l

i

n

p

u

t

S

i

g

n

a

l

i

n

p

u

t

T

o

l

i

n

e

a

m

p

l

i

f

i

e

r

T

o

l

i

n

e

a

m

p

l

i

f

i

e

r

T

o

p

o

w

e

r

a

m

p

l

i

f

i

e

r

T

o

p

o

w

e

r

a

m

p

l

i

f

i

e

r

F

o

r

s

p

e

c

t

r

u

m

a

n

a

l

y

z

e

r

d

i

s

p

l

a

y

o

r

r

e

c

o

r

d

i

n

g

t

h

r

o

u

g

h

g

r

a

p

h

i

c

e

q

u

a

l

i

z

e

r

F

o

r

s

p

e

c

t

r

u

m

a

n

a

l

y

z

e

r

d

i

s

p

l

a

y

o

r

r

e

c

o

r

d

i

n

g

t

h

r

o

u

g

h

g

r

a

p

h

i

c

e

q

u

a

l

i

z

e

r

C

X

A

1

3

5

2

A

S

D

V

C

C

D

V

C

C

G

N

D

G

N

D

G

N

D

G

N

D

G

N

D

C

8

2

2

0

µ

C

1

0

4

.

7

µ

C

1

2

4

.

7

µ

C

1

3

2

2

0

µ

C

1

5

2

.

2

µ

C

1

7

2

.

2

µ

C

1

9

2

.

2

µ

C

2

0

4

.

7

µ

R

9

5

.

1

k

40

0H

z

10

0H

z

BA

L

VO

L

1k

Hz

4k

Hz

10

kH

z

DV

CC

DC

1

IN

1

GN

D

L O

UT

1

F O

UT

1

OU

T1

IS

ET

DC

2

IN

2

V

CC

L O

UT

2

F O

UT

2

OU

T2

VG

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility fo

r

any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same

.

--8--

CXA1352AS

Description of Operation

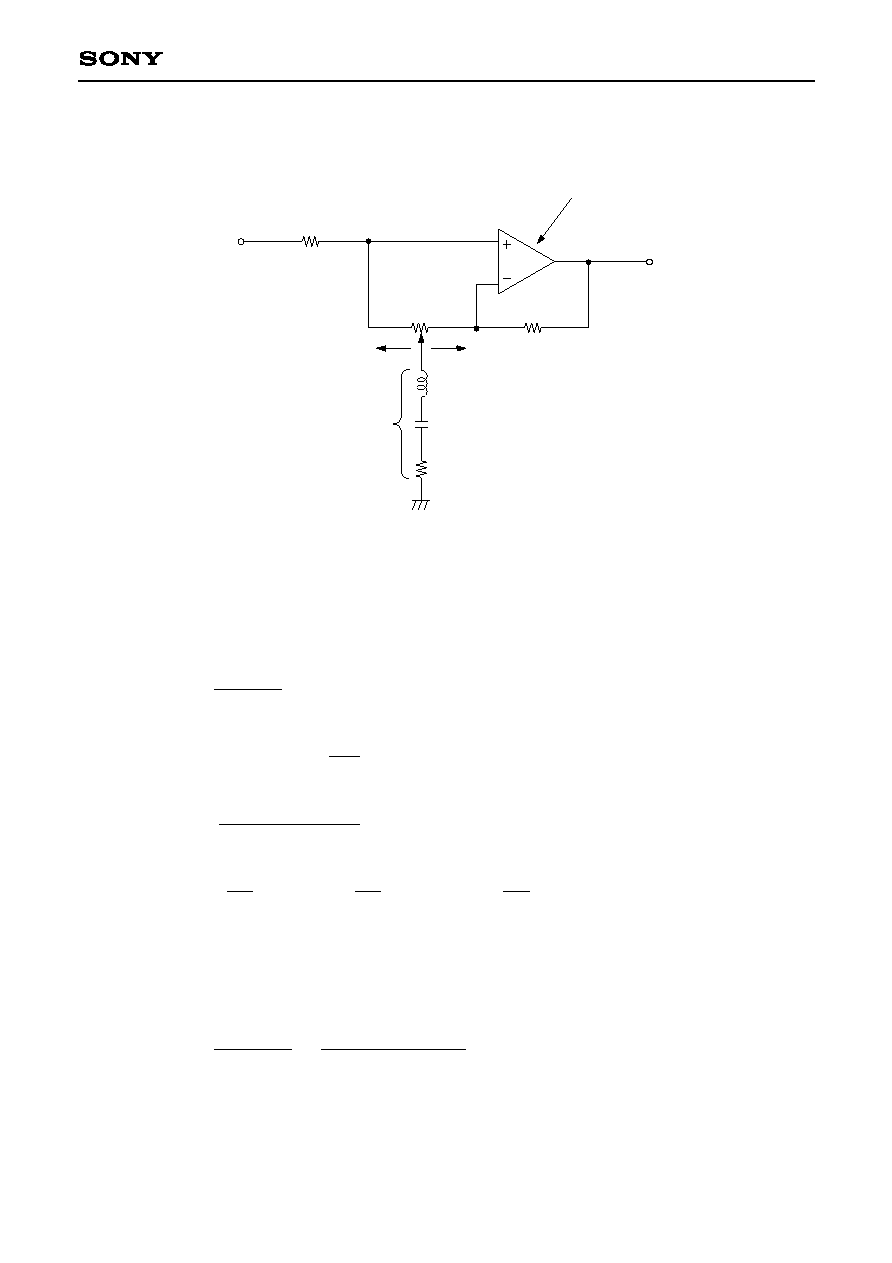

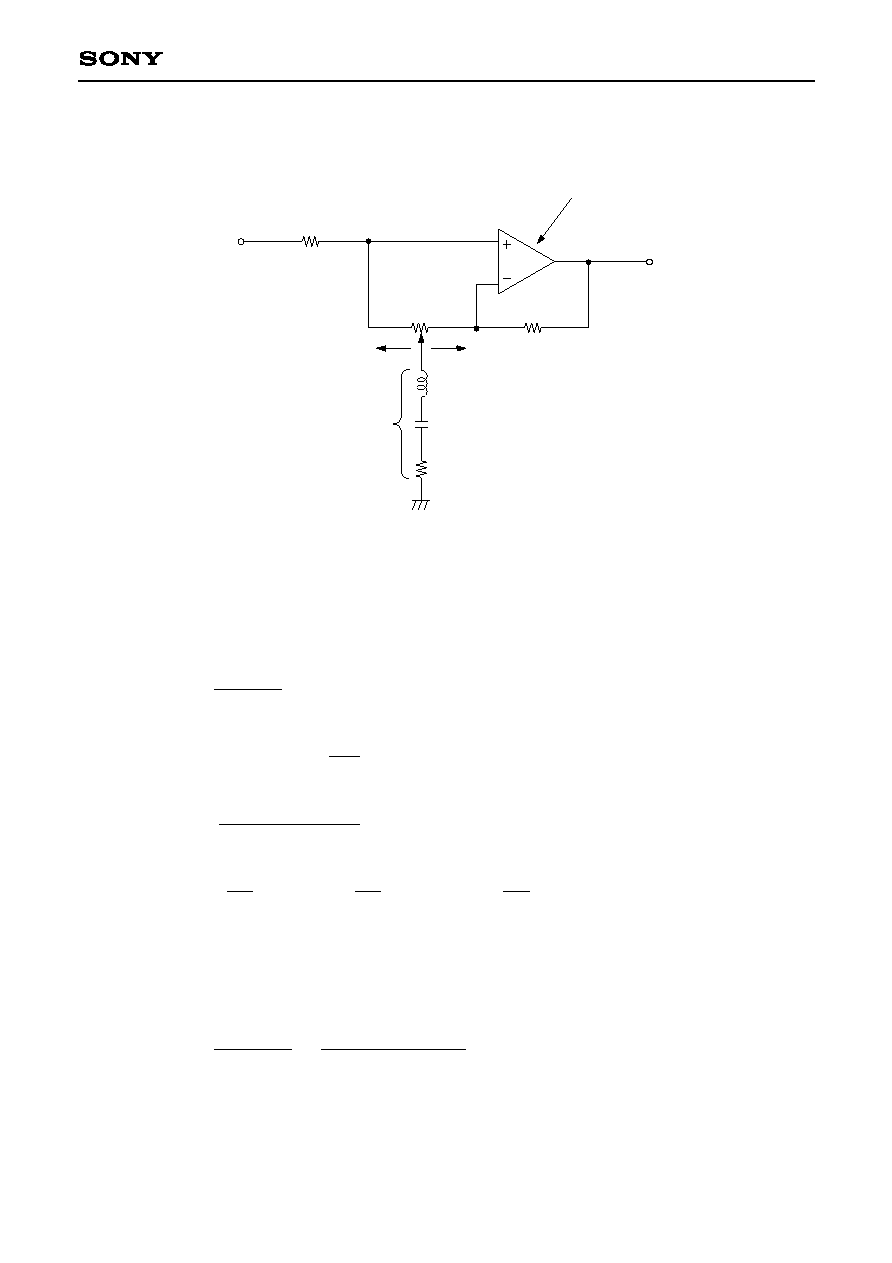

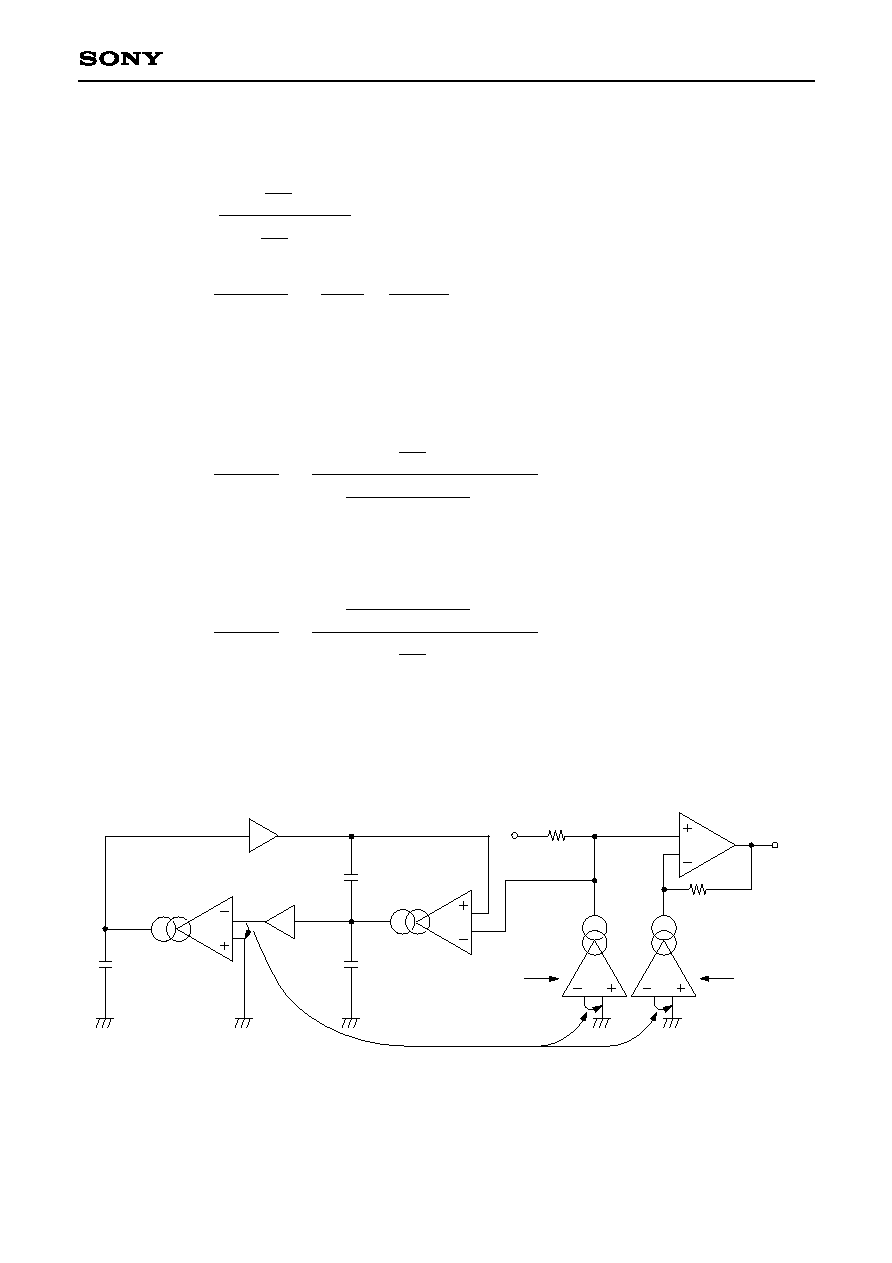

1. Graphic equalizer

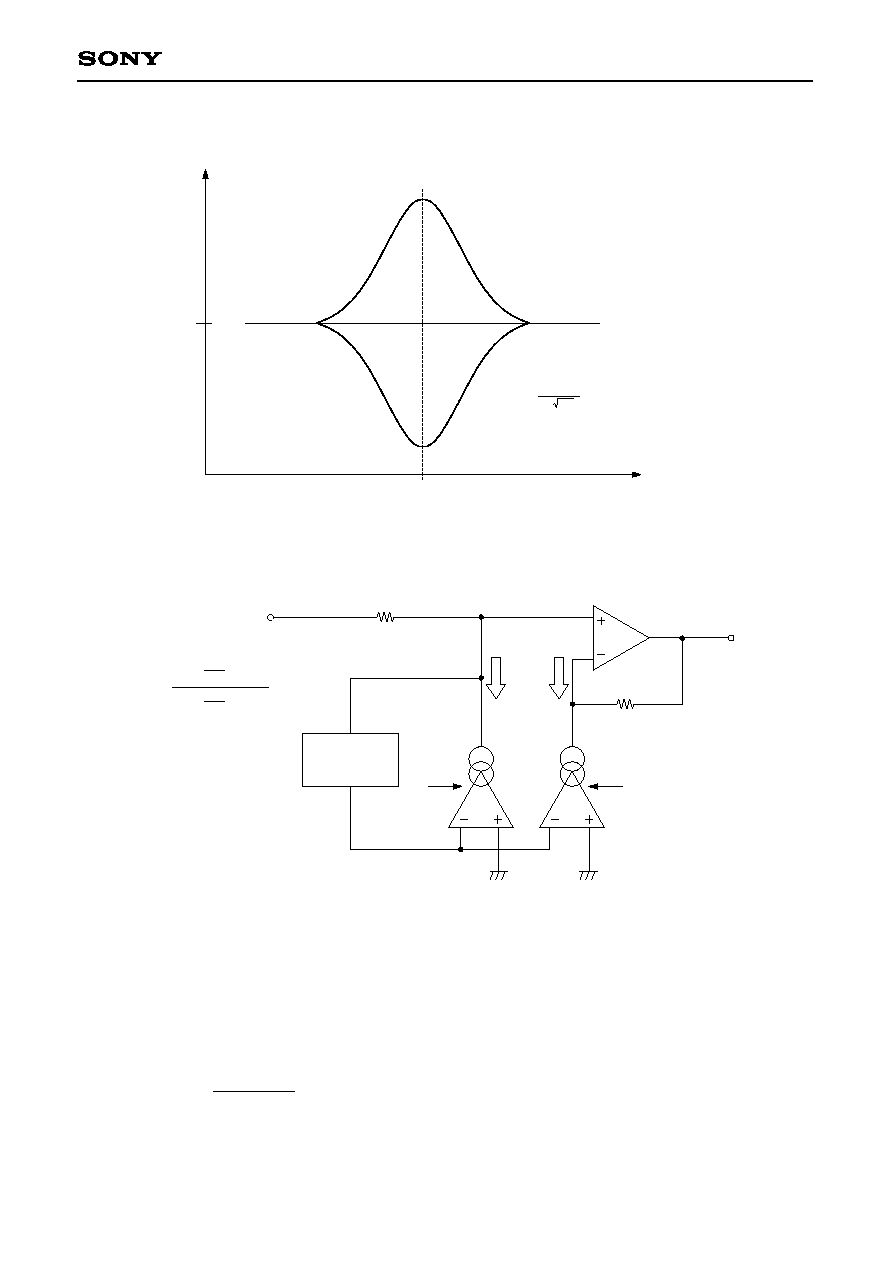

∑ Conventional system

Fig. 1.

Fig. 1. indicates the conventional graphic equalizer system. This circuit performs boost and cut near "f

O

"

controlled by the variable volume R

V

. ("f

O

" is resonance frequency determined by Z (s) (formed LCR).) The

operation can be seen as follows : When the LCR circuit goes to the far left of R

V

, a state of graphic

equalizer becomes maximum cut. At that time, assuming transmittance as T (s), we have

T (s) =

Z (s)

Z (s)+ R

O

Here as

Z (s) = sL+R+

1

sC

Then

T (s) =

LCs

2

+RCs+1

LCs

2

+ (R+Ro) Cs+1

Defining fo as f

O

=

o

,

o as

o =

1

, and Q as Q =

oL

,

2

LC

R

we can obtain the frequency

characteristics at cut.

Also, when LCR circuit goes to the far right of R

V

, a state of graphic equalizer becomes maximum boost.

At that time transmittance is :

T (s) =

Z (s) +R

O

=

LCs

2

+ (R+Ro) Cs+1

Z (s)

LCs

2

+RCs+1

Defining fo,

o and Q as for cut, we can obtain the frequency characteristics at boost.

V

I

R

1

R

V

R

2

R

0

=R

1

=R

2

V

O

OPERATIONAL AMPLIFIER

BOOST

CUT

L

C

Z (s)

R

--9--

CXA1352AS

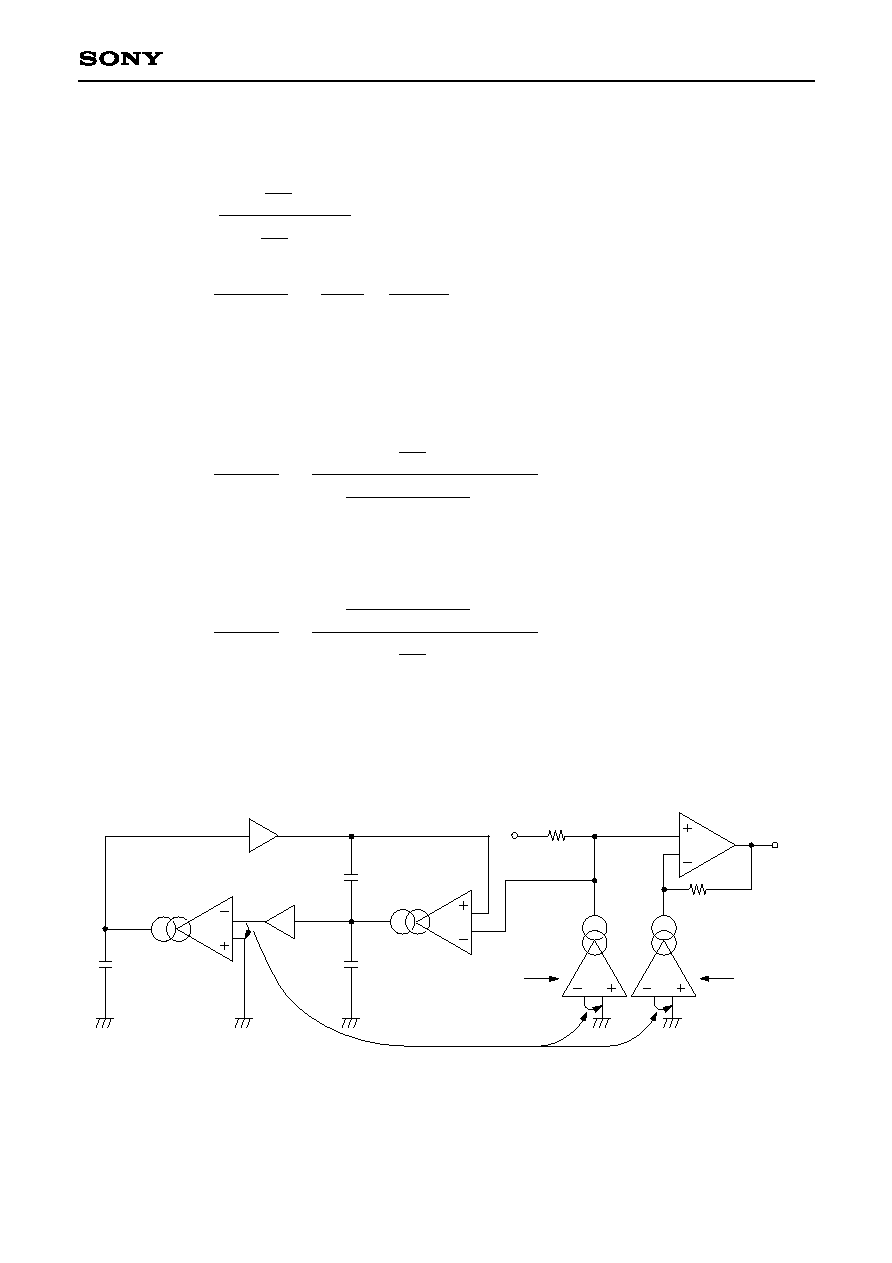

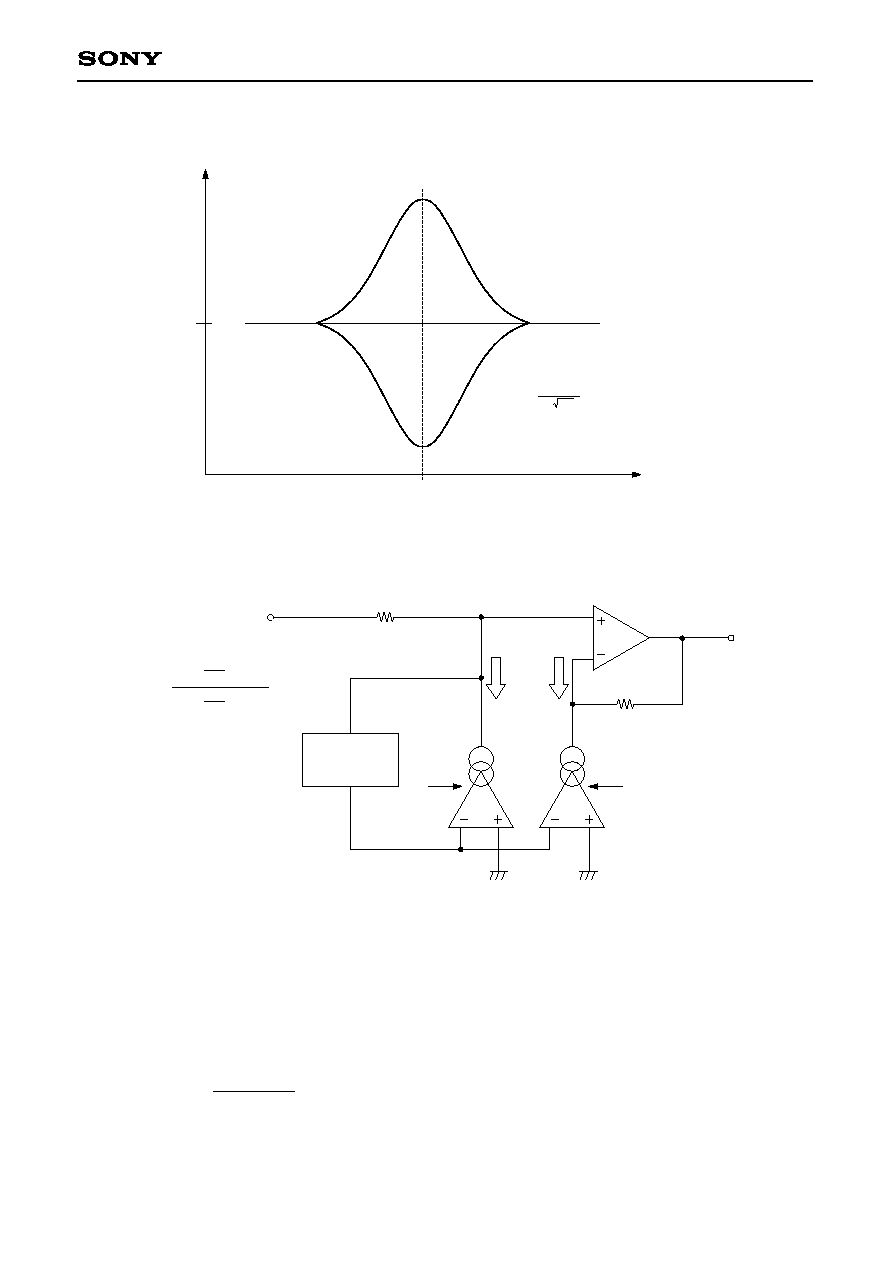

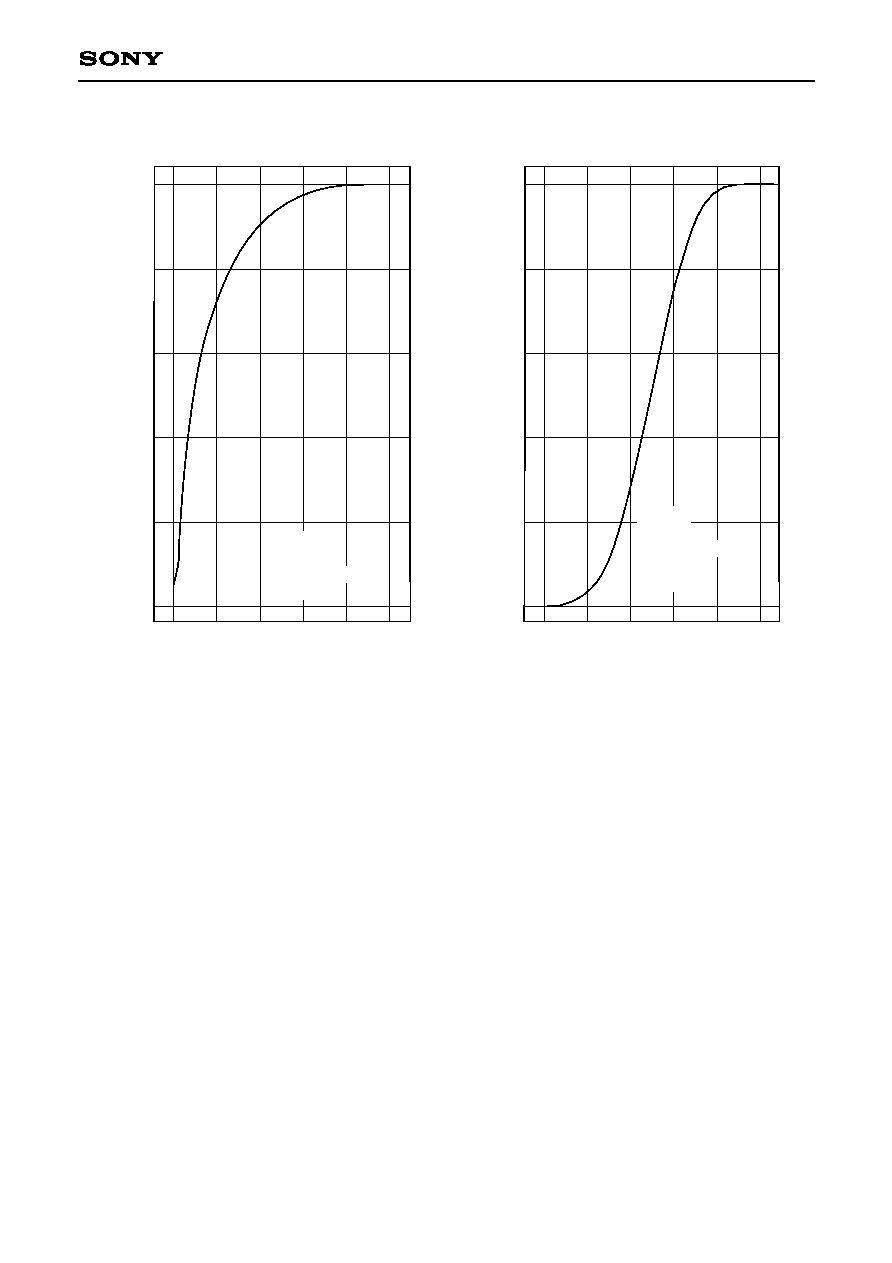

Fig. 2. Indicates frequency characteristics at boost and cut.

Fig. 2.

∑ CXA1352AS system

Fig. 3.

The structure of the graphic equalizer used in this IC is shown on Fig. 3. This circuit performs boost and

cut controlled by 2 transconductance amplifiers that can vary the conversion coefficient through control

currents Ib, and Ic around

o. ("

o" is central frequency determined by Band Pass Filter.) Considering

output impedance Z (s) of Gm1, Gm2 we have

Z (s) =

1

H(s) ∑ Gm1

Response (dB)

0dB

Boost

FIat

Cut

f

O

=

2

LC

1

Frequency (Hz)

f

O

V

I

H(s)=

s

2

+

s+

o

2

Q

o

s

Q

o

H(s)

Ic

Ib

Z(s)

Z(s)

R

R

Gm1

Gm2

V

O

Operational amplifier

--10--

CXA1352AS

Here, using

o and Q we can express BPF transmittance H (s) as

Z (s) =

Q

s+

1

+

o ∑ Q

o ∑ Gm1

Gm1

Gm1 ∑ s

This formula shows that this system and the aforementioned LCR circuit have equivalent impedance

characteristics on Z (s).

Then, regarding Gm as the maximum value of Gm1 and Gm2, the operation can be observed as follows.

Maximum cut occurs when Gm1=Gm and Gm2=0. At that time we have transmittance T (s) as

T (s) =

Z (s)

=

Z (s) +R

This is equal to the frequency characteristics of the conventional graphic equalizer at cut.

Also, maximum boost occurs when Gm1=0 and Gm2=Gm. At that time we have transmittance T (s) as

T (s) =

Z (s) +R

=

Z (s)

This is equal to the frequency characteristics of the conventional graphic equalizer at boost.

We can then deduce that, as far as the operation is concerned the graphic equalizer on this IC and the

conventional graphic equalizer are equal, even when the system differs. The merit in using this IC's system

rests with the fact that monolithic filter technology realizes a graphic equalizer without external parts.

The structure of the actual graphic equalizer, including BPF, is shown on Fig. 4.

Fig. 4

H (s) =

o

∑ s

Q

s

2

+

o

s +

o

2

Q

s

2

+

o

∑ s +

o

2

Q

s

2

+

(1+R ∑ Gm) ∑

o

2

∑ s+

o

2

Q

s

2

+

o

∑ s +

o

2

Q

s

2

+

(1+R ∑ Gm) ∑

o

2

∑ s+

o

2

Q

R2

30k

SUM

V

O

Gm4

Gm3

Gm1

I CUT

I BOOST

GND

GND

GND

GND

GND

C2

C1

C3

Gm2

VI

V

I

1

1

R1

30k

--11--

CXA1352AS

2. Control through microcomputer possible

Volume, balance and the 100 Hz, 400 Hz, 1 kHz, 4 kHz, 10 kHz boost, cut control respectively are all

executed through DC voltage.

Also, the control voltage range is determined through DV

CC

(control power supply, independent from V

CC

)

and is from 0 V to DV

CC

. Accordingly, the control range can be varied at will, by changing DV

CC

voltage.

By setting DV

CC

5 V, control through the microcomputer becomes possible.

Setting to DV

CC

=V

CC

enables usage with single power supply.

3. Pseudo loudness

A loudness function interlocking with volume (VOL) is featured.

With this IC, to provide a loudness effect, the 100 Hz and 10 kHz graphic equalizer part does not use a

BPF but is composed of a low pass filter (LPF) and a high pass filter (HPF) respectively.

The operation is explained as follows. As VOL drops below the center, the 100 Hz and 10 kHz graphic

equalizer part Ib (See Fig. 3.) gradually increases even if the graphic equalizer control pin (100 Hz and 10

kHz) is flat, boost applies and as a result loudness effect is obtained.

--12--

CXA1352AS

Notes on Operation

1. Power supply

DV

CC

can be used independently from V

CC

but supply voltage should be

V

CC

DV

CC

, without fall.

2. Pseudo loudness

As mentioned in the paragraph on Description of Operation, as it is interlocked with VOL, loudness can not

be put OFF.

3. Output pin

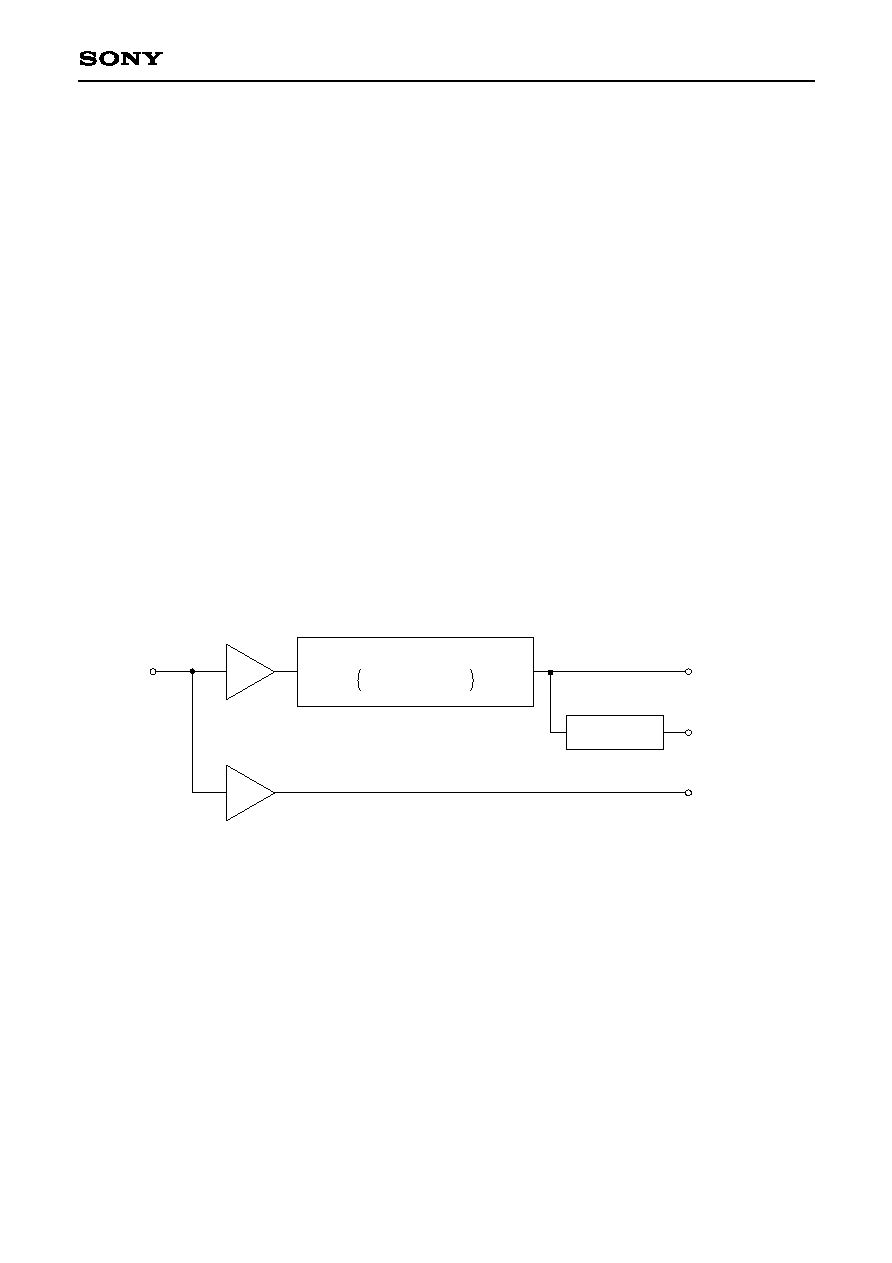

This IC features 2 channels for each of OUT pin, LINE OUT pin and FIX OUT pin.

Usage of the respective output pins is indicated as follows.

∑ OUT pin

Normally used as the graphic equalizer output.

∑ LINE OUT pin

A sound from a source that has not passed through the graphic equalizer is only amplified and output

from this pin.

∑ FIX OUT pin

This pin is useful for REC or spectrum analyzer display after the sound formation at the graphic

equalizer.

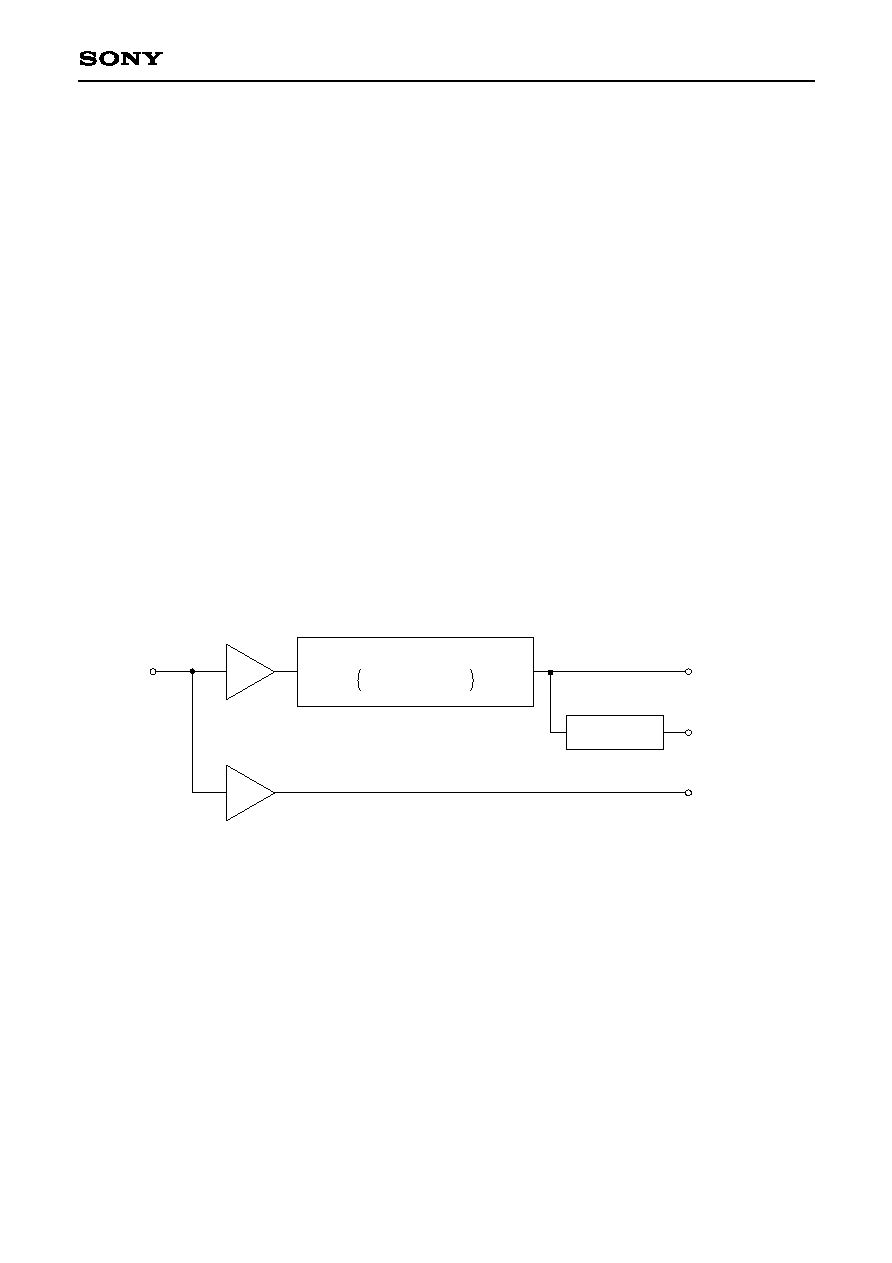

The relation between the input and the respective outputs is shown on Fig. 5.

Fig. 5.

4. Reference resistor

To check the central frequency deviation of the graphic equalizer, the control current that determines the

filter time constant is determined by means of an external, not an internal, resistor.

This is the 160 k

external resistor connected to ISET pin (Pin 11). Accordingly, for the resistor to be

connected to ISET pin, it is recommended to use a resistor with excellent dispersion and temperature

characteristics.

Also, by varying the value of the resistor connected to ISET pin, the frequency characteristics of the

graphic equalizer can be shifted. By reducing the resistor value the shift moves to the high band and by

increasing the value the shift moves to the low band.

However, 5 elements cannot be shifted independently.

F OUT

≠20dBm

L OUT

≠5dBm

OUT

≠20dBm

(VARIABLE)

VOLUME

IN AMP

≠34dBm

IN

14dB

LINE AMP

29dB

GRAPHIC EQUALIZER

GEBPF+GEHPF+

GELPF+SUM AMP

--13--

CXA1352AS

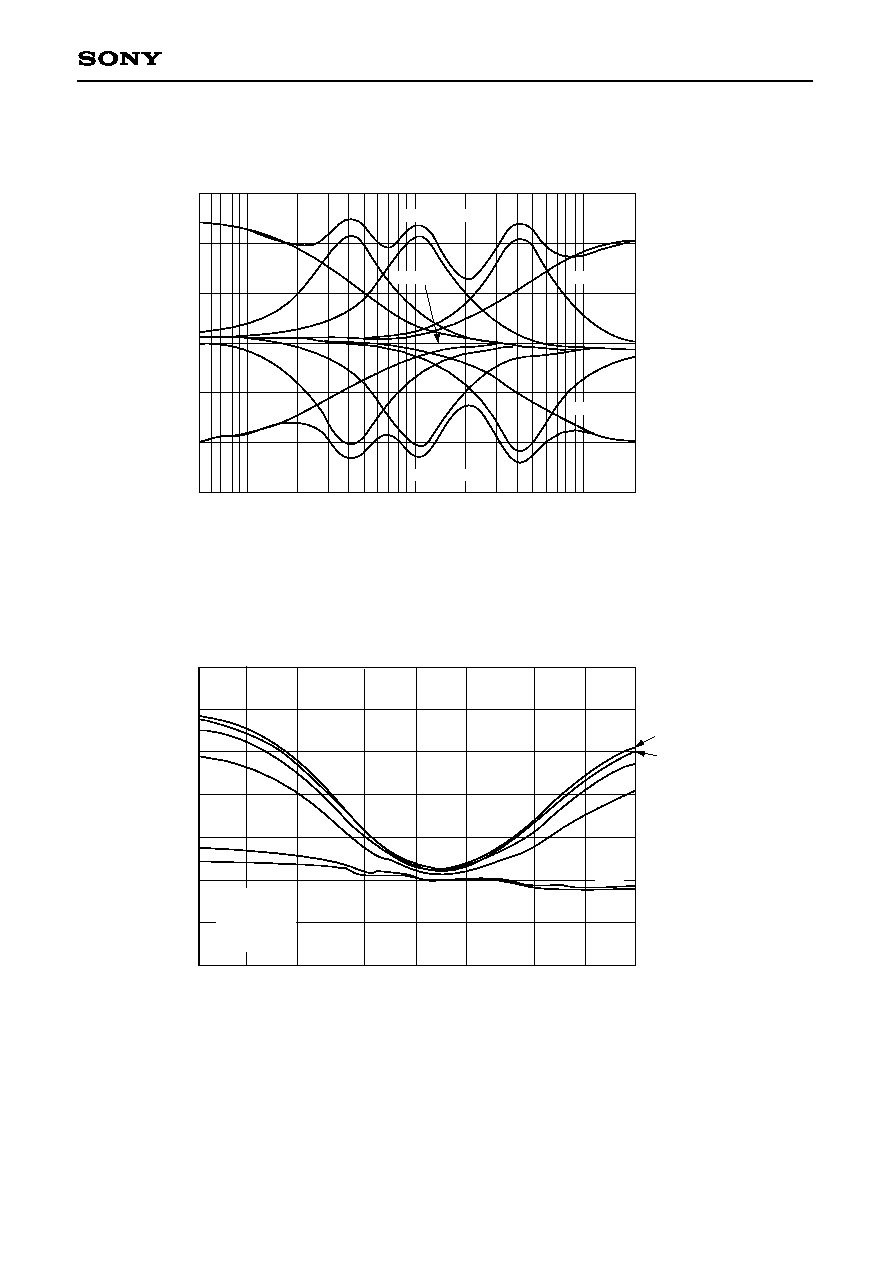

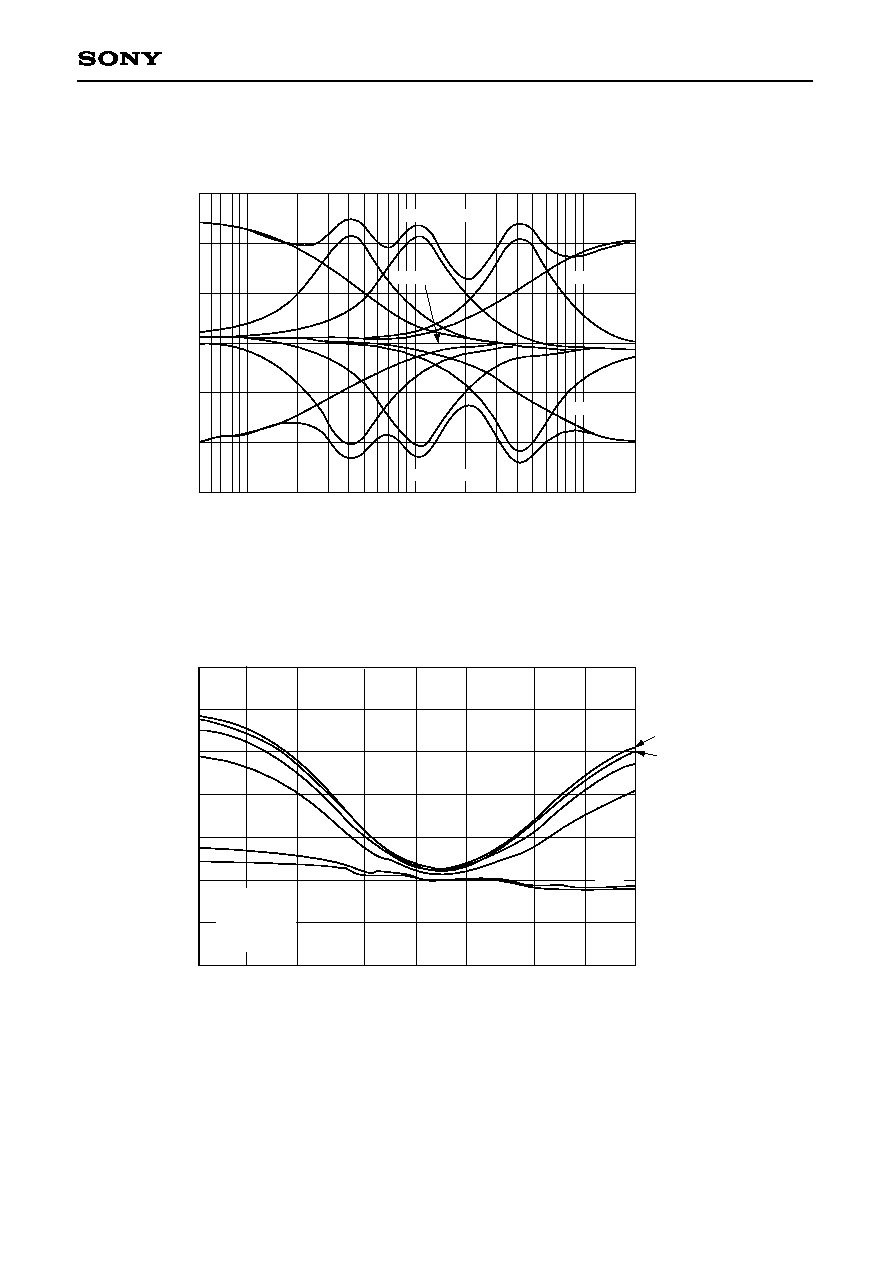

Example of Representative Characteristics

15

10

≠5

≠10

≠15

5

0

50

100

200

500

1k

2k

5k

10k

20k

Frequency characterlstlcs

ALL BOOST

ALL FLAT

ALL CUT

BOOST

CUT

R

E

S

P

O

N

S

E

(

d

B

)

V

CC

=8V

DV

CC

=5V

0dB=≠20dBm, 1kHz

VOL : MAX

FREQUENCY(Hz)

≠4

8

4

0

50

100

200

500

1k

2k

5k

10k

20k

Loudness characteristics

2.5V

B

O

O

S

T

(

d

B

)

FREQUENCY(Hz)

V

CC

=8V

DV

CC

=5V

0dB=at 1kHz

ALL FLAT

VOL=0.0V

1.0V

1.5V

2.0V

5.0V

--14--

CXA1352AS

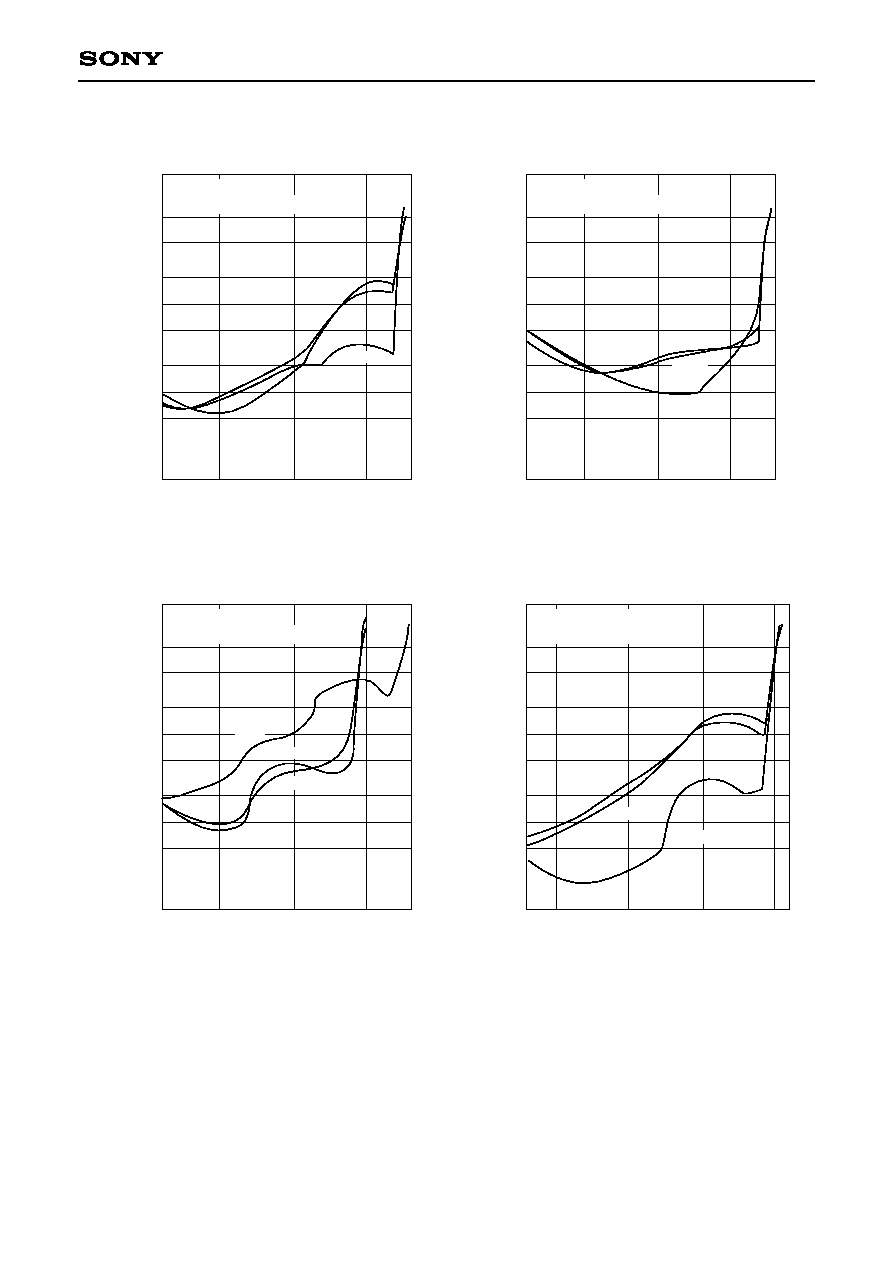

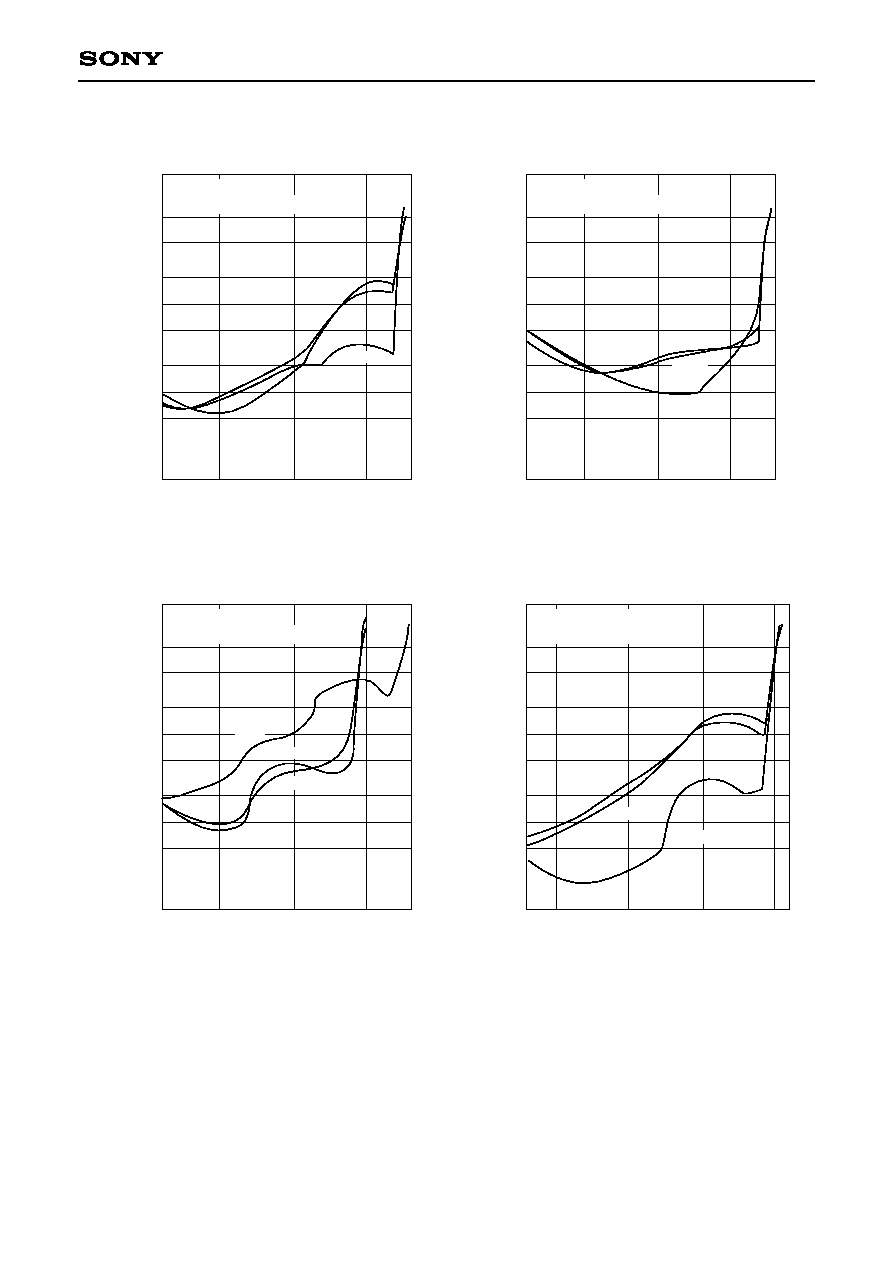

THD-OUT characteristics (ALL FLAT)

V

CC

=8V, DV

CC

=5V

0dB=≠20dBm, VOL : MAX

10.0

5.0

2.0

1.0

0.5

0.2

0.1

0.05

T

H

D

+

N

(

%

)

0

10

20

100Hz

10kHz

1kHz

OUT pin output level (dB)

THD-OUT characteristics (ALL BOOST)

V

CC

=8V, DV

CC

=5V

0dB=≠20dBm, VOL : MAX

10.0

5.0

2.0

1.0

0.5

0.2

0.1

0.05

T

H

D

+

N

(

%

)

0

10

20

100Hz

10kHz

1kHz

OUT pin output level (dB)

THD-OUT characteristics (ALL CUT)

V

CC

=8V, DV

CC

=5V

0dB=≠20dBm, VOL : MAX

10.0

5.0

2.0

1.0

0.5

0.2

0.1

0.05

T

H

D

+

N

(

%

)

0

10

20

100Hz

10kHz

1kHz

OUT pin output level (dB)

THD-F OUT characteristics (ALL FLAT)

V

CC

=8V, DV

CC

=5V

0dB=≠20dBm, VOL : MAX

10.0

5.0

2.0

1.0

0.5

0.2

0.1

0.05

T

H

D

+

N

(

%

)

0

10

20

30

100Hz

10kHz

1kHz

FIX OUT pin output level (dB)

--15--

CXA1352AS

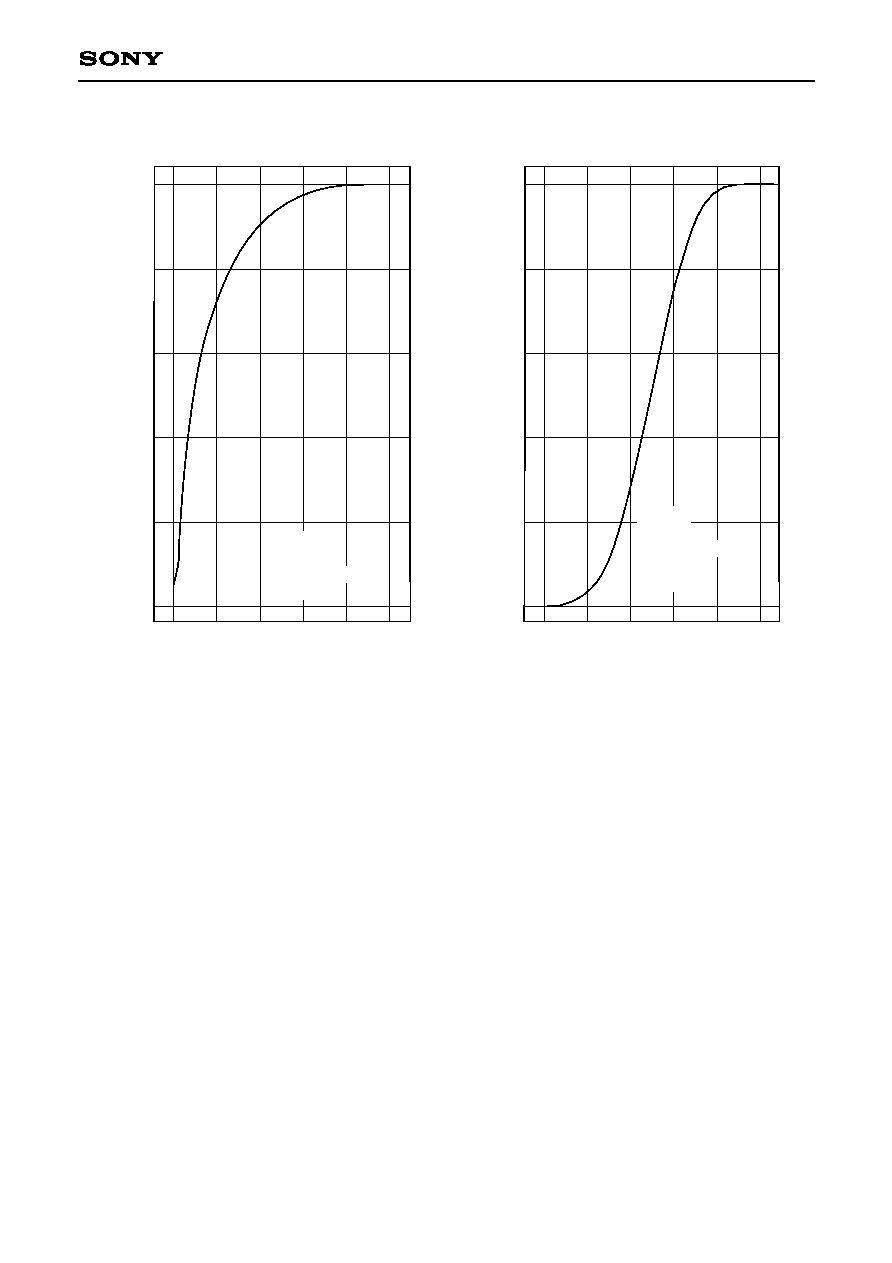

THD-F OUT characteristics (ALL BOOST)

V

CC

=8V, DV

CC

=5V

0dB=≠20dBm, VOL : MAX

10.0

5.0

2.0

1.0

0.5

0.2

0.1

0.05

T

H

D

+

N

(

%

)

0

10

20

30

100Hz

10kHz

1kHz

FIX OUT pin output level (dB)

THD-F OUT characteristics (ALL CUT)

V

CC

=8V, DV

CC

=5V

0dB=≠20dBm, VOL : MAX

10.0

5.0

2.0

1.0

0.5

0.2

0.1

0.05

T

H

D

+

N

(

%

)

0

10

20

100Hz

10kHz

1kHz

FIX OUT pin output level (dB)

THD-L OUT characteristics

V

CC

=8V, DV

CC

=5V

0dB=≠6dBm, VOL : MAX

10.0

5.0

2.0

1.0

0.5

0.2

0.1

0.05

T

H

D

+

N

(

%

)

0

10

≠10

10

0H

z

10

kH

z

1kHz

LINE OUT pin output level (dB)

Output voltage vs. Control voltage (VOL)

0

≠20

≠40

≠60

≠80

O

U

T

p

i

n

o

u

t

p

u

t

l

e

v

e

l

(

d

B

m

)

0.1

0.2

0.5

1

2

5

Control voltage (V)

V

CC

=8V

DV

CC

=5V

V

IN

=≠14dBm,1kHz

ALL FLAT

--16--

CXA1352AS

Output voltage vs. Control voltage (VOL)

0

≠20

≠40

≠60

≠80

≠100

O

U

T

p

i

n

o

u

t

p

u

t

l

e

v

e

l

(

d

B

m

)

0

1.0

2.0

3.0

4.0

5.0

Control voltage (V)

V

CC

=8V

DV

CC

=5V

V

IN

=≠14dBm, 1kHz

ALL FLAT

Output voltage vs. Control voltage (VOL)

100

80

60

40

20

0

O

U

T

p

i

n

o

u

t

p

u

t

l

e

v

e

l

(

%

)

0

1.0

2.0

3.0

4.0

5.0

Control voltage (V)

V

CC

=8V

DV

CC

=5V

V

IN

=≠14dBm, 1kHz

100%=0dBm

ALLFLAT

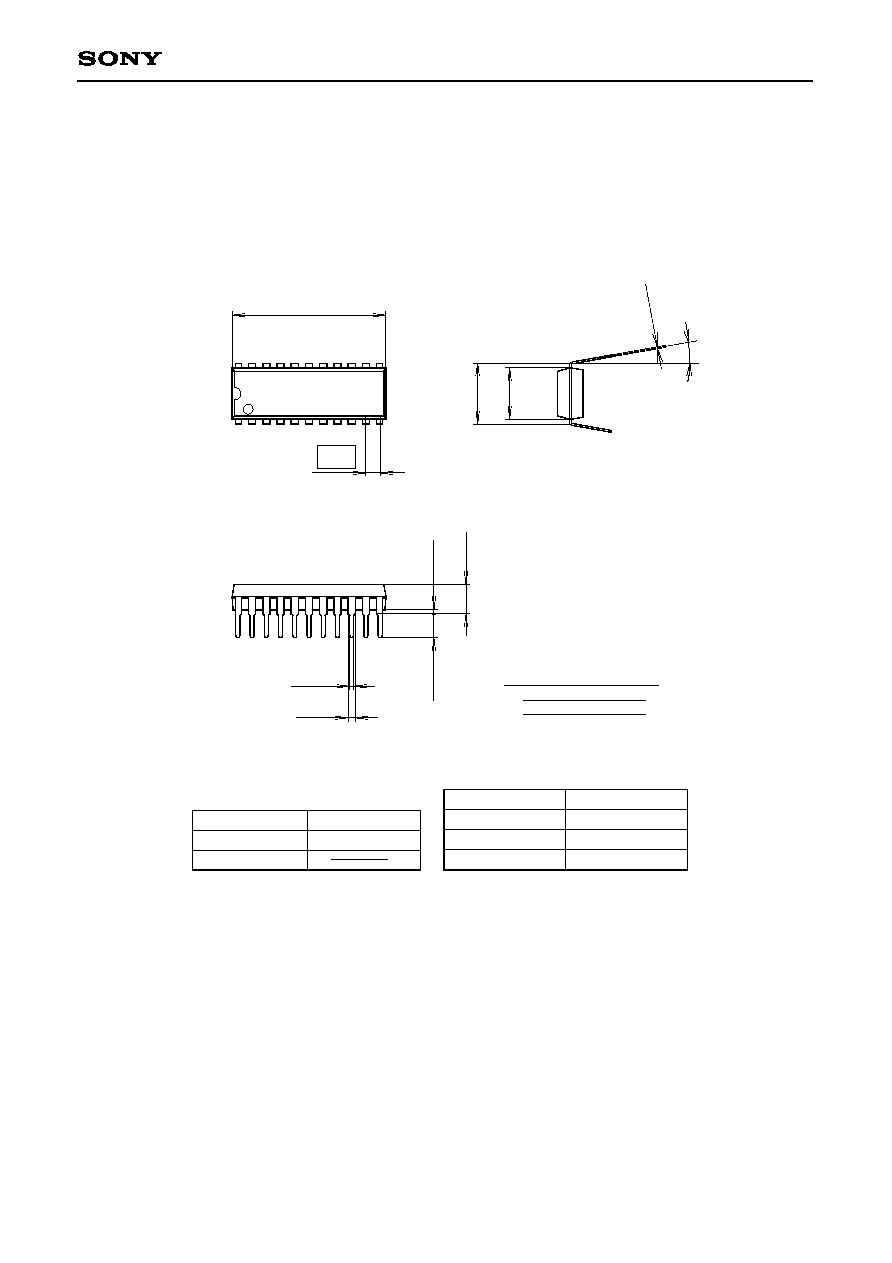

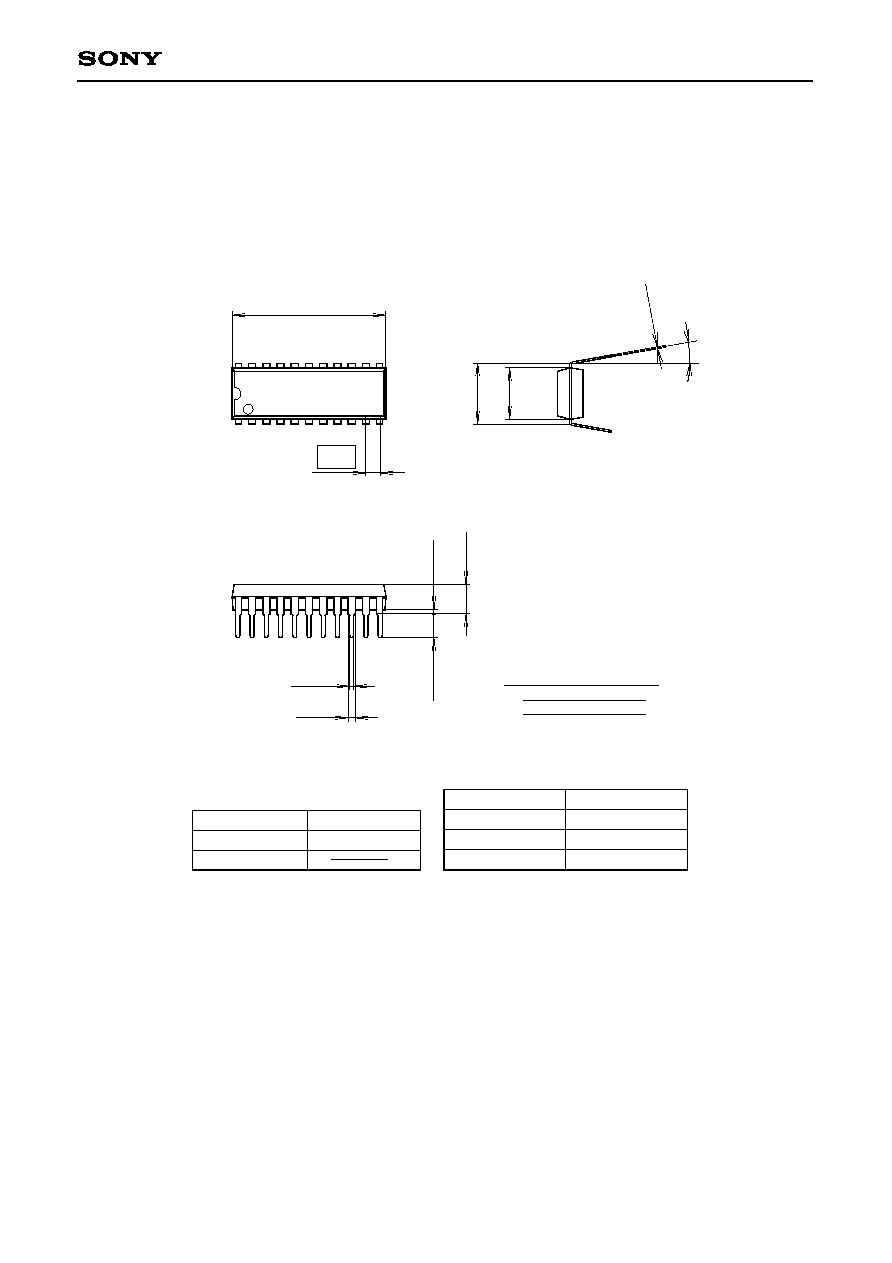

SONY CODE

EIAJ CODE

JEDEC CODE

PACKAGE STRUCTURE

MOLDING COMPOUND

LEAD TREATMENT

LEAD MATERIAL

PACKAGE MASS

EPOXY RESIN

SOLDER PLATING

COPPER ALLOY

22PIN SDIP (PLASTIC)

SDIP-22P-01

SDIP022-P-0300

0.95g

1.778

11

12

1

22

19.2 ≠ 0.1

+ 0.4

7

.

6

2

6

.

4

≠

0

.

1

+

0

.

3

0

.2

5

≠

0

.0

5

+

0

.1

0∞ to 15∞

0.5 ± 0.1

0.9 ≠ 0.1

+ 0.15

3

.

2

5

≠

0

.

2

+

0

.

1

5

0

.

5

1

M

I

N

3

.

9

≠

0

.

1

+

0

.

4

1.All mat surface type.

Two kinds of package surface:

2.All mirror surface type.

Package Outline Unit : mm

CXA1352AS

--17--