| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: CXA1852N | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

--1--

E93517A5Y-TE

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

Absolute Maximum Ratings (Ta=25 ∞C)

∑ Supply voltage

V

CC

6

V

∑ Operating temperature Topr

≠20 to +70

∞C

∑ Storage temperature

Tstg

≠65 to +150

∞C

∑ Allowable power dissipation

P

D

530

mW

When mounted on a 50

◊

50

◊

1.6 mm copper-

foiled glass epoxy board

Recommended Operating Conditions

∑ Supply voltage

V

CC

2.7±5.0

V

Description

The CXA1852N is an IC package that combines a

/2 phase shifter with a quadrature modulator.

This is suitable for 900 MHz digital cordless

telephone (CT2) and digital cellular.

Features

∑ Quadrature modulator IC has a built-in

/2 phase

shifter.

∑ Local frequency = 300.1 MHz (max.); I&Q = 36

kHz (max.)

∑ Small phase error

∑ Operating voltage range: 2.7 to 5 V

∑ Power saving function

∑ 20-pin SSOP package used for set size reduction

Applications

∑ CT2 digital cordless telephone

∑ Digital cellular

Structure

Bipolar silicon monolithic IC

Quadrature Modulator for 900 MHz-Band Mobile Communications

20 pin SSOP (Plastic)

Block Diagram and Pin Configuration

LPF

MIXER

GN

D

GN

D

GN

D

L

O

IN

LO

b

Q

b

BI

AS

Q

BI

AS

Qb

Q

IF

OU

T

GN

D

GN

D

GN

D

NC

I

b

BI

AS

I

BI

AS

Ib

I

P/

S

V

CC

AM

P

F/F

LPF

REGULATOR

ADDER

-AMP

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

20

19

CXA1852N

For the availability of this product, please contact the sales office.

--2--

CXA1852N

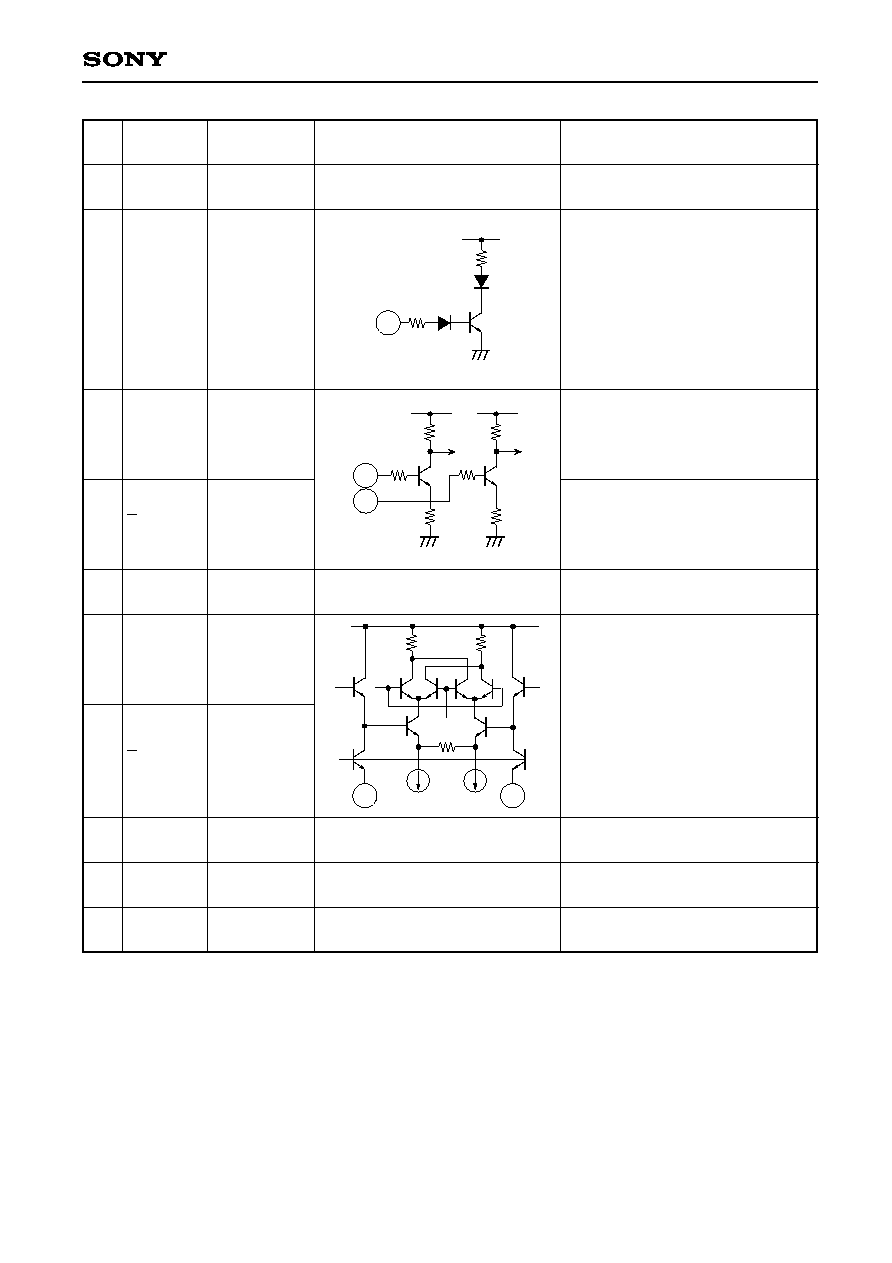

Pin Description

Pin

No.

1

2

3

4

5

6

7

8

9

10

Symbol

LOCAL IN

LOCAL IN

GND

Q-BIAS

Q-BIAS

GND

Q-INPU

Q-INPUT

GND

IF OUTPUT

Typical

pin voltage (V)

0

2.0

0

0.175

0.175

0

1.85 V to

0.85 V

1.85 V to

0.85 V

0

1.4

Equivalent circuit

Description

Local input pin. The internal resistor

provides 50

matching.

Bias pin for the local input amplifier.

Ground this pin via a capacitor.

Local leak level adjustment pins.

Normally ground these pins via 1 k

resistors.

Q signal input pin. The input

impedance is 500 k

or more.

(Only DC signals can be normally

input at the V

CC

/2 DC Bias.)

Q signal input pin. The input

impedance is 500k

or more.

(Signals of up to 1 Vp-p can be input

at the V

CC

/2 DC Bias.)

IF output pin. (An output impedance

of 50

is provided by the emitter

follower.)

1

2

4

5

7

8

10

--3--

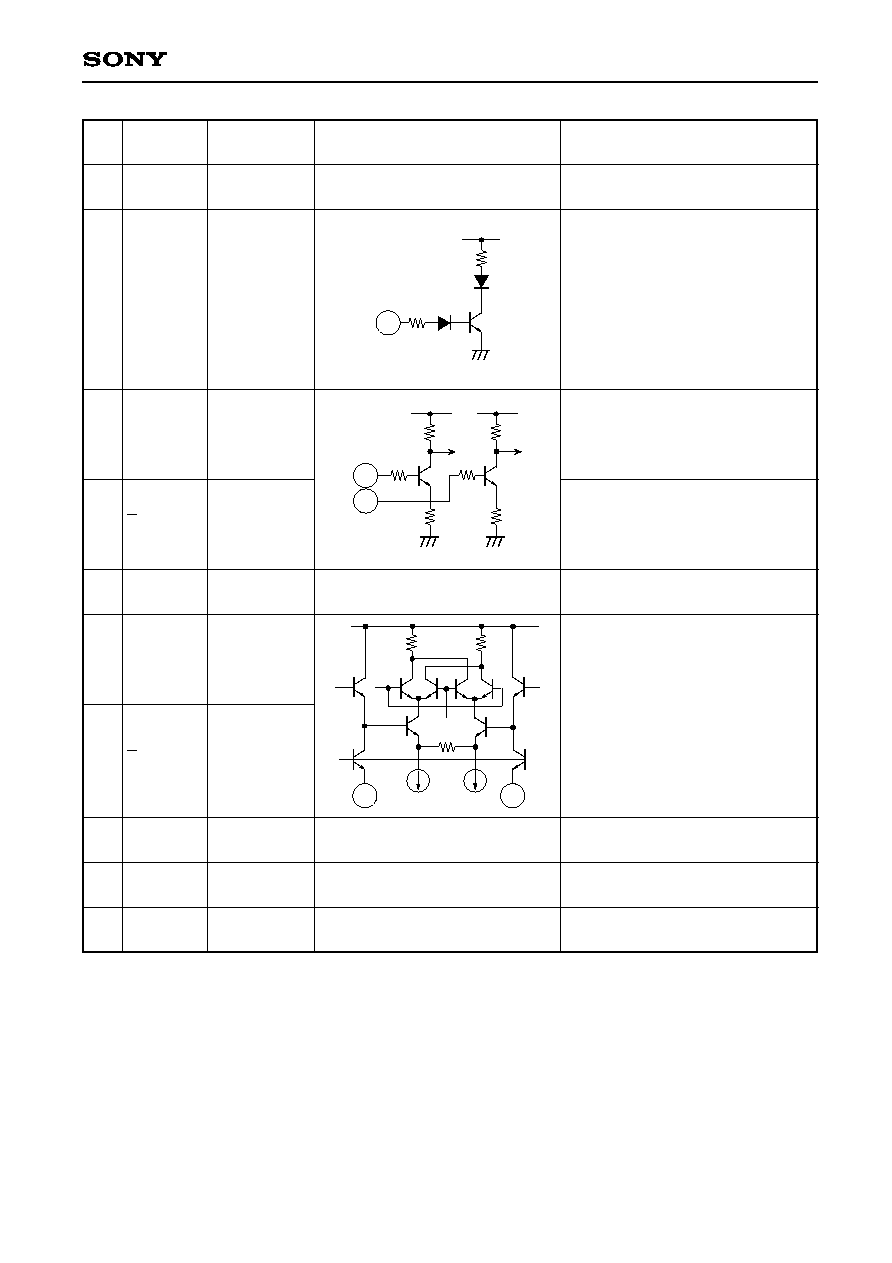

CXA1852N

Pin

No.

11

12

13

14

15

16

17

18

19

20

Symbol

V

CC

POWER

SAVE

I-INPUT

I-INPUT

GND

I-BIAS

I-BIAS

GND

N.C

GND

Typical

pin voltage (V)

5.5 to 2.7

0 to 5.5

0.85

to

1.85

0.85

to

1.85

0

0.175

0.175

0

--

0

Equivalent circuit

Description

Power supply pin.

Power saving control pin.

OFF when V

P/S

1.0 V; ON when

V

P/S

1.8 V

I signal input pin. The input

impedance is 500 k

or more.

(Signals of up to 1 Vp-p can be input

at the V

CC

/2 DC Bias.)

I signal input pin. The input

impedance is 500 k

or more

(Only DC signals can be normally

input at the V

CC

/2 DC Bias.)

Local leak level adjustment pin.

Normally ground this pin via a 1 k

resistor.

12

13

14

16

17

--4--

CXA1852N

Electrical Characteristics

(Ta=25 ∞C, V

CC

=2.7 V, Z

L

=Z

S

=50

)

Item

Current consumption

Standby current consumption

IF output power

Lo carrier leak

Lo leak level

Image rejection (side-band leak)

I/Q input impedance

Power saving response time

Rise

Fall

Power saving control voltage

Lo input level

Symbol

I

CC

I

CC

(PS)

Pout

ISO (Lo)

P

LO

ImR

Z

I/Q

T

P/S

(RISE)

T

P/S

(DOWN)

V

P/S

(ON)

V

P/S

(OFF)

Loin

Symbol

IM3

I/Q

Conditions

For no signal input

PS

50

load, f=f

LO

/2+f

I/Q

f

I/Q

=36 kHz, 1 Vp-p, fout=f

LO

/2

I/Q=V

CC

/2, fout=f

LO

/2

fout=f

LO

/2-f

I/Q

Conditions

fout=f

LO/2

-3fI/

Q

f

Min. Typ. Max. Unit

10

15.0

22

mA

330

480

µA

≠15

≠11

≠7.0 dBm

26

35.0

dBc

≠49.0 ≠37

dBm

28.5 37.5

dBc

500

k

1.0

5.0

µs

1.0

3.0

µs

1.8

5.5

V

1.0

V

≠17

≠7

dBm

Typ.

Unit

37.3

dBc

1.1

X:1

1.2

X:1

Design Reference Values

(Ta=25 ∞C, V

CC

=2.7 V, Z

L

=Z

S

=50

)

Item

I/Q third-order intermodulation

distortion

Lo input VSWR

IF output VSWR

f

LO

=300.1 MHz Pin=≠10 dBm

f

I/Q

=36 kHz 1 Vp-p DC=V

CC

/2

--5--

CXA1852N

Electrical Characteristics Test Circuit

GN

D

GN

D

GN

D

LPF

MIXER

GN

D

GN

D

GN

D

LO I

N

LO b

Qb BI

AS

Q BI

AS

Qb

Q

I

F

OU

T

NC

I

b

BI

AS

I

BI

AS

Ib

I

P/

S

V

CC

AM

P

F/F

LPF

REGULATOR

ADDER

-AMP

Q s

ignal

0.

033µ

1k

1k

50

30p

1000p

LO SG

I

s

i

gnal

0.

033µ

0.01µ

2000p

5µ

1/

2V

CC

1000p

1k

1k

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

20

19

Signal

Lo

I signal

Q signal

Frequency

300.1 MHz

36 kHz

35 kHz

Input level

≠10 dBm

1 Vp-p

1 Vp-p

Remarks

I/O phase difference = 90 ∞C

DC for measuring the local leak

V

CC

=V

P/S

2.7 to 5.5 V

V

I

=V

Ib

=V

Q

=V

Qb

0.5

◊

V

CC

--6--

CXA1852N

Block Diagram

Digital cordless telephone chip set (CXA1744R/CXA1851N/CXA1852N)

FM DE

M

O

D

◊

5

139.

35M

H

z

27.

87M

H

z

R

SSI

BI

T

ST

R

EAM

R

SSI

F

R

EE C

H

DE

T

E

CT

I

O

N

150.

05M

H

z

PL

L

1014 t

o

1018.

2M

H

z

PL

L

SW

864 t

o

868.

2M

H

z

1 t

o

10m

W

TX GC

A

RX

LN

A

F/

F

300.

1M

H

z

150.

05M

H

z

C

X

A

1852N

(QU

A

D

R

A

T

U

R

E

M

O

D

U

L

A

T

O

R

)

C

X

A

1744R

(I

F

A

M

P)

I

Q

C

X

A

1851N

(U

P/

D

O

W

N

C

O

NV

E

R

TE

R

)

10.

7M

H

z

--7--

CXA1852N

Modulation spectrum (V

CC

=2.7V, S.P.A. measurement)

f

LO

vs. Pout, P

LO

, PIm, P

I/Q

characteristics (V

CC

=2.7V)

10

50

100

f

LO

-Input frequency (MHz)

Output level (dBm)

V

CC

vs. I

CC

characteristics

5.0

V

CC

-Supply voltage (V)

I

CC

-Current consumption (mA)

40

30

20

10

0

2.0

3.0

6.0

I/Q 3rd order

P

Im

P

LO

Pout

ImR

LoL

500

f

LO

vs. Pout , P

LO

,PIm , P

I/Q

characteristics (V

CC

=5.5V)

- 20

- 80

10

50

100

f

LO

-Input frequency (MHz)

Output level (dBm)

0

- 30

- 40

- 50

- 60

- 70

- 10

500

4.0

No signal input

V

CC

vs. Pout, PIm, PI/Q characteristics

5

V

CC

-Supply voltage (V)

Output level (dBm)

0

- 10

- 20

- 30

- 40

- 50

- 60

- 70

- 80

2.7

3

3.5

4

5.5

4.5

P

I/Q

- 20

- 80

0

- 30

- 40

- 50

- 60

- 70

- 10

- 45

- 65

- 5

- 105

- 25

- 85

Recommended operating range

Pout

P

LO

P

I

m

P

I/Q

Pout

P

LO

P

I

m

P

I/Q

Ta=80∞C

Ta=25∞C

Ta=-30∞C

Pout

P

Im

P

I/Q

3rd-order distortion

P/S=V

CC

L

O

: f

LO

=300.1MHz

Pin=-10dBm

--8--

CXA1852N

- 20

- 80

- 30

10 20

Ta (∞C)

Output level (dBm)

V

P/S

vs. I

CC

characteristics

0

- 30

- 40

- 50

- 60

- 70

- 10

60

30

4

P/S pin potential (V)

I

CC

-Current consumption (mA)

10

100µ

50µ

1.6

1

2

3

5

250µ

20

- 20 - 10

0

30 40 50

70 80

P

LO

200µ

6

1.4

1.2

V

CC

=5.5V

V

CC

=2.7V

Ta vs. Pout, P

LO

, PIm, P

I/Q

characteristics (V

CC

=2.7V)

Pout

P

LO

P

Im

P

I/Q

3rd-order distortion

f

LO

=300.1MHz - 10dBm

I=Ib=Q=Qb=GND

--9--

CXA1852N

Notes on Operation

(1) Electrostatic sensitive diveces because of the high-frequency process .

(2) Earth pattern should be as wide as possible, and do not increase ground impedance to prevent from the

parasitic oscillation.

(3) Wire the GND pin as short as possible.

(4) Connect a by-pass capacitor to the V

CC

pin.

--10--

CXA1852N

SONY CODE

EIAJ CODE

JEDEC CODE

M

PACKAGE STRUCTURE

MOLDING COMPOUND

LEAD TREATMENT

LEAD MATERIAL

PACKAGE WEIGHT

EPOXY / PHENOL RESIN

SOLDER PLATING

20PIN SSOP (PLASTIC)

7.0 MAX

0.65

0.22 ≠ 0.05

+ 0.10

1.0 ±

0.1

4.4 ±

0.1

1.5 ±

0.1

1.8 MAX

0.575 MAX

0.15

0.10

0.15 ≠ 0.05

+ 0.10

A

0.1 ± 0.1

0∞ to 10∞

0.5 ±

0.2

DETAIL A

SSOP-20P-L072

SSOP020-P-0225-BN

1

10

11

20

COPPER ALLOY

0.1g

6.4 ±

0.2

Package Outline Unit : mm