| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: CXA2000 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Description

The CXA2000Q is a bipolar IC which integrates the

luminance signal processing, chroma signal

processing, RGB signal processing, and sync and

deflection signal processing functions for NTSC/PAL

system color TVs onto a single chip. This IC includes

deflection processing functions for wide-screen TVs,

and is also equipped with a SECAM decoder

interface, making it possible to construct a TV

system that supports multiple color systems.

Features

∑ I

2

C bus compatible

∑ Compatible with both PAL and NTSC systems

(also compatible with SECAM if a SECAM decoder is connected)

∑ Built-in deflection compensation circuit capable of supporting various wide modes

∑ Countdown system eliminates need for H and V oscillator frequency adjustment

∑ Automatic identification of 50/60Hz vertical frequency (forced control possible)

∑ Non-interlace display support (even/odd selectable)

∑ Automatic identification of PAL, NTSC, and SECAM color systems (forced control possible)

∑ Automatic identification of 4.43MHz/3.58MHz crystal (forced control possible)

∑ Non-adjusting Y/C block filter

∑ One CV input, one set of Y/C inputs, two sets of analog RGB inputs (one set of which can serve as both

analog and digital inputs)

∑ Built-in AKB circuit

∑ Support for forcing YS1 off

Applications

Color TVs (4:3, 16:9)

Structure

Bipolar silicon monolithic IC

Absolute Maximum Ratings (Ta = 25∞C, SGND, DGND = 0V)

∑ Supply voltage

SV

CC

1, 2, DV

CC

1, 2

≠0.3 to 12

V

∑ Operating temperature

Topr

≠20 to +65

∞C

∑ Storage temperature

Tstg

≠65 to +150

∞C

∑ Allowable power dissipation

P

D

1.7

W

(when mounted on 50mm

◊

50mm board)

∑ Voltages at each pin

≠0.3 to SV

CC

1, SV

CC

2,

DV

CC

1, DV

CC

2 + 0.3

V

Operating Conditions

Supply voltage

SV

CC

1, 2

9.0 ± 0.5

V

DV

CC

1, 2

9.0 ± 0.5

V

≠ 1 ≠

CXA2000Q

E96103-ST

Y/C/RGB/D for PAL/NTSC Color TVs

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

64 pin QFP (Plastic)

For the availability of this product, please contact the sales office.

≠ 2 ≠

CXA2000Q

Block Diagram

S

SEP

VIDEO

SW

SHARP

NESS

SUB

CONT

TRAP

KILLER

DET

ACC

DET

DL

DC

TRAN

CLP

D PIC

WIDE

Sawtooth

Gen.

AKB

BLK

CV/YC

TRAP OFF

DL

SHARP

DC

TRAN

D PIC

AGING

STATUS

VM OFF

SUB COLOR

TRAP F0

TOT

ACC

PRE/OVER

TOT

PAL

ID

PAL/

NTSC

DEM

APC

HUE

VCO

DEM

AXIS

IREF

fsc

ID

COLOR SW

fsc R-Y

fsc B-Y

V SYNC

SEP

H SYNC

SEP

1Vp-p

CVIN

YIN

CIN

SV

CC

1

SV

CC

2

SGND1

SGND2

XTAL

HUE

IREF

APCFIL

X358

X443

FSCOUT

SECAMREF

≠(R-Y) OUT

≠(B-Y) OUT

YOUT

YRET

≠(R-Y) IN

≠(B-Y) IN

YS1

R1IN

G1IN

B1IN

YS2

YM

R2IN

G2IN

B2IN

ABLFIL

CUT

OFF

GB

DRV

BRT

D-

COL

OSD

MIX

PIC

YS/YM

SW

Y/C

MIX

COLOR

& AXIS

COL

CLP

CLP

DIG

HV

COMP

ABL

EHT H, V

AKB OFF

IKIN

BOUT

GOUT

ROUT

E-WOUT

VD≠OUT

/VPROT

VD+OUT

/VPROT

SAWOSC

VAGCSH

VTIM

SCPOUT

HD OUT

DGND

DV

CC

2

DV

CC

1

ABLIN/

VCOMP

RSH

GSH

BSH

L2FIL

AFCPIN/

HOFF

CERA

AFCFIL

HSIN

VSIN

VSFIL

BLHOLD

DCTRAN

VM

SCL

SDA

SYNCOUT

EXT SYNC IN

GB CUT

GB DRV

BRT

PIC

WIDE

Parabola

Gen.

VLIN, SCORR

VPOSI, VOFF,

VSIZE

Count Down

525/625

INTER

-LACE

D-COL

GATE

50/60 ID

GATE

PHASE

DET.

1/32

PHASE

SHIFT

PHASE

DET

32f

H

VCO

2f

H

H POSI

AFC

C MODE

INTERLACE

V FREQ

SCP BGR/BGF

40

39

38

41

45

46

47

48

49

50

51

52

54

56

2

9

20

59

53

55

57

43

60

64

61

62

1

3

4

5

6

7

8

11

12

13

14

15

16

17

18

19

21

23

25

28

29

10

22

24

26

30

37

36

35

34

31

32

33

42

44

27

2Vp-p

1Vp-p

EXT

SYNC

6dB

H.DRIVE

YS1 OFF

YS

SW

SUB CONT

Sand

Castle

≠ 3 ≠

CXA2000Q

Pin Configuration

HSIN

E-WOUT

VSFIL

L2FIL

IREF

SAWOSC

CERA

HDOUT

SDA

VAGCSH

VSIN

AFCFIL

DV

CC

2

DV

CC

1

DGND

AFCPIN/HOFF

VM

SCL

SYNCOUT

EXT SYNC IN

TEST

APCFIL

X358

BLHOLD

CIN

NC

SV

CC

1

X443

DCTRAN

CVIN

YIN

ABLIN/VCOMP

BOUT

SV

CC

2

GOUT

ROUT

IKIN

RSH

BSH

GSH

VTIM

VD≠OUT/VPROT

ABLFIL

40 39 38

37 36

41

42

43

44

45

46

47

48

49

50

51

35

34

33

26

27

28

29

30

31

32

20

21

22

23

24

25

YOUT

B2IN

≠(R-Y) IN

G1IN

SGND2

R2IN

YS1

YS2

SECAMREF

G2IN

YRET

R1IN

≠(B-Y) IN

YM

SCPOUT

B1IN

≠(R-Y) OUT

SGND1

≠(B-Y) OUT

2

3

4

5

6

7

8

9

10 11 12 13 14 15 16 17 18 19

1

52

53

54

55

56

57

58

59

60

63

64

61

62

FSCOUT

VD+OUT/VPROT

≠ 4 ≠

CXA2000Q

SECAM decoder interface. This pin

serves as both a 4.43MHz output and as

a SECAM identification input/output pin.

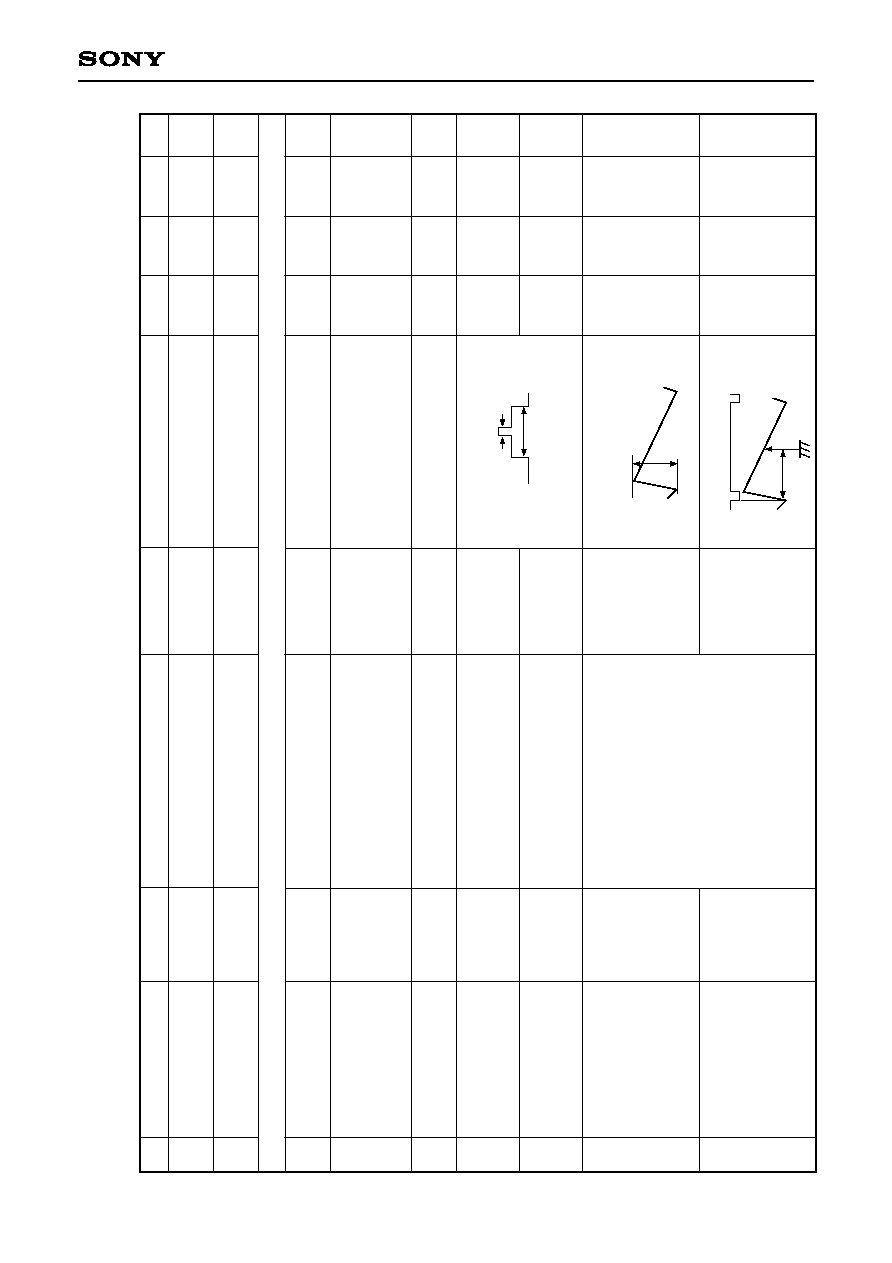

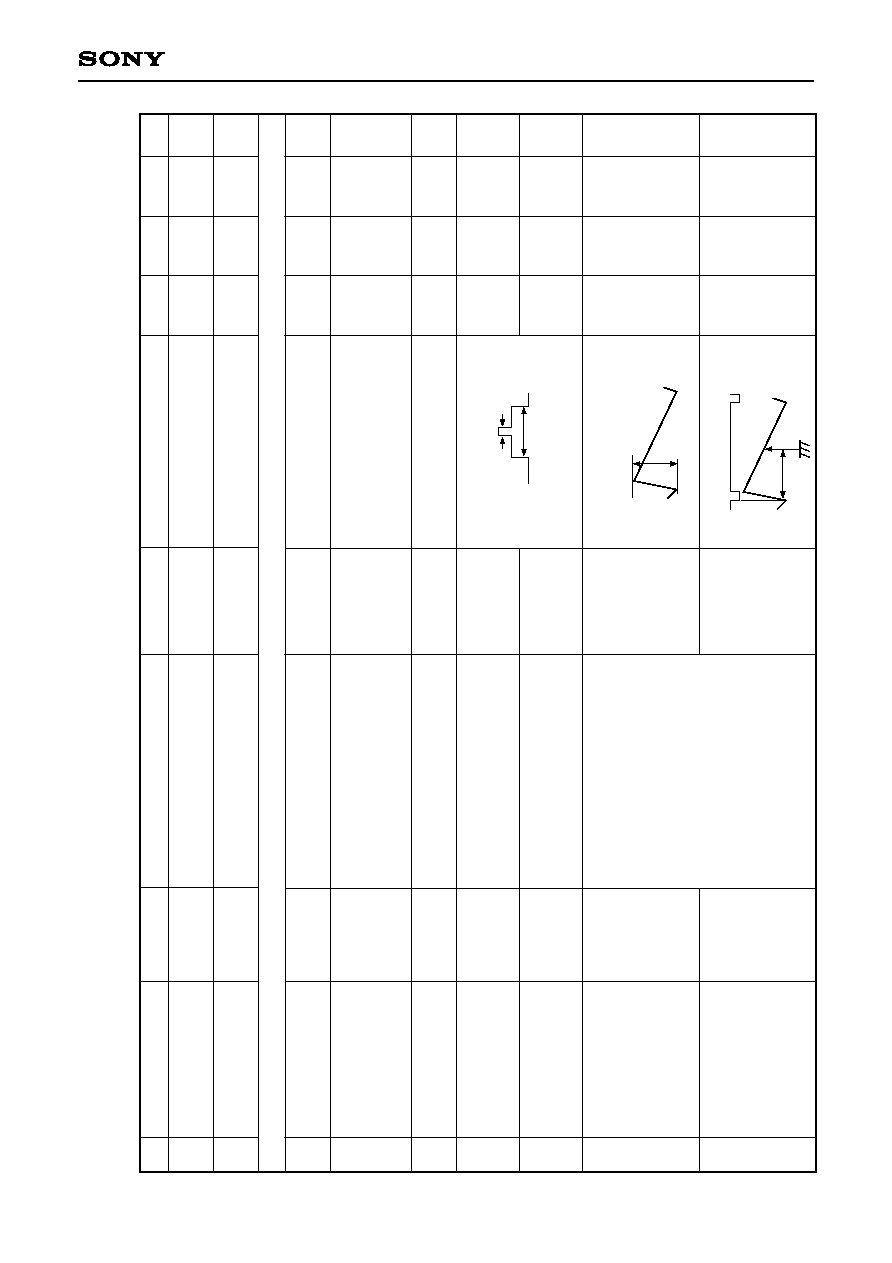

Pin Description

Pin

No.

Symbol

Equivalent circuit

Description

1

SECAMREF

3

4

≠(R-Y) OUT

≠(B-Y) OUT

Color difference signal outputs. Go to

high impedance when the SECAM

system is detected.

Standard output levels for 75% CB:

B-Y: 0.665Vp-p

R-Y: 0.525Vp-p

5

YOUT

Luminance signal output.

Black level is 3.5VDC.

Standard output level for 100 IRE input:

1Vp-p

6

YRET

Luminance signal input.

Clamped to 4.8V at the burst timing.

Standard input level for 100 IRE input:

1Vp-p

7

8

≠(R-Y) IN

≠(B-Y) IN

Color difference signal inputs.

Clamped to 5.5V at the burst timing.

Standard input levels for 75% CB:

B-Y: 1.33Vp-p

R-Y: 1.05Vp-p

2

SGND1

GND for Y/C block.

9

SGND2

GND for the RGB block.

1

250µA

6k

20p

7.2V

3

200µA

4

400µA

500

30k

5

6

1.5k

70k

7

8

1.5k

70k

--

≠ 5 ≠

CXA2000Q

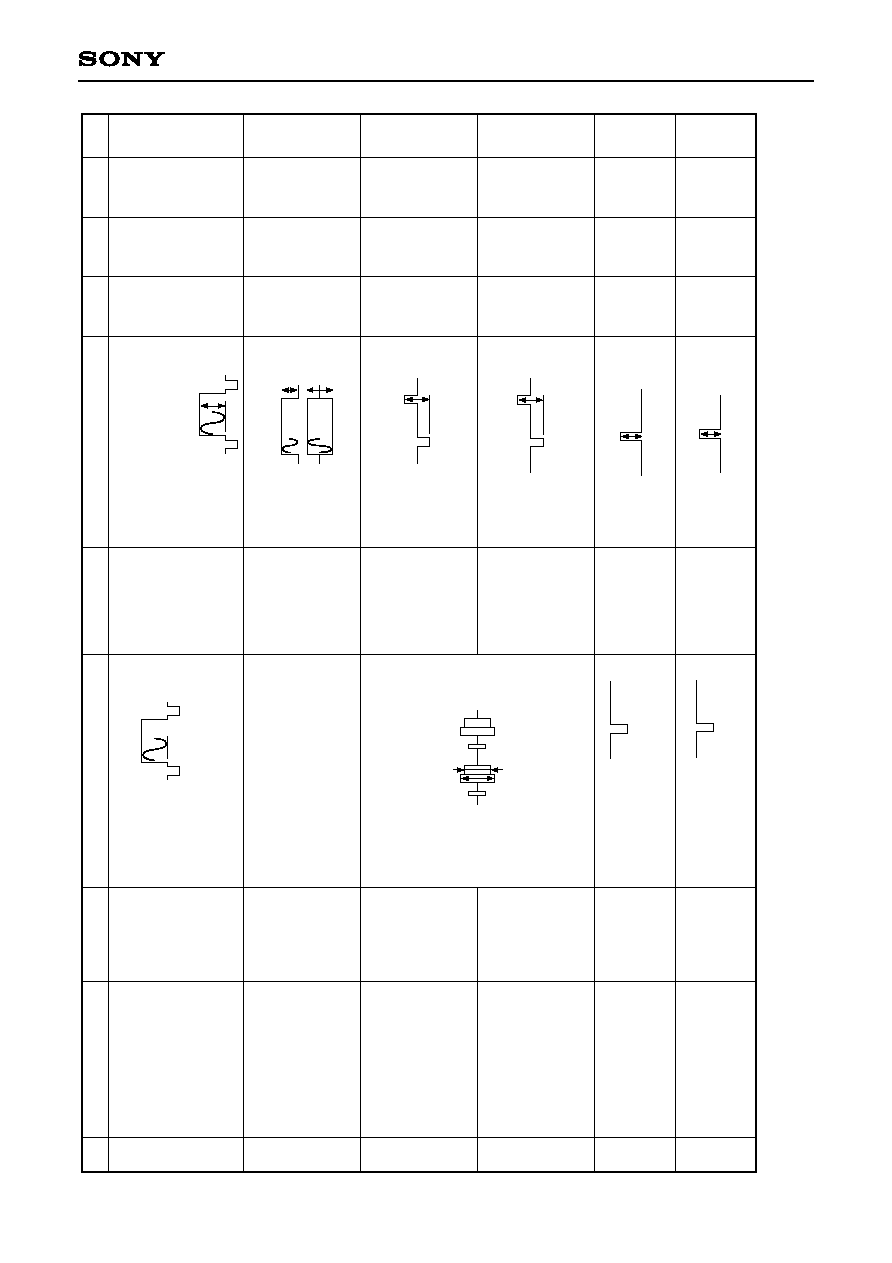

YSSW control input.

When YS is high, the RGB1 block signal

is selected; when YS is low, the Y/C block

is selected. This function can be disabled

by the YS1OFF setting for the I

2

C bus.

VILMAX = 0.4V

VIHMIN = 1.0V

10

SCPOUT

Sand castle pulse output. The 0 to 5V

BGP pulse, the phase of which is

controlled through the bus, is

superimposed with the 0 to 2V H and

VBLK pulse for output.

11

YS1

12

13

14

R1IN

G1IN

B1IN

Analog R, G and B signal inputs.

Input a 0.7Vp-p (no sync, 100 IRE) signal

via a capacitor.

The signal is clamped to 5.7V at the burst

timing of the signal input to the HSIN

input pin (Pin 47).

15

YS2

YS/YMSW YS control input.

When YS is high, the RGB2 block signal

is selected; when YS is low, the YSSW

output signal is selected.

VILMAX = 0.4V

VIHMIN = 1.0V

10k

1k

1k

10

100µA

40k

11

12

13

14

30k

200

100µA

40k

15

16

YM

YS/YMSW YM control input.

When YM is high, the YSSW output

signal is attenuated by 9.6dB.

VILMAX = 0.4V

VIHMIN = 1.0V

100µA

40k

16

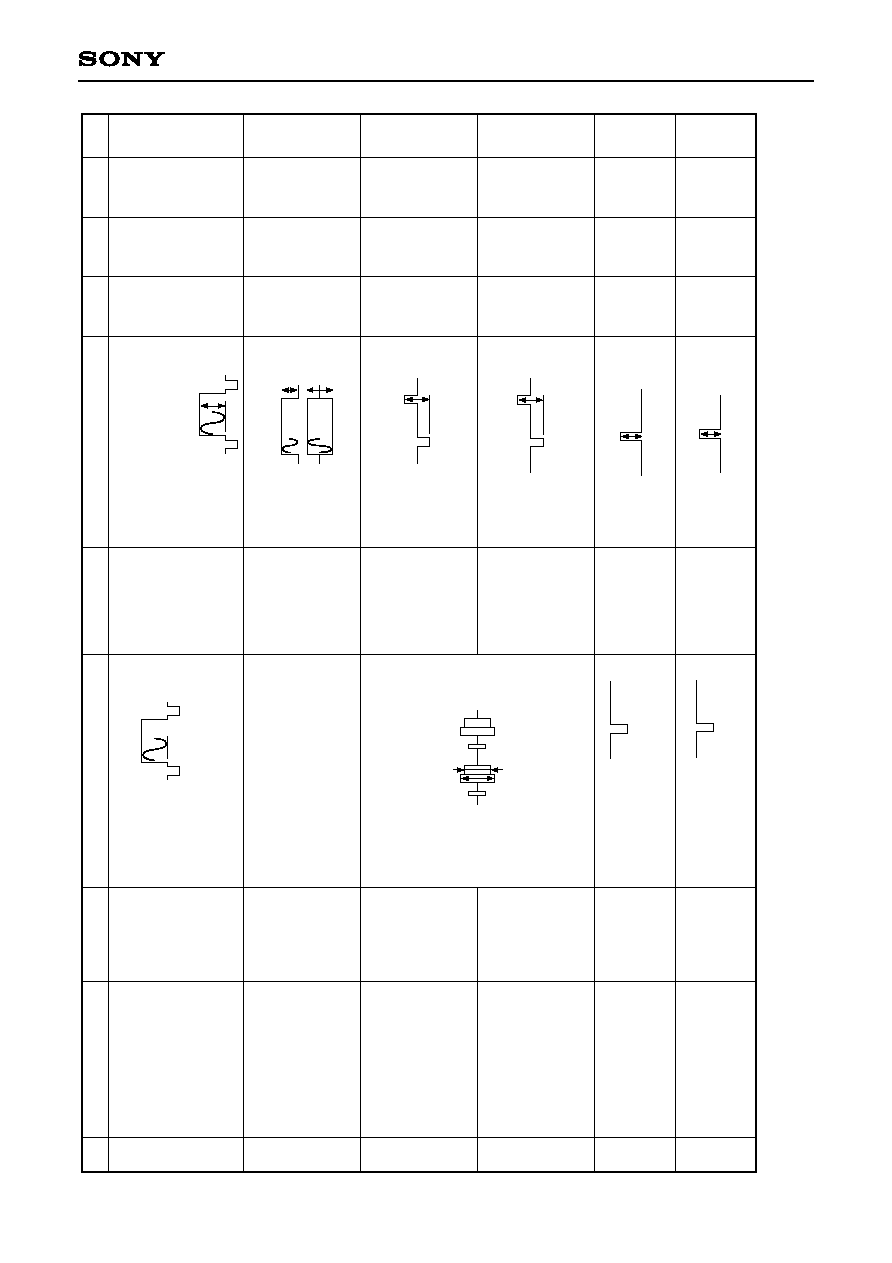

Pin

No.

Symbol

Equivalent circuit

Description

≠ 6 ≠

CXA2000Q

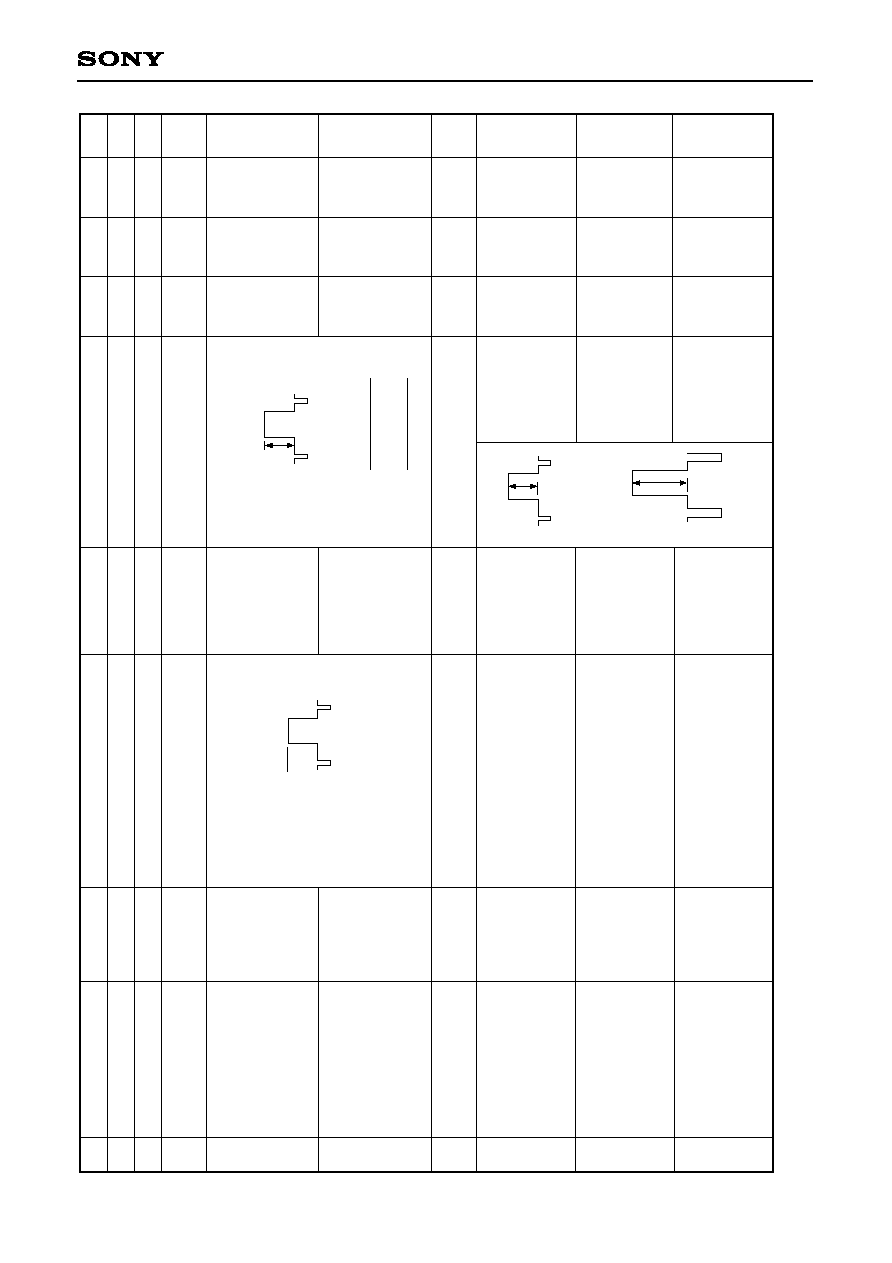

Power supply for RGB block.

17

18

19

R2IN

G2IN

B2IN

Analog/digital (dual-purpose) RGB signal

inputs.

The input signals are input via capacitors.

When using analog input, input a 0.7Vp-p

signal (no sync, 100 IRE); when using

digital input, input a signal of at least

1.5Vp-p (Vth = 1.2V).

The display level is 67 IRE. When using

digital input, digital input is selected

regardless of the YS setting.

In addition, the VM output is turned off.

These pins are clamped to 5.7V at the

burst timing of the signal input to the

sync input pin (Pin 47).

30k

200

19

17

18

100µA

21

23

25

RSH

GSH

BSH

Sample-and-hold for R, G and B AKB.

Connect to GND via a capacitor.

When not using AKB (manual CUTOFF

mode), R, G and B cut-off voltage can be

controlled by applying a control voltage to

each pin. The control voltage is 4.5 ± 1V.

200

21

23

25

22

24

26

ROUT

GOUT

BOUT

R, G and B signal outputs.

2.5Vp-p is output during 100% white

input.

1.1mA

200

12k

22

24

26

27

IKIN

Input the signal converted from the CRT

beam current (cathode current Ik) to a

voltage via a capacitor. The V blanking

part is clamped to 2.7V at the V retrace

timing.

The input for this pin is the reference

pulse return, and the loop operates so

that the Rch is 1Vp-p and the G and Bch

are 0.81Vp-p. The G and Bch can be

varied by ±0.5V by the bus CUTOFF

control. When not using AKB, this pin

should be open.

1k

27

50µA

20

SV

CC

2

Pin

No.

Symbol

Equivalent circuit

Description

≠ 7 ≠

CXA2000Q

Connect a capacitor to form the LPF of

the ABL control signal.

28

ABLIN/VCOMP

ABL control signal input and VSAW high

voltage fluctuation compensation signal

input.

High voltage compensation has linear

control characteristics for the pin voltage

range of about 8V to 1V. The control

characteristics can be varied through

EHT-V control of the bus. ABL begins to

have effect below a threshold voltage of

about 1.2V.

ABL functions as PIC/BRT-ABL (average

value type).

29

ABLFIL

30

VTIM

V timing pulse output.

Outputs the timing pulse from V sync

identification to the end of V blanking.

Pulses are positive polarity from 1 to 6V.

During zoom mode, the V blanking pulse

which has been expanded before and

after the V sync is superimposed and

output as the 1 to 3V pulse.

1.5V

147

28

29

1.2k

100k

10k

1k

1k

30

31

VD≠OUT/VPROT

V sawtooth wave output and V protect

signal input.

When a large current (3mA) is drawn

from this pin, the RGB outputs are all

blanked and "1" is output to the status

register VNG.

31

400µA

700

24k

30k

32

VD+OUT/VPROT

Serves as both a V sawtooth wave output

with the reverse polarity of VD≠OUT,

and a Vprotect signal input. The Vprotect

function can even be applied to this pin.

400µA

700

30k

24k

32

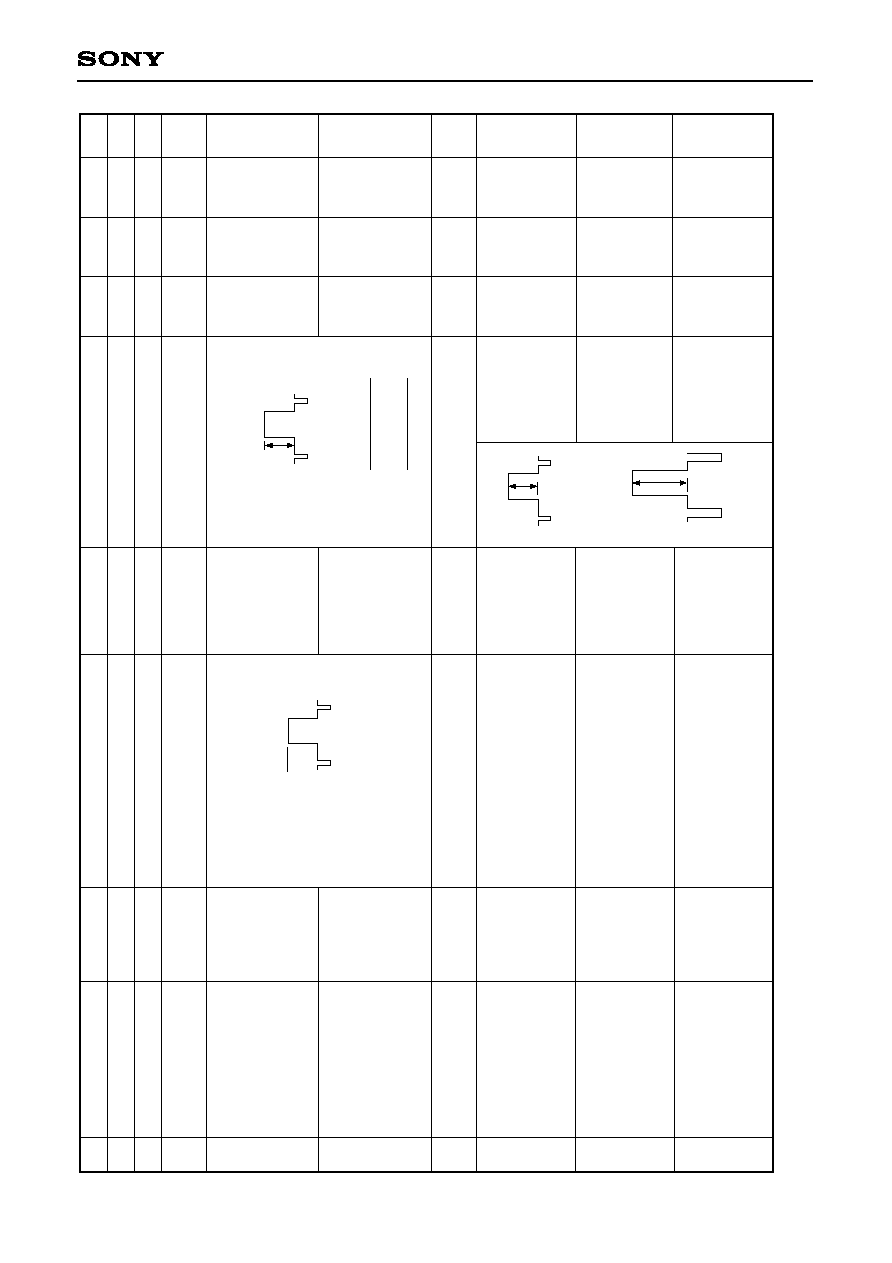

Pin

No.

Symbol

Equivalent circuit

Description

≠ 8 ≠

CXA2000Q

H deflection pulse input for H AFC.

Input an about 5Vp-p pulse via a

capacitor. Set the pulse width to 10 to

12µs. This pin is also used as the hold-

down signal input for the HD output, and

if this pin is 1V or less for a 7V cycle or

longer, the hold-down function operates

and the HD output is held to 9VDC. In

addition, the RGB outputs are all blanked.

Outputs "1" to the status register XRAY.

38

33

E-WOUT

V parabola wave output.

34

VAGCSH

Sample-and-hold for AGC which

maintains the V sawtooth wave at a

constant amplitude.

Connect to GND via a capacitor.

800µA

15k

78k

1.4k

33

1.2k

34

35

SAWOSC

Connect a capacitor to generate the V

sawtooth wave. For the capacitor, use an

MPS (metalized polyester capacitor), etc.,

with a small tan

.

100

300

35

36

DV

CC

1

Power supply for the V deflection block.

37

HD OUT

H drive signal output.

This signal is output with the open

collector.

147

37

20k

AFCPIN/HOFF

10k

68k

38

10k

147

4.2V

Pin

No.

Symbol

Equivalent circuit

Description

≠ 9 ≠

CXA2000Q

CR connection for the AFC lag-lead filter.

IREF

39

L2FIL

Filter for H AFC.

Connect to GND via a capacitor.

The H phase can also be controlled from

this pin by leading current in and out of

this capacitor.

As the pin voltage rises, the picture shifts

to the left; as the pin voltage drops, the

picture shifts to the right.

40

AFCFIL

100

39

46k

1.2k

40

41

CERA

Connect the 32

◊

FH VCO ceramic

oscillator.

41

400µA

10k

42

44

DGND

DV

CC

2

Power supply for the H deflection block.

GND for the deflection block.

43

Internal reference current setting.

Connect to GND via a resistor with an

error of less than 1% (such as a metal

film resistor).

147

43

20k

45

VSFIL

Filter for V sync separation.

Connect to GND via a capacitor.

1k

45

Pin

No.

Symbol

Equivalent circuit

Description

≠ 10 ≠

CXA2000Q

Sync signal output for VSIN and HSIN.

The output can be selected from the

internal sync signals (Pin 53 or Pin 55) or

the external sync signal (Pin 56) by the

I

2

C bus.

Output signal level: 2Vp-p

(0.6Vp-p sync only)

Input/output gain: 6dB

46

VSIN

Sync signal input for V sync separation.

Input a 2Vp-p Y signal (or a 0.6Vp-p

sync signal).

47

HSIN

Sync signal input for H sync separation.

Input a 2Vp-p Y signal (or a 0.6Vp-p sync

signal).

48

SYNCOUT

147

4.1V

46

20µA

15k

147

3.2V

10µA

14k

47

240µA

1.2k

40k

48

147

49

VM

Outputs the differential waveform of the

VM (Velocity Modulation) Y signal.

(6.6VDC, 1.1Vp-p)

The signal advanced for 200ns from

YOUT is output. The delay time versus

YIN is determined by the DL setting of

the I

2

C bus. This output can be turned off

through the I

2

C bus.

This output can also be turned off by

YS1, YM, and YS2.

400µA

500

30k

147

49

1.2k

50

SCL

I

2

C bus protocol SCL (Serial Clock) input.

VILMAX = 1.5V

VIHMIN = 3.5V

4k

50

Pin

No.

Symbol

Equivalent circuit

Description

≠ 11 ≠

CXA2000Q

Capacitor connection for black peak hold

of the dynamic picture (black expansion).

51

SDA

I

2

C bus protocol SDA (Serial Data) I/O.

VILMAX = 1.5V

VIHMIN = 3.5V

VOLMAX = 0.4V

52

BLHOLD

53

CVIN

Composite video signal input.

Input the 1Vp-p (100% white including

sync) CV signal via a capacitor. The

sync level of the input signal is

clamped to 3.8V.

In addition, this pin detects input video

signal HSYNC, and outputs the status

via the status register CVSYNC.

4k

51

1.2k

4k

52

9µA

20k

20k

4.6V

1µA

4.6V

53

54

DCTRAN

Connect a capacitor that determines the

DC transmission ratio to GND.

2k

54

2V

1.2k

4k

55

YIN

Y signal input.

Input a 1Vp-p (100% white including

sync) Y signal via a capacitor. The

sync level of the input signal is

clamped to 3.8V.

1µA

4.6V

55

Pin

No.

Symbol

Equivalent circuit

Description

≠ 12 ≠

CXA2000Q

Chroma signal input.

Input a C signal with a burst level of

300mVp-p via a capacitor. Input signal is

biased to 4.5V internally.

56

EXT SYNC IN

External sync signal input.

Input a 0.3Vp-p sync signal (or a 1Vp-p

CV signal or Y signal) via a capacitor.

The sync level of the input signal is

clamped to 3.8V.

57

CIN

1µA

4.6V

56

30k

5.2V

50k

57

58

TEST

Test pin.

Outputs a 0 to 3V V-SYNC SEP with

positive polarity. If not used, leave this

pin open.

15k

1k

58

59

SV

CC

1

Power supply for Y/C block.

60

APCFIL

CR connection for the chroma APC lag-

lead filter.

1.2k

4.6V

1.2k

60

61

X443

Connect a 4.433619MHz crystal oscillator.

200µA

4k

61

500

Pin

No.

Symbol

Equivalent circuit

Description

≠ 13 ≠

CXA2000Q

Not connected.

Normally connected to GND to prevent

interference with other pins.

62

X358

Connect a 3.579545MHz crystal oscillator.

200µA

4k

500

62

64

FSCOUT

Subcarrier output.

Output level: 5.2VDC, 0.4Vp-p

280µA

1.2k

147

64

63

NC

Pin

No.

Symbol

Equivalent circuit

Description

≠ 14 ≠

CXA2000Q

Electrical Characteristics

Setting conditions

∑

Ta = 25∞C, SV

CC

1, 2 = DV

CC

1, 2 = 9V, SGND1, 2 = DGND = 0V

∑

Measures the following after setting the I

2

C bus register as shown in "I

2

C Bus Register Initial Settings".

1

2

3

4

5

6

7

8

9

SICC

DICC

fHFR

fHR

HDw

VBLKh

VBGPh

VSp-p

VSdc

86

65

15.90

400

26.5

12.6

3.3

1.1

3.1

42

30

15.55

≠400

24.5

11.6

2.5

0.9

2.9

Measure the pin inflow current.

Measure the pin inflow current.

HDRIVE output frequency

Confirm that I

2

C status register

HLOCK is 1 (the pull-in range

when f

H

is shifted from

15.734kHz).

Measure the pulse width for the section

where the HDRIVE output is high.

Measure the VDRIVE output Vp-p.

V

CC

= 9.0V,

Bus data = center

V

CC

= 9.0V,

Bus data = center

AFC MODE = 0h

SYNCIN: composite sync

SYNCIN: composite sync

SCP

Measure the pulse width for the

section where the BLK output is high.

SCP

Measure the pulse width for the section

where the BGP output is high.

SYNCIN: composite sync

Signal block current

consumption

Sync block current

consumption

Horizontal free-running

frequency

Horizontal sync pull-in

range

HD output pulse width

SCP

BLK output pulse width

SCP

BGP output pulse width

VDRIVE output

amplitude

VDRIVE output center

potential

20, 59

36, 44

37

--

37

10

10

31, 32

31, 32

mA

mA

kHz

Hz

µs

µs

µs

V

V

No.

Item

Symbol

Measurement conditions

Measurement pins

Measurement contents

Min.

Typ.

Max.

Unit

Sync deflection block items

VBGPh

VBLKh

VSp-p

10.79ms

VDRIVE+

VSdc

46: VSIN in

65

48

15.734

--

25.5

12.1

2.9

1.0

3.0

≠ 15 ≠

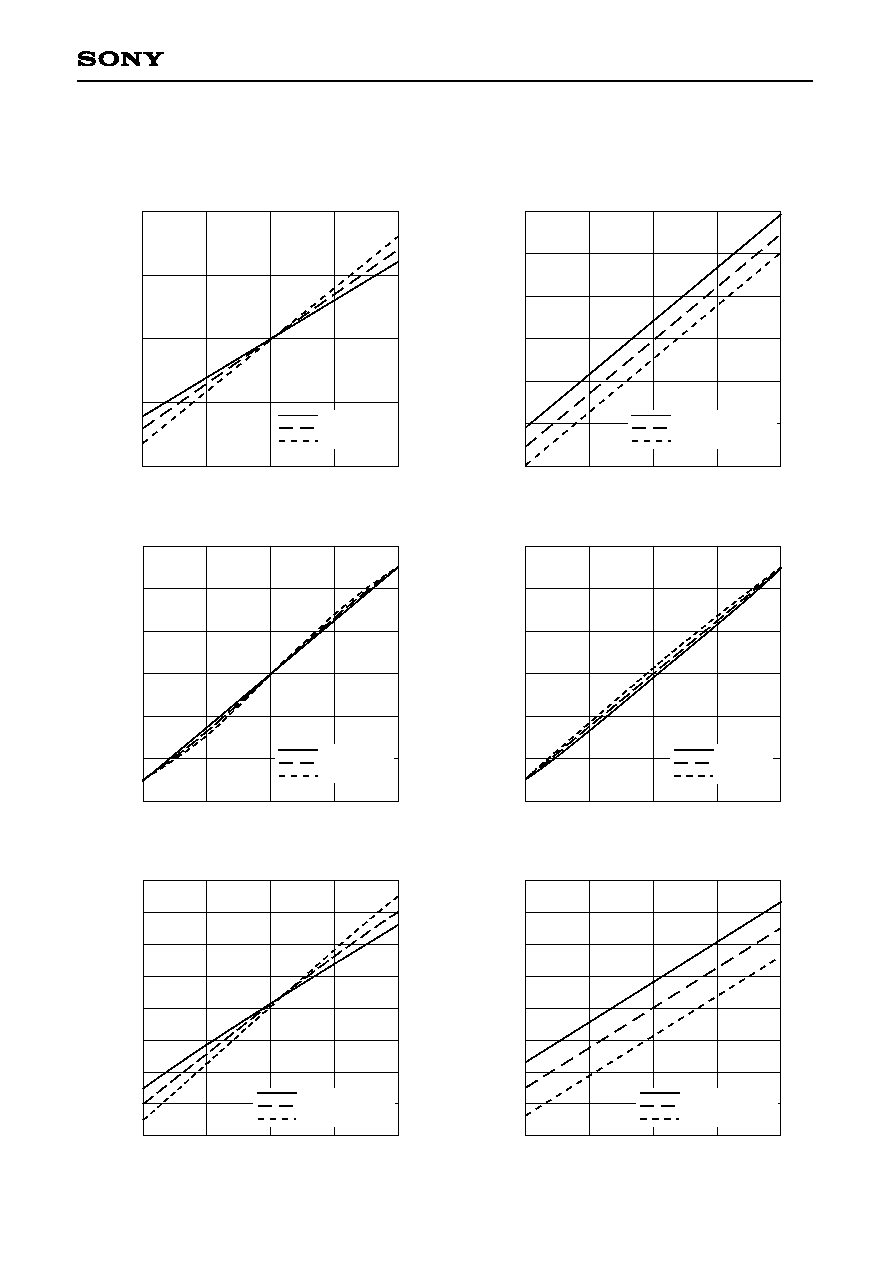

CXA2000Q

Measure the EWDRIVE output

Vp-p.

Output amplitude when a video

signal with an amplitude of

0.7Vp-p/100 IRE is input.

Input fsc to CVIN.

Ratio of the fsc component of the

Yout amplitude when CTRAP = 1

against the Yout amplitude when

CTRAP = 0.

SYNCIN: composite sync

TRAPOFF = 0/1

TRAP-F0 = 7h

10

11

12

13

14

EWDRIVE output

amplitude

EWDRIVE output

center potential

R, G and B output

amplitude

R, G and B output

linearity

C-TRAP attenuation

(3.58MHz)

VEWp-p

VEWdc

VRout1

Lin

C-Trap3.58

33

33

22, 24, 26

22, 24, 26

22

0.42

3.8

2.25

96

--

0.52

3.95

2.5

100

≠30

0.62

4.1

2.85

104

--

V

V

V

%

dB

No.

Item

Symbol

Measurement conditions

Measurement pins

Measurement contents

Min.

Typ.

Max.

Unit

Signal block items

VEWp-p

10.79ms

VEW dc

46: VSIN in

V1

V2

Lin

=

V2

◊

2

V1

◊

100

f = 3.58MHz

CVIN:

0.7Vp-p

/100 IRE

CVIN:

100 IRE

50 IRE

CVIN:

fsc, 50 IRE

≠ 16 ≠

CXA2000Q

Input fsc to CVIN.

Ratio of the fsc component of the

Yout amplitude when CTRAP = 1

against the Yout amplitude when

CTRAP = 0.

TRAPOFF = 0/1

TRAP-F0 = 7h

CVIN: 3MHz, 50 IRE

VMOFF = 0

4.43MHz PAL input

burst fsc 300mVp-p

640mVp-p fsc + 90∞

SUB-COLOR = 7h

PAL input: COLOR = 1Fh

PAL input: COLOR = 1Fh

15

16

17

18

19

20

C-TRAP attenuation

(4.43MHz)

VM output

Color difference

≠(R-Y) output

Color difference

≠(B-Y) output

Color gain

≠(R-Y)

Color gain

≠(B-Y)

C-Trap4.43

Vvm

Vr-y

Vb-y

Vcolr-y

Vcolb-y

22

49

3

4

22

24

--

0.75

440

570

1.4

1.1

≠30

0.95

510

640

1.6

1.3

--

1.15

570

710

1.8

1.5

dB

V

mV

mV

V

V

No.

Item

Symbol

Measurement conditions

Measurement pins

Measurement contents

Min.

Typ.

Max.

Unit

BOUT

Vcolb-y

ROUT

Vcolr-y

≠(B-Y)

OUT

Vb-y

≠(R-Y)

OUT

Vr-y

f = 3MHz

50 IRE

Vvm

f = 4.43MHz

CVIN:

fsc, 50 IRE

450mVp-p

fsc + 0∞

,

fsc + 180∞

CIN

≠(R-Y) IN: 525mVp-p

≠(B-Y) IN: 665mVp-p

≠ 17 ≠

CXA2000Q

Confirm that the burst frequency

is pulled in at 3.58MHz ±

400Hz.

ROUT, BOUT

GdcolR =

◊

100

GdcolB =

◊

100

Output amplitude ratio when the

R, G and BOUT YM = 1 and 0

VLR1out = Vout

VLG1out = Vout

VLB1out = Vout

HUE = 1Fh, SUB ≠ HUE = 7h

CVIN: Burst only

D-COL = 0/1

YS1: 1V

RGB1IN: 0.7Vp-p

YS1: 1V

RGB1IN: 0.7Vp-p

YS1: 1V

RGB1IN: 0.7Vp-p

21

22

23

24

25

26

27

28

29

Hue center offset

Killer point

APC pull-in range

Dynamic color

operation R output

Dynamic color

operation B output

YM gain

R output amplitude

during linear R1 input

G output amplitude

during linear G1 input

B output amplitude

during linear B1 input

offset

KP

fAPC

GdcolR

GdcolB

GYM

VLR1out

VLG1out

VLB1out

--

--

--

22

24

22, 24, 26

22

24

26

≠8

--

≠400

94

102

≠10.6

1.85

1.85

1.85

0

≠35

--

96

104

≠9.6

2.05

2.05

2.05

8

--

400

98

106

≠8.6

2.25

2.25

2.25

deg

dB

Hz

%

%

dB

V

V

V

No.

Item

Symbol

Measurement conditions

Measurement pins

Measurement contents

Min.

Typ.

Max.

Unit

Vp-p (DCOL = 1)

Vp-p (DCOL = 0)

Vp-p (DCOL = 1)

Vp-p (DCOL = 0)

Vp-p

CVIN: 100 IRE

RGB1

IN

R, G, B

out

≠ 18 ≠

CXA2000Q

Unit

VLR2out = Vout

VLG2out = Vout

VLB2out = Vout

VDRout = Vout

VDGout = Vout

VDBout = Vout

YS2: 1V

RGB2IN: 0.7Vp-p

YS2: 1V

RGB2IN: 0.7Vp-p

YS2: 1V

RGB2IN: 0.7Vp-p

RGB2IN: 1.5Vp-p

RGB2IN: 1.5Vp-p

RGB2IN: 1.5Vp-p

SYNCIN: composite sync

GCUTOFF = 0h

BCUTOFF = 0h

30

31

32

33

34

35

36

37

38

R output amplitude

during linear R2

input

G output amplitude

during linear G2

input

B output amplitude

during linear B2

input

R output amplitude

during digital R2

input

G output amplitude

during digital G2

input

B output amplitude

during digital B2

input

IK level R

IK level G

IK level B

VLR2out

VLG2out

VLB2out

VDRout

VDGout

VDBout

VIKR

VIKG

VIKB

22

24

26

22

24

26

27

27

27

1.85

1.85

1.85

58

58

58

0.85

0.22

0.22

2.05

2.05

2.05

67

67

67

1.00

0.35

0.35

2.25

2.25

2.25

75

75

75

1.15

0.5

0.5

V

V

V

IRE

IRE

IRE

V

V

V

No.

Item

Symbol

Measurement conditions

Measurement pins

Measurement contents

Min.

Typ.

Max.

RGB2

IN

RGB2

IN

VIKG

VIKR VIKB

R, G, B

out

R, G, B

out

≠ 19 ≠

CXA2000Q

Electrical Characteristics Measurement Circuit

Signal sources are all GND unless otherwise specified in the Measurement conditions column of Electrical

Characteristics.

YOUT

B2IN

≠(R-Y) IN

G1IN

SGND2

R2IN

YS1

YS2

SECAMREF

G2IN

YRET

R1IN

≠(B-Y) IN

YM

SCPOUT

B1IN

≠(R-Y) OUT

SGND1

≠(B-Y) OUT

120µ

SECAMREF

≠(R-Y) OUT

≠(B-Y) OUT

Y OUT

0.1µ

≠(R-Y) IN

0.1µ

0.1µ

≠(B-Y) IN

SCP OUT

220

YS1

0.01µ

220

YS2

220

YM

0.01µ

0.01µ

RGB1IN

RGB2IN

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

1

3.3k

4700p

500k

SDA

220

SCL

220

VM

100p

560

4700p

100

1µ

1k

+9V

330k

+9V

0.47µ

0.01µ

47µ

10k

270

8.2k

1µ

0.01µ

E/W

100

0.1µ

0.1µ

(MPS)

+9V

0.01µ

47µ

+9V

2.7k

0.01µ

HP GEN.

10k

HOFF

40

39

38

37

36

41

42

43

44

45

46

47

48

49

50

51

35

34

33

HSIN

E-WOUT

VSFIL

L2FIL

IREF

SAWOSC

DGND

HDOUT

SDA

VAGCSH

VSIN

AFCFIL

DV

CC

2

DV

CC

1

CERA

AFCPIN/HOFF

VM

SCL

SYNCOUT

10µ

10µ

CV IN

0.47µ

10µ

Y IN

10µ

EXT SYNC IN

10µ

C IN

TEST

EXT SYNC IN

TEST

FSC OUT

APCFIL

X358

BLHOLD

CIN

NC

SV

CC

1

X443

DCTRAN

CVIN

YIN

FSC OUT

1.5k

3.58MHz

15p

470

4.43MHz

15p

470p

0.01µ

47µ

0.47µ

15k

+9V

52

53

54

55

56

57

58

59

60

63

64

61

62

+9V

0.01µ

47µ

0.1µ

0.1µ

100

100

0.1µ

100

20k

51k

20k

ABLIN/VCOMP

BOUT

SV

CC

2

GOUT

ROUT

VD+OUT/VPROT

IKIN

RSH

BSH

GSH

VTIM

VD≠OUT/VPROT

ABLFIL

0.001µ

1µ

+9V

IK IN

9V

100

10µ

100

100

10k

820

VPROT

26

27

28

29

30

31

32

20

21

22

23

24

25

R OUT

G OUT

B OUT

0.01µ

0.01µ

0.01µ

VTIM

VDRV≠

VDRV+

≠ 20 ≠

CXA2000Q

1T1

V

SS

1T2

1B

1CD

1Q

1A

1Q

V

DD

2Q

2T1

2A

2T2

2Q

2CD

2B

TC4538BP

1k

1k

5V

from HDOUT

10k

2

3

4

5

6

7

8

1

2000p

10k

2000p

9

10

11

12

13

14

15

16

47µ

to AFCPIN

HDOUT

delay 7µ

s

AFCPIN

width12µ

s

9V

HP GEN.

≠ 21 ≠

CXA2000Q

Application Circuit

YOUT

B2IN

≠(R-Y) IN

G1IN

SGND2

R2IN

YS1

YS2

SECAMREF

G2IN

YRET

R1IN

≠(B-Y) IN

YM

SCPOUT

B1IN

≠(R-Y) OUT

SGND1

≠(B-Y) OUT

SECAM reference

input/output for

SECAM IC

0.1µ

3.3k

4700p

500k

I

2

C BUS

input/output

220

220

VM

output

100p

470

0.0047µ

100

1µ

2.2k

+9V

+9V

0.47µ

47µ

0.01µ

10k

470

5.6k

2.2µ

0.01µ

100

0.1µ

0.1µ

+9V

0.01µ

47µ

0.1µ

10k

HSIN

E-WOUT

VSFIL

L2FIL

IREF

SAWOSC

DGND

HDOUT

SDA

VAGCSH

VSIN

AFCFIL

DV

CC

2

DV

CC

1

CERA

AFCPIN/HOFF

VM

SCL

SYNCOUT

4.7µ

CV signal input

0.47µ

2.2µ

2.2µ

0.47µ

EXT SYNC IN

TEST

APCFIL

X358

BLHOLD

CIN

NC

SV

CC

1

X443

DCTRAN

CVIN

YIN

FSC OUT

1.5k

3.579545MHz

15p

510

4.433619MHz

15p

470p

0.01µ

47µ

0.47µ

15k

+9V

+9V

0.01µ

47µ

0.1µ

0.1µ

100

100

0.1µ

100

ABLIN/VCOMP

BOUT

SV

CC

2

GOUT

ROUT

VD+OUT/VPROT

IKIN

RSH

BSH

GSH

VTIM

VD≠OUT/VPROT

ABLFIL

0.001µ

220

100

10µ

100

100

820

Color difference

outputs for 1H

delay line

Color difference

outputs from

1H delay line

0.1µ

0.1µ

Sand castle

pulse output

YS1

input

220

Analog RGB

inputs

YS2/YM

inputs

220

220

Analog/digital

RGB inputs

RGB outputs

1µ

10µ

1k

Ik input

ABL/Vertical high

voltage fluctuation

compensation signal

input

10k

V protect

signal input

V timing

pulse output

V sawtooth

wave outputs

HD output

HP output

Hold-down input

330k

220

Y signal input

External sync

signal input

C signal input

2.2µ

40

39

38

37

36

41

42

43

44

45

46

47

48

49

50

51

35

34

33

26

27

28

29

30

31

32

20

21

22

23

24

25

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

1

52

53

54

55

56

57

58

59

60

63

64

61

62

1: Metal film resistor recommended

2: MPS capacitor recommended

V parabola wave output

0.01µ

0.01µ

0.01µ

0.01µ

0.01µ

0.01µ

2.7k

100

0.1µ

1

2

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for

any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

≠ 22 ≠

CXA2000Q

Electrical Characteristics Measurement Conditions "I

2

C Bus Register Initial Settings"

Register

name

No. of

bits

Initial

setting

Description

PICTURE

TRAPOFF

VMOFF

HUE

DCTRAN

D-PIC

COLOR

TOT

BRIGHT

D-COL

SHARPNESS

PRE-OVER

COLOR SW

SUB-CONT

TRAP F0

SUB-COLOR

SUB-HUE

SUB-BRIGHT

GAMMA

G-DRIVE

AGING

B-DRIVE

INTERLACE

G-CUTOFF

B-CUTOFF

RON

GON

BON

PICON

VOFF

FHHI

CD-MODE

AKBOFF

V-SIZE

6

1

1

6

1

1

6

1

6

1

4

2

2

4

4

4

4

6

2

6

1

6

2

4

4

1

1

1

1

1

1

1

1

6

3Fh

1h

1h

1Fh

0h

0h

1Fh

0h

1Fh

0h

7h

3h

0h

7h

7h

7h

7h

1Fh

0h

2Ah

0h

2Ah

0h

0h

0h

1h

1h

1h

1h

0h

0h

0h

0h

1Fh

Maximum value

TRAP off

VM off

Center value

DCTRAN off

DPIC off

Center value

TOT off

Center value

DCOL off

Center value

Maximum value

Automatic switching

Center value

Center value

Center value

Center value

Center value

Minimum value

Center value

AGING off

Center value

Interlace

Minimum value

Minimum value

R output on

G output on

B output on

Picture mute off

VD output on

FH normal

Automatic switching

AKB on

Center value

V FREQ

V-POSITION

AFC-MODE

S-CORR

V-LIN

H-SIZE

REF-POSI

PIN-COMP

VBLKW

H-POSITOPN

PIN-PHASE

AFC-BOW

AFC-ANGLE

SCP BGR

SCP BGF

XTAL

EXT SYNC

CV/YC

V-ASPECT

ZOOM SW

HBLKSW

V-SCROLL

JMPSW

HSIZESW

UP-VLIN

LO-VLIN

LEFT-BLK

RIGHT-BLK

EHT H

EHT V

CORNER-PIN

YS1OFF

DL

2

6

2

4

4

6

2

6

2

4

4

4

4

2

2

2

1

1

6

1

1

6

1

1

4

4

4

4

2

2

4

1

3

0h

1Fh

1h

0h

7h

1Fh

3h

1Fh

0h

7h

7h

7h

7h

1h

1h

0h

0h

0h

0h

0h

0h

1Fh

0h

0h

0h

0h

7h

7h

0h

0h

7h

0h

3h

Automatic switching

Center value

Low gain

Minimum value

Center value

Center value

Maximum value

Center value

Minimum value

Center value

Center value

Center value

Center value

Center value

Center value

Automatic switching

Internal sync

CV input

Minimum value

ZOOM SW off

HBLKSW off

Center value

JMPSW off

HSIZESW off

Minimum value

Minimum value

Center value

Center value

EHT H off

EHT V off

Center value

YS1 normal

Center value

Register

name

No. of

bits

Initial

setting

Description

≠ 23 ≠

CXA2000Q

TRAP F0

SUB-HUE

B-CUTOFF

V-LIN

PIN-PHASE

AFC-ANGLE

LO-VLIN

RIGHT-BLK

CORNER-PIN

PICTURE

HUE

COLOR

BRIGHT

SUB-BRIGHT

G-DRIVE

B-DRIVE

V-SIZE

V-POSITION

H-SIZE

PIN-COMP

V-ASPECT

V-SCROLL

SHARPNESS

SUB-CONT

SUB-COLOR

G-CUTOFF

S-CORR

H-POSITION

AFC-BOW

UP-VLIN

LEFT-BLK

Definition of I

2

C Bus Registers

Slave Addresses

88h: Slave Receiver

89h: Slave Transmitter

Register Table

"

": Undefined

Control Register

Bit0

Bit1

Bit2

Bit3

Bit4

Bit5

Bit6

Bit7

Sub Address

◊ ◊ ◊

0 0 0 0 0 00 h

◊ ◊ ◊

0 0 0 0 1 01 h

◊ ◊ ◊

0 0 0 1 0 02 h

◊ ◊ ◊

0 0 0 1 1 03 h

◊ ◊ ◊

0 0 1 0 0 04 h

◊ ◊ ◊

0 0 1 0 1 05 h

◊ ◊ ◊

0 0 1 1 0 06 h

◊ ◊ ◊

0 0 1 1 1 07 h

◊ ◊ ◊

0 1 0 0 0 08 h

◊ ◊ ◊

0 1 0 0 1 09 h

◊ ◊ ◊

0 1 0 1 0 0A h

◊ ◊ ◊

0 1 0 1 1 0B h

◊ ◊ ◊

0 1 1 0 0 0C h

◊ ◊ ◊

0 1 1 0 1 0D h

◊ ◊ ◊

0 1 1 1 0 0E h

◊ ◊ ◊

0 1 1 1 1 0F h

◊ ◊ ◊

1 0 0 0 0 10 h

◊ ◊ ◊

1 0 0 0 1 11 h

◊ ◊ ◊

1 0 0 1 0 12 h

◊ ◊ ◊

1 0 0 1 1 13 h

◊ ◊ ◊

1 0 1 0 0 14 h

◊ ◊ ◊

1 0 1 0 1 15 h

◊ ◊ ◊

1 0 1 1 0 16 h

◊ ◊ ◊

1 0 1 1 1 17 h

◊ ◊ ◊

1 1 0 0 0 18 h

◊ ◊ ◊

1 1 0 0 1 19 h

TRAPOFF

DC-TRAN

TOT

D-COL

VMOFF

D-PIC

PRE-OVER

COLOR SW

GAMMA

AGING

0

AKBOFF

CD-MODE

FHHI

VOFF

PICON

BON

GON

RON

V-FREQ

AFC-MODE

REF-POSI

VBLKW

EXT SYNC

ZOOM SW

JMP SW

CV/YC

HBLKSW

HSIZESW

Status Register

Bit0

CV SYNC

Bit1

Bit2

Bit3

Bit4

XRAY

Bit5

VNG

Bit6

IKR

Bit7

H LOCK

INTERLACE

SCP BGR

SCP BGF

XTAL

EHT H

EHT V

YS1 OFF

DL

COLOR SYS

≠ 24 ≠

CXA2000Q

Description of Registers

Register name (No. of bits)

1. Video switch register

CV/YC

(1)

: CV input/YC input selector

0 = CV input selected

1 = YC input selected

EXT SYNC

(1)

: EXT SYNC selector switch

0 = Internal sync (CV or Y) selected

1 = EXT SYNC selected

2. Y signal block register

SUB-CONT

(4)

: Contrast gain control (Y gain control)

0h = ≠3.5dB

7h = 0dB

Fh = +2.5dB

TRAP-F0

(4)

: Chroma trap f0 fine adjustment (Y block chroma trap current control)

0h = High

7h = Center

Fh = Low

SHARPNESS (4)

: Sharpness gain control (Sharpness F0 3MHz)

0h = ≠6dB

7h = +2.5dB

Fh = +6.5dB

PRE-OVER

(2)

: Sharpness preshoot/overshoot ratio control

0h = 1:1

(PRE: OVER)

3h = 2:1

VM OFF

(1)

: Y signal output ON/OFF for VM

0 = ON

1 = OFF

TRAP OFF

(1)

: Y block chroma trap ON/OFF

0 = Trap ON

1 = Trap OFF

DL

(3)

: Y signal delay time control (80ns/step)

0h = Max.

7h = Min.

≠ 25 ≠

CXA2000Q

DC-TRAN

(1)

: Y DC transmission ratio selector switch

0 = 100%

1 = 81%

D-PIC

(1)

: Y black expansion ON/OFF switch

0 = OFF

1 = ON

Point of inflection: 30 IRE

3. C signal block register

TOT

(1)

: Chroma TOT filter band selector switch

0 = TOT -- TRAP OFF

1 = TOT -- TRAP ON (TRAP fo 2MHz)

COLOR

(6)

: Color gain control (Chroma gain control)

0h = Color OFF (≠40dB or less)

1Fh = 0dB B output: 1.02Vp-p (I/O gain: +11dB, 0.285Vp-p input)

3Fh = +6dB

SUB-COLOR (4)

: Color gain control (ACC reference level control)

0h = ≠5dB

7h = 0dB

Fh = +3dB

HUE

(6)

: Hue control (Phase control for chroma demodulation axis when SUB-HUE is 7h)

Control not possible for a PAL system.

0h = +35∞

Flesh color appears red.

1Fh = 0∞

3Fh = ≠35∞

Flesh color appears green.

SUB-HUE

(4)

: Hue control (Phase control for chroma demodulation axis when HUE is 1Fh)

B-Y axis adjustable to 0∞.

Control not possible for a PAL system.

0h = +10∞

7h = 0∞

Fh = ≠10∞

XTAL

(2)

: XTAL selection setting switch

0h = Automatic identification

1h = Force to XTAL1 (3.58MHz)

2h = Force to XTAL2 (4.43MHz)

COLOR SW

(2)

: Color system setting

0h = Automatic identification

1h = Force to PAL

2h = Force to NTSC

3h = Force to SECAM

≠ 26 ≠

CXA2000Q

4. RGB signal block register

PICTURE

(6)

: Picture gain control (RGB gain control)

0h = ≠14dB

3Fh = 0dB

RGB output: 2.5Vp-p (I/O gain: +8dB, 1Vp-p input)

BRIGHT

(6)

: Bright control (RGB DC bias control)

0h = ≠440mV

1Fh = 0mV (≠300mV for REF-P level)

3Fh = +450mV

SUB-BRIGHT (6)

: Bright control (RGB DC bias control)

0h = ≠440mV

1Fh = 0mV (≠300mV for REF-P level)

3Fh = +450mV

G-DRIVE

(6)

: Gch drive gain adjustment (Gch gain control)

0h = G/R ≠4.5dB

2Ah = G/R 0dB (G/R 0dB)

3Fh = G/R +1.5dB

B-DRIVE

(6)

: Bch drive gain adjustment (Bch gain control)

0h = B/R ≠4.5dB

2Ah = B/R 0dB (B/R 0dB)

3Fh = B/R +1.5dB

G-CUTOFF

(4)

: Gch cut-off adjustment (Gch reference pulse value control of IKIN pin input)

0h = +34%

7h = +81% (G/R)

Fh = +135%

B-CUTOFF (4): Bch cut-off adjustment (Bch reference pulse value control of IKIN pin input)

0h = +34%

7h = +81% (B/R)

Fh = +135%

D-COL

(1)

: Dynamic color ON/OFF switch

0 = Dynamic color OFF

1 = Dynamic color ON (R, Bch level control)

GAMMA

(2)

: Gamma control (RGB gamma correction amount control)

0h = Gamma OFF

3h = Gamma peak 17 IRE (at input 40 IRE), +400mV (at 2.5Vp-p OUT)

≠ 27 ≠

CXA2000Q

REF-POSITION (2)

: Reference pulse timing setting

0h = From rising edge of V TIM: Rch 22H, Gch 23H, Bch 24H

1h = From rising edge of V TIM: Rch 20H, Gch 21H, Bch 22H

2h = From rising edge of V TIM: Rch 18H, Gch 19H, Bch 20H

3h = From rising edge of V TIM: Rch 16H, Gch 17H, Bch 18H

PIC-ON

(1)

: ON/OFF switch for RGB output with a reference pulse

(Set to OFF mode at power-on.)

0 = RGB output OFF (All blanked status)

1 = RGB output ON

R ON

(1)

: ON/OFF switch for Rch video output without a reference pulse

(Operates when PIC ON = 1, set to OFF mode at power-on.)

0 = Rch video output OFF (Blanked status, reference pulse only output)

1 = Rch video output ON

G ON

(1)

: ON/OFF switch for Gch video output without a reference pulse

(Operates when PIC ON = 1, set to OFF mode at power-on.)

0 = Gch video output OFF (Blanked status, reference pulse only output)

1 = Gch video output ON

B ON

(1)

: ON/OFF switch for Bch video output without a reference pulse

(Operates when PIC ON = 1, set to OFF mode at power-on.)

0 = Bch video output OFF (Blanked status, reference pulse only output)

1 = Bch video output ON

AKB OFF

(1)

: AKB ON/OFF switch (Set to ON mode at power-on.)

0 = AKB ON

1 = AKB OFF (IK CLAMP, IK S/H and reference pulse fixed to OFF)

R, G and B cut-off adjustment at AKB OFF performed by voltage applied to RSH,

GSH and BSH pins, respectively.

YS1 OFF

(1)

: YS1 forced OFF mode/YS1 normal mode

0 = YS1 normal mode

1 = YS1 forced OFF mode

≠ 28 ≠

CXA2000Q

5. Deflection block register

AFC-MODE

(2)

: AFC loop gain control (PLL between H SYNC and H VCO)

0h = H free run mode

1h = Small gain

2h = Medium gain

3h = Large gain

FH-HI

(1)

: H oscillator frequency fixation ON/OFF switch

(Set to ON mode at power-on.)

0 = H oscillator frequency fixation OFF AFC normal mode

1 = H oscillator frequency fixation ON

Oscillator frequency fixed to maximum value

(approx. 16.2kHz).

V FREQ

(1)

: V frequency mode setting

0, 1h = Automatic identification

2h = Forced mode (50Hz)

3h = Forced mode (60Hz)

V OFF

(1)

: V sawtooth wave oscillation stop ON/OFF switch

(Set to OFF mode at power-on.)

0 = Oscillation stop OFF (V DRIVE≠ and V DRIVE+: normal output)

1 = Oscillation stop ON (V DRIVE≠ and V DRIVE+: DC output and DC value vary

according to V POSITION.)

CD-MODE

(1)

: V countdown system mode selector

(Set to automatic selection mode during power-on.)

0 = Non-standard signal mode, standard signal mode and no signal mode

automatically selected

1 = Fixed to non-standard signal mode

(V oscillator frequency is 55Hz during no signal mode "free run".)

VBLKW

(2)

: VBLK width control (Blanked pulses after reference pulse. Operates when

JMPSW = 1; blanked pulses after reference pulse fixed to 1H when JMPSW = 0.)

0h = 12H from Bch reference pulse

1h = 11H from Bch reference pulse

2h = 10H from Bch reference pulse

3h = 9H from Bch reference pulse

H-POSITION

(4)

: Horizontal position adjustment (HAFC phase control)

0h = 1µs delay

Picture position shifts to right. (Picture delayed with respect to HD.)

7h = 0µs

Fh = 1µs advance

Picture position shifts to left. (Picture advanced with respect to HD.)

V-POSITION

(6)

: Vertical position adjustment (V SAW output DC bias control)

0h = ≠0.09V Picture position drops, V DRIVE+ output DC Down.

1Fh = 0V Center potential: DC 3V

3Fh = +0.09V Picture position rises, V DRIVE+ output DC Up.

≠ 29 ≠

CXA2000Q

V-SIZE

(6)

: Vertical amplitude adjustment (V SAW output gain control)

0h = ≠14%

Vertical picture size decreases.

1Fh = 0%

Amplitude: 1.23Vp-p, center potential: DC 3V when V-ASPECT is 2FH.

3Fh = +14%

Vertical picture size increases.

V-LIN

(4)

: Vertical linearity adjustment (Gain control for V SAW secondary component)

0h = 115%

(Bottom/top of picture) Top of picture compressed; bottom of picture

expanded.

7h = 100%

(Bottom/top of picture)

Fh = 85%

(Bottom/top of picture) Top of picture expanded; bottom of picture

compressed.

S-CORR

(4)

: Vertical S correction amount adjustment (V SAW secondary component gain control)

0h = Secondary component amplitude by adding sawtooth and other signals = 0

Fh = Secondary component amplitude by adding sawtooth and other signals = Maximum

AFC-BOW

(4)

: Vertical line bow compensation amount adjustment (Phase control according to

HAFC parabola wave)

0h = Top and bottom of picture delayed 500ns with respect to picture center.

7h = 0 ns

Fh = Top and bottom of picture advanced 500ns with respect to picture center.

AFC-ANGLE

(4)

: Vertical line slope compensation amount adjustment (Phase control according to

HAFC V SAW)

0h = Top of picture delayed 500ns, bottom of picture advanced 500ns with respect to

picture center.

7h = 0 ns

Fh = Top of picture advanced 500ns, bottom of picture delayed 500ns with respect to

picture center.

PIN-COMP

(6)

: Horizontal pin distortion compensation amount adjustment (V parabola wave gain

control)

0h = 0.10Vp-p Horizontal size for top/bottom of picture increases. (Compensation

amount minimum)

1Fh = 0.58Vp-p Amplitude, center potential: DC 4V when V-ASPECT is 2Fh

3Fh = 1.06Vp-p Horizontal size for top/bottom of picture decreases. (Compensation

amount maximum)

H-SIZE

(6)

: Horizontal amplitude adjustment (V parabola wave DC bias control)

0h = ≠0.5V

Horizontal picture size decreases, EW-DRIVE output DC Down.

1Fh = 0V

Amplitude: 0.58Vp-p, center potential: DC 4 V when V-ASPECT is 2Fh

3Fh = +0.5V

Horizontal picture size increases, EW-DRIVE output DC Up.

EHT-H

(2)

: Horizontal high-voltage fluctuation compensation amount setting (DC adjustment for

parabolic output)

0h = 0V (Compensation amount when 1V is applied to ABL IN versus 8V applied

to ABL IN)

3h = ≠0.1V (Compensation amount when 1V is applied to ABL IN versus 8V applied

to ABL IN)

EHT-V

(2)

: Vertical high-voltage fluctuation compensation amount setting (V SAW output gain control)

0h = 0% (Compensation amount when 1V is applied to ABL IN versus 8V applied to

ABL IN)

3h = ≠7% (Compensation amount when 1V is applied to ABL IN versus 8V applied to

ABL IN)

INTERLACE

(1)

: Interlace mode and non-interlace display selector switch

0,1h = Interlace mode

2h = Interlace mode; 1/2H shift applied to EVEN lines

3h = Interlace mode; 1/2H shift applied to ODD lines

≠ 30 ≠

CXA2000Q

PIN-PHASE

(4)

: Horizontal trapezoidal distortion compensation amount adjustment (V parabola wave

center timing control)

0h = 1.5ms advance

Horizontal size for top of picture increases; horizontal size for

bottom of picture decreases.

7h = 0ms

8.9ms from 4VDC VTIM

Fh = 1.5ms delay

Horizontal size for top of picture decreases; horizontal size

for bottom of picture increases.

CORNER-PIN (4)

: Horizontal pin distortion compensation amount adjustment for top/bottom of picture

(V parabola wave top/bottom gain control)

0h = ≠0.2V

Horizontal size for top/bottom of picture decreases.

(compensation amount maximum)

7h = 0V

(0.7Vp-p 4:3 mode)

Fh = +0.2V

Horizontal size for top/bottom of picture increases.

(compensation amount minimum)

V-ASPECT

(6)

: Aspect ratio control. (Gain control for sawtooth wave)

0h = 75%

16:9 CRT full

2Fh = 100%

4:3 CRT full, amplitude: 1.23Vp-p

3Fh = 112%

ZOOM SW

(1)

: Zoom mode ON/OFF switch for 16:9 CRT (25% of video cut)

0 = Zoom OFF

Sawtooth wave amplitude: 1.23Vp-p

1 = Zoom ON

Sawtooth wave amplitude: 70%

HBLKSW

(1)

: HBLK width control ON/OFF switch during 4:3 software full display mode on a 16:9

CRT

0 = Control OFF

HBLK pulse generated from HPIN.

1 = Control ON

HBLK pulse generated as pulse generated from HPIN or as

pulse generated from HVCO and width adjusted.

Width adjustment is performed by the LEFT-BLK and

RIGHT-BLK registers.

V-SCROLL

(6)

: Vertical picture scroll control during zoom mode on a 16:9 CRT

(DC component added to sawtooth wave AGC output to control ZOOMSW cut

timing.)

0h = ≠0.2V

Scrolled toward top of screen by 32H and top of picture zoomed.

1Fh = 0V

3Fh = +0.2V

Scrolled toward bottom of screen by 32H and bottom of picture zoomed.

JUMPSW

(1)

: Reference pulse jump mode ON/OFF switch (In addition to V-ASPECT control, sawtooth

wave gain control performed for 100% of VBLK interval and 67% of picture interval)

0 = Jump mode OFF

1 = Jump mode ON

On a 4:3 CRT, jump mode expands the sawtooth wave amplitude to 112% with V-

ASPECT; on a 16:9 CRT, jump mode compresses the sawtooth wave amplitude to

75% with V-ASPECT. The V blanking width is expanded at both the top and bottom

of the picture. Blanking for the bottom of the picture starts 251H after VTIM, and

blanking for the top of the picture can be varied as the blanking width after the

reference pulse from the VBLKW register.

HSIZESW

(1)

: Lowers the E-W OUT DC level (during H-SIZE compression)

0 = Normal

1 = ≠1.35V

≠ 31 ≠

CXA2000Q

UP-VLIN

(4)

: Vertical linearity adjustment for top of picture (Secondary component gain control for

sawtooth wave added to sawtooth wave AGC output)

0h = 100%

(Bottom/top of picture)

Fh = 115%

(Bottom/top of picture) Top of picture compressed.

LO-VLIN

(4)

: Vertical linearity adjustment for bottom of picture (Tertiary component gain control

for sawtooth wave added to sawtooth wave AGC output)

0h = 100%

(Bottom/top of picture)

Fh = 85%

(Bottom/top of picture) Bottom of picture compressed.

LEFT-BLK

(4)

: HBLK width control for the left side of picture when HBLKSW = 1 (Phase control for

timing pulse generated from HVCO)

0h = +1.3µs

HBLK width maximum

7h = 0µs

Center HBLK: 13µs

Fh = ≠1.3µs

HBLK width minimum

RIGHT-BLK

(4)

: HBLK width control for the right side of picture when HBLKSW = 1 (Phase control for

timing pulse generated from HVCO)

0h = +1.3µs

HBLK width maximum

7h = 0µs

Center HBLK: 13µs

Fh = ≠1.3µs

HBLK width minimum

SCP BGR

(2)

: Controls the phase of the rising edge of the burst pulse in sand castle pulse output

(0.4µs/step)

0h = +0.4µs

1h = Center

3h = ≠0.8µs

SCP BGF

(2)

: Controls the phase of the falling edge of the burst pulse in sand castle pulse output

(0.4µs/step)

0h = +0.4µs

1h = Center

3h = ≠0.8µs

6. Other

AGING

(1)

: White output aging mode ON/OFF switch

(Takes priority over RGB ON and PIC ON control. Set to OFF mode at power-on.)

0 = Aging mode OFF

1 = Aging mode ON (When there is no input signal, a 60 IRE flat signal is output

from the Y block)

≠ 32 ≠

CXA2000Q

7. Status register

HLOCK

(1)

: Lock status between H SYNC and H VCO

0 = HVCO free run status

1 = Locked to H SYNC

IKR

(1)

: AKB operation status

0 = REF-P at Ik small and AKB loop unstable.

1 = REF-P at Ik sufficient and AKB loop stable.

VNG

(1)

: Signal input status to V PROT pin

0 = No V PROT input

1 = V PROT input (In this case, the RGB output is blanked.)

XRAY

(1)

: Signal input status to XRAY control pin (HOFF pin)

0 = No XRAY control input

1 = XRAY control input (In this case, the RGB output is blanked.)

COLOR SYS

(3)

: Color system status

0h = --

1h = --

2h = NO STANDARD

3h = SECAM

4h = 3.58MHz NTSC

5h = 4.43MHz NTSC

6h = 3.58MHz PAL

7h = 4.43MHz PAL

CV SYNC

(1)

: CV input SYNC SEP result

When VIDEO is input to CVIN, "1" is returned when the SYNC level is 100mV or

more (standard: 300mV)

0 = No SYNC

1 = SYNC

≠ 33 ≠

CXA2000Q

Description of Operation

1. Power-on sequence

The CXA2000Q does not have an internal power-on sequence. Therefore, power-on sequence is all controlled

by the set microcomputer (I

2

C bus controller).

1) Power-on

The IC is reset and the RGB outputs are all blanked. Hdrive starts to oscillate, but oscillation is at the

maximum frequency (16kHz or more) and is not synchronized to the input signal. Output of vertical signal

VTIM starts, but Vdrive is DC output. Bus registers which are set by power-on reset are as follows.

AGING

= 0: All white output aging mode OFF

RON

= 0: Rch video blanking ON

GON

= 0: Gch video blanking ON

BON

= 0: Bch video blanking ON

PICON

= 0: RGB all blanking ON

VOFF

= 1: VDRIVE output stopped mode

VFREQ

= 0: Automatic identification mode (identification starts at 50Hz)

FHHI

= 1: H oscillator maximum frequency mode

HSIZESW

= 0: Normal

CD-MODE = 0: Automatic selection mode of the countdown mode

AKBOFF

= 0: AKB mode

2) Bus register data transfer

The register setting sequence differs according to the set sequence. Register settings for the following

sequence are shown as an example.

Set sequence

CXA2000Q register settings

Power-on

Reset status in 1) above.

Degauss

Reset status in 1) above.

The CRT is degaussed in the completely darkened condition.

VDRIVE oscillation

The IC is set to the power-on initial settings. (See the following page.)

A sawtooth wave is output to VDRIVE and the IC waits for the vertical

deflection to stabilize. The HDRIVE oscillator frequency goes to the standard

frequency.

AKB operation start

PICON is set to 1 and a reference pulse is output from Rout, Gout and Bout.

Then, the IC waits for the cathode to warm up and the beam current to start

flowing.

AKB loop stable

Status register IKR is monitored.

IKR = 0: No cathode current

IKR = 1: Cathode current

Note that the time until IKR returns to 1 differs according to the initial status

of the cathode.

Video output

RON, GON and BON are set to 1 and the video signal is output from Rout,

Gout and Bout.

≠ 34 ≠

CXA2000Q

0

1

0

1

1

0

0

0

1

0

0

0

1

0

0

1

1

0

1

0

1

1

1

1

Bit0

Bit1

Bit2

Bit3

Bit4

Bit5

Bit6

Bit7

Sub Address

◊ ◊ ◊

0 0 0 0 0 00 h

◊ ◊ ◊

0 0 0 0 1 01 h

◊ ◊ ◊

0 0 0 1 0 02 h

◊ ◊ ◊

0 0 0 1 1 03 h

◊ ◊ ◊

0 0 1 0 0 04 h

◊ ◊ ◊

0 0 1 0 1 05 h

◊ ◊ ◊

0 0 1 1 0 06 h

◊ ◊ ◊

0 0 1 1 1 07 h

◊ ◊ ◊

0 1 0 0 0 08 h

◊ ◊ ◊

0 1 0 0 1 09 h

◊ ◊ ◊

0 1 0 1 0 0A h

◊ ◊ ◊

0 1 0 1 1 0B h

◊ ◊ ◊

0 1 1 0 0 0C h

◊ ◊ ◊

0 1 1 0 1 0D h

◊ ◊ ◊

0 1 1 1 0 0E h

◊ ◊ ◊

0 1 1 1 1 0F h

◊ ◊ ◊

1 0 0 0 0 10 h

◊ ◊ ◊

1 0 0 0 1 11 h

◊ ◊ ◊

1 0 0 1 0 12 h

◊ ◊ ◊

1 0 0 1 1 13 h

◊ ◊ ◊

1 0 1 0 0 14 h

◊ ◊ ◊

1 0 1 0 1 15 h

◊ ◊ ◊

1 0 1 1 0 16 h

◊ ◊ ◊

1 0 1 1 1 17 h

◊ ◊ ◊

1 1 0 0 0 18 h

◊ ◊ ◊

1 1 0 0 1 19 h

1

1

1

1

1

1

1

1

1

1

1

0

1

1

1

1

1

1

1

1

0

1

1

1

0

1

1

1

1

1

1

1

1

1

1

1

0

1

1

1

1

1

1

1

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

1

1

1

1

1

1

1

1

0

1

1

1

1

1

1

1

1

0

0

0

1

1

1

0

0

1

1

0

1

1

0

0

0

0

1

0

1

0

0

1

1

1

1

0

1

1

1

1

1

1

0

1

1

1

1

1

1

1

0

0

1

1

1

1

0

0

0

0

1

0

1

1

0

0

0

1

0

0

1

1

0

0

1

1

0

1

0

1

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

I

2

C bus power-on initial settings

The initial settings listed here for power-on when VDRIVE starts to oscillate are reference values; the actual

settings may be determined as needed according to the conditions under which the set is to be used.

Register Table

"

" Undefined

Control Register

≠ 35 ≠

CXA2000Q

3) Power-on initial settings

The initial settings listed here for power-on when VDRIVE starts to oscillate are reference values; the actual

settings may be determined as needed according to the conditions under which the set is to be used.

PICTURE

= 3Fh

Max (User Control)

TRAP OFF

= 0

Chroma Trap ON

VM OFF

= 0

VM out ON

HUE

= 1Fh

Center (User Control)

DC-TRAN

= 0

Y DC transmission ratio 100%

D-PIC

= 1

Y black expansion ON

COLOR

= 1Fh

Center (User Control)

TOT

= 0

Chroma low frequency increased

BRIGHT

= 1Fh

Center (User Control)

D-COL

= 1

Dynamic Color ON

SHARPNESS = 7h

Center (User Control)

PRE-OVER

= 0

Sharpness pre/over ratio 1:1

COLOR SW

= 0

AUTO

SUB-CONT

= 7h

Center (Adjust)

TRAP F0

= 7h

Center (Adjust)

SUB-COLOR = 7h

Center (Adjust)

SUB-HUE

= 7h

Center (Adjust)

SUB-BRIGHT = 1Fh

Center (Adjust)

GAMMA

= 0

Gamma OFF

G-DRIVE

= 1Fh

Center (Adjust)

AGING

= 0

Aging Mode OFF

B-DRIVE

= 1Fh

Center (Adjust)

INTERLACE

= 0

INTERLACE mode

G-CUTOFF

= 7h

Center (Adjust)

B-CUTOFF

= 7h

Center (Adjust)

RON

= 0

Rch video output OFF

GON

= 0

Gch video output OFF

BON

= 0

Bch video output OFF

PICON

= 0

RGB all blanked

VOFF

= 0

Vdrive oscillation

FHHI

= 0

Horizontal oscillator frequency standard

CD-MODE

= 0

V countdown auto mode

AKBOFF

= 0

AKB ON

V-SIZE

= 1Fh

Center (Adjust)

V-FREQ

= 0

AUTO

V-POSITION

= 1Fh

Center (Adjust)

AFC-MODE

= 2

Center

S-CORR

= 7h

Center (Adjust)

V-LIN

= 7h

Center (Adjust)

H-SIZE

= 1Fh

Center (Adjust)

REF-POSI

= 0

PIN-COMP

= 1Fh

Center (Adjust)

VBLKW

= 0

≠ 36 ≠

CXA2000Q

(Power-on initial settings cont.)

H-POSITION

= 7h

Center (Adjust)

PIN-PHASE

= 7h

Center (Adjust)

AFC-BOW

= 7h

Center (Adjust)

AFC-ANGLE

= 7h

Center (Adjust)

SCP BGR

= 1

Center

SCP BGF

= 1

Center

XTAL

= 0

AUTO

EXT SYNC

= 0

Internal SYNC

CV/YC

= 0

CV input

V-ASPECT

= 0h

16:9 CRT Full Mode

ZOOMSW

= 1

16:9 CRT

HBLKSW

= 1

Hblk width adjust ON

V-SCROLL

= 1Fh

Center (User Control)

JMPSW

= 0

16:9 CRT Full Mode

HSIZE SW

= 0

Normal

UP-VLIN

= 7h

16:9 CRT Full Mode

LO-VLIN

= 7h

16:9 CRT Full Mode

LEFT-BLK

= Fh

Hblk width Min.

RIGHT-BLK

= Fh

Hblk width Min.

EHT-H

= 0

Hdrive high-voltage compensation OFF

EHT-V

= 3

Vdrive high-voltage compensation amount maximum

CORNERPIN = 7h

Center (Adjust)

YS1 OFF

= 0

Normal

DL

= 3

Normal (Adjust)

2. Various mode settings

The CXA2000Q contains bus registers for deflection compensation which can be set for various wide modes.

Wide mode setting registers can be used separately from registers for normal picture distortion adjustment,

and once deflection adjustment has been performed in full mode, wide mode settings can be made simply by

changing the corresponding register data.

∑ VDRIVE signal picture distortion adjustment registers

V-SIZE, V-POSITION, S-CORR, V-LIN

∑ E/WDRIVE signal picture distortion adjustment registers

H-SIZE, PIN-COMP, PIN-PHASE, CORNER-PIN

∑ Wide mode setting registers

V-ASPECT, ZOOMSW, HBLKSW, V-SCROLL, JMPSW, HSIZESW, UP-VLIN, LO-VLIN,

LEFT-BLK, RIGHT-BLK

≠ 37 ≠

CXA2000Q

Examples of various modes are listed below. These modes are described using 570 (NTSC: 480) lines as the

essential number of display scanning lines. Wide mode setting register data is also listed, but settings may

differ slightly due to IC variation. The standard setting data differs for 16:9 CRTs and 4:3 CRTs.

Register 16:9 CRT 4:3 CRT

V-ASPECT

0h

2Fh

V-SCROLL

1Fh

1Fh

ZOOMSW

1

0

UP-VLIN

0h

0h

LO-VLIN

0h

0h

JMPSW

0

0

HSIZESW

0

0

HBLKSW

0

0

LEFT-BLK

7h

7

RIGHT-BLK

7h

7h

1) 16:9 CRT full mode

This mode reproduces the full 570 (NTSC:480) lines on a 16:9 CRT. 4:3 images are reproduced by stretching

the picture to the left and right.

Normal images are compressed vertically, but 16:9 images can be reproduced in their original 16:9 aspect

ratio with a video source which compresses (squeezes) 16:9 images to 4:3 images. The register settings are

the 16:9 CRT standard values.

2) 16:9 CRT normal mode

In this mode, 4:3 images are reproduced without modification. A black border appears at the left and right of

the picture. In this mode, the H deflection size must be compressed by 25% compared to full mode. The

CXA2000Q permits compression with a register (HSIZESW) that compresses the H size by 25%. Because

excessive current flows to the horizontal deflection coil in this case, adequate consideration must be given to

the allowable power dissipation, etc., of the horizontal deflection coil in the design of the set. In addition, this

concern can also be addressed through measures taken external to the IC, such as by switching the horizontal

deflection coil. Full mode should be used when using memory processing to add a black border to the video

signal.

H blanking of the image normally uses the flyback pulse input to AFCPIN (Pin 38). However, the blanking

width can be varied according to the control register setting when blanking is insufficient for the right and left

black borders.

The following three settings are added to the 16:9 CRT standard values for the register settings.

HBLKSW = 1

LEFT-BLK = Adjustment value

RIGHT-BLK = Adjustment value

The H angle of deflection also decreases, causing it to differ from the PIN compensation amount during H size

full status. Therefore, in addition to the wide mode registers, PIN-COMP must also be readjusted only for this

mode.

3) 16:9 CRT zoom mode

In this mode, 4:3 images are reproduced by enlarging the picture without other modification. The top and

bottom of normal 4:3 images are lost, but almost the entire picture can be reproduced for vista size video

software, etc. which already has black borders at the top and bottom. The enlargement ratio can be controlled

by the V-ASPECT register, and enlarging the picture by 33% compared to full mode allows zooming to be

performed for 4:3 images without distortion. In this case, the number of scanning lines is reduced to 430 lines

compared to 570 lines for full mode. The zooming position can be shifted vertically by the V-SCROLL register.

V blanking of the image normally begins from V sync and continues for 2H after the AKB reference pulse, and

the top and bottom parts are also blanked during this mode.

Adjust the following two registers with respect to the 16:9 CRT standard values for the register settings.

V-ASPECT = 2Fh

V-SCROLL = 1Fh or user control

≠ 38 ≠

CXA2000Q

4) 16:9 CRT subtitle-in mode

When CinemaScope size images which have black borders at the top and bottom of the picture are merely

enlarged with the zoom mode in 3) above, subtitles present in the black borders may be lost. Therefore, this

mode is used to super-compress only the subtitle part and reproduce it on the display.

Add the LO-VLIN adjustment to the zoom mode settings for the register settings.

V-ASPECT = 2Fh

V-SCROLL = 1Fh or user control

LO-VLIN = Adjustment value

The LO-VLIN register causes only the linearity at the bottom of the picture to deteriorate. Therefore, UP-VLIN

should also be adjusted if the top and bottom of the picture are to be made symmetrical. Since the picture is

compressed vertically, the number of scanning lines exceeds 430 lines.

5) 16:9 CRT V compression mode

This mode is used to reproduce two 4:3 video displays such as for PandP. The V size must be compressed to

67% in order to reproduce two displays on a 16:9 CRT without distortion using 480 scanning lines, and this can

be set by JMPSW. Compression is performed after the AKB reference pulse, so the reference pulse remains in

the overscan position. The V blanking width after the reference pulse becomes larger than normal and can be

varied by the VBLKW register. During this mode, the bottom V blanking width is also expanded to 3H wider

than normal so that the bottom of the picture is not overscanned.

16:9 CRT standard values are used with only the JMPSW setting changed for the register settings.

JMPSW = 1

6) 16:9 CRT wide zoom mode

This mode reproduces 4:3 video software naturally on wide displays by enlarging 4:3 images without other

modification and compressing the parts of the image which protrude from the picture into the top and bottom

parts of the picture. The display enlargement ratio is controlled by V-ASPECT, and the compression ratios at

the top and bottom of the picture are controlled by UP-VLIN and LO-VLIN.

Adjust the following three registers with respect to the 16:9 CRT standard values for the register settings.

V-ASPECT = Adjustment value

UP-VLIN = Adjustment value

LO-VLIN = Adjustment value

7) 4:3 CRT normal mode

This is the standard mode for 4:3 CRTs.

The register settings are the 4:3 CRT standard values.

8) 4:3 CRT V compression mode

This mode is used to reproduce M-N converter output consisting of 16:9 images expanded to a 4:3 aspect ratio

and other squeezed signals without distortion on a 4:3 CRT. The V size must be compressed to 75% in order

to reproduce a 4:3 squeezed signal at a 16:9 aspect ratio without any distortion. Compressing the V size with

the JMPSW register used in mode 5) above, compresses the V size to 67%. Therefore, V-ASPECT is set to

enlarge the V size by 8%. AKB reference pulse handling and V blanking are the same as for mode 5) above.

4:3 CRT standard values are used with the V-ASPECT and JMPSW settings changed for the register settings.

V-ASPECT = 3Fh

JMPSW = 1

≠ 39 ≠

CXA2000Q

Mode Settings

1)-1

1)-2

2)

3)

4)

5)

6)

7)

8)

16:9

16:9

16:9

16:9

16:9

16:9

16:9

4:3

4:3

16:9

4:3

4:3

4:3

4:3

(16:9

+ subtitle

area)

4:3

4:3

4:3

16:9

16:9 CRT full

Wide full

16:9 CRT normal

16:9 CRT zoom

16:9 CRT with

subtitle area on

16:9 CRT V

compression

16:9 CRT wide

zoom

4:3 CRT normal

4:3 CRT V

compression

V-ASPECT = 0h: V size 75%

V-ASPECT = 0h: V size 75%

V-ASPECT = 0h: V size 75%

HBLKSW

= 1h: HBLK width adjustment ON

LEFT-BLK

= Adjustable

RIGHT-BLK = Adjustable

PIN-COMP = Adjustable

(External support: H-DY H amplitude 75%)

V-ASPECT = 2Fh: V size 100%

ZOOMSW

= 1h: Zoom ON

V size limited at 75%