| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: CXD2463 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Timing Controller for CCD Camera

Description

The CXD2463R generates the sync signals for

timing control and back end signal processing in a

CCD camera system using a 510H or 760H black-

and-white CCD image sensor.

Features

∑ Built-in sync signal generation function

∑ Built-in electronic iris (electronic shutter) function

∑ Supports low-speed limiter for electronic iris

∑ Supports external synchronization

(Line-Lock, VReset + HPLL)

∑ Supports automatic external sync discrimination

∑ Window pulse output for backlight compensation

∑ Built-in V driver

Applications

∑ Surveillance camera

∑ Door phone camera

Structure

Silicon gate CMOS IC

Applicable CCD Image Sensors

∑ Type 1/2, 760H black-and-white CCD (EIA/CCIR)

∑ Type 1/3, 510/760H black-and-white CCD (EIA/CCIR)

∑ Type 1/4, 510/760H black-and-white CCD (EIA/CCIR)

Absolute Maximum Ratings

∑ Supply voltage

V

DD

, AV

DD

V

SS

≠ 0.5 to V

SS

+ 7.0

V

∑ Supply voltage

V

SS

VL ≠ 0.5 to VL + 26.0

V

∑ Supply voltage

VH

VL ≠ 0.5 to VL + 26.0

V

∑ Supply voltage

VM

VL ≠ 0.5 to VL + 26.0

V

∑ Input voltage

V

I

V

SS

≠ 0.5 to V

DD

+ 0.5

V

∑ Output voltage

V

O

V

SS

≠ 0.5 to V

DD

+ 0.5

V

∑ Operating temperature

Topr

≠20 to +75

∞C

∑ Storage temperature

Tstg

≠55 to +150

∞C

Recommended Operating Conditions

∑ Supply voltage 1 V

DD

, AV

DD

4.75 to 5.25

V

∑ Supply voltage 3 VH

14.55 to 15.45

V

∑ Supply voltage 4 VL

≠9.0 to ≠8.0

V

∑ Supply voltage 5 VM

0

V

∑ Operating temperature

Topr

≠20 to +75

∞C

Base oscillation

∑ 1212f

H

(EIA: 19.0699MHz)

(CCIR: 18.9375MHz)

∑ 1820f

H

(EIA: 28.6364MHz)

∑ 1816f

H

(CCIR: 28.375MHz)

≠ 1 ≠

E98930B9X

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

CXD2463R

48 pin LQFP (Plastic)

≠ 2 ≠

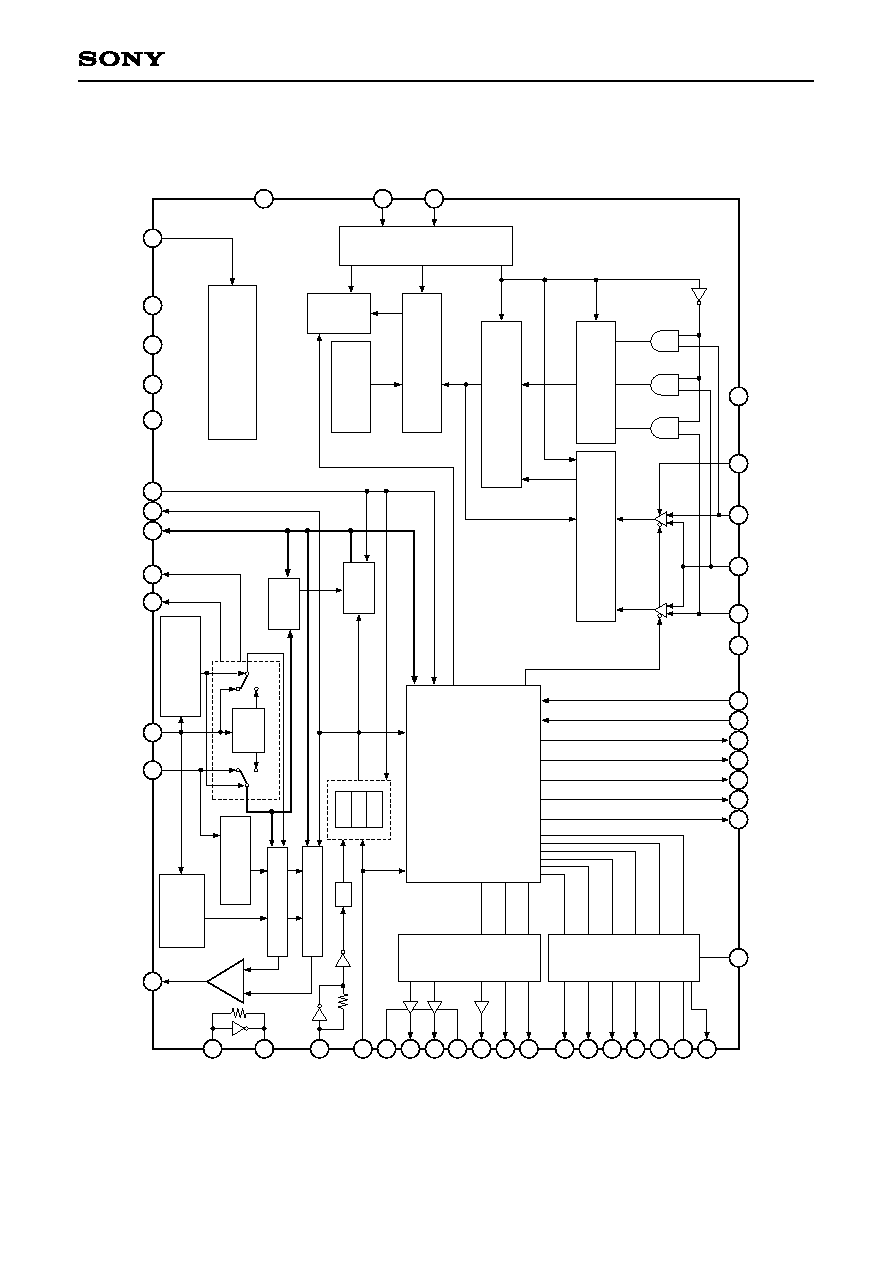

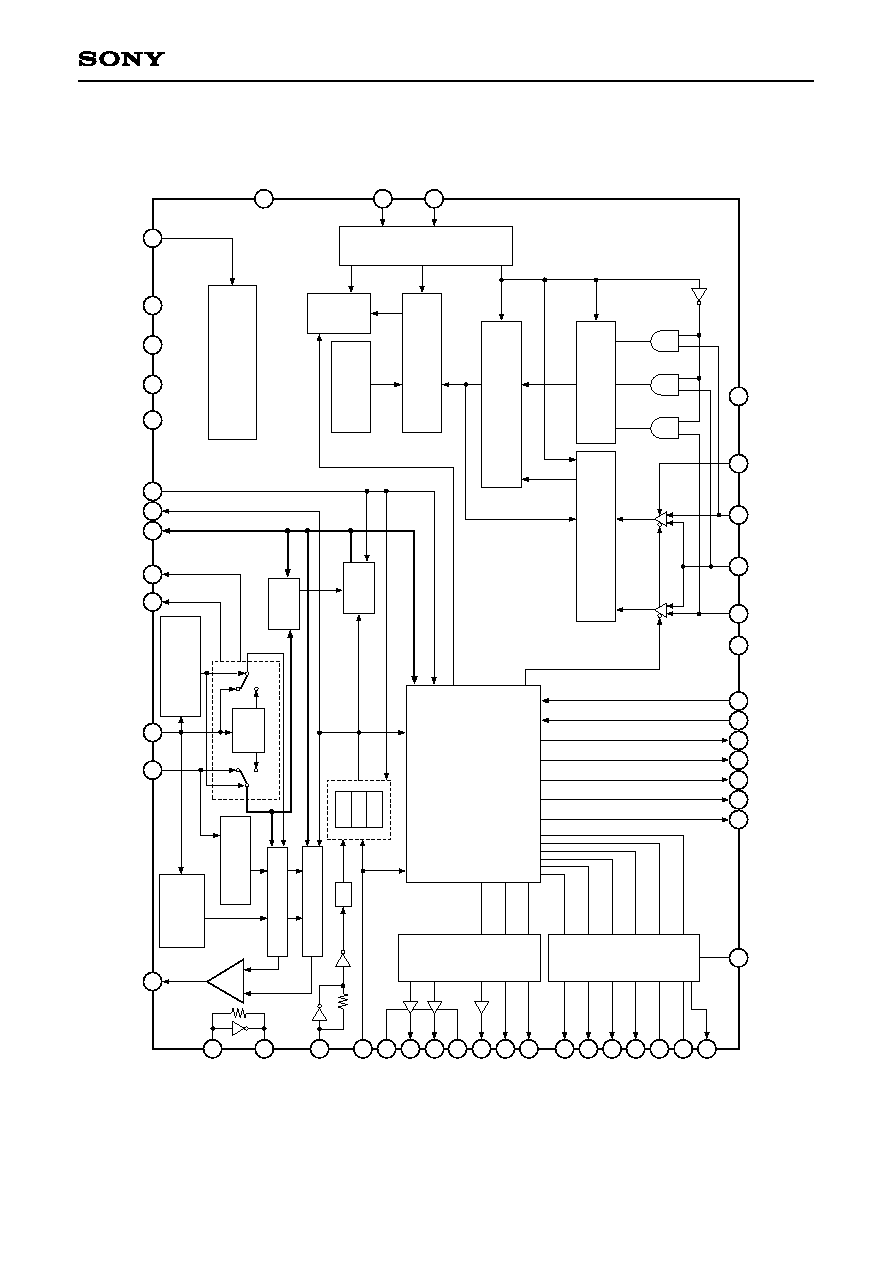

CXD2463R

NO SIGNAL

DETECTION

CIRCUIT

VD DETECTION

CIRCUIT

SYNC

DISCRIMINA

TION

CIRCUIT

GA

TE

HV

-PLL

SELECT

OR

LCIN

COMP

EVD

EHD/SYNC

EXT

HVDET

VD

HD

EIA

V

DD

1

V

DD

2

V

SS

1

V

SS

2

TEST

LCOUT

CKI

CCD

AV

SS

H1

H2

AV

DD

RG

SHP

SHD

V1

V2

V3

V4

VL

VM

SUB

VH

SYNC

CBLK

CLP1

CLP2

BLC

BLCW2

BLCW1

CV

SS

IRIN/ED1

SPDNV/ED2

Vreg

CV

DD

SPUPV/ED0

1/2

1/606

1/910

1/908

TG/SSG

RESET

GEN

IRIS/SHUTTER

CK GEN

COUNTER

ESHUT2

ESHUT1

RST

TEST

CIRCUIT

SELECT

OR

DECODE

UP/DOWN ADDER

GA

TE

VD

IHD

IVD

EIA

HD

40

39

41

42

28

47

45

46

44

48

31

30

6

3

4

2

8

1

7

5

25

26

23

24

15

17

18

12

13

11

10

9

20

21

29

22

32

16

43

19

27

36

35

33

34

38

37

14

1/525

1/625

SYNC

SEP

V DRIVER

DECODER

HV

-PLL

SELECT

OR

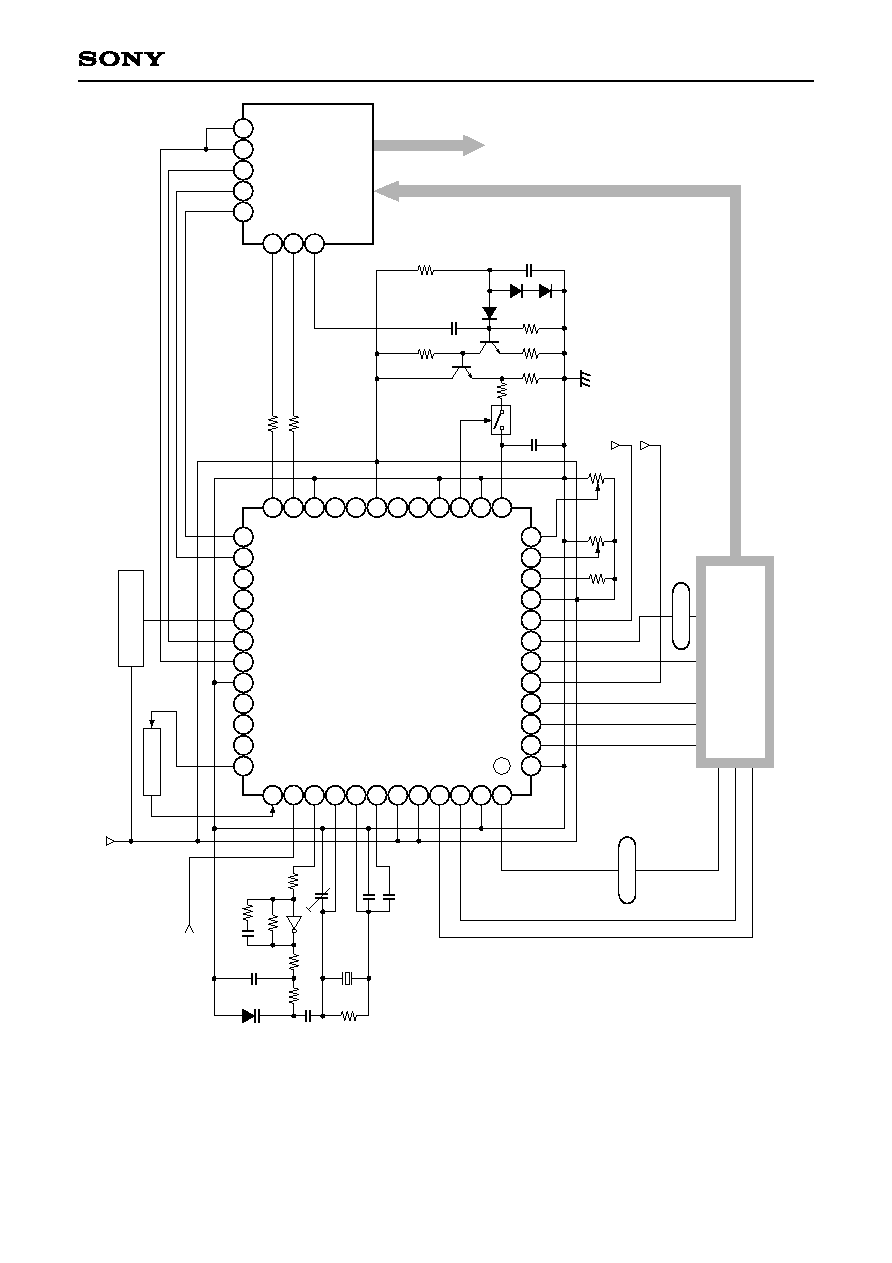

Block Diagram

≠ 3 ≠

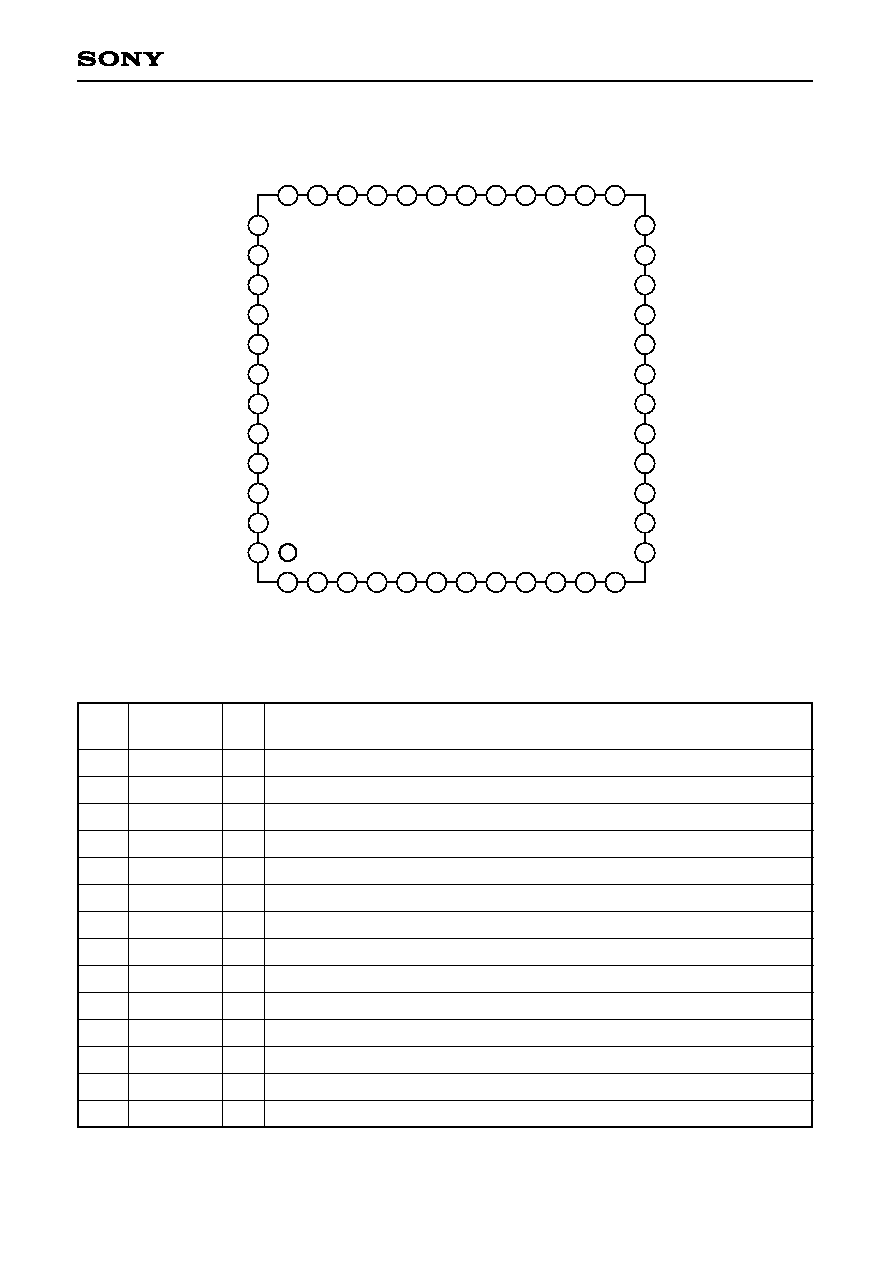

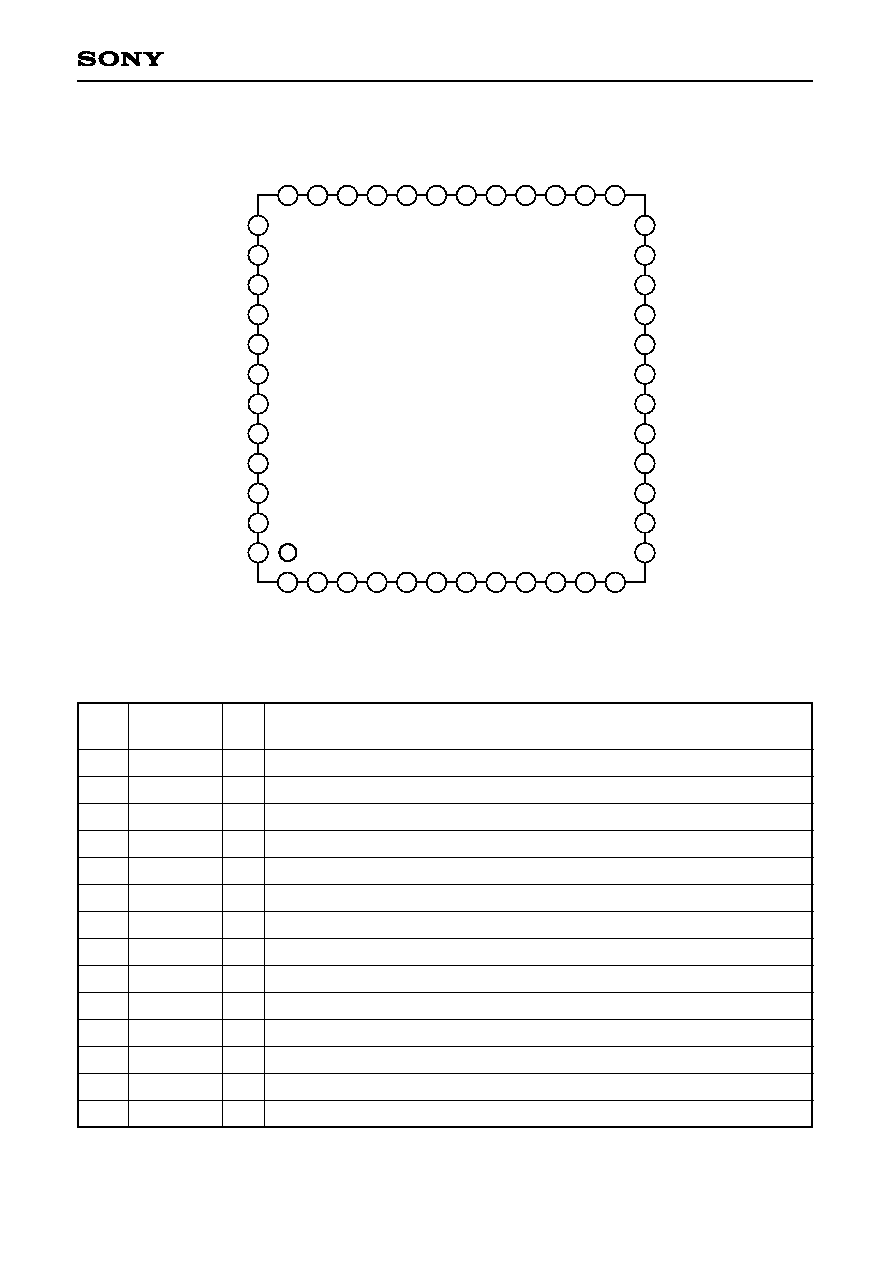

CXD2463R

Pin Configuration (Top View)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

IRIN/ED1

CV

SS

BLC

V

SS

1

BLCW1

BLCW2

V

DD

1

ESHUT2

ESHUT1

TEST

CLP1

CLP2

S

Y

N

C

C

B

L

K

E

I

A

C

C

D

R

S

T

S

H

D

S

H

P

V

S

S

2

H

V

D

E

T

E

X

T

V

D

H

D

S

P

D

N

V

/

E

D

2

S

P

U

P

V

/

E

D

0

V

r

e

g

C

V

D

D

V

L

S

U

B

V

1

V

H

V

3

V

2

V

4

V

M

RG

AV

SS

H2

H1

AV

DD

V

DD

2

CKI

LCOUT

LCIN

COMP

EHD/SYNC

EVD

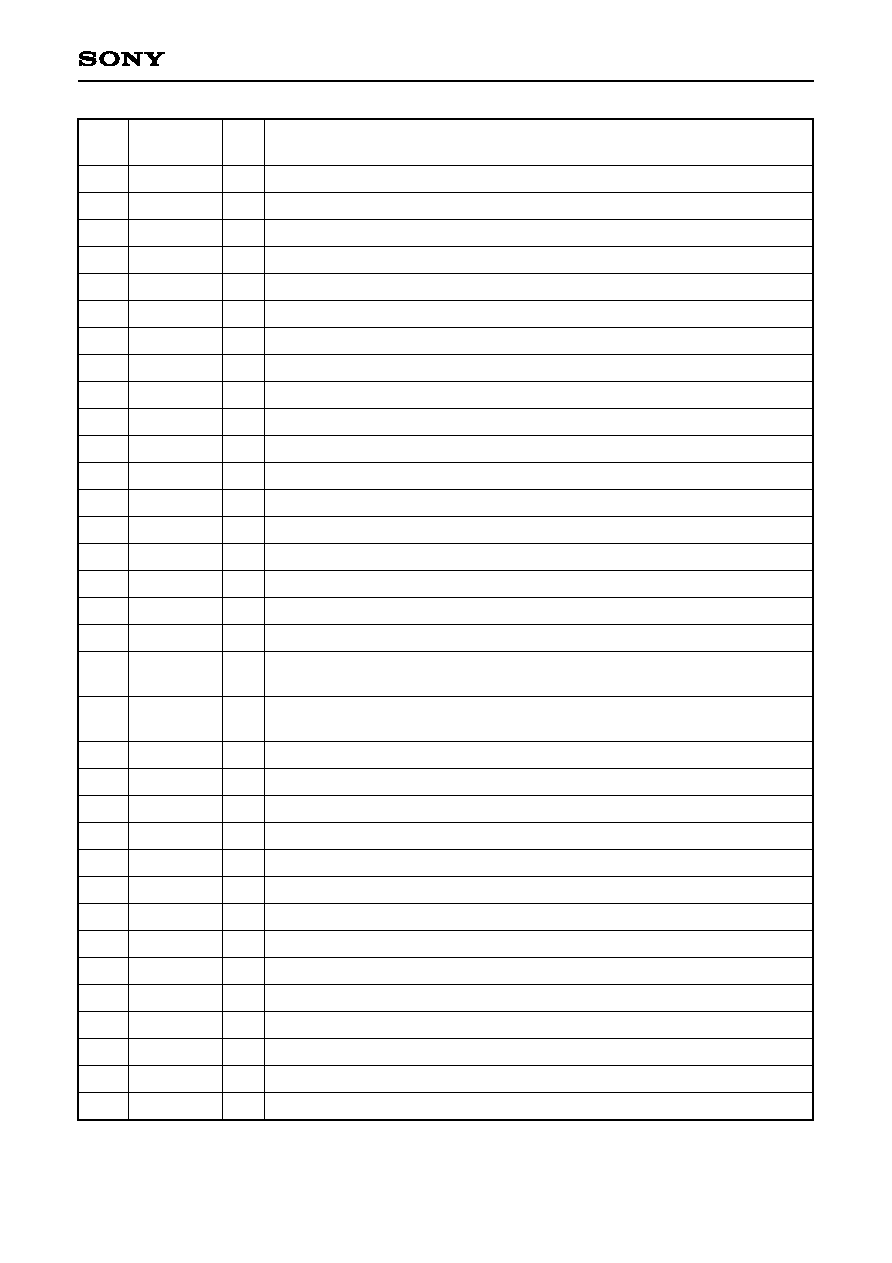

Pin Description

Pin

No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

VM

V4

V2

V3

VH

V1

SUB

VL

CV

DD

Vreg

SPUPV/ED0

SPDNV/ED2

IRIN/ED1

CV

SS

--

O

O

O

--

O

O

--

--

--

I

I

I

--

Power supply (GND for V driver)

Pulse output for CCD vertical register drive

Pulse output for CCD vertical register drive

Pulse output for CCD vertical register drive

Power supply (positive power supply for V driver)

Pulse output for CCD vertical register drive

CCD discharge pulse output

Power supply (negative power supply for V driver)

Power supply (for comparator)

Bias current supply for comparator

Shutter speed up reference voltage/shutter speed setting

Shutter speed down reference voltage/shutter speed setting

Iris signal input/shutter speed setting

GND (for comparator)

Symbol

I/O

Description

≠ 4 ≠

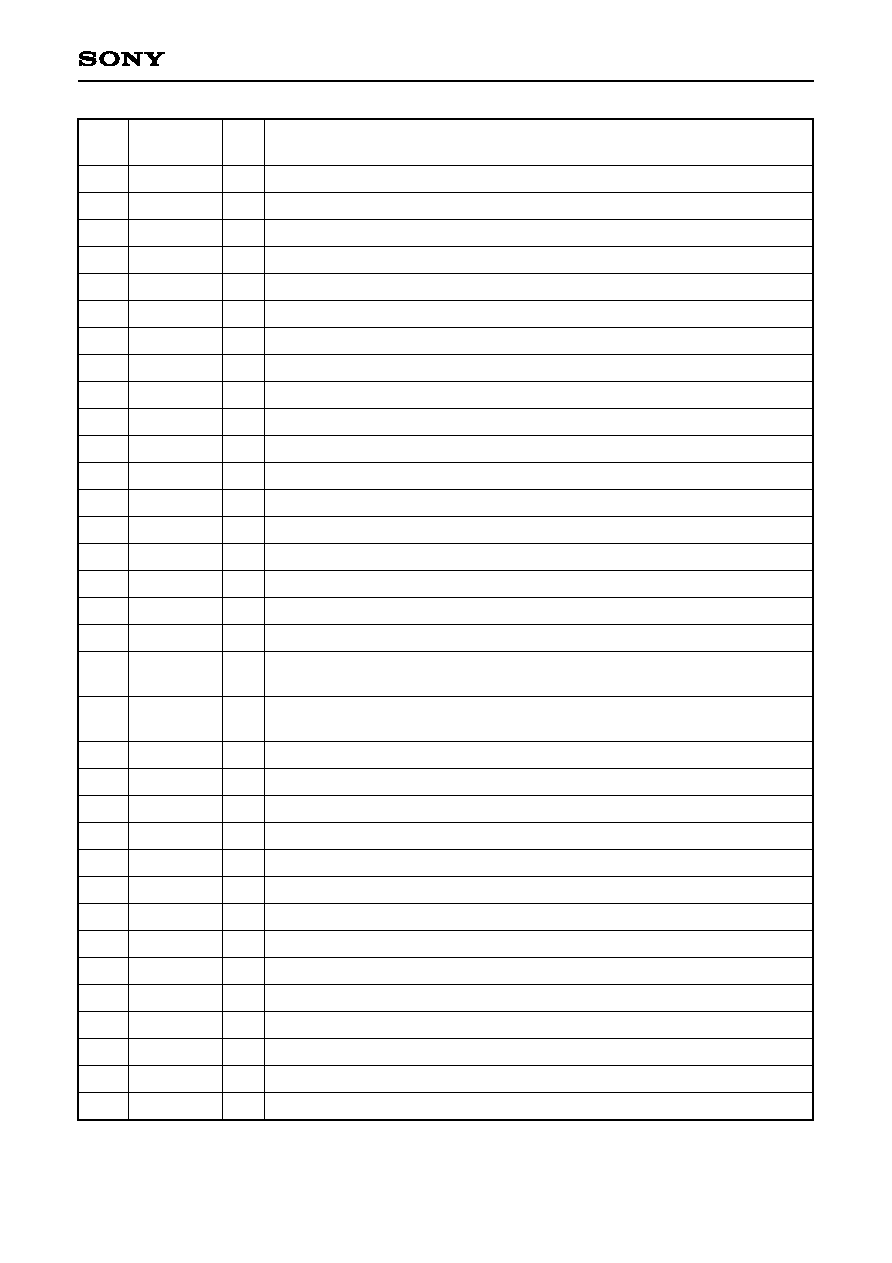

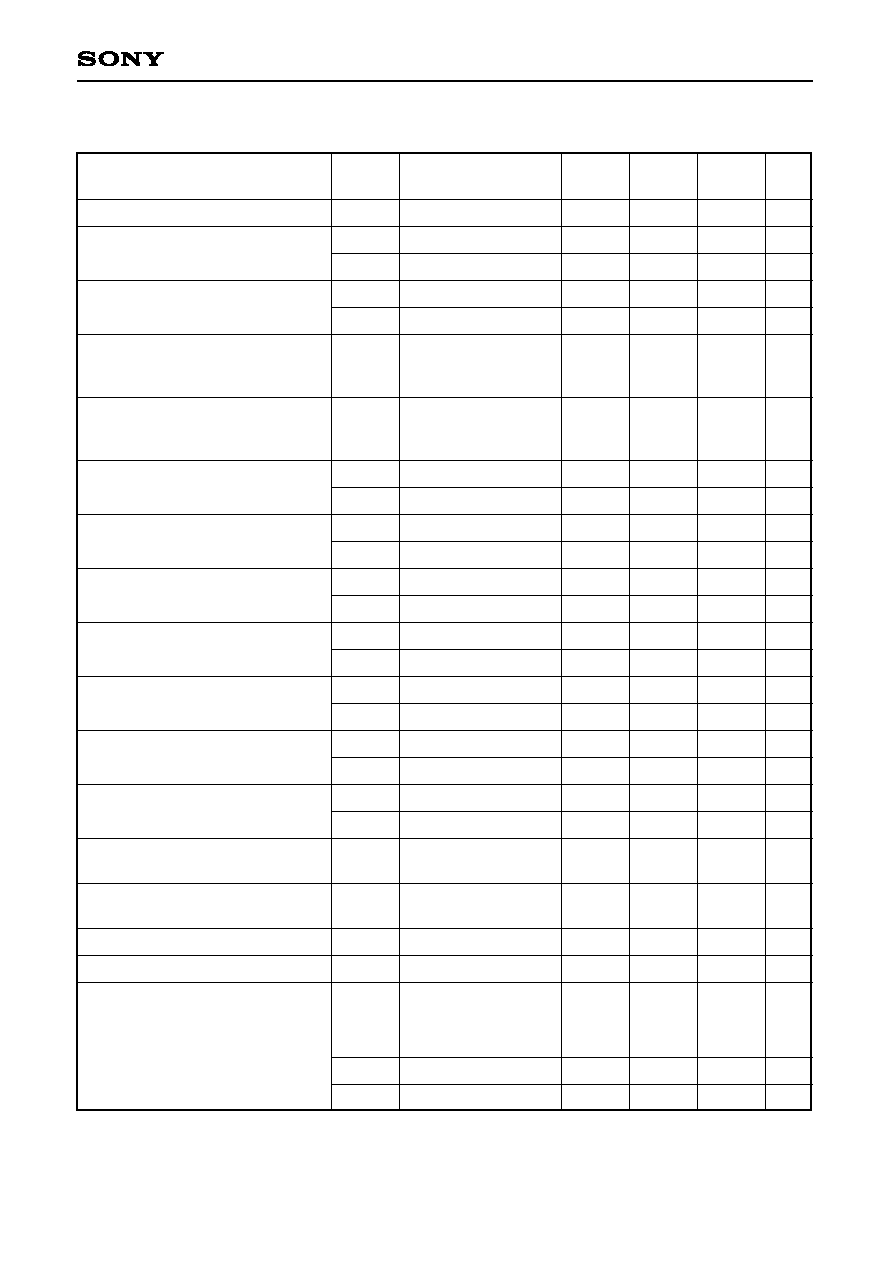

CXD2463R

Pin

No.

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

BLC

V

SS

1

BLCW1

BLCW2

V

DD

1

ESHUT2

ESHUT1

TEST

CLP1

CLP2

SYNC

CBLK

EIA

CCD

RST

SHD

SHP

V

SS

2

HVDET

EXT

VD

HD

EVD

EHD/SYNC

COMP

LCIN

LCOUT

CKI

V

DD

2

AV

DD

H1

H2

AV

SS

RG

O

--

I

I

--

I

I

I

O

O

O

O

I

I

I

O

O

--

O

O

O

O

I

I

O

I

O

I

--

--

O

O

--

O

Window pulse output for backlight compensation

GND

Window select 1 for backlight compensation (with pull-down resistor)

Window select 2 for backlight compensation (with pull-down resistor)

Power supply

Sub pulse control (with pull-down resistor)

Sub pulse control (with pull-down resistor)

Fixed low (with pull-down resistor)

Clamp pulse output

Clamp pulse output

Composite sync output

Composite blanking output

Low: EIA, High: CCIR (with pull-down resistor)

Low: 510H, High: 760H (with pull-down resistor)

Reset (low reset). Always input reset pulse after power-on.

Data sample-and-hold pulse

Precharge level sample-and-hold pulse

GND

Horizontal PLL/Vertical PLL discrimination signal

High: Vertical PLL, Low: Horizontal PLL

External sync/internal sync discrimination signal

High: External sync, Low: Internal sync

Vertical drive output

Horizontal drive output

Vertical drive signal input (with pull-up resistor)

Horizontal drive signal input/Composite sync input (with pull-up resistor)

Comparator output

Inverter input for oscillation

Inverter output for oscillation

2MCK input

Power supply

Power supply (for H1, H2, and RG)

H1 clock output for CCD horizontal register drive

H2 clock output for CCD horizontal register drive

GND (for H1, H2, and RG)

Reset gate pulse output

Symbol

I/O

Description

≠ 5 ≠

CXD2463R

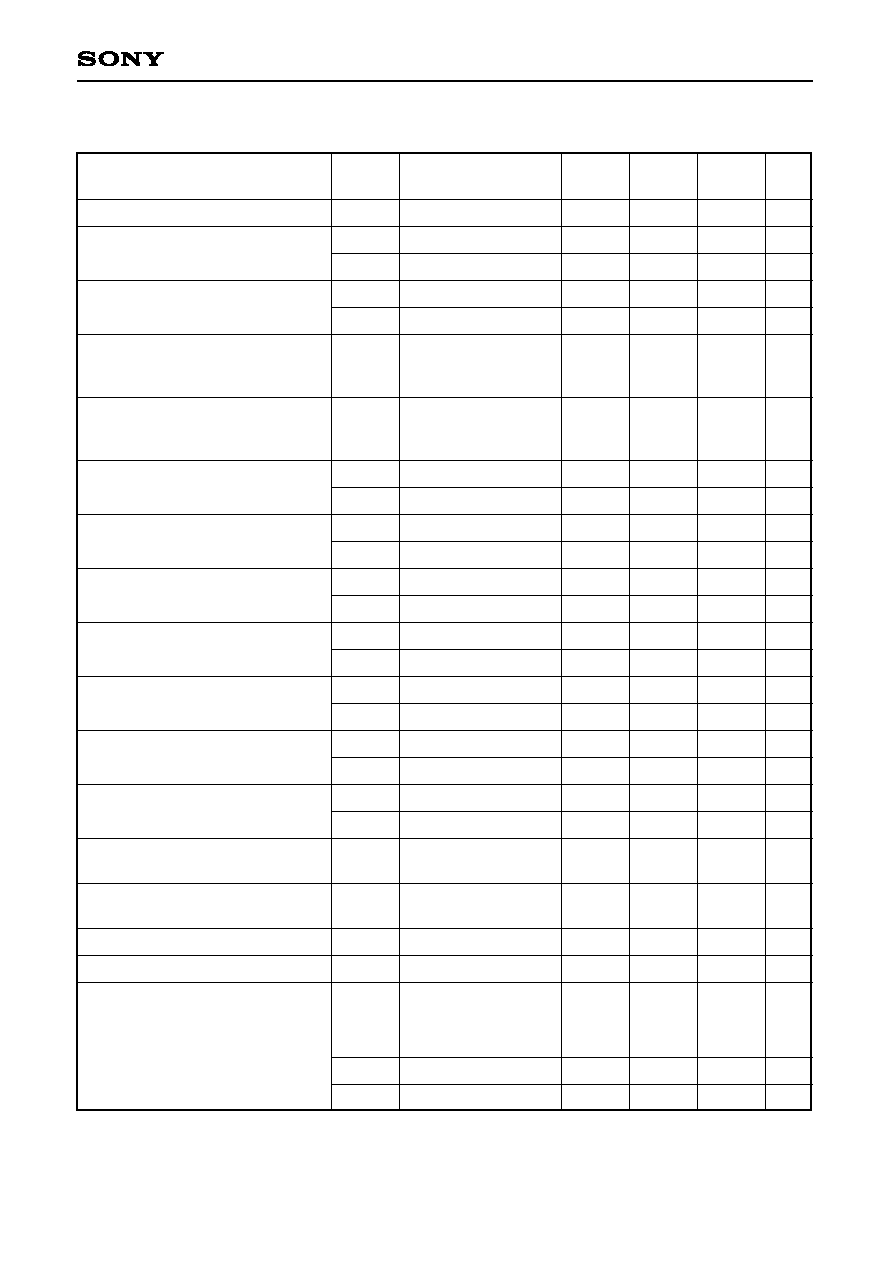

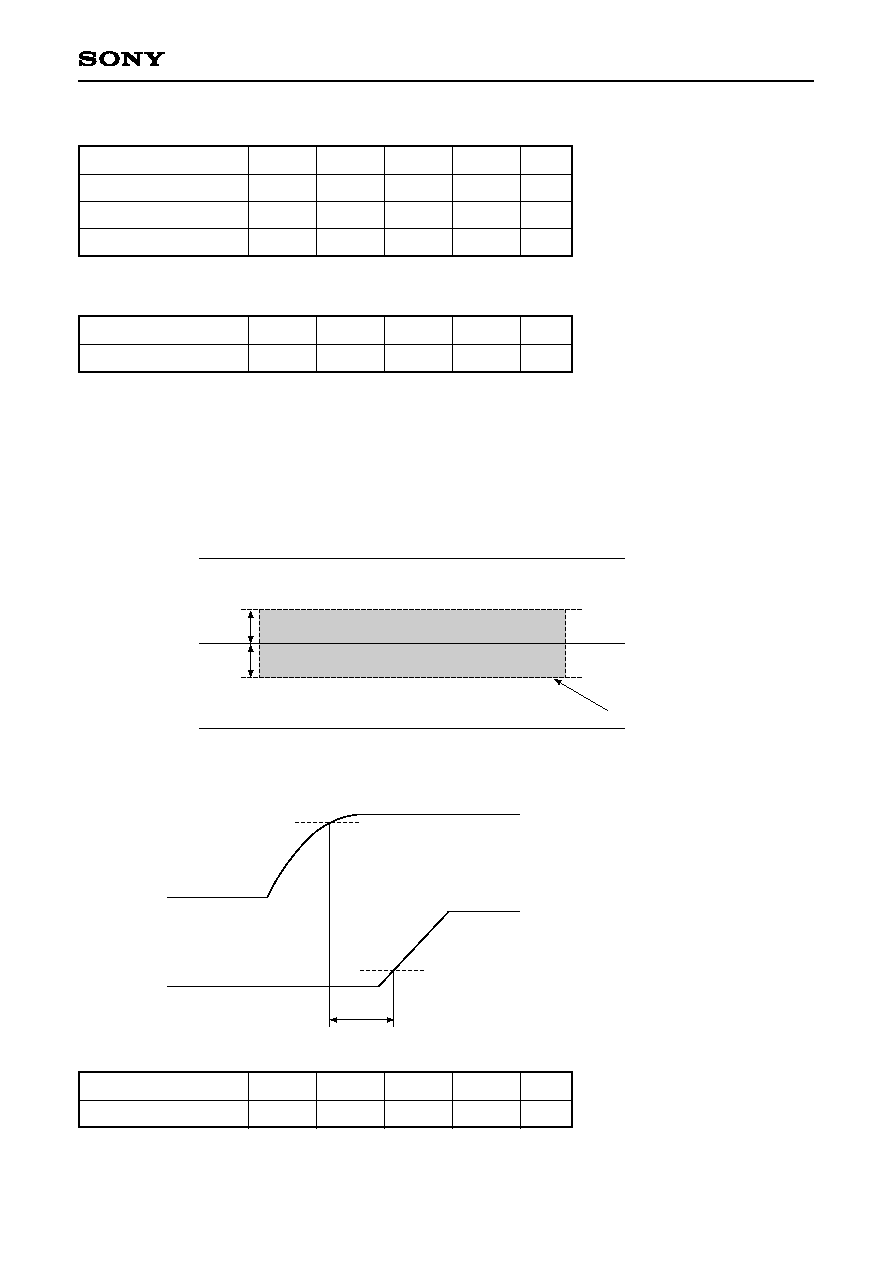

Electrical Characteristics

1) DC Characteristics

(V

DD

= 5V ± 0.25V, Topr = ≠20 to +75∞C)

Item

V

DD

V

IH

1

V

IL

1

V

IH

2

V

IL

2

V

IN

3

V

IN

4

V

OH

1

V

OL

1

V

OH

2

V

OL

2

V

OH

3

V

OL

3

V

OH

4

V

OL

4

V

OH

5

V

OL

5

V

OH

6

V

OL

6

V

OH

7

V

OL

7

R

FE

1

R

FE

2

R

PU

R

RD

I

VM

I

VL

I

VH

I

OH

= ≠4.0mA

I

OL

= 8.0mA

I

OH

= ≠6.9mA

I

OL

= 3.0mA

I

OH

= ≠17.4mA

I

OL

= 12.0mA

I

OH

= ≠6.0mA

I

OL

= 4.0mA

I

OH

= ≠5.0mA

I

OL

= 10.0mA

I

OH

= ≠7.2mA

I

OL

= 5.0mA

I

OH

= ≠4.0mA

I

OL

= 5.4mA

V

IN

= V

DD

or V

SS

V

IN

= V

DD

or V

SS

V

IL

= 0V

V

IH

= V

DD

AV

DD

= 5V

CV

DD

= 5V

V

DD

1 = 5V

V

DD

2 = 5V

V

L

= ≠8.5V

V

H

= 15V

4.75

0.7V

DD

0.8V

DD

2.0

V

SS

V

DD

≠ 0.8

V

DD

≠ 0.8

V

DD

≠ 0.8

V

DD

≠ 0.8

V

M

≠ 0.25

V

H

≠ 0.25

V

H

≠ 0.25

250k

250k

20k

20k

5.0

1M

1M

50k

50k

24

1.9

0.8

5.25

0.3V

DD

0.2V

DD

V

DD

V

DD

0.4

0.4

0.4

0.4

V

L

+ 0.25

V

M

+ 0.25

V

L

+ 0.25

2.5M

2.5M

125k

125k

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

mA

mA

mA

Symbol

Conditions

Min.

Typ.

Max.

Unit

Supply voltage

Input voltage 1

(For input pins not listed below)

Input voltage 2

(Pin 29)

Input voltage 3

(Pins 11 and 12 in electronic iris

mode)

Input voltage 4

(Pin 13 in electronic iris mode)

Output voltage 1

(Pins 15, 23, 24, 25, 26, 33, 34, 35 and 36)

Output voltage 2

(Pins 30, 31 and 48)

Output voltage 3

(Pins 45 and 46)

Output voltage 4

(Pin 39)

Output voltage 5

(Pins 2, 3, 4 and 6)

Output voltage 6

(Pins 4 and 6 (SG))

Output voltage 7

(Pin 7)

Feedback resistor 1

(Pin 42)

Feedback resistor 2

(Resistor between Pins 40 and 41)

Pull-up resistor

Pull-down resistor

Current consumption

The typical power consumption is 148mW with the ICX054BL load (in the normal operating state).

≠ 6 ≠

CXD2463R

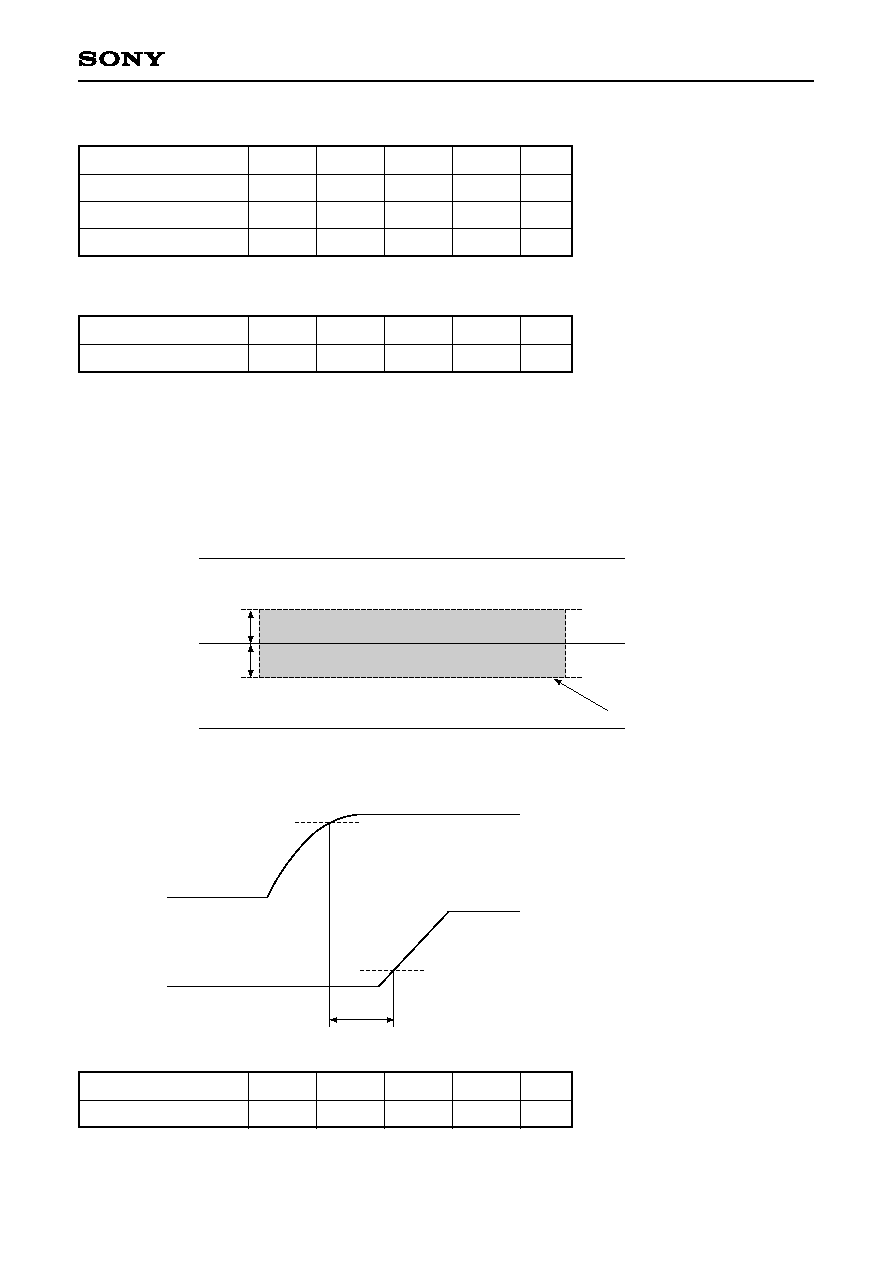

2) Input/Output Capacitance

(V

DD

= V

I

= 0V, f

M

= 1MHz)

Item

Input pin capacitance

Output pin capacitance

I/O pin capacitance

C

IN

C

OUT

C

I/O

9

11

11

pF

pF

pF

Symbol

Min.

Typ.

Max.

Unit

3) Comparator Characteristics (V

DD

= 5V ± 0.25V, Topr = ≠20 to +75∞C)

Item

Indefinite region

Vf

±70

mV

Symbol

Min.

Typ.

Max.

Unit

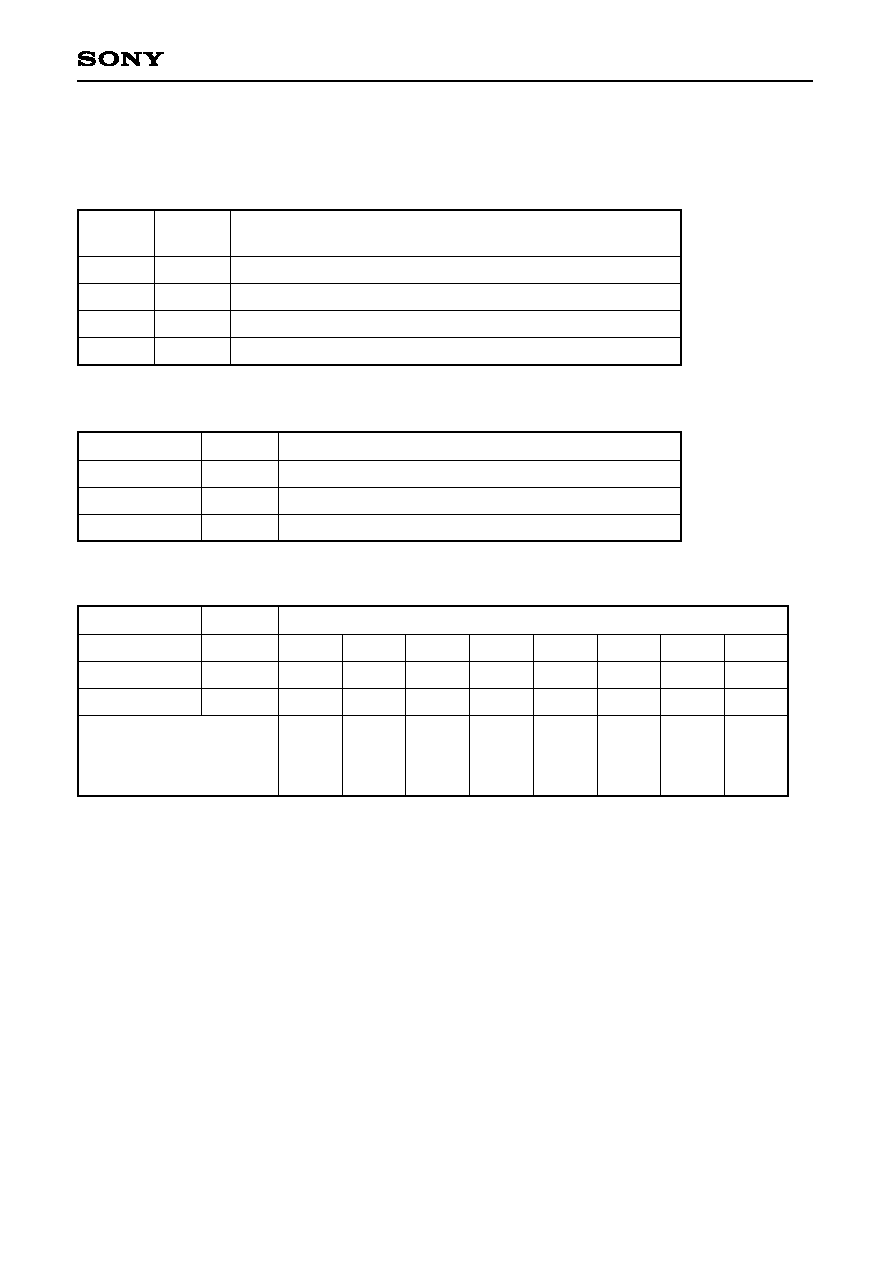

4) Power-on Reset Condition

(Within the recommended operating condition)

Item

Power-on reset period

t

WRST

35

ns

Symbol

Min.

Typ.

Max.

Unit

Note 1) Input offset voltage and indefinite region

The input offset voltage and indefinite region (region in which the comparator output is not set to high

or low) shown in the figure below exist in the built-in comparator in this IC, so be careful when

designing the external circuit.

Note 2) Pins 11 and 12 in electronic iris mode

Make sure of Pin 11 (SPUPV) < Pin 12 (SPDNV).

5.0V

GND

70mV

70mV

Pins 11 and 12

(SPUPV, SPDNV)

Indefinite region

4.75V

t

WRST

0.2V

DD

V

DD

RST

≠ 7 ≠

CXD2463R

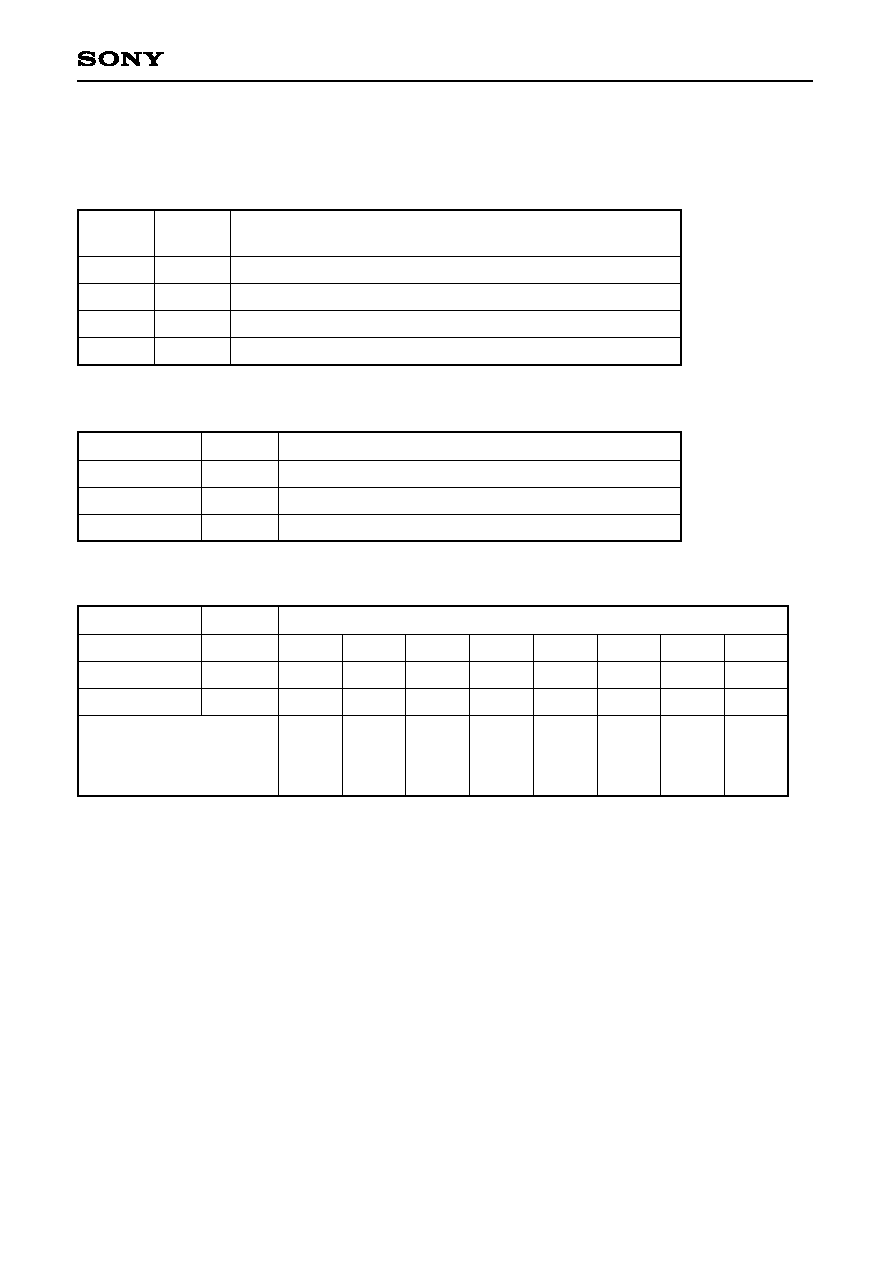

1. Electronic Iris/Electronic Shutter Function

The electronic iris or electronic shutter can be selected by setting the following pins to different combinations of

high and low.

ESHUT1

Pin 21

L

H

L

H

L

L

H

H

Electronic iris without limiter

Electronic iris with limiter EIA: 1/100 (s), CCIR: 1/120 (s)

Electronic shutter mode

Sub pulse stopped

ESHUT2

Pin 20

Operating Mode

Symbol

IRIN/ED1

SPDNV/ED2

SPUPV/ED0

13

12

11

Iris signal input

Shutter speed down reference voltage

Shutter speed up reference voltage

Pin No.

Function

1) Electronic Iris Mode

Symbol

SPUPV/ED0

IRIN/ED1

SPDNV/ED2

Shutter speed

11

13

12

H

H

H

EIA:

1/100

CCIR:

1/120

L

H

H

1/250

H

L

H

1/500

L

L

H

1/1000

H

H

L

1/2000

L

H

L

1/5000

H

L

L

1/10000

L

L

L

1/100000

Pin No.

Mode

2) Electronic Shutter Mode

≠ 8 ≠

CXD2463R

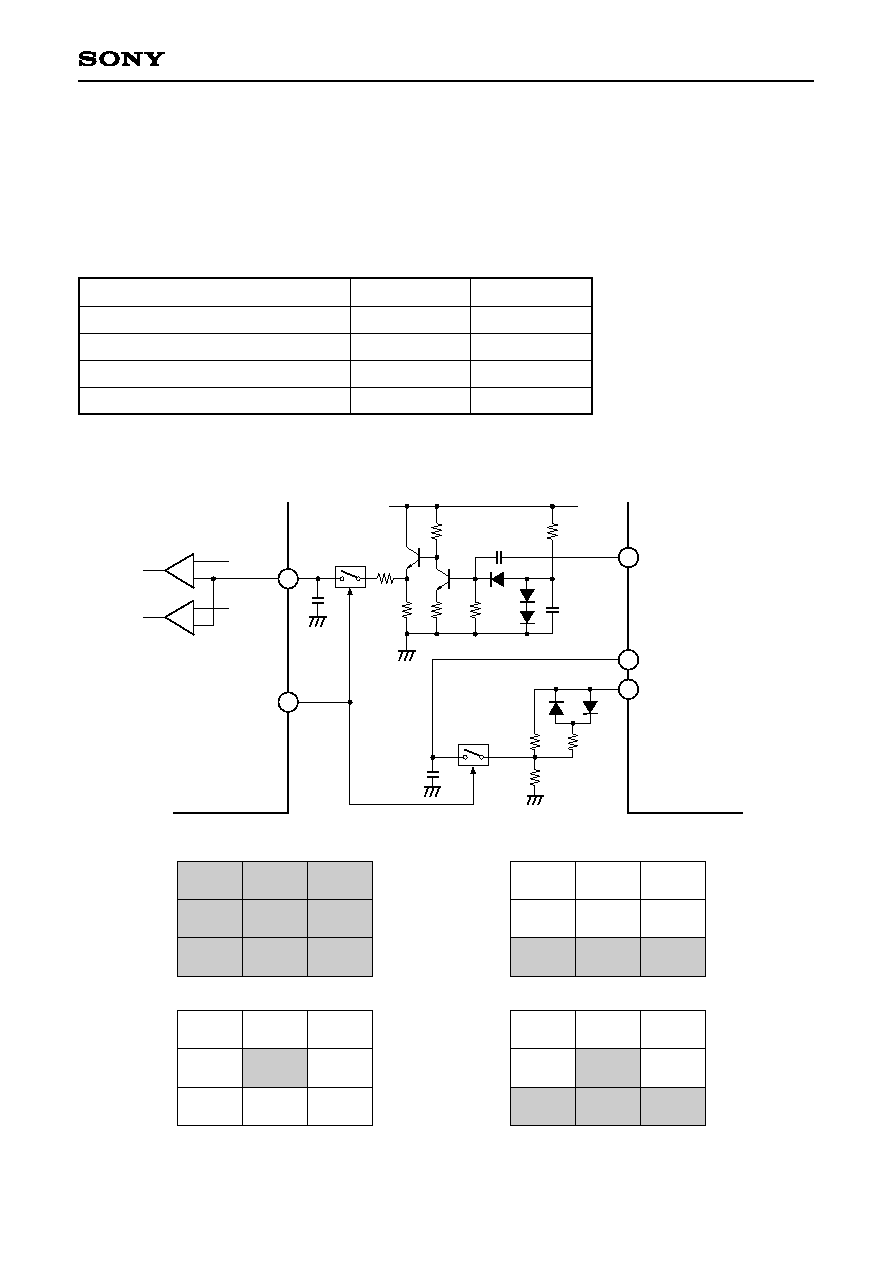

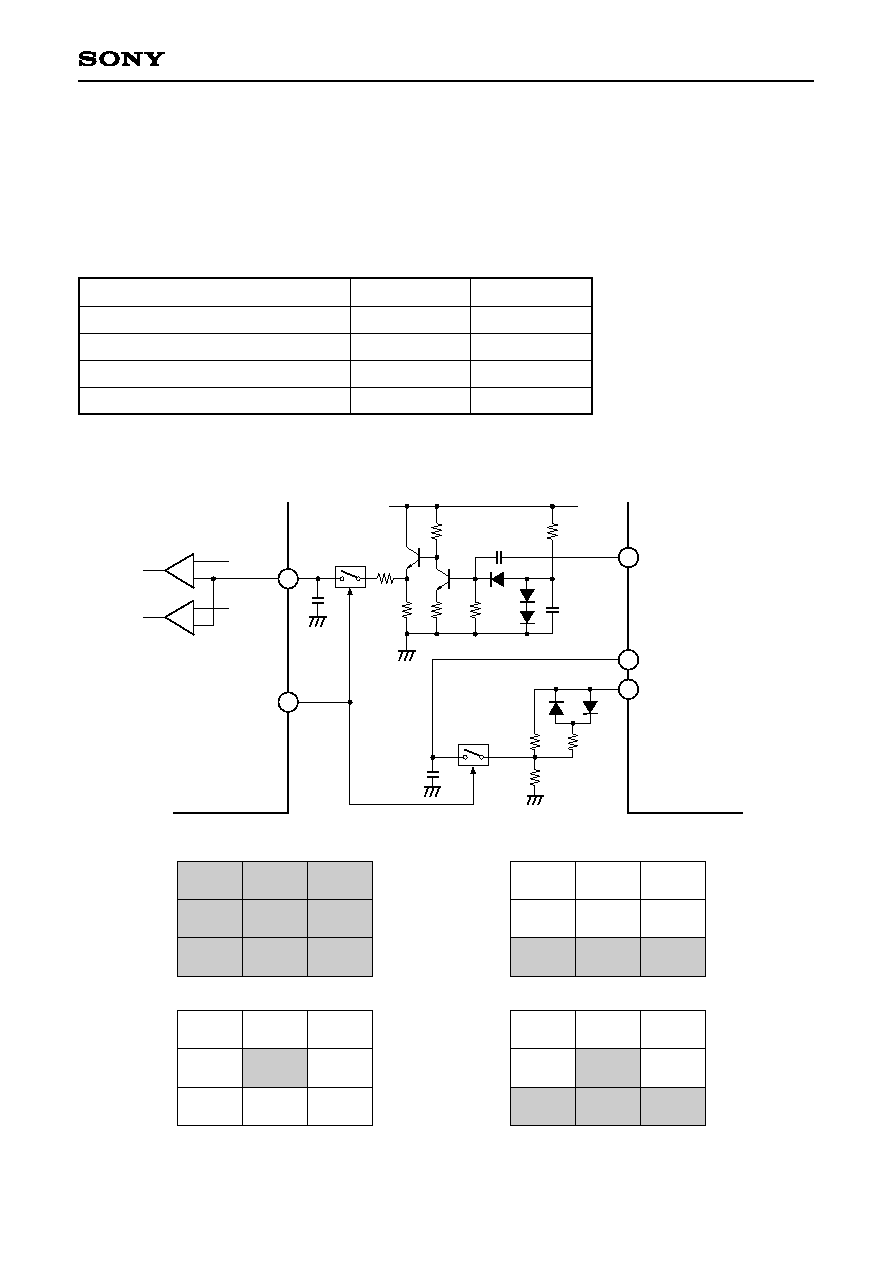

2. Backlighting Correction Function

The CXD2463R has a function to output the window pulse for backlight compensation.

The backlight compensation pulse is output from BLC (Pin 15) in the following range according to the high/low

combination of BLCW1 (Pin 17) and BLCW2 (Pin 18).

Window Type for Different Pin Combinations

Window type

Full-screen photometry

Bottom emphasis photometry

Center emphasis photometry

Bottom + center emphasis photometry

L

H

L

H

L

L

H

H

BLCW1 (Pin 17) BLCW2 (Pin 18)

Example of Basic Circuit Configuration

Iris comparator

Iris

window switch

AGC

window switch

IRIN/ED1

13

BLC

3.9k

10k

39k

+5V

100k

10

µ

IRIS

OP+

DETOUT

1k

10k

100k

10

µ

10k

10k

CXD2463R

CXA1310AQ

15

27

19

13

Full-screen photometry

Center emphasis photometry

Bottom emphasis photometry

Bottom + center emphasis photometry

≠ 9 ≠

CXD2463R

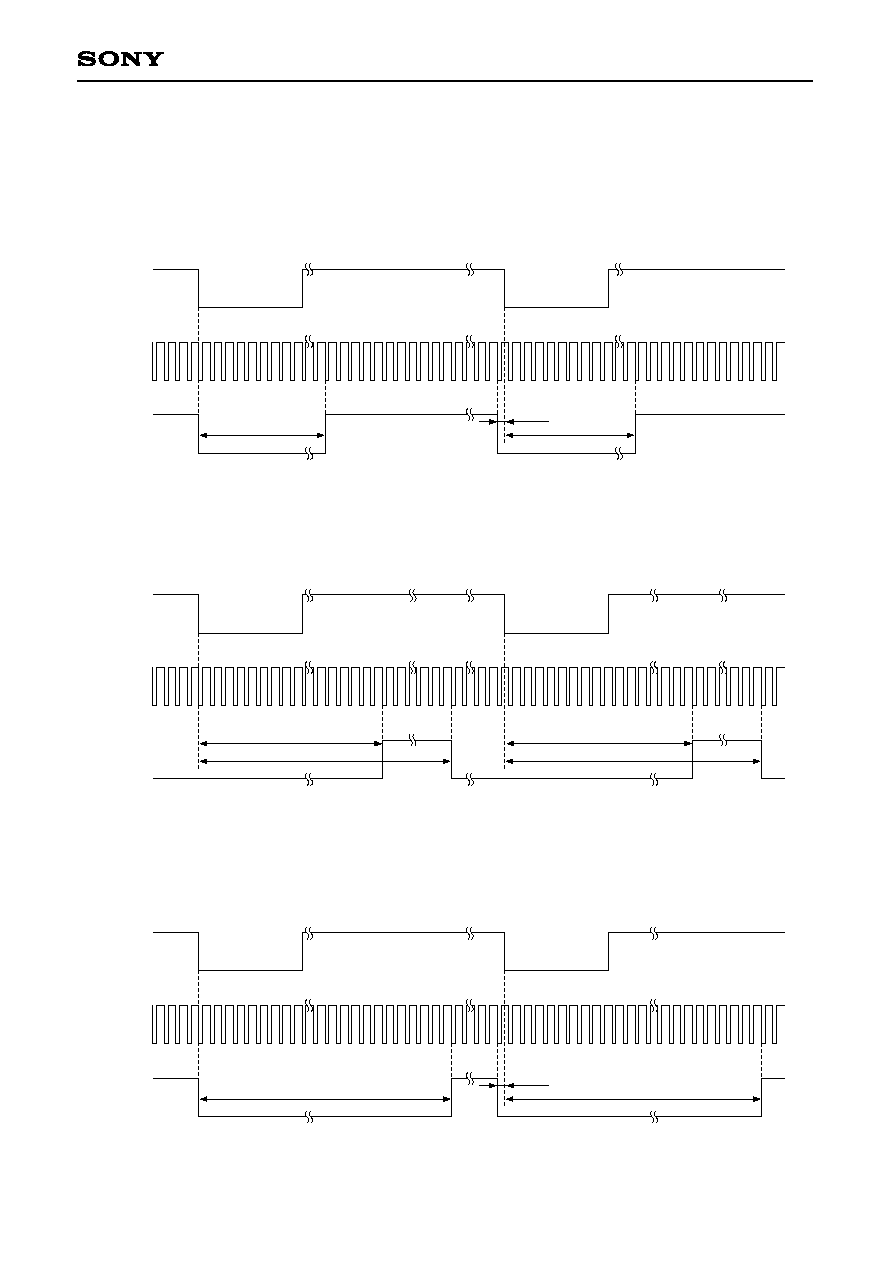

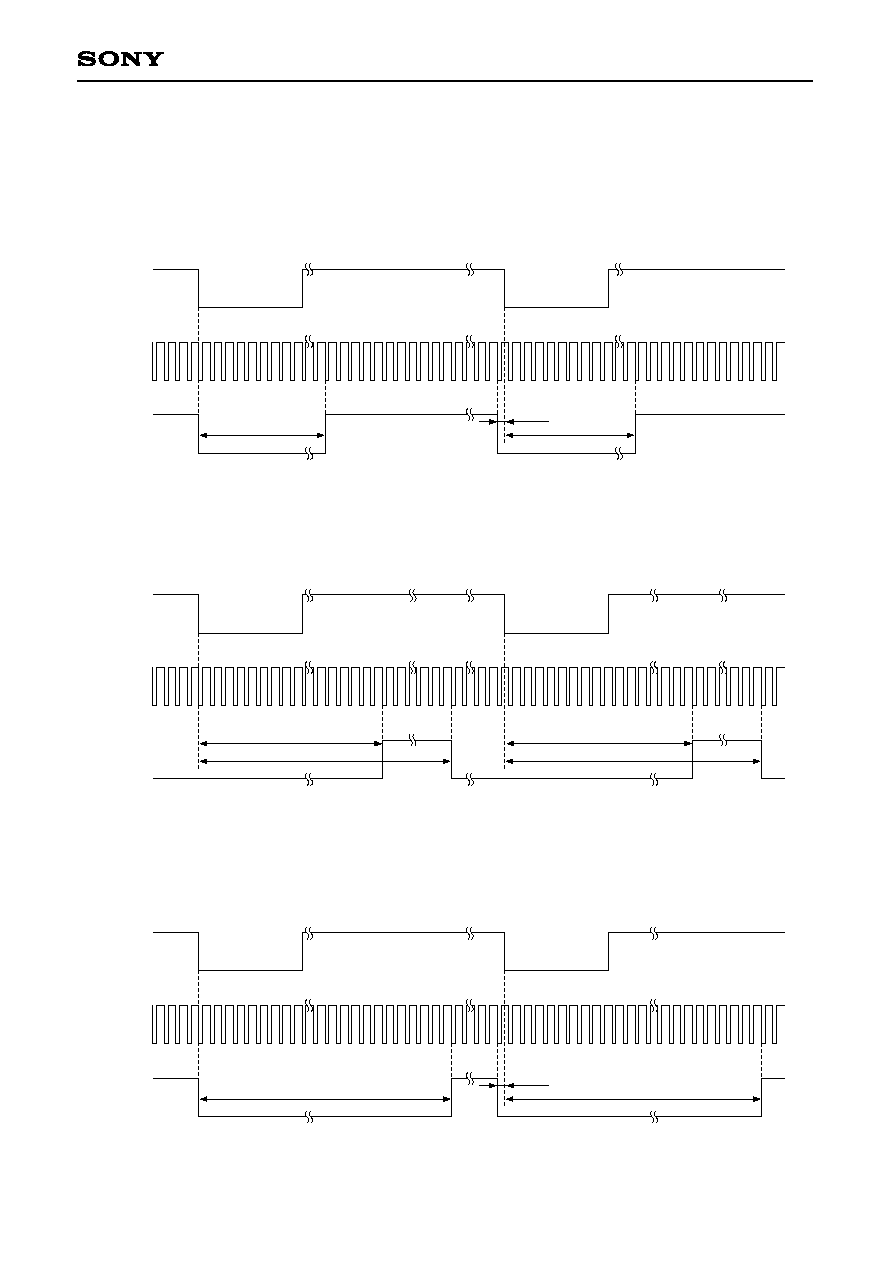

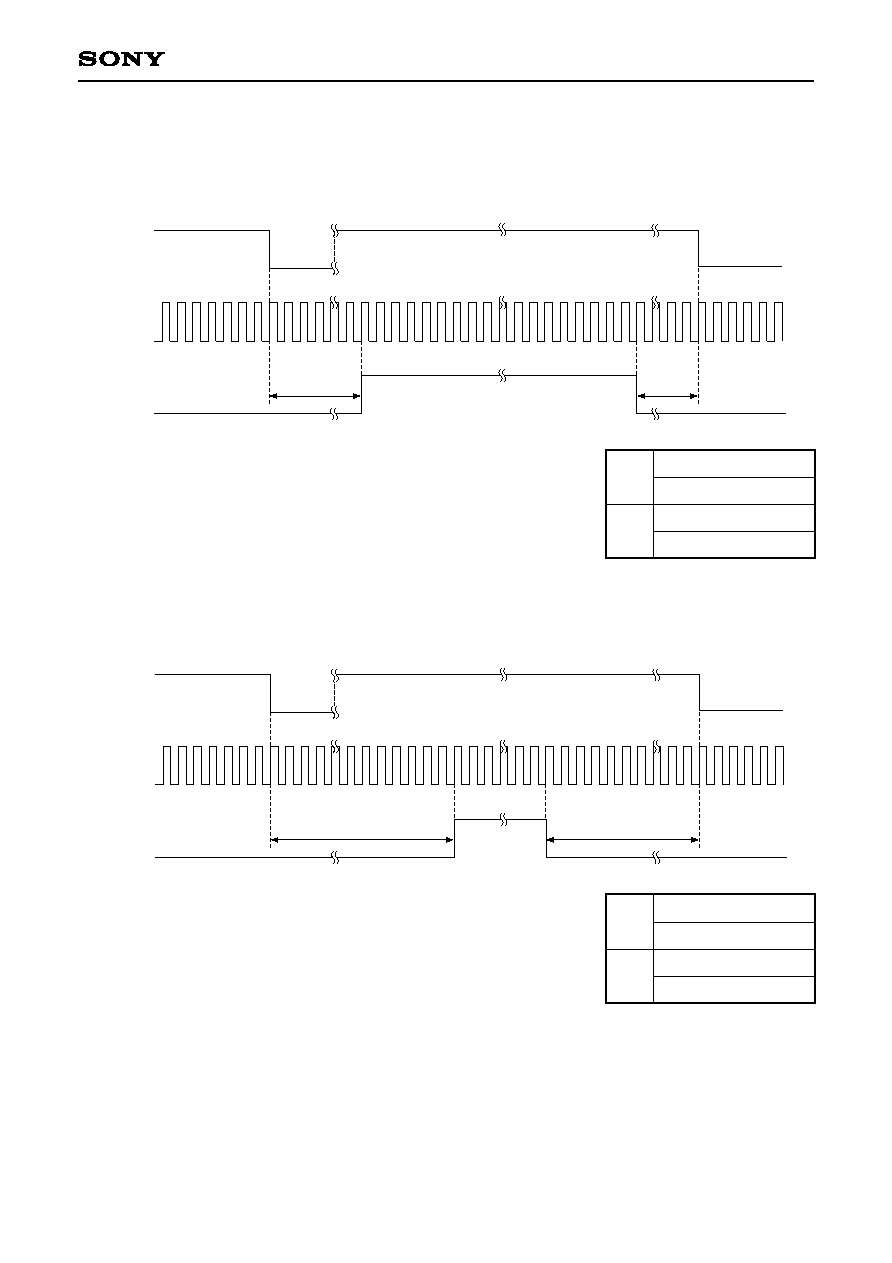

1) Window Pulse Timing Charts

∑ EIA Mode/Vertical Direction Timing

(1) Full-screen photometry

VD

HD

BLC

20HD

20.5HD

0.5HD

(2) Center emphasis photometry

VD

HD

BLC

181HD

101HD

181.5HD

101.5HD

(3) Bottom emphasis photometry

VD

HD

BLC

181HD

181.5HD

0.5HD

≠ 10 ≠

CXD2463R

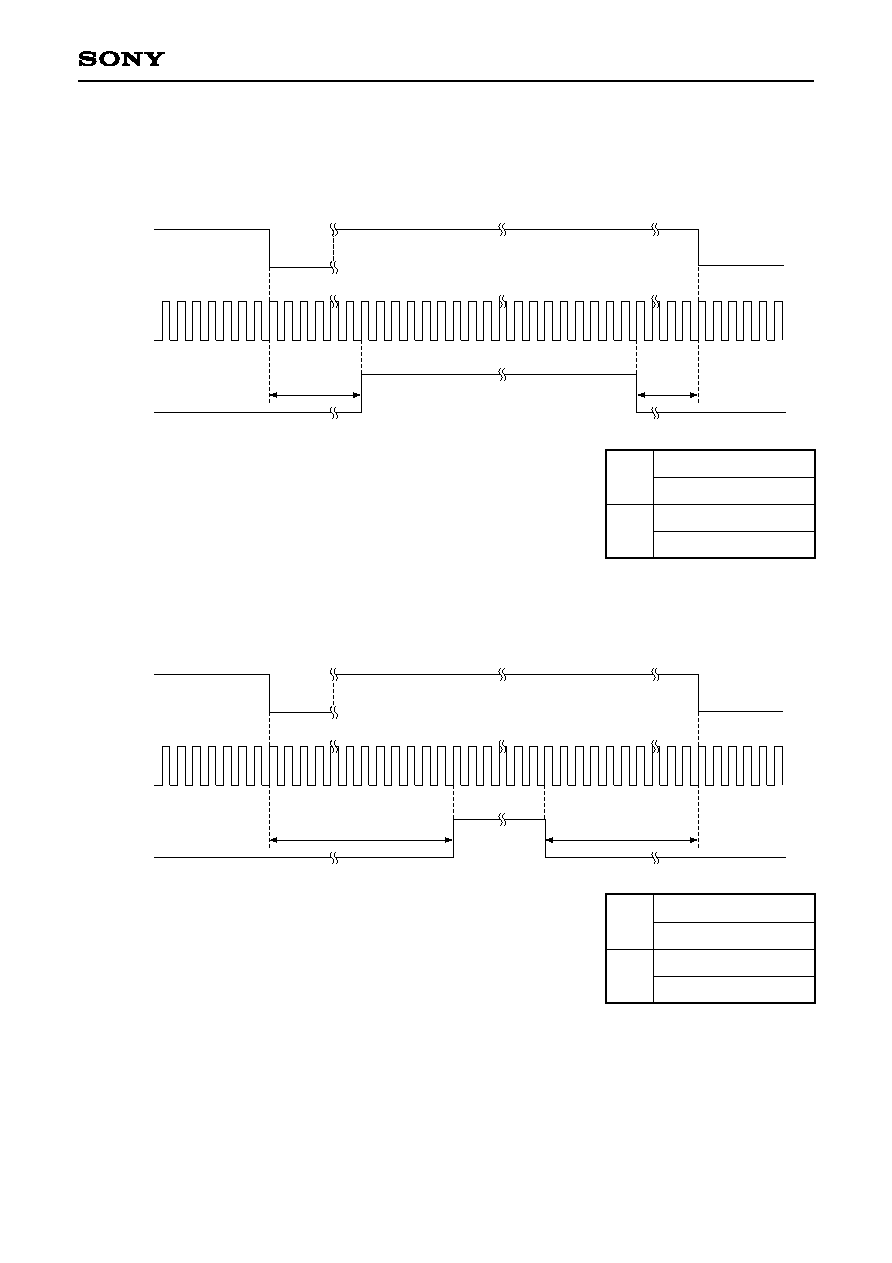

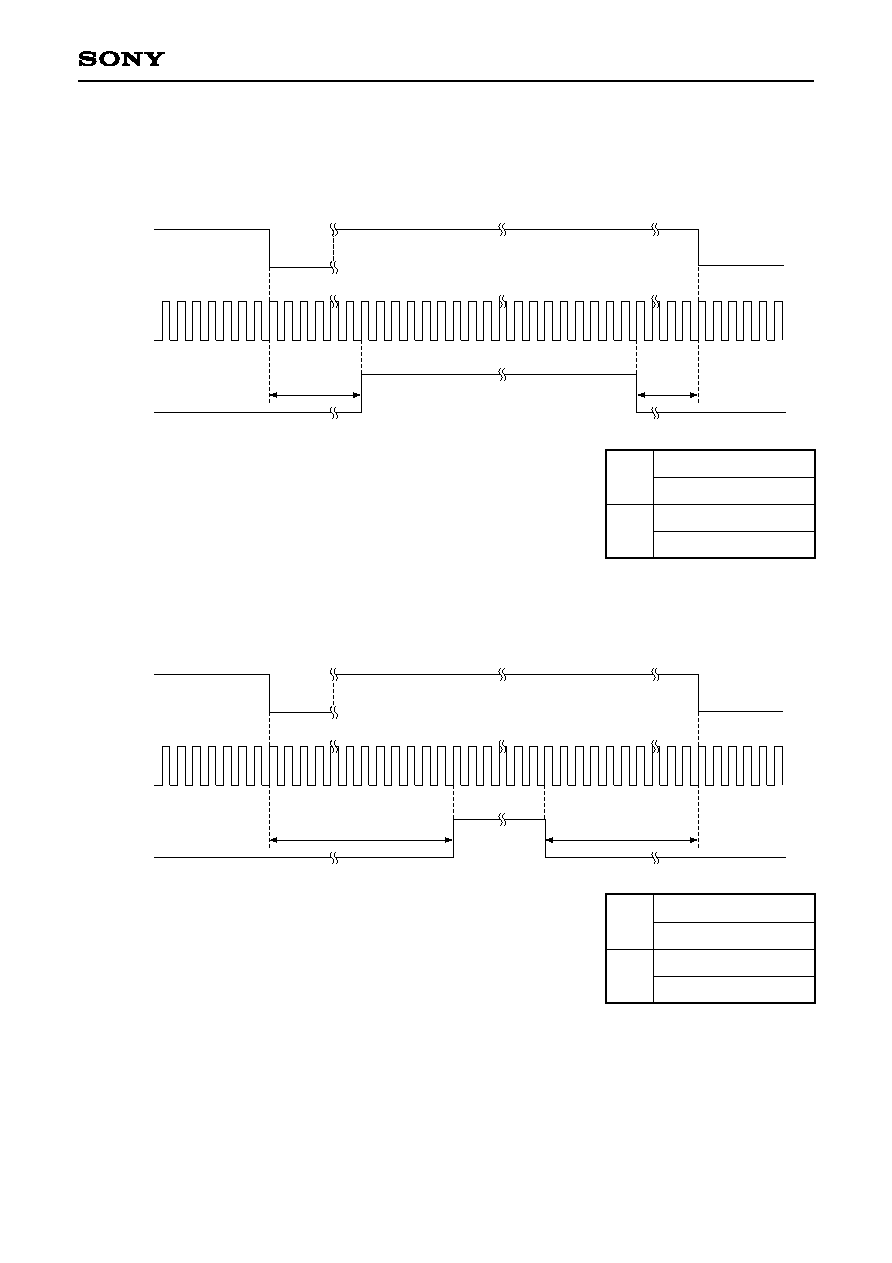

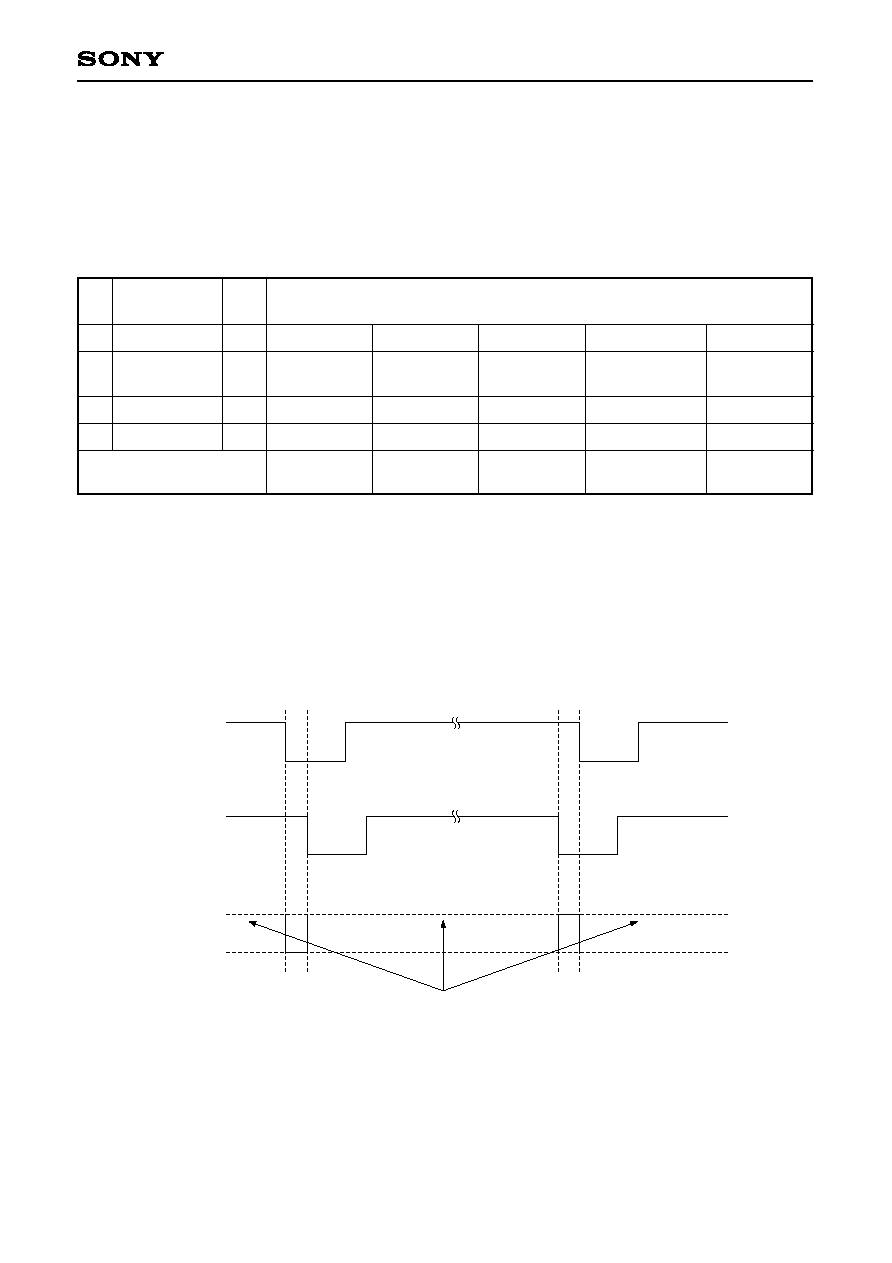

∑ EIA Mode/Horizontal Direction Timing

(1) Bottom emphasis photometry and full-screen photometry

HD

MCK

BLC

X1

X2

X1

510H

760H

510H

760H

104MCK

154MCK

3MCK

22MCK

X2

(2) Center emphasis photometry

HD

MCK

BLC

X1

X2

X1

510H

760H

510H

760H

272MCK

407MCK

167MCK

252MCK

X2

≠ 11 ≠

CXD2463R

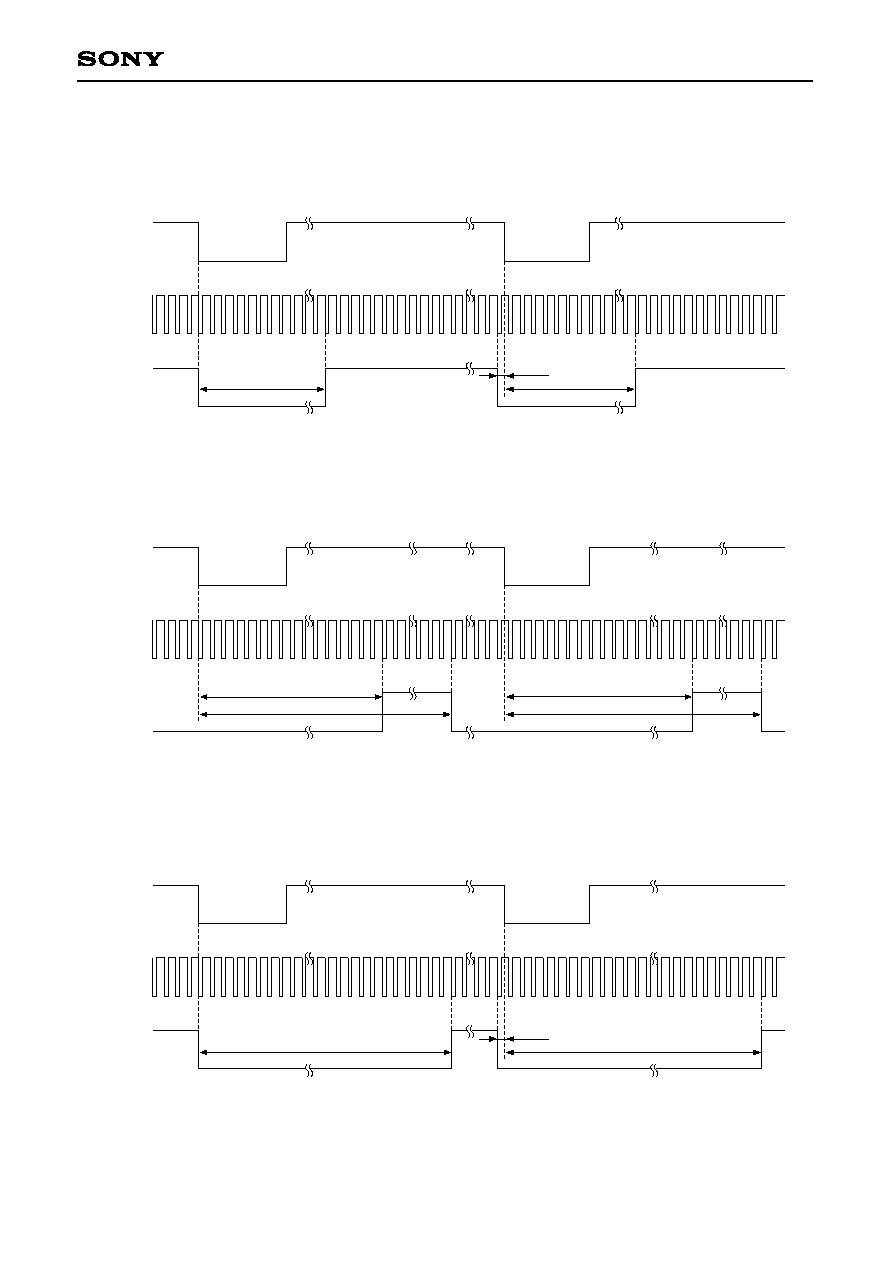

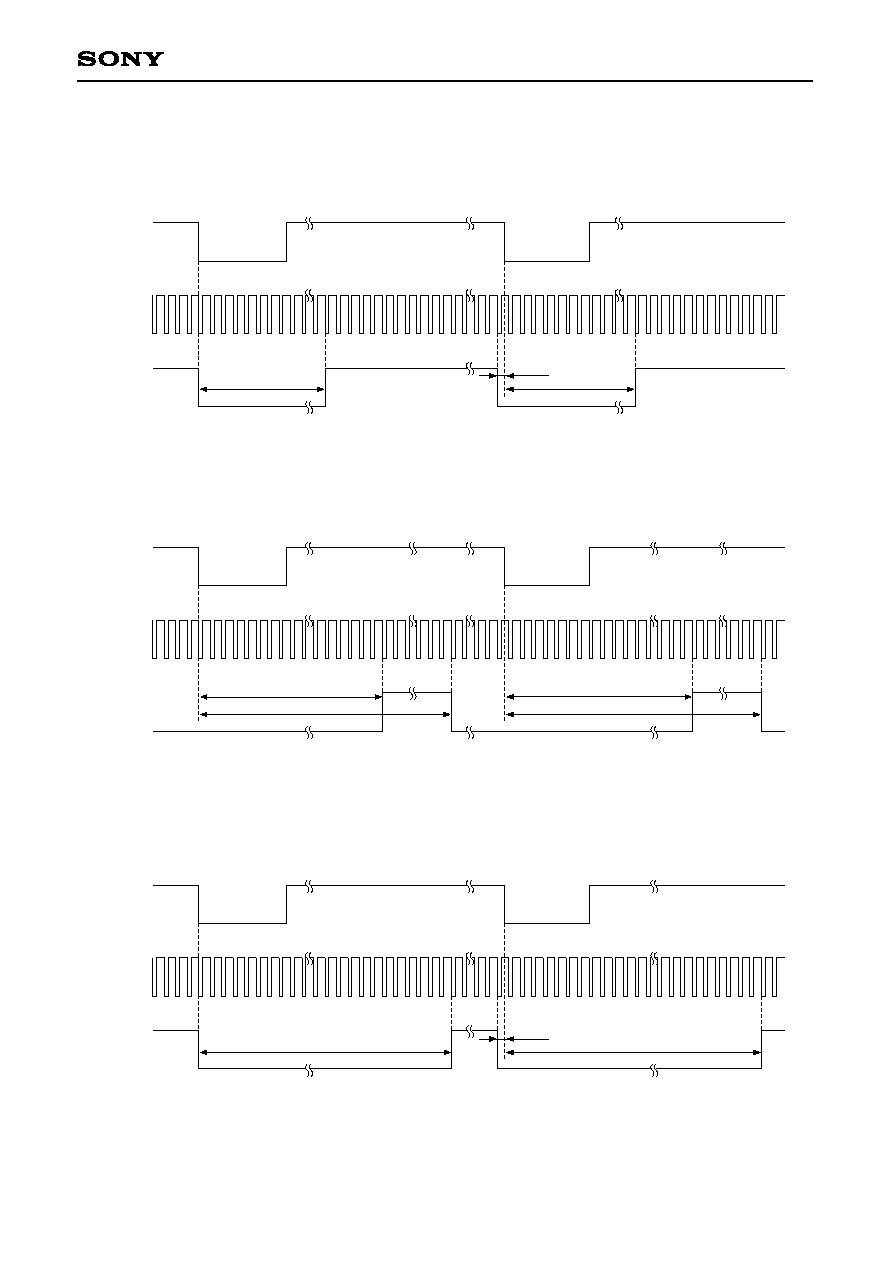

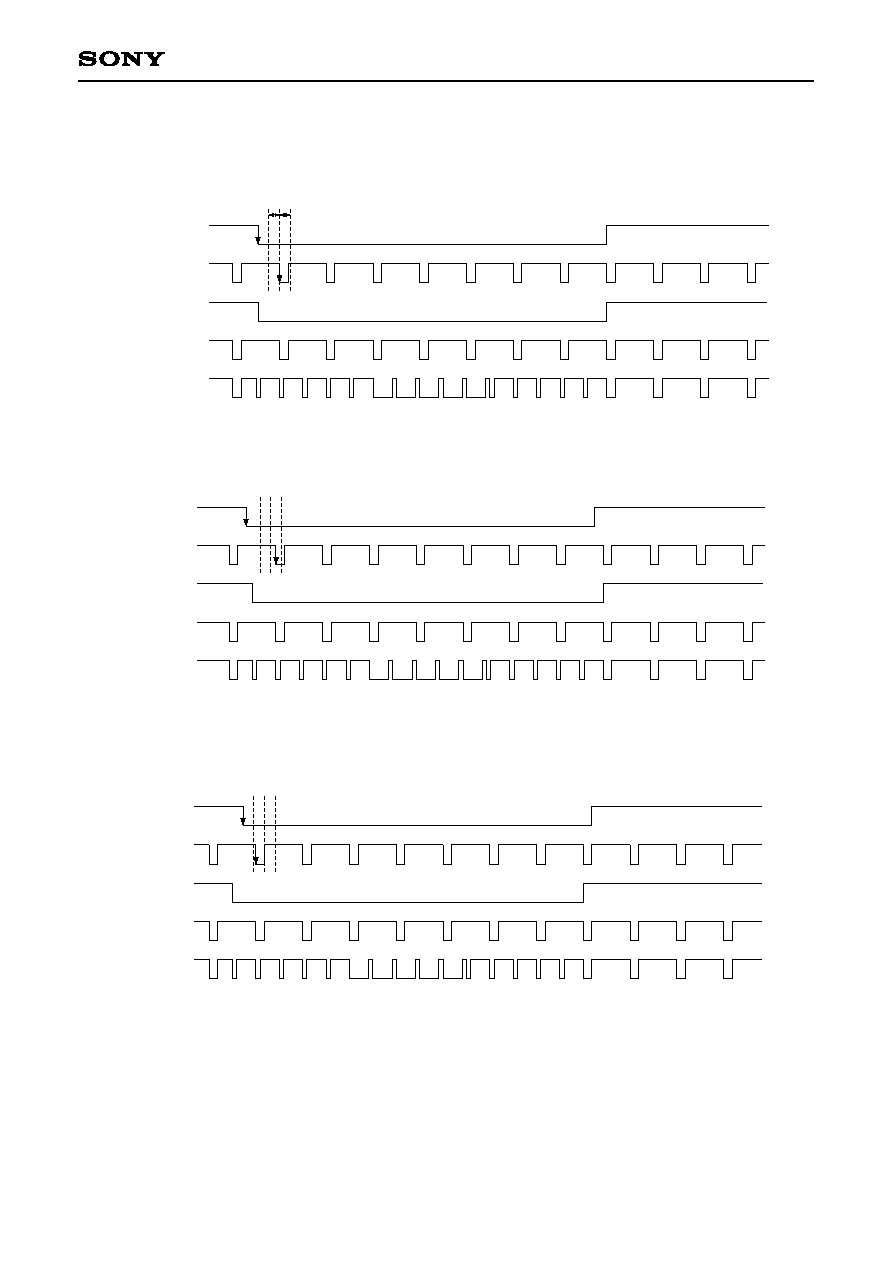

∑ CCIR Mode/Vertical Direction Timing

(1) Full-screen photometry

VD

HD

BLC

25HD

25.5HD

0.5HD

(2) Center emphasis photometry

VD

HD

BLC

216HD

121HD

216.5HD

121.5HD

(3) Bottom emphasis photometry

VD

HD

BLC

216HD

216.5HD

0.5HD

≠ 12 ≠

CXD2463R

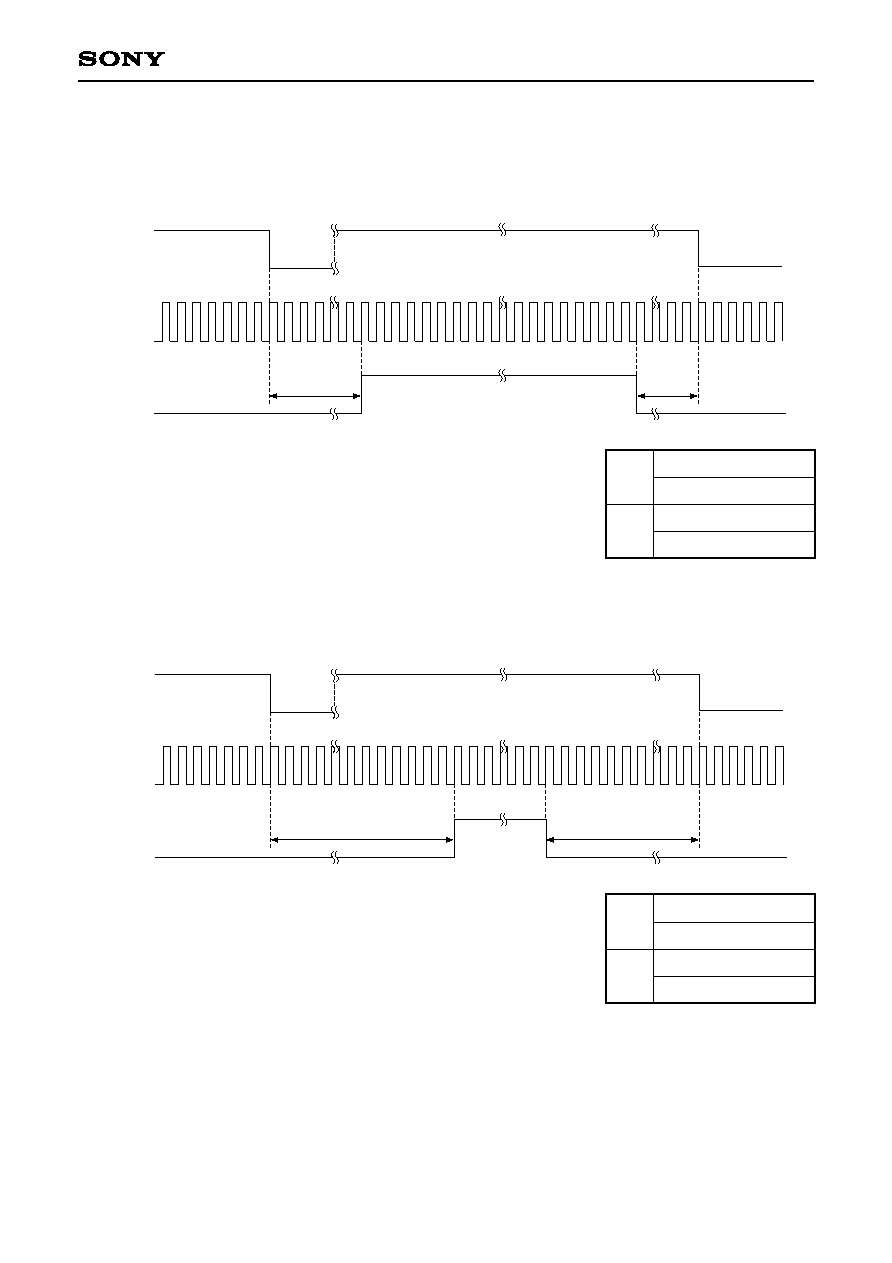

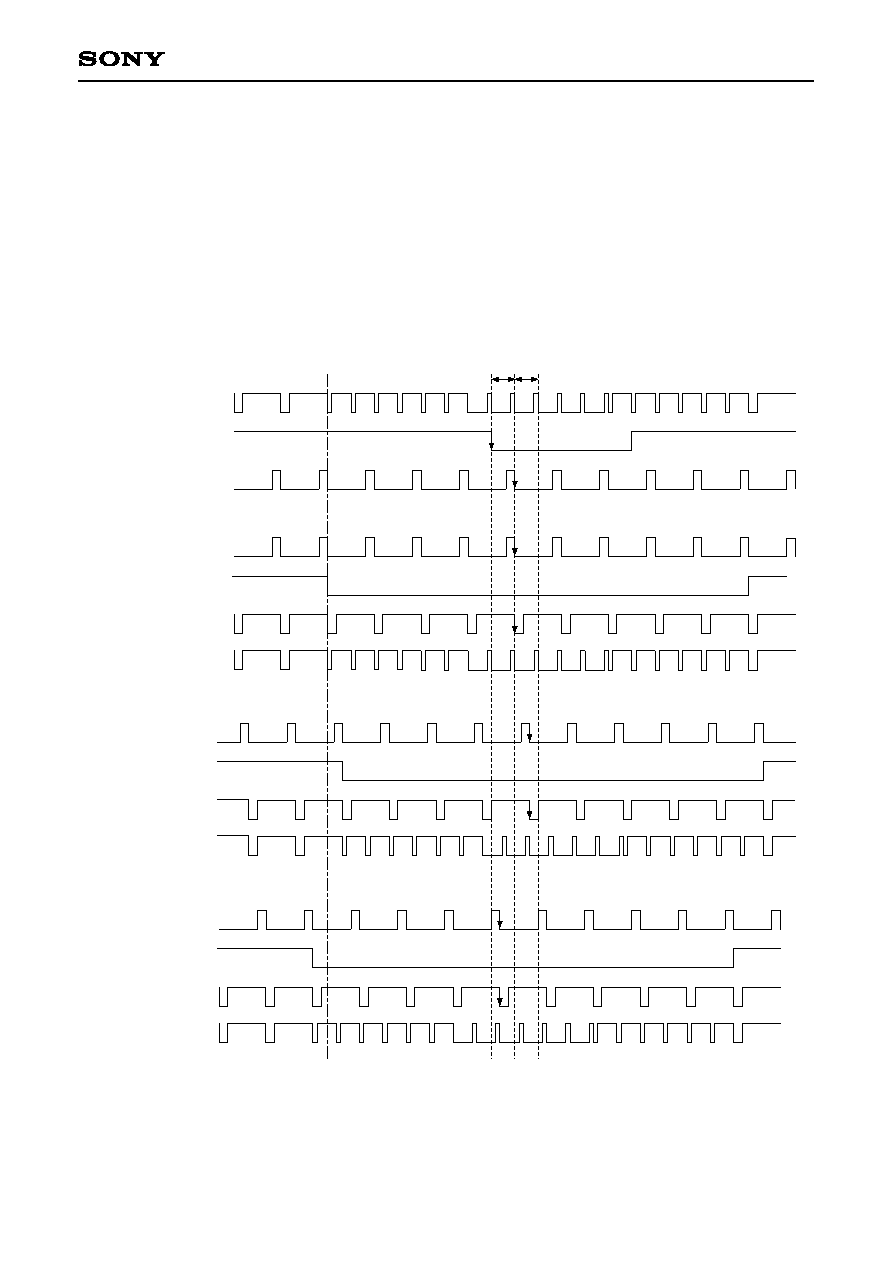

∑ CCIR Mode/Horizontal Direction Timing

(1) Bottom emphasis photometry and full-screen photometry

HD

MCK

BLC

X1

X2

X1

510H

760H

510H

760H

114MCK

169MCK

3MCK

22MCK

X2

(2) Center emphasis photometry

HD

MCK

BLC

X1

X2

X1

510H

760H

510H

760H

279MCK

416MCK

164MCK

246MCK

X2

≠ 13 ≠

CXD2463R

3. External Sync Function

The CXD2463R supports the three modes of Line-Lock, VReset + HPLL (VD and HD inputs), and VReset +

HPLL (Sync input) as the external sync functions. Each mode is automatically switched according to the

combination of signals input to EHD/SYNC (Pin 38) and EVD (Pin 37).

1) Automatic External Sync Discrimination

I/O

I

I

O

O

EHD/SYNC

EVD

HVDET

EXT

38

37

33

34

HD

No signal

L

L

INT

No signal

VD

H

H

LL

HD

VD

L

H

VReset

+ HPLL

SYNC

HD after SYNC

separation

L

H

VReset

+ HPLL

No signal

No signal

L

L

INT

Symbol

Pin

No.

EHD/SYNC and EVD pins signal input state

and HVDET and EXT pins discrimination results

Mode

∑ If unspecified signals are input for the external signals given above, there may be recognition errors.

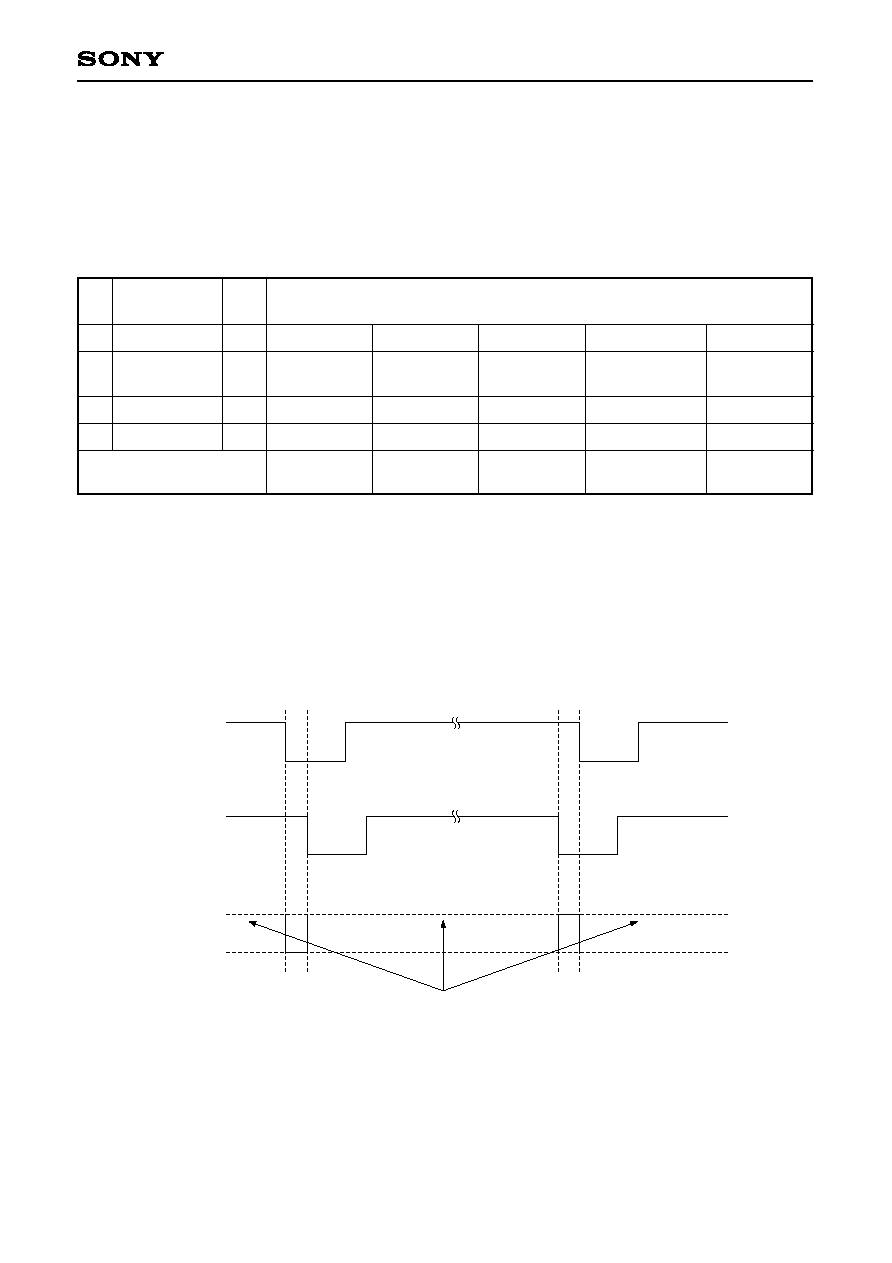

2) LL (Line-Lock) Mode

When the V sync clock is externally input to EVD (Pin 37), the result of comparing the falling edge of the clock

and the falling edge of the internal VD is output from COMP (Pin 39). The output polarity is compatible with the

active filter.

EXT-VD

(Pin 37)

INT-VD

(Pin 35)

COMP

(Pin 39)

High impedance state

≠ 14 ≠

CXD2463R

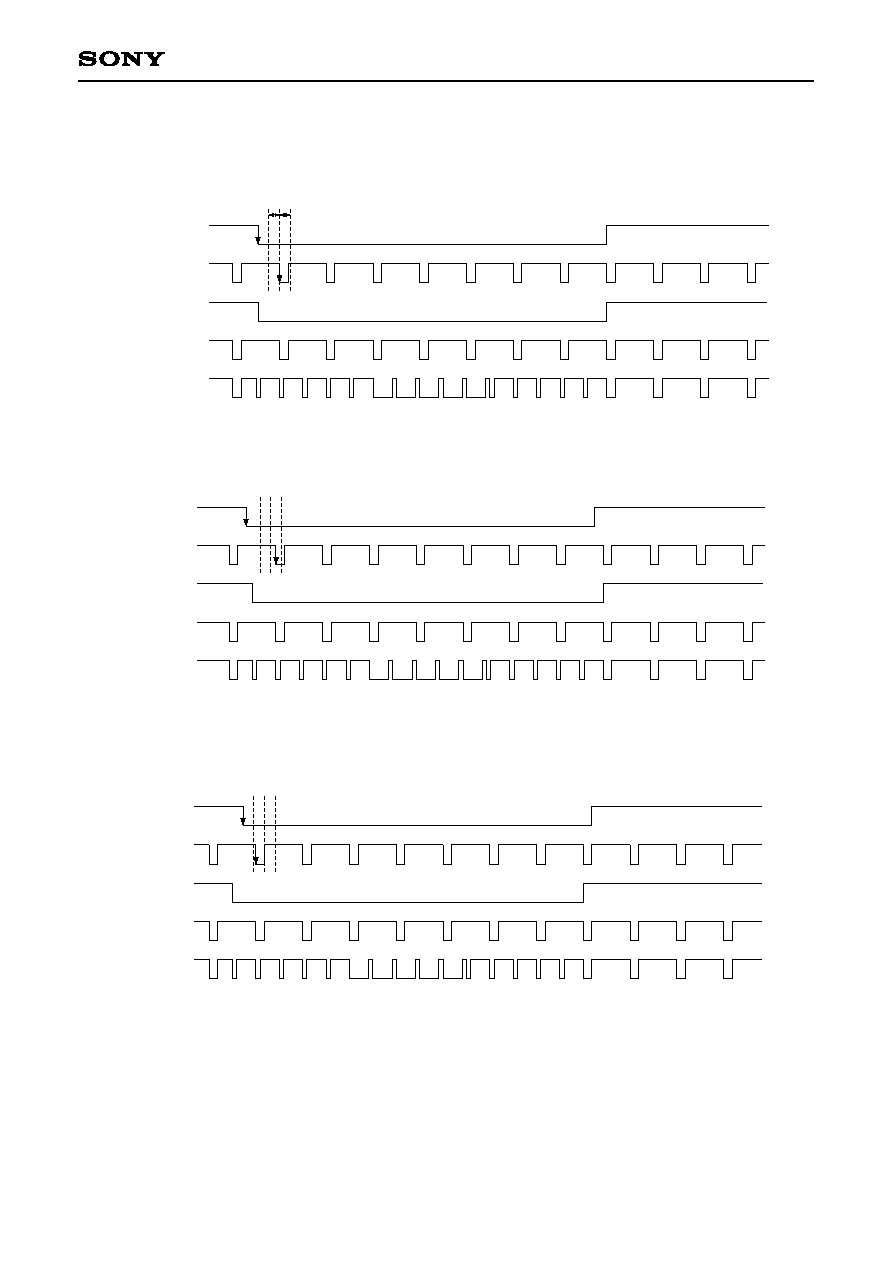

3) VReset + HPLL (VD and HD Inputs) Mode

When the HD cycle clock is externally input to EHD/SYNC (Pin 38) and the V cycle clock is externally input to

the EVD (Pin 37), the CXD2463R sync signal is output as shown below based on the phase difference

between these signals.

Similar to Line-Lock mode, the result of comparing the phase of the falling edges of the HD cycle clock input to

Pin 38 and the CXD2463R internal HD is output from COMP (Pin 39). The PLL is applied using this signal.

Similar to Line-Lock mode, the polarity of the COMP (Pin 39) output is compatible with the active filter. The

phase of the HD falling edge can be shifted up to ±1/4H with respect to the falling edge of the master VD (EXT-

VD).

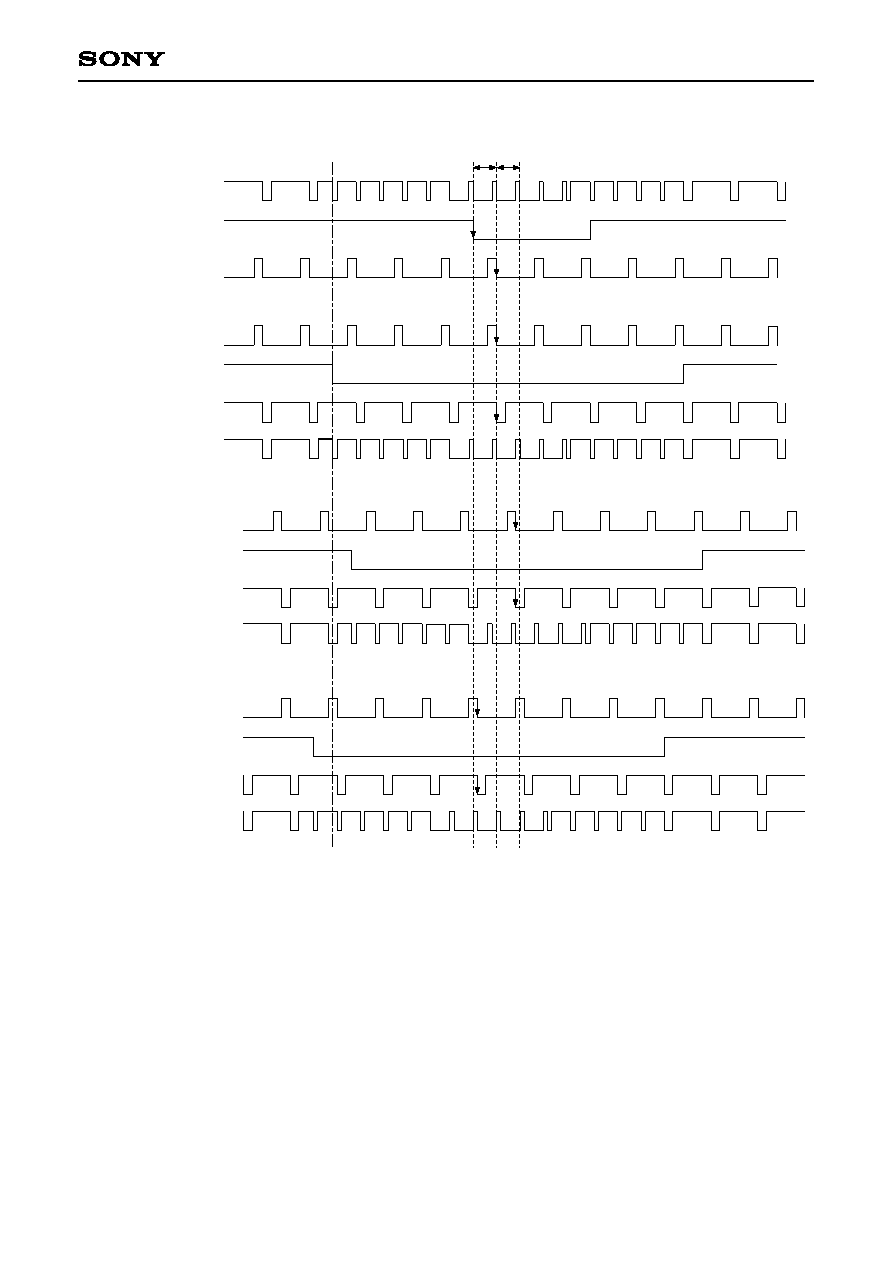

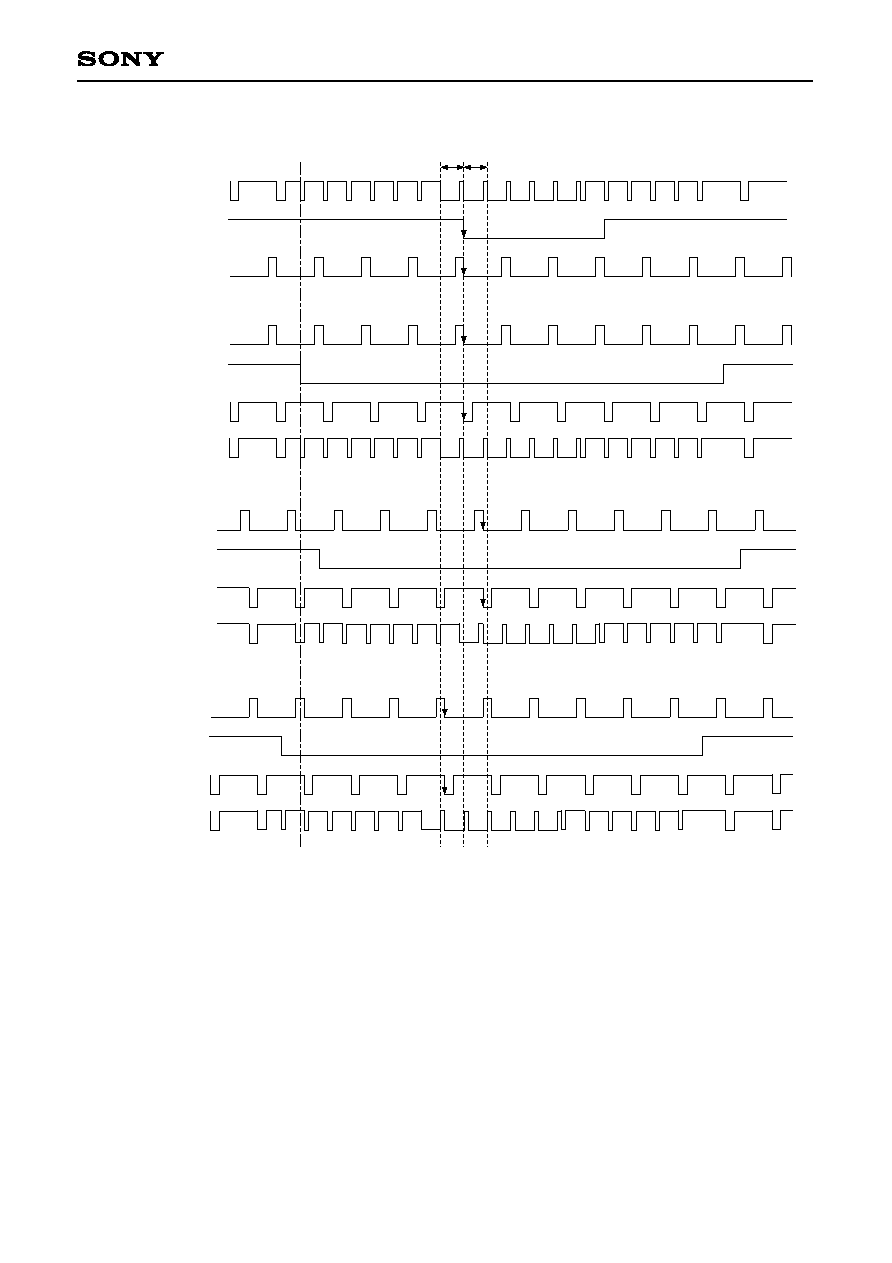

∑ EIA/ODD

(1) EXT-VD and EXT-HD have the same phase.

1/4H 1/4H

EXT-VD

(Pin 37 input)

EXT-HD

(Pin 38 input)

VD

(Pin 35 output)

HD

(Pin 36 output)

SYNC

(Pin 25 output)

(2) EXT-VD and EXT-HD have the same phase to +1/4H.

EXT-VD

EXT-HD

VD

HD

SYNC

(3) EXT-VD and EXT-HD have the ≠1/4H to the same phase.

EXT-VD

EXT-HD

VD

HD

SYNC

≠ 15 ≠

CXD2463R

∑ EIA/EVEN

(1) EXT-VD and EXT-HD have the same phase.

1/4H 1/4H

EXT-VD

(Pin 37 input)

EXT-HD

(Pin 38 input)

VD

(Pin 35 output)

HD

(Pin 36 output)

SYNC

(Pin 25 output)

(2) EXT-VD and EXT-HD have the same phase to +1/4H.

EXT-VD

EXT-HD

VD

HD

SYNC

(3) EXT-VD and EXT-HD have the same phase to ≠1/4H.

EXT-VD

EXT-HD

VD

HD

SYNC

≠ 16 ≠

CXD2463R

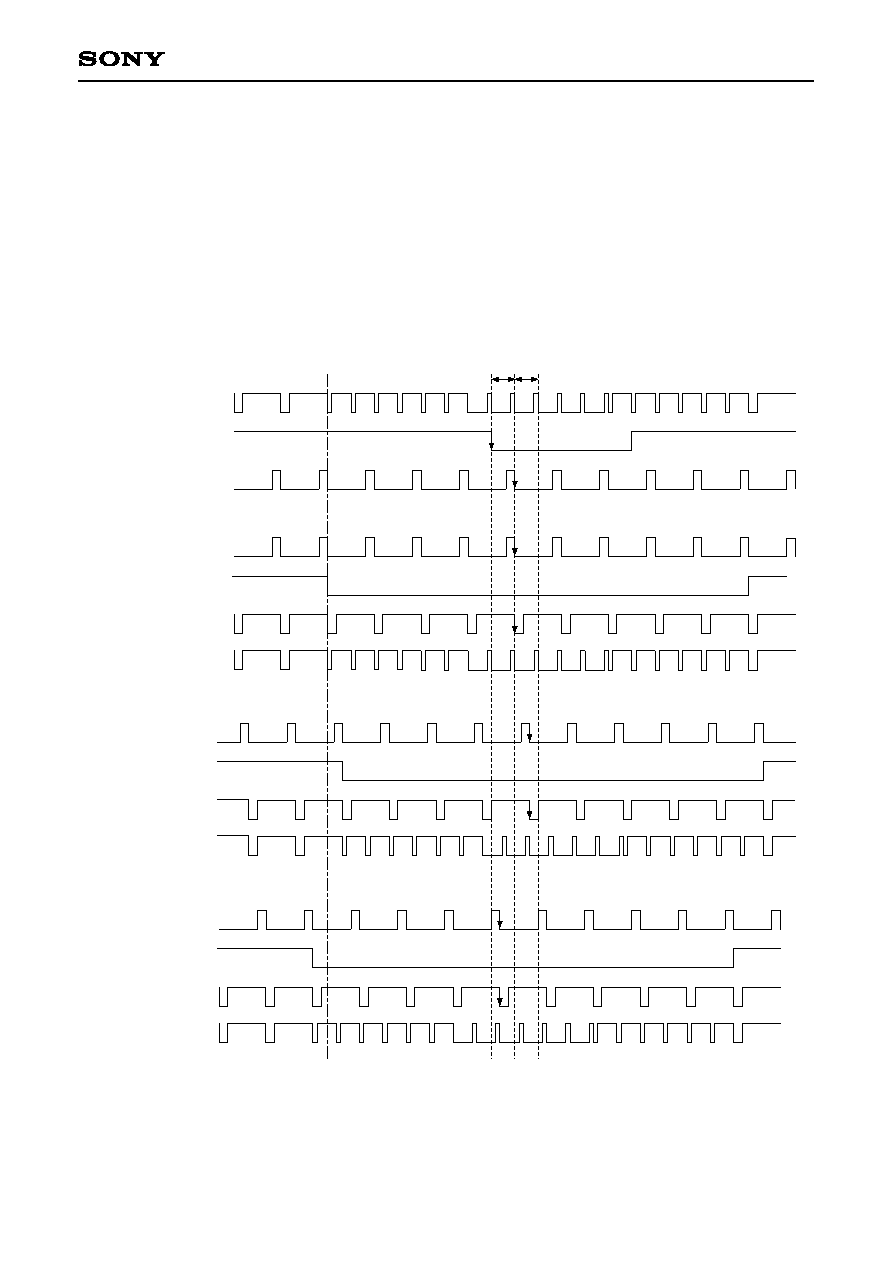

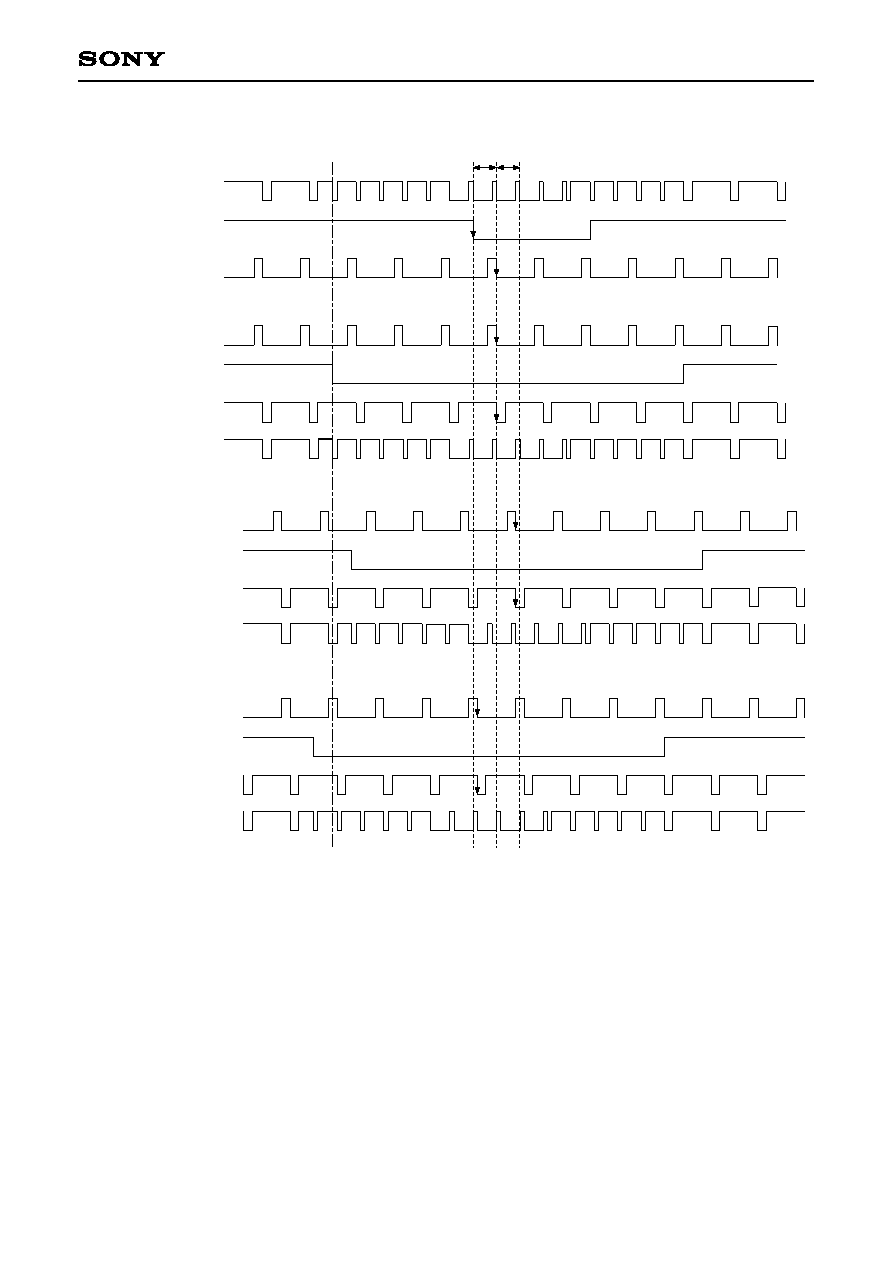

∑ CCIR/ODD

(1) EXT-VD and EXT-HD have the same phase.

1/4H 1/4H

EXT-VD

(Pin 37 input)

EXT-HD

(Pin 38 input)

VD

(Pin 35 output)

HD

(Pin 36 output)

SYNC

(Pin 25 output)

(2) EXT-VD and EXT-HD have the same phase to +1/4H.

EXT-VD

EXT-HD

VD

HD

SYNC

(3) EXT-VD and EXT-HD have the same phase to ≠1/4H.

EXT-VD

EXT-HD

VD

HD

SYNC

≠ 17 ≠

CXD2463R

∑ CCIR/EVEN

(1) EXT-VD and EXT-HD have the same phase.

1/4H 1/4H

EXT-VD

(Pin 37 input)

EXT-HD

(Pin 38 input)

VD

(Pin 35 output)

HD

(Pin 36 output)

SYNC

(Pin 25 output)

(2) EXT-VD and EXT-HD have the same phase to +1/4H.

EXT-VD

EXT-HD

VD

HD

SYNC

(3) EXT-VD and EXT-HD have the same phase to ≠1/4H.

EXT-VD

EXT-HD

VD

HD

SYNC

≠ 18 ≠

CXD2463R

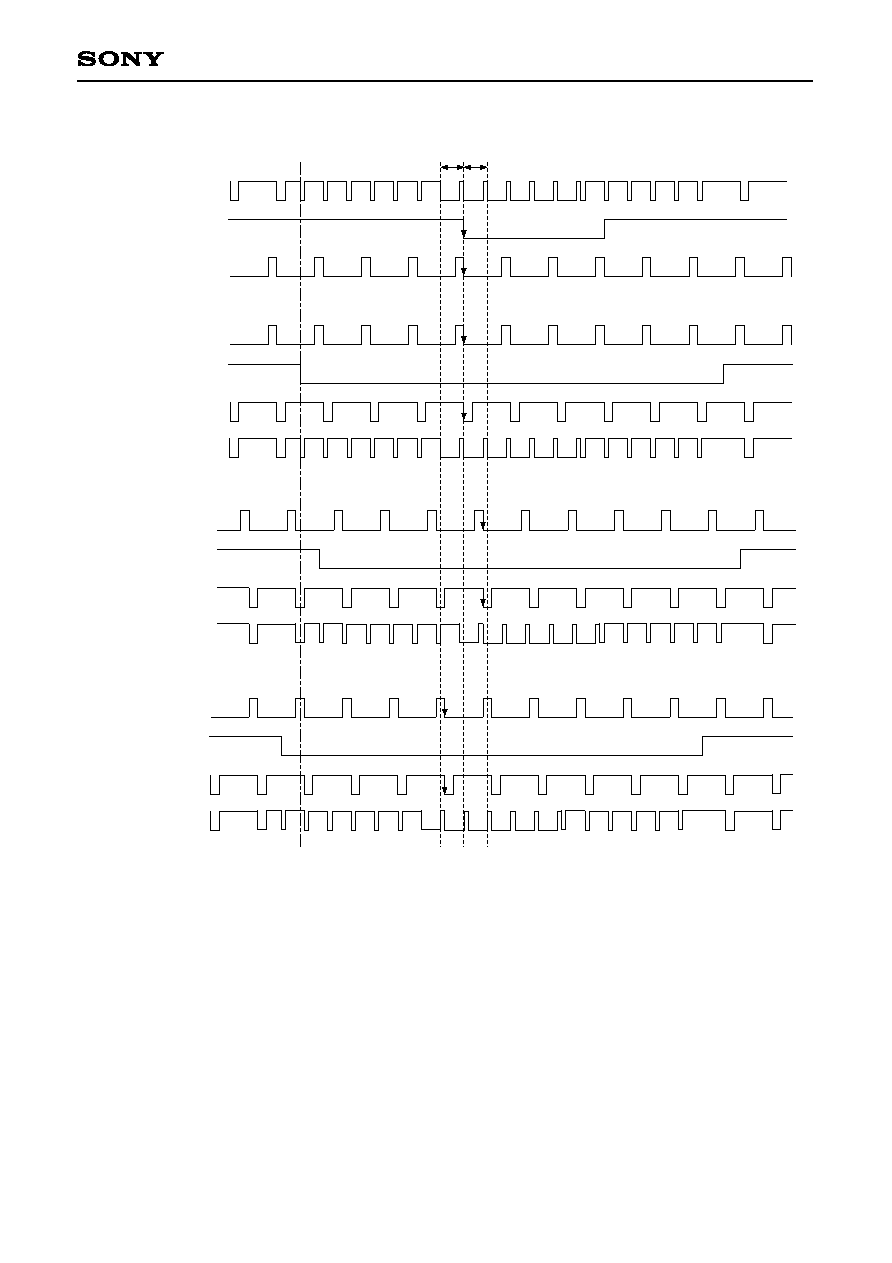

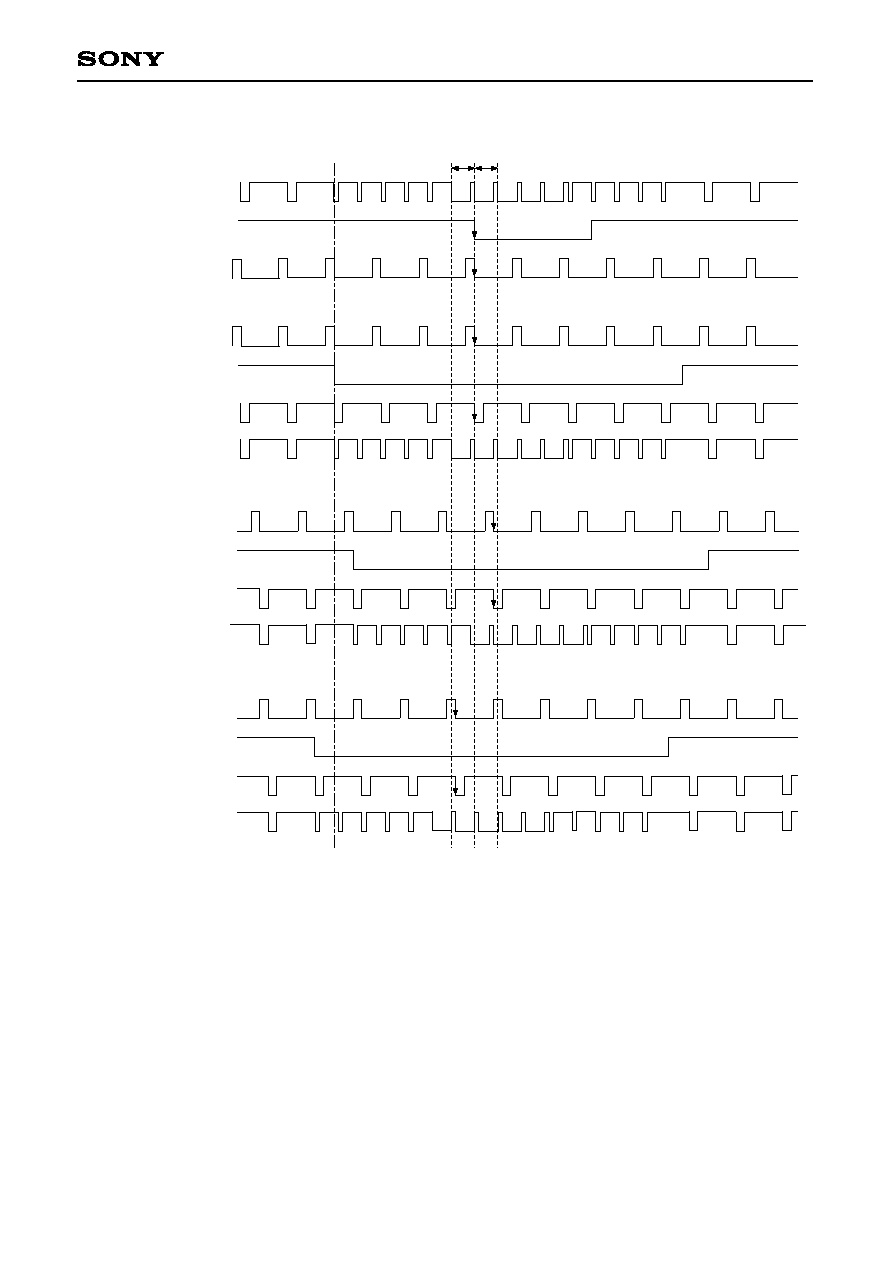

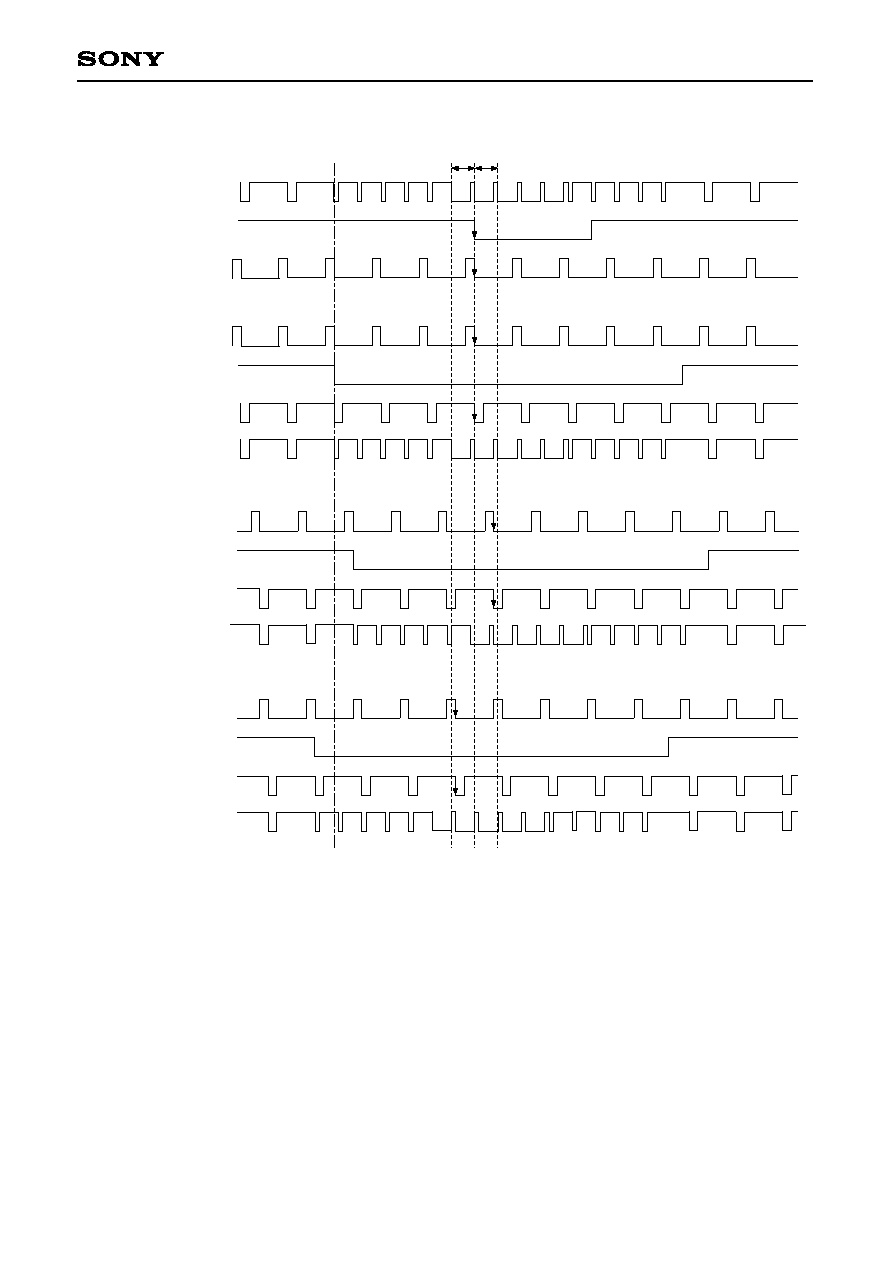

4) VReset + HPLL (SYNC Input) Mode

When the specified sync signal is externally input to EHD/SYNC (Pin 38), the EXT-HD separated from this

sync signal is output from HD (Pin 36). This signal is input through the shifter to EVD (Pin 37). At this time, the

CXD2463R sync signal is output as shown below based on the amount by which EXT-HD is shifted. (The

phase can be shifted up to ±1/2H with respect to the falling edge of EXT-HD.)

COMP (Pin 39) outputs the result of comparing the phase of the falling edge of the shifted EXT-HD (signal

input to Pin 37) and the falling edge of the CXD2463R internal HD. The polarity is compatible with the active

filter.

∑ EIA/ODD

EXT-HD

(Pin 36 output)

(1) Same phase

(2) Delayed phase

EXT-VD

(Generated inside

the CXD2463R)

HD

(Generated inside

the CXD2463R)

EXT-SYNC

(Pin 38 input)

SFT-HD (1) to (3) are the signals after shifting EXT-HD.

1/2H 1/2H

VD

(Pin 35 output)

SFT-HD (1)

(Pin 37 input)

SFT-HD (2)

VD

HD

SYNC

(3) Advanced phase

SFT-HD (3)

VD

HD

SYNC

SYNC

(Pin 25 output)

≠ 19 ≠

CXD2463R

∑ EIA/EVEN

EXT-HD

(Pin 36 output)

(1) Same phase

(2) Delayed phase

EXT-VD

(Generated inside

the CXD2463R)

HD

(Generated inside

the CXD2463R)

EXT-SYNC

(Pin 38 input)

1/2H 1/2H

VD

(Pin 35 output)

SFT-HD (1)

(Pin 37 input)

SFT-HD (2)

VD

HD

SYNC

(3) Advanced phase

SFT-HD (3)

VD

HD

SYNC

SYNC

(Pin 25 output)

≠ 20 ≠

CXD2463R

∑ CCIR/ODD

EXT-HD

(Pin 36 output)

(1) Same phase

(2) Delayed phase

EXT-VD

(Generated inside

the CXD2463R)

HD

(Generated inside

the CXD2463R)

EXT-SYNC

(Pin 38 input)

1/2H 1/2H

VD

(Pin 35 output)

SFT-HD (1)

(Pin 37 input)

SFT-HD (2)

VD

HD

SYNC

(3) Advanced phase

SFT-HD (3)

VD

HD

SYNC

SYNC

(Pin 25 output)

≠ 21 ≠

CXD2463R

∑ CCIR/EVEN

EXT-HD

(Pin 36 output)

(1) Same phase

(2) Delayed phase

EXT-VD

(Generated inside

the CXD2463R)

HD

(Generated inside

the CXD2463R)

EXT-SYNC

(Pin 38 input)

1/2H 1/2H

VD

(Pin 35 output)

SFT-HD (1)

(Pin 37 input)

SFT-HD (2)

VD

HD

SYNC

(3) Advanced phase

SFT-HD (3)

VD

HD

SYNC

SYNC

(Pin 25 output)

≠ 22 ≠

CXD2463R

H

D

F

I

E

L

D

.

O

F

I

E

L

D

.

E

V

D

S

Y

N

C

B

L

K

V

1

V

2

V

3

V

4

5

1

0

H

C

C

D

O

U

T

7

6

0

H

C

C

D

O

U

T

C

L

P

1

1

3

2

4

1

3

2

4

4

9

2

4

9

3

4

9

2

4

9

3

C

L

P

2

9

H

2

0

H

4

9

4

H

D

F

I

E

L

D

.

E

F

I

E

L

D

.

O

V

D

S

Y

N

C

B

L

K

V

1

V

2

V

3

V

4

5

1

0

H

C

C

D

O

U

T

7

6

0

H

C

C

D

O

U

T

C

L

P

1

4

9

1

2

4

9

3

4

9

2

1

3

1

3

2

4

9

3

4

9

4

C

L

P

2

9

H

2

0

H

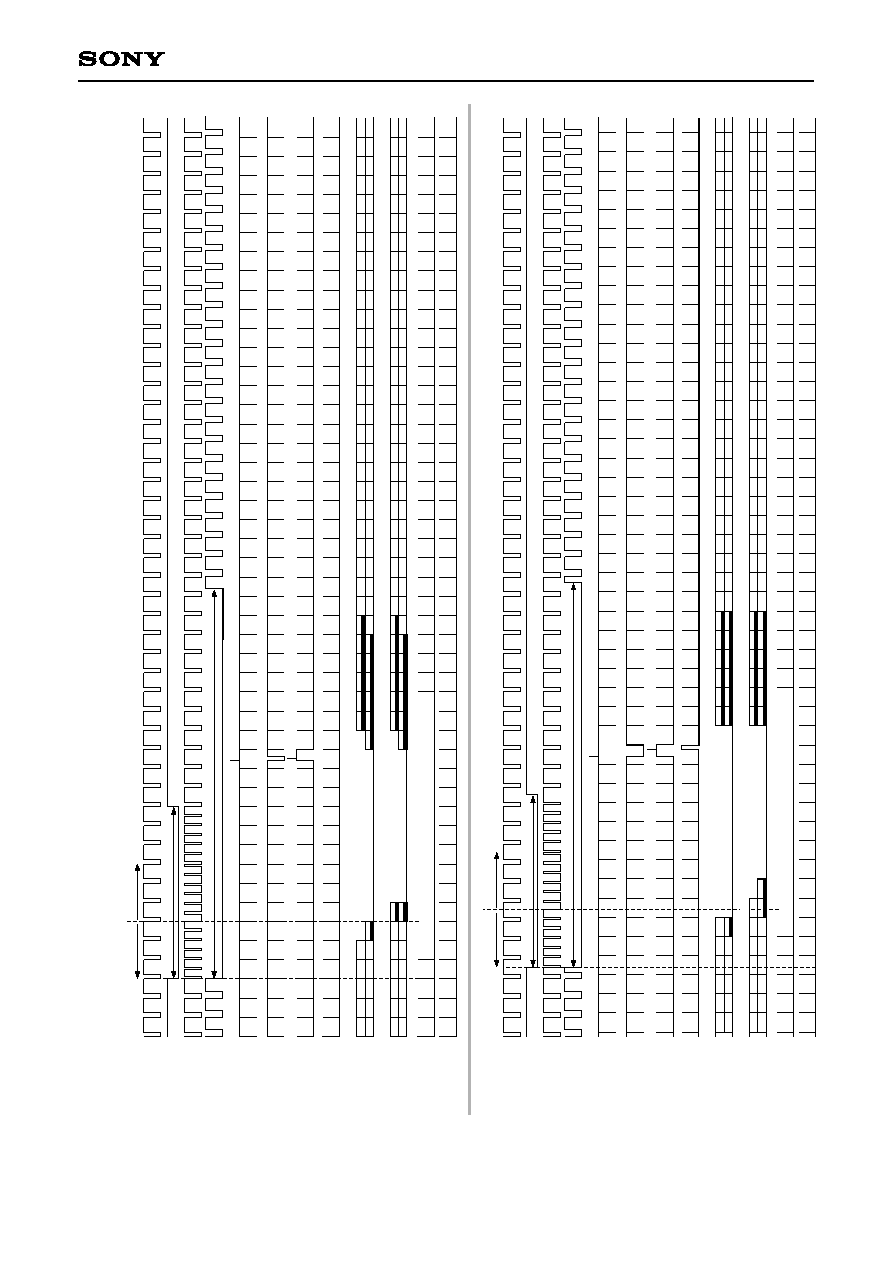

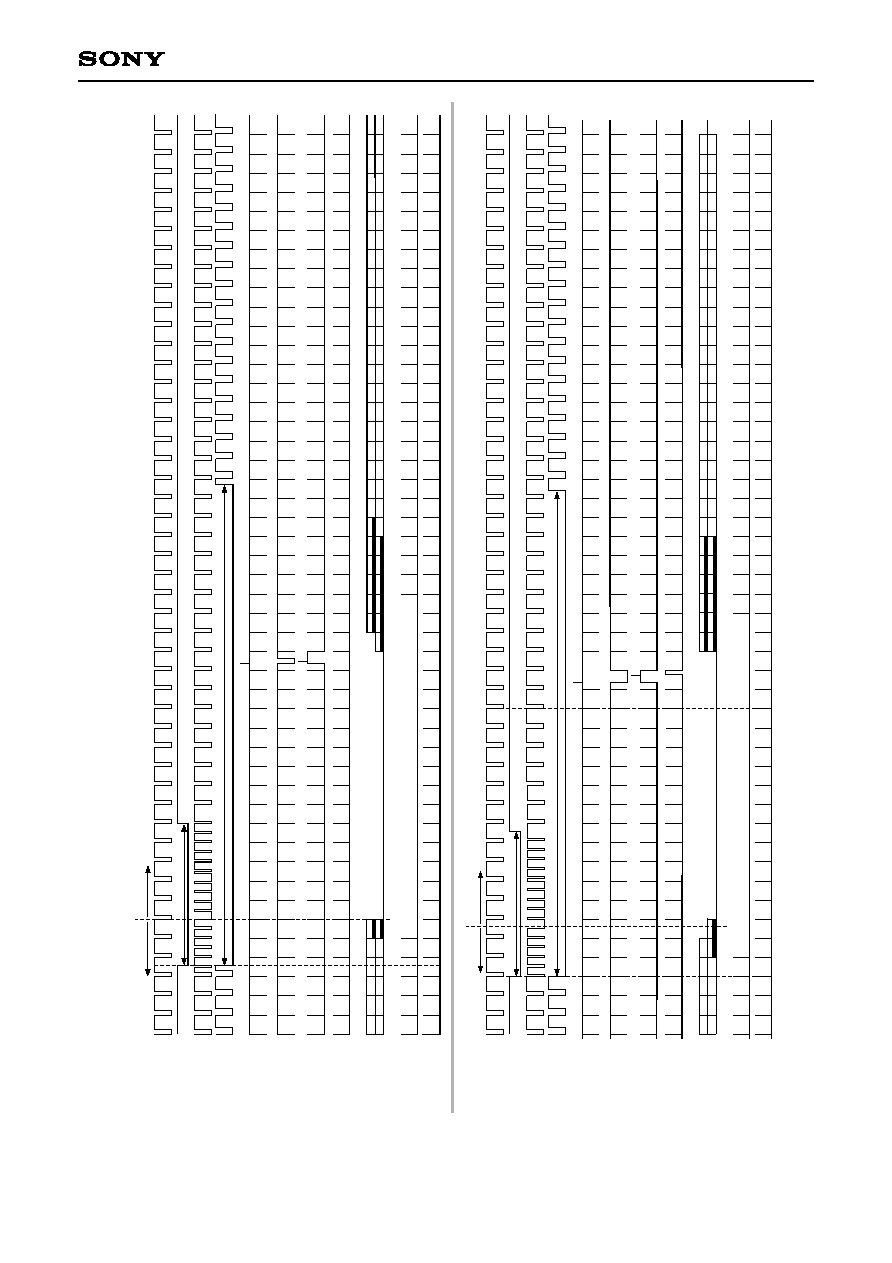

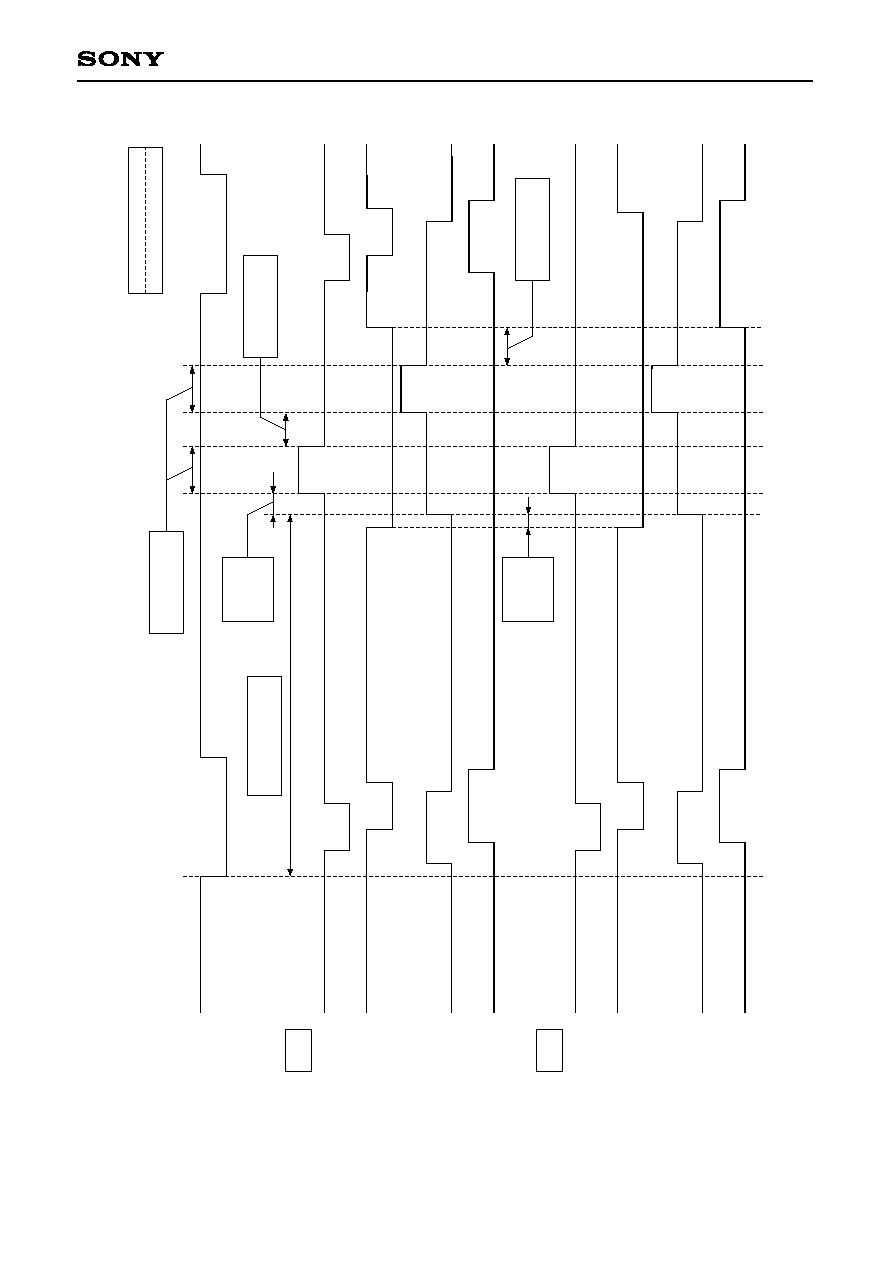

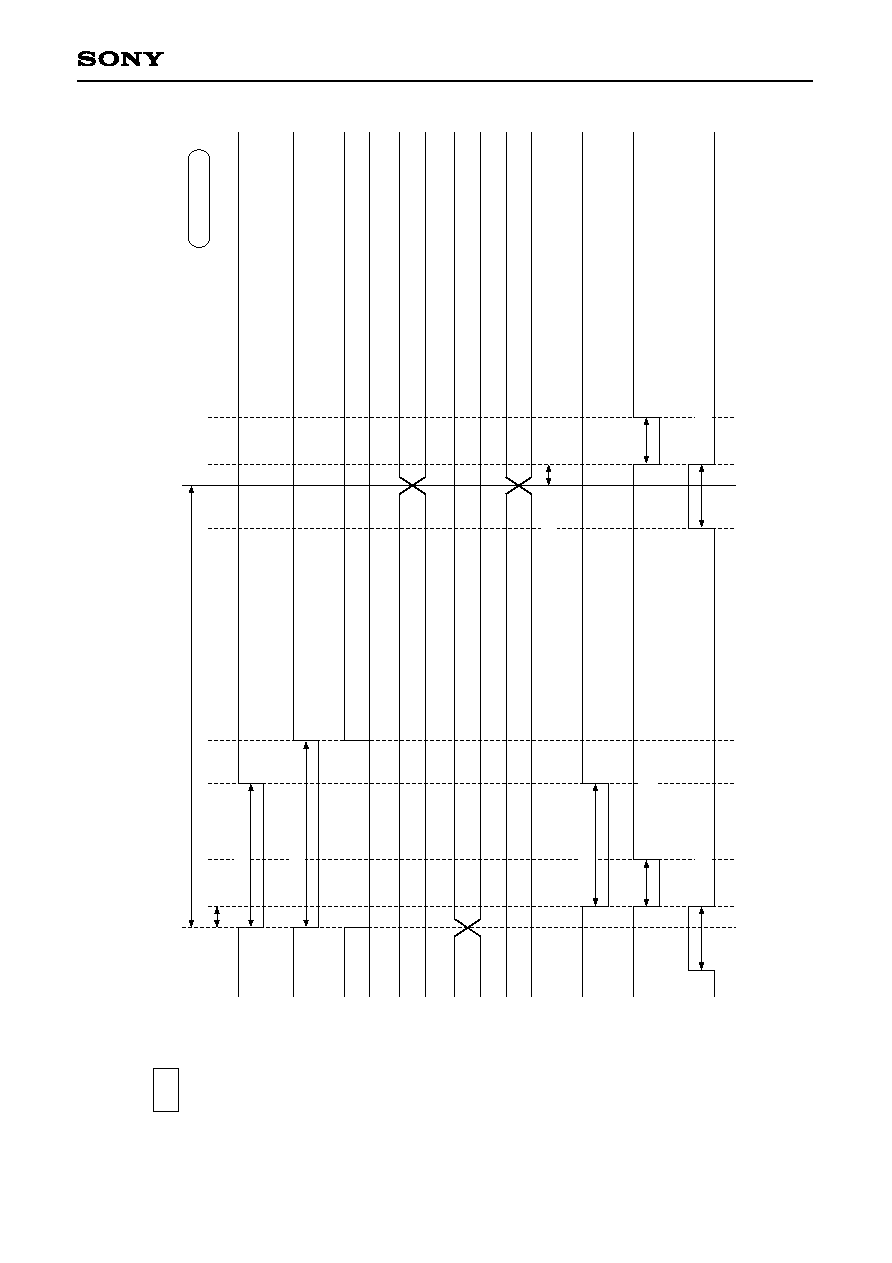

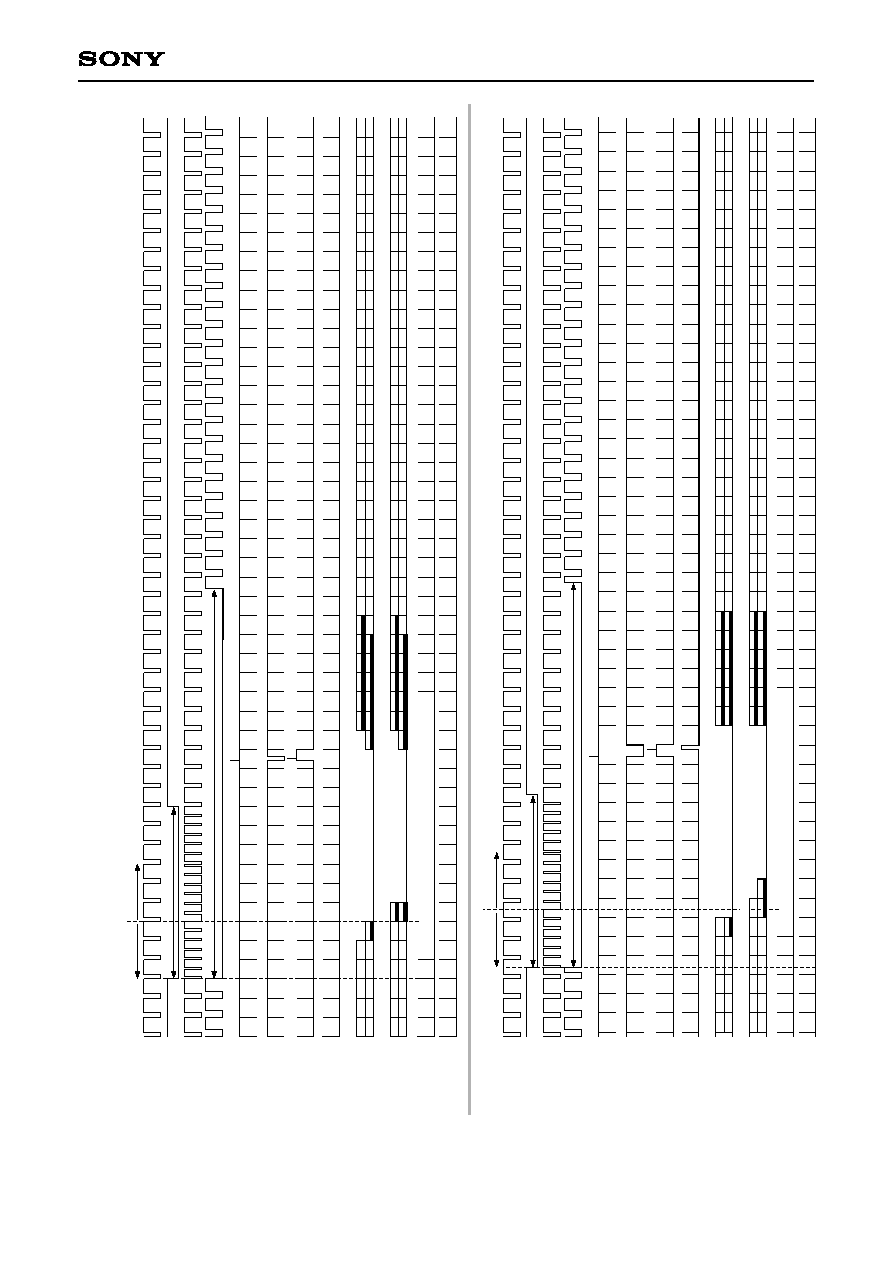

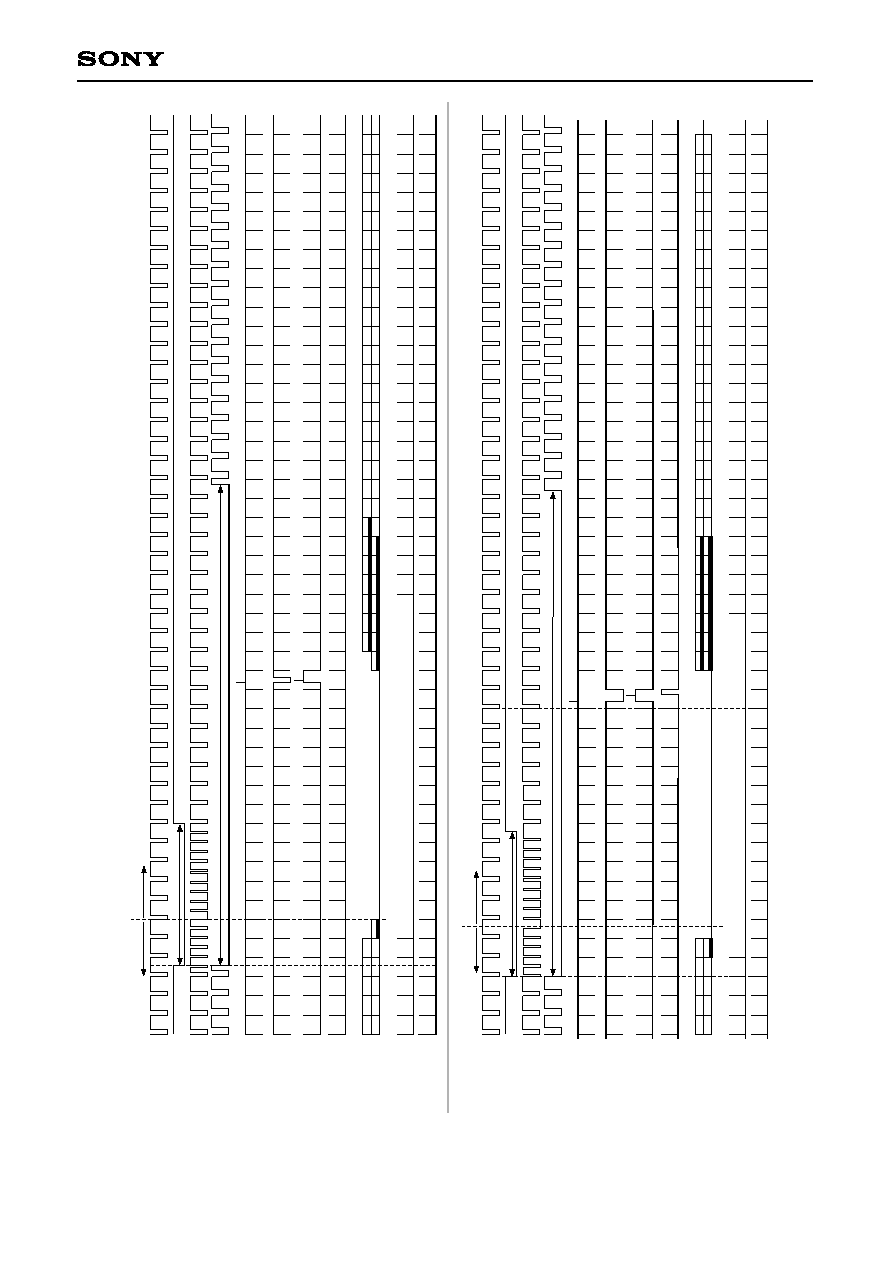

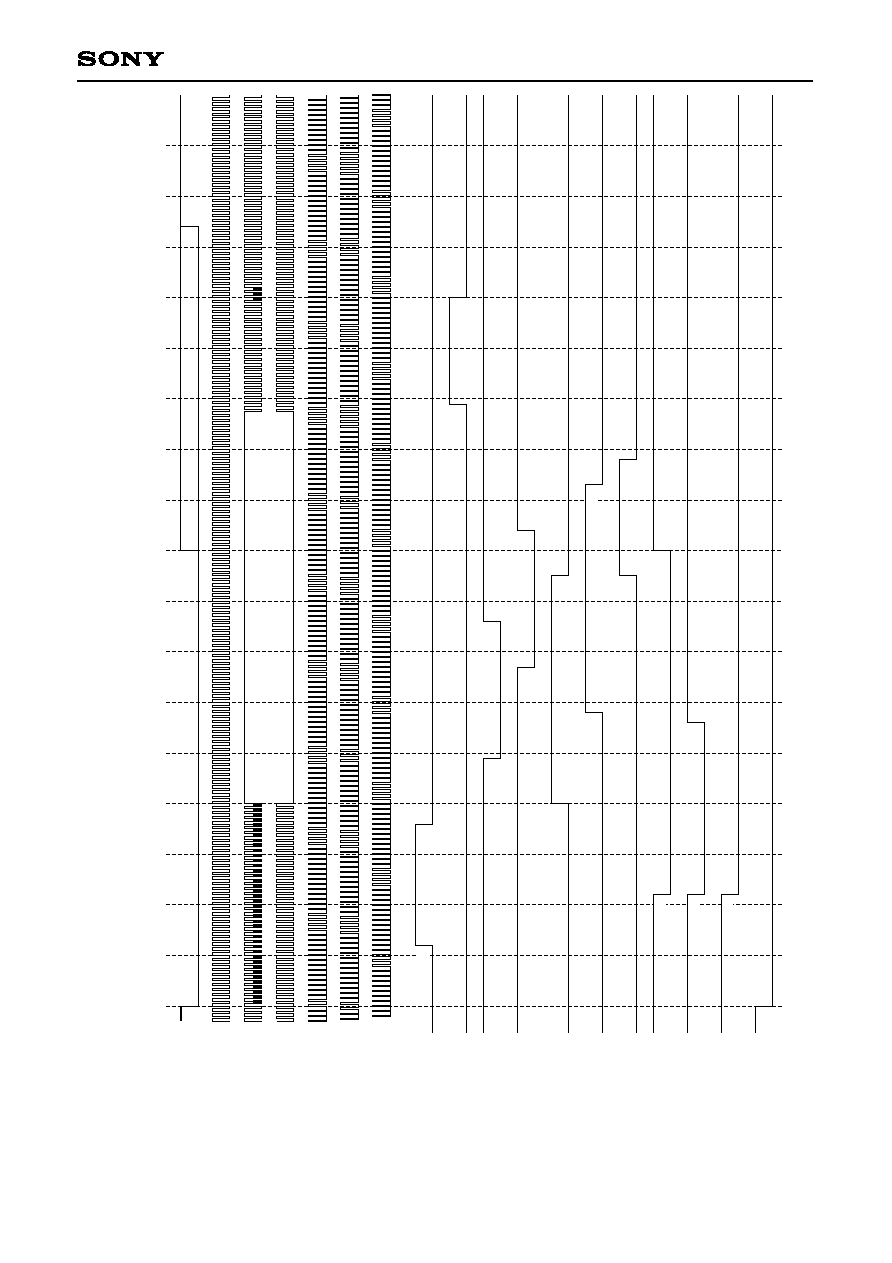

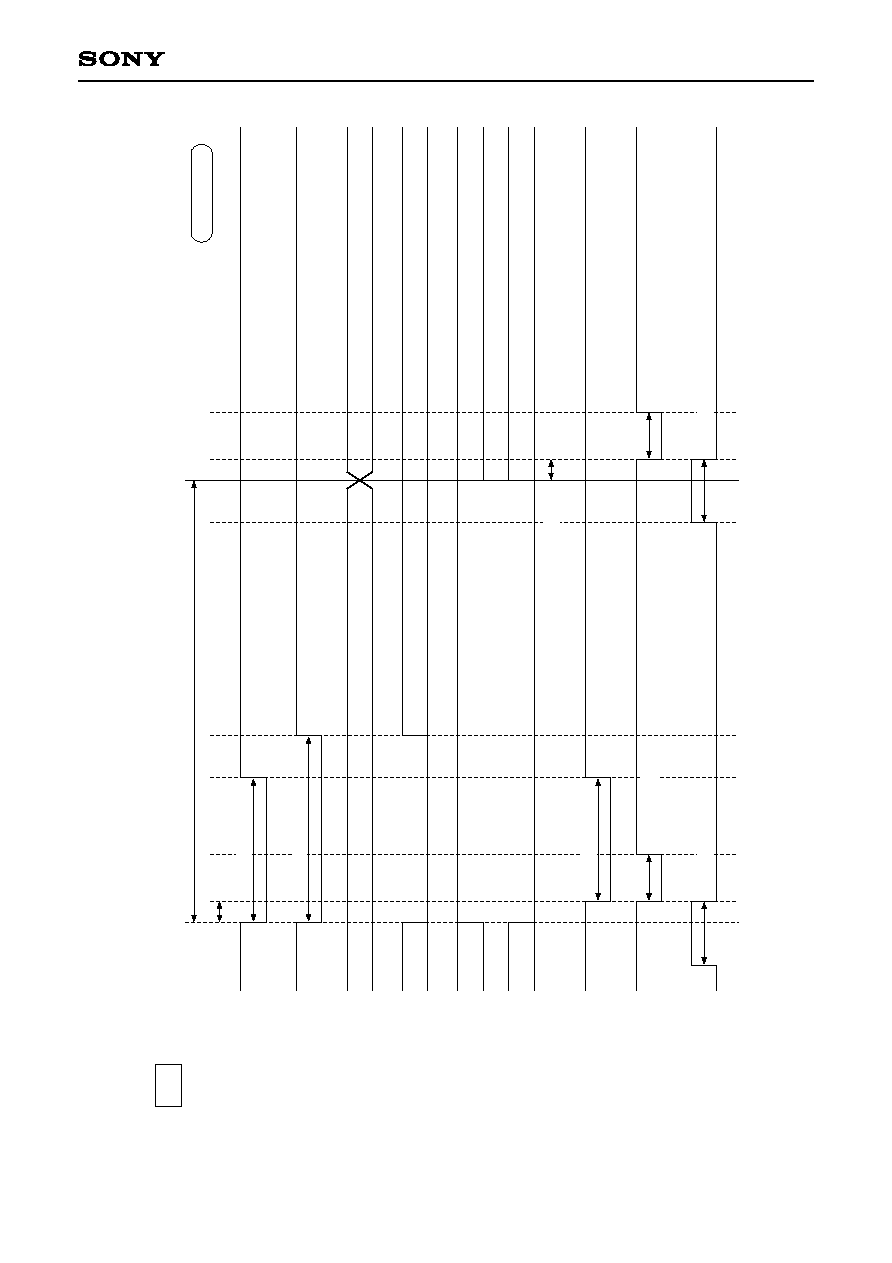

Timing Generator + Sync Generator Block Timing Chart

Vertical Direction EIA (during 510H/760H CCD drive)

≠ 23 ≠

CXD2463R

H

D

F

I

E

L

D

.

E

F

I

E

L

D

.

O

V

D

S

Y

N

C

B

L

K

V

1

V

2

V

3

V

4

5

1

0

H

C

C

D

O

U

T

5

8

1

5

8

2

5

8

3

2

1

3

7

.

5

H

2

5

H

H

D

F

I

E

L

D

.

O

F

I

E

L

D

.

E

V

D

S

Y

N

C

B

L

K

7

.

5

H

2

5

H

1

3

2

4

5

8

2

5

8

3

V

1

V

2

V

3

V

4

5

1

0

H

C

C

D

O

U

T

C

L

P

1

C

L

P

2

C

L

P

1

C

L

P

2

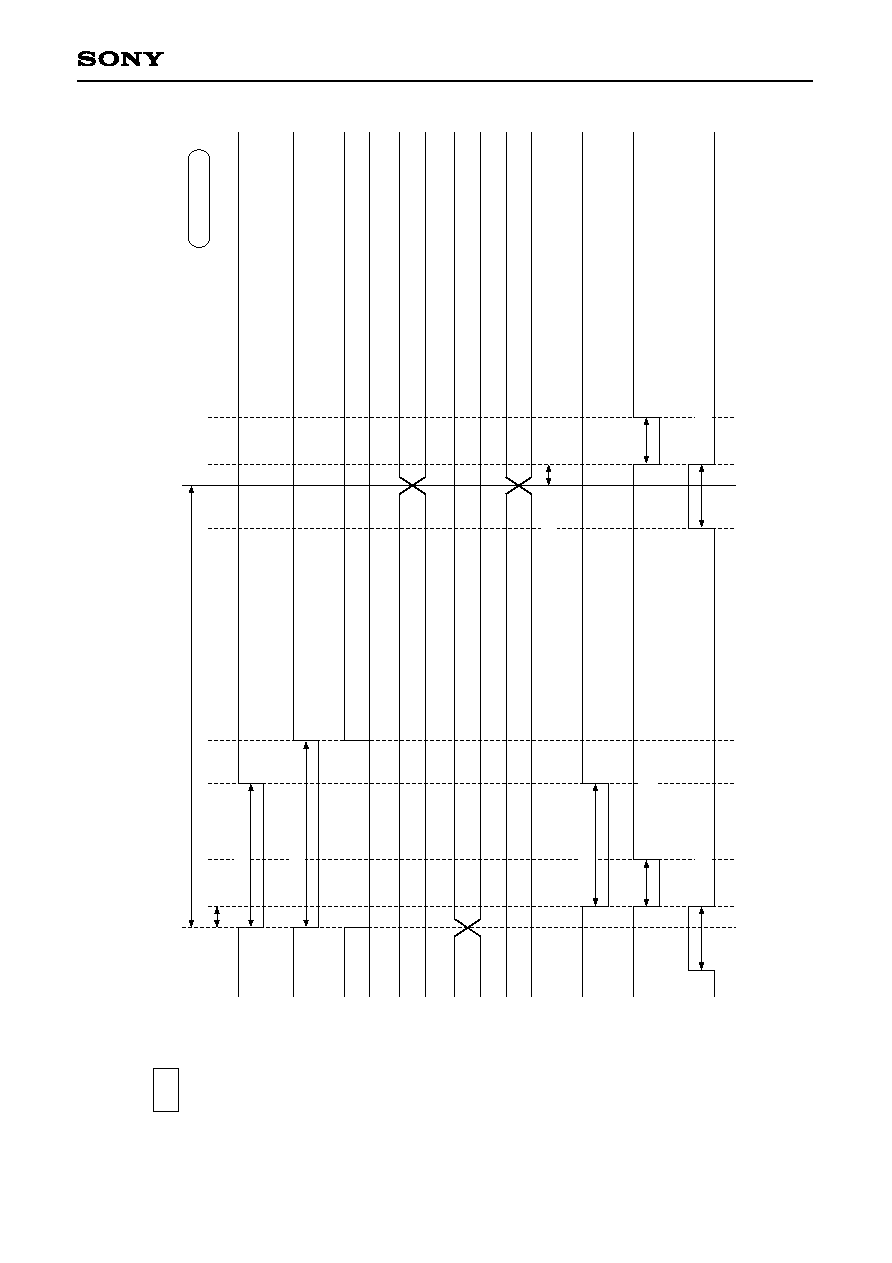

Timing Generator + Sync Generator Block Timing Chart

Vertical Direction CCIR (during 510H CCD drive)

≠ 24 ≠

CXD2463R

H

D

F

I

E

L

D

.

E

F

I

E

L

D

.

O

V

D

S

Y

N

C

B

L

K

V

1

V

2

V

3

V

4

7

6

0

H

C

C

D

O

U

T

5

8

1

5

8

2

5

8

3

2

1

3

7

.

5

H

2

5

H

H

D

F

I

E

L

D

.

O

F

I

E

L

D

.

E

V

D

S

Y

N

C

B

L

K

7

.

5

H

2

5

H

1

2

5

8

2

5

8

3

V

1

V

2

V

3

V

4

7

6

0

H

C

C

D

O

U

T

C

L

P

1

C

L

P

2

C

L

P

1

C

L

P

2

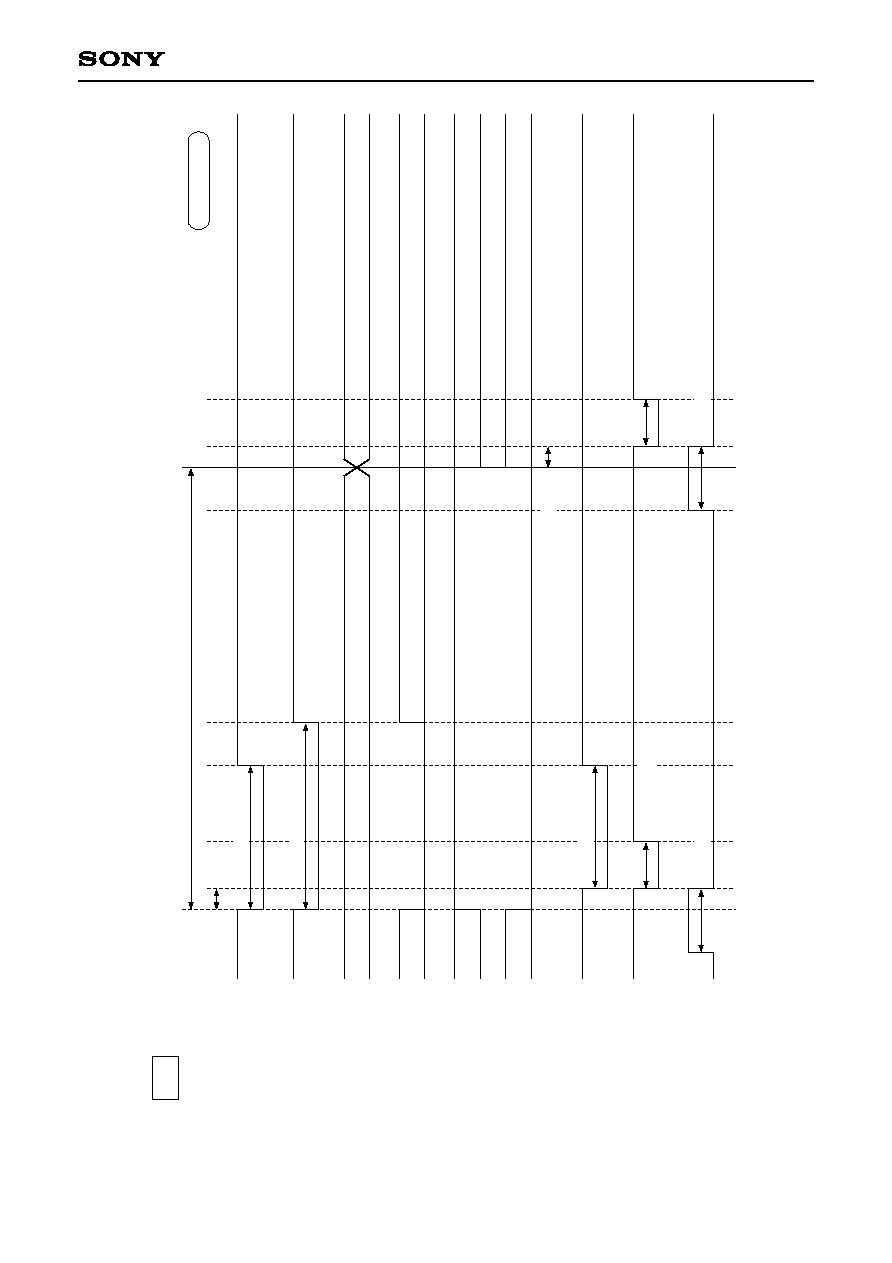

Timing Generator + Sync Generator Block Timing Chart

Vertical Direction CCIR (during 760H CCD drive)

≠ 25 ≠

CXD2463R

H

D

/

B

L

K

M

C

K

(

I

n

t

e

r

n

a

l

c

l

o

c

k

)

H

1

H

2

R

G

S

H

P

S

H

D

V

1

V

2

V

3

V

4

S

U

B

H

S

Y

N

C

E

Q

V

S

Y

N

C

V

D

C

L

P

1

C

L

P

2

0

1

0

2

0

3

0

4

0

5

0

6

0

7

0

8

0

9

0

1

0

0

1

1

0

1

0

4

M

C

K

=

1

0

4

.

8

8

n

s

5

9

7

9

2

6

8

0

9

4

5

0

3

2

6

2

4

4

5

6

2

6

6

8

3

8

7

2

5

5

5

9

1

4

3

6

1

4

1

4

2

3

7

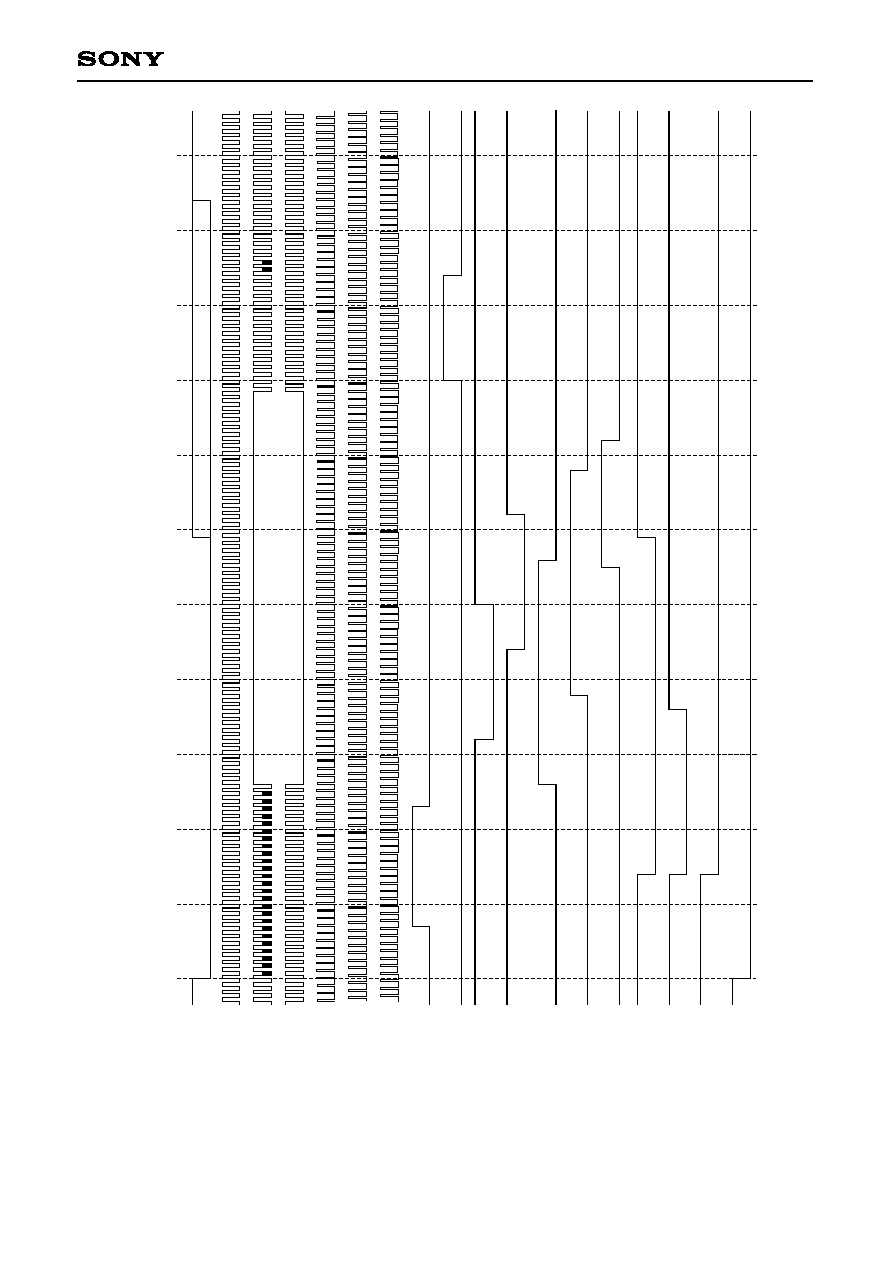

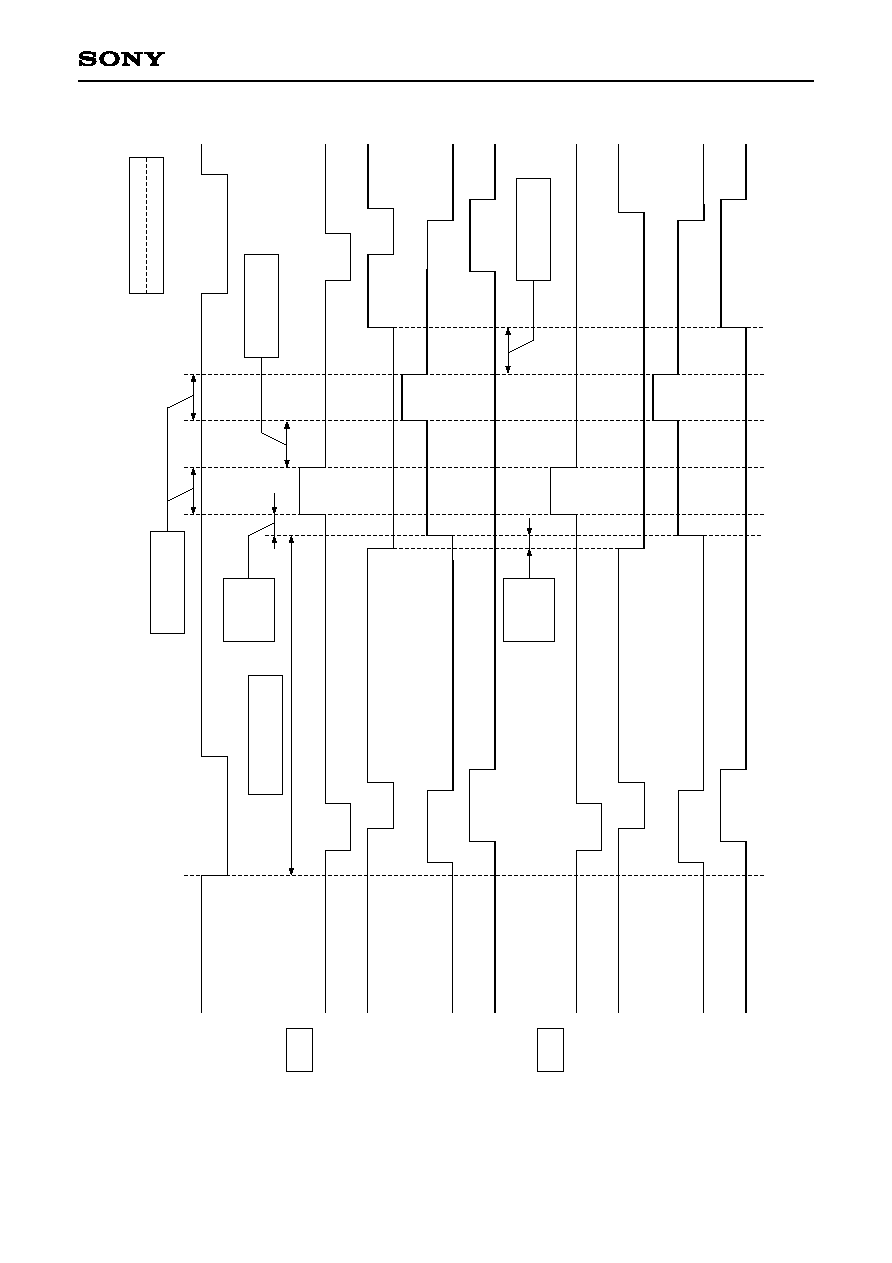

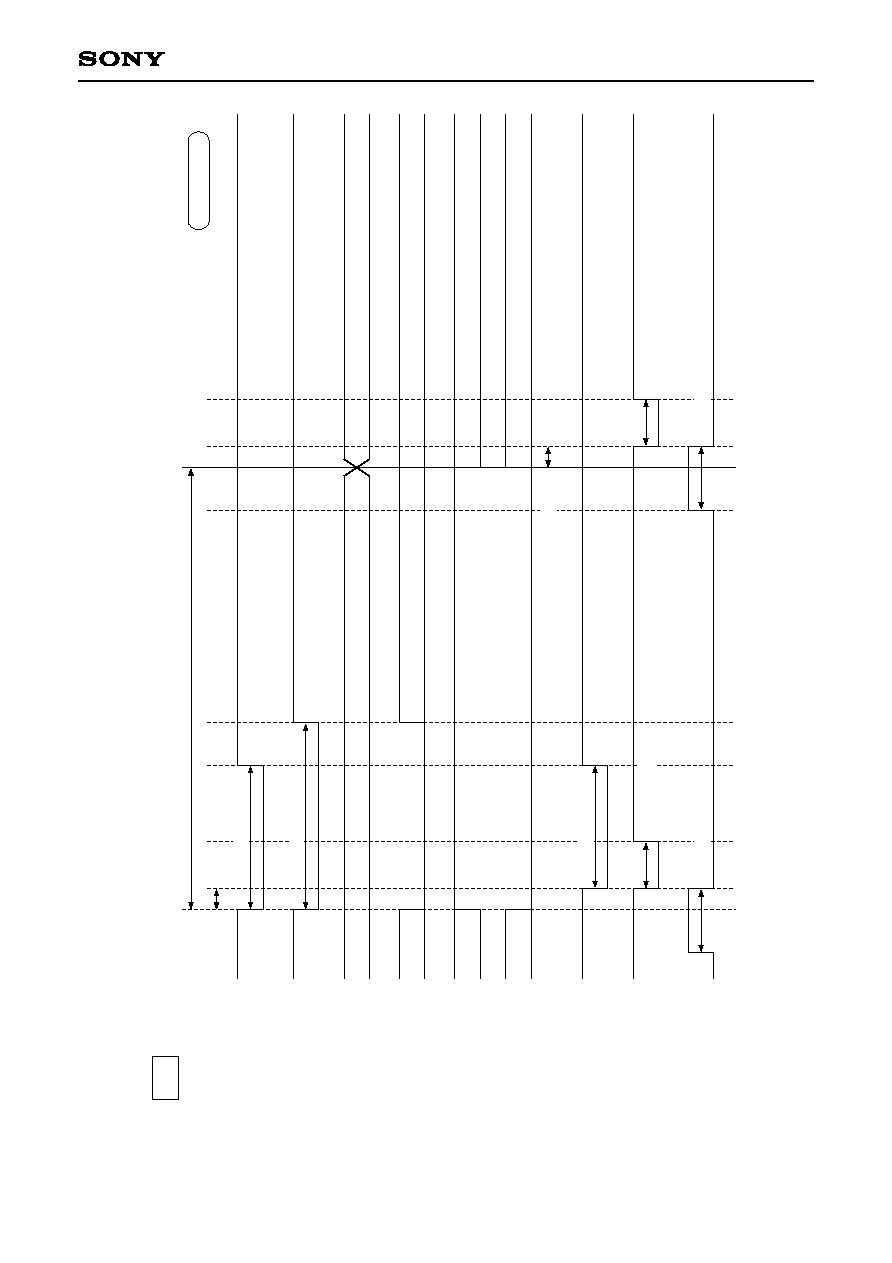

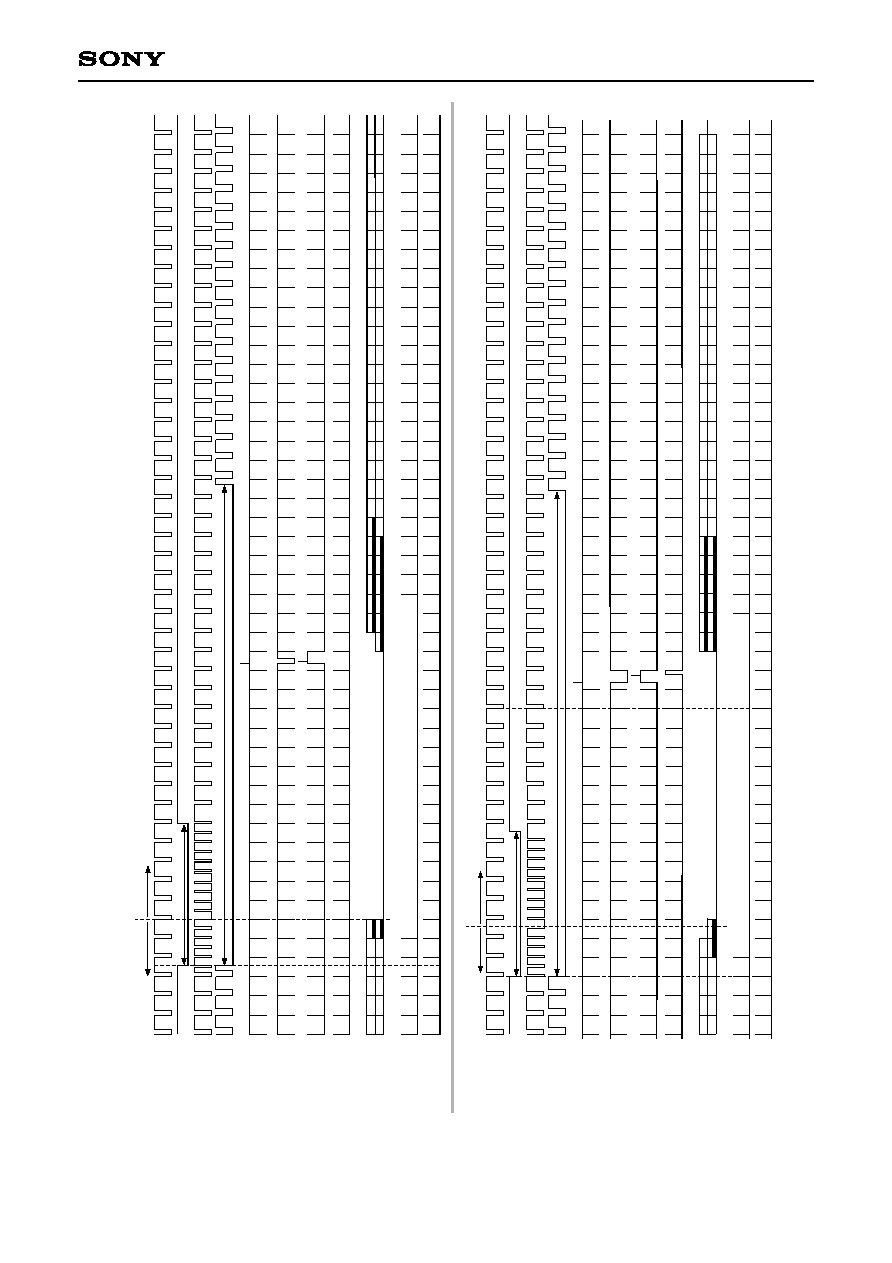

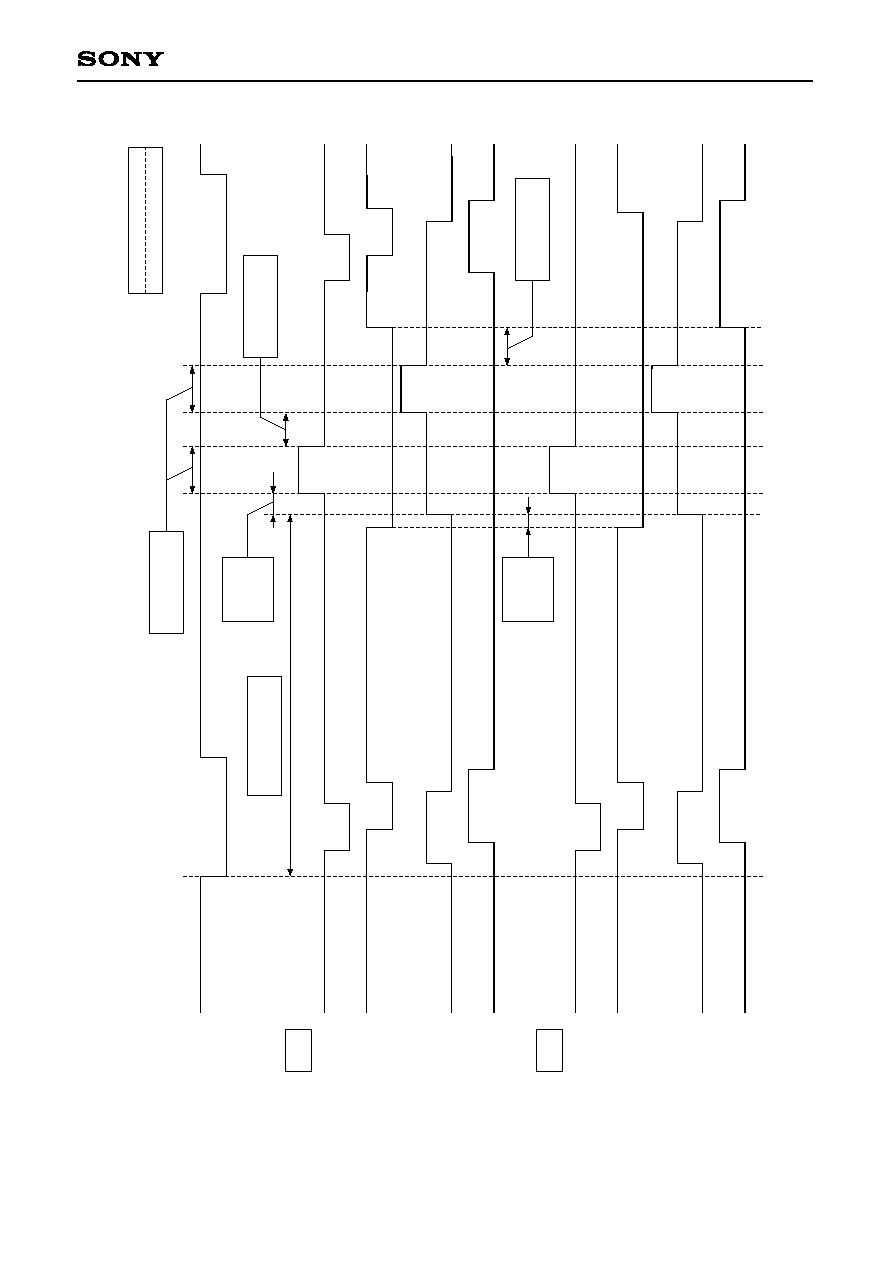

Timing Generator + Sync Generator Block Timing Chart

Horizontal Direction EIA (during 510H CCD drive)

≠ 26 ≠

CXD2463R

H

D

/

B

L

K

M

C

K

(

I

n

t

e

r

n

a

l

c

l

o

c

k

)

H

1

H

2

R

G

S

H

P

S

H

D

V

1

V

2

V

3

V

4

S

U

B

H

S

Y

N

C

E

Q

V

S

Y

N

C

V

D

C

L

P

1

C

L

P

2

0

1

0

2

0

3

0

4

0

5

0

6

0

7

0

8

0

9

0

1

0

0

1

1

0

1

1

4

5

9

8

4

3

1

8

5

9

9

5

5

3

7

6

7

4

9

6

1

3

1

7

3

4

3

7

7

6

0

5

9

1

4

3

6

1

4

1

4

2

3

7

M

C

K

=

1

0

5

.

6

1

n

s

Timing Generator + Sync Generator Block Timing Chart

Horizontal Direction CCIR (during 510H CCD drive)

≠ 27 ≠

CXD2463R

0

1

0

2

0

9

0

8

0

1

4

0

1

5

0

1

6

0

1

7

0

1

0

0

6

0

5

0

4

0

3

0

7

0

1

1

0

1

2

0

1

3

0

1

5

4

9

0

4

0

1

1

8

3

6

1

2

1

4

0

1

1

9

7

6

4

9

9

4

6

7

8

5

4

0

1

0

3

5

8

1

0

8

8

5

9

0

2

2

5

6

2

2

2

2

H

D

/

B

L

K

M

C

K

(

I

n

t

e

r

n

a

l

c

l

o

c

k

)

H

1

H

2

R

G

S

H

P

S

H

D

V

1

V

2

V

3

V

4

S

U

B

H

S

Y

N

C

E

Q

V

S

Y

N

C

V

D

C

L

P

1

C

L

P

2

M

C

K

=

6

9

.

8

4

n

s

Timing Generator + Sync Generator Block Timing Chart

Horizontal Direction EIA (during 760H CCD drive)

≠ 28 ≠

CXD2463R

0

1

0

2

0

9

0

8

0

1

4

0

1

5

0

1

6

0

1

7

0

1

0

0

6

0

5

0

4

0

3

0

7

0

1

1

0

1

2

0

1

3

0

1

6

9

9

0

4

0

1

3

2

3

6

1

2

1

5

4

8

4

5

1

1

0

6

7

3

9

5

4

0

1

1

7

6

2

1

2

2

9

5

9

0

2

2

5

6

2

2

2

2

H

D

/

B

L

K

M

C

K

(

I

n

t

e

r

n

a

l

c

l

o

c

k

)

H

1

H

2

R

G

S

H

P

S

H

D

V

1

V

2

V

3

V

4

S

U

B

H

S

Y

N

C

E

Q

V

S

Y

N

C

V

D

C

L

P

1

C

L

P

2

M

C

K

=

7

0

.

4

8

n

s

1

3

3

Timing Generator + Sync Generator Block Timing Chart

Horizontal Direction CCIR (during 760H CCD drive)

≠ 29 ≠

CXD2463R

H

D

E

:

2

.

5

1

µ

s

C

:

2

.

5

3

µ

s

(

2

4

C

K

)

V

1

O

D

D

V

2

V

3

V

4

V

1

E

V

E

N

V

2

V

3

V

4

E

:

1

.

5

7

µ

s

C

:

1

.

5

8

µ

s

(

1

5

C

K

)

E

:

1

.

9

9

µ

s

C

:

2

.

0

0

µ

s

(

1

9

C

K

)

E

:

E

I

A

1

C

K

=

1

0

4

.

8

8

n

s

C

:

C

C

I

R

1

C

K

=

1

0

5

.

6

1

n

s

E

:

3

8

.

3

8

µ

s

C

:

3

8

.

6

5

µ

s

(

3

6

6

C

K

)

(

1

2

C

K

)

E

:

1

.

2

6

µ

s

C

:

1

.

2

7

µ

s

(

3

C

K

)

E

:

0

.

3

2

µ

s

C

:

0

.

3

2

µ

s

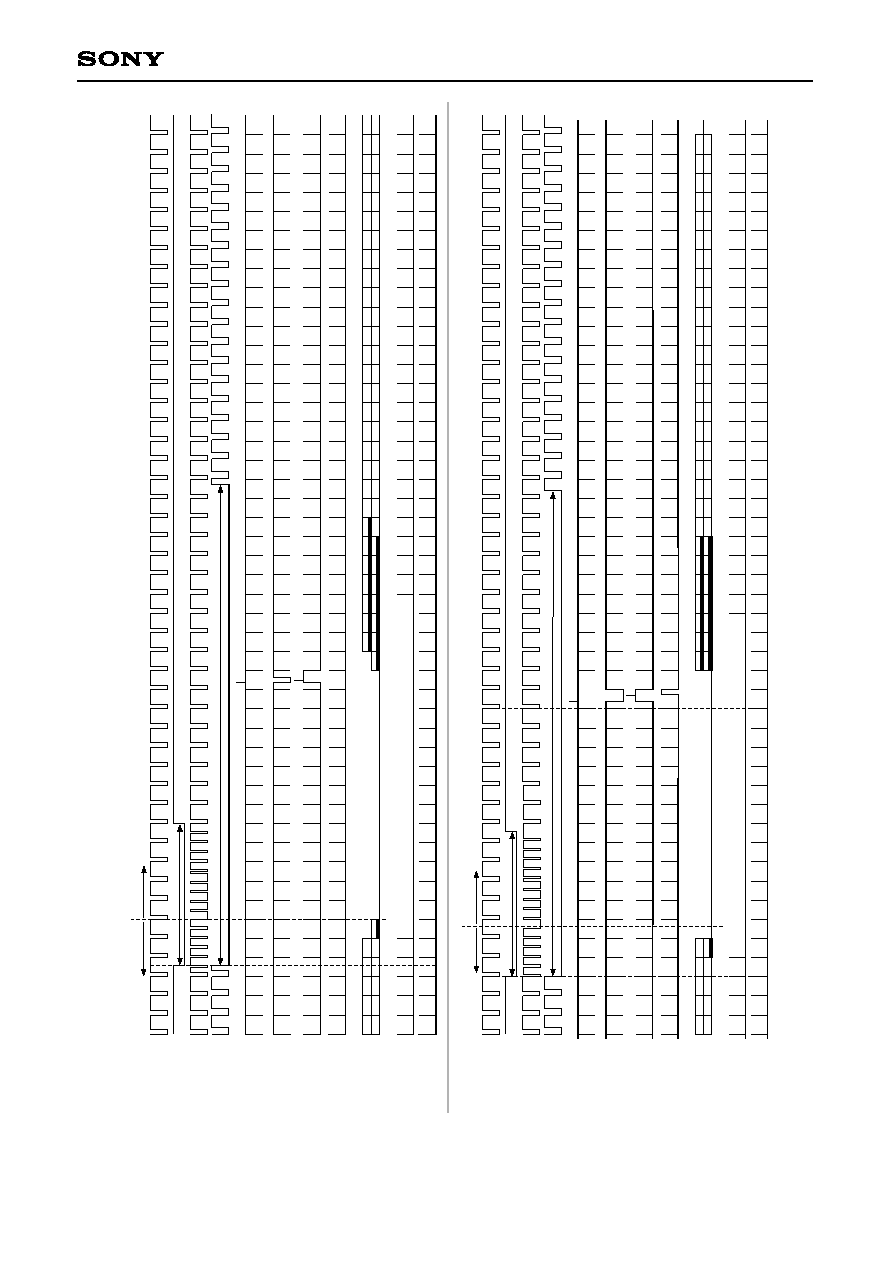

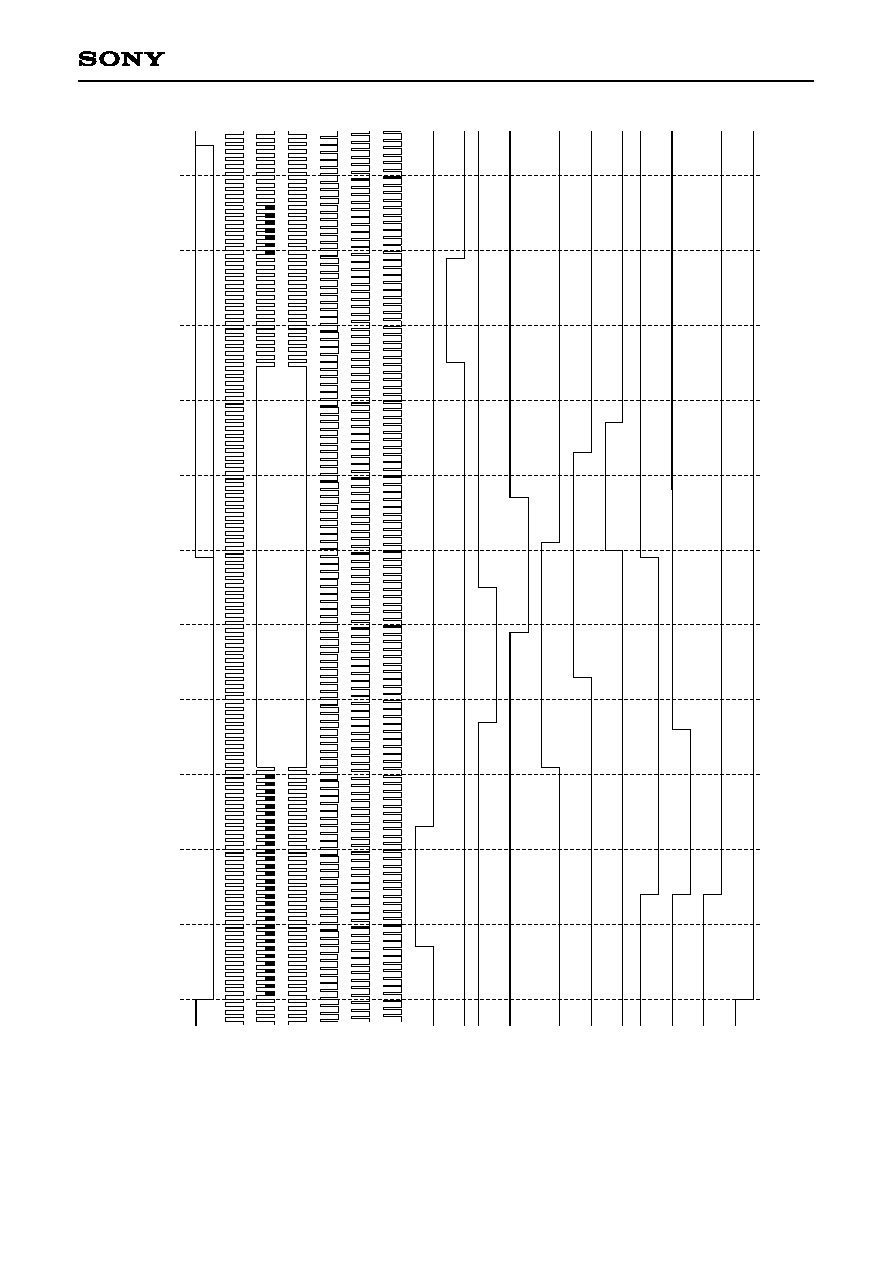

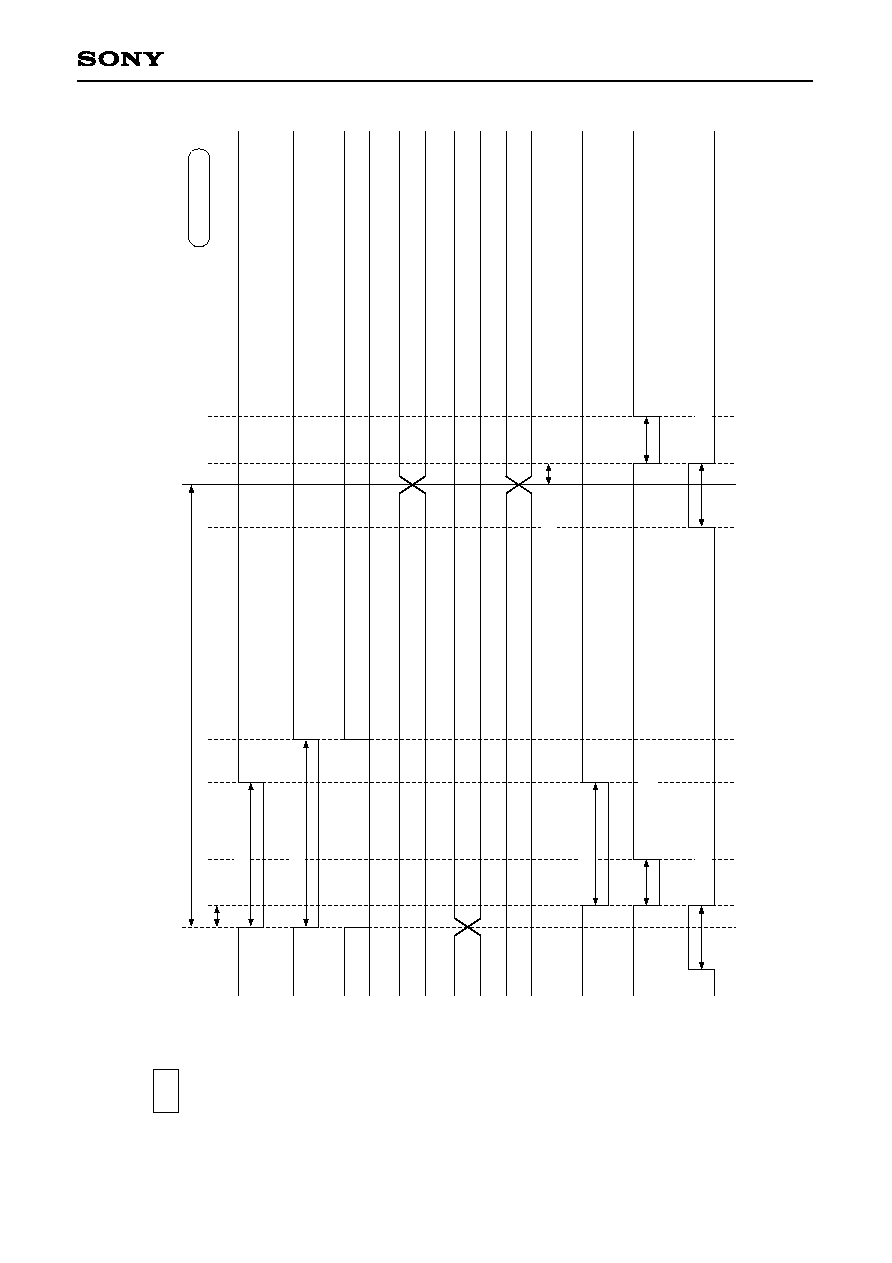

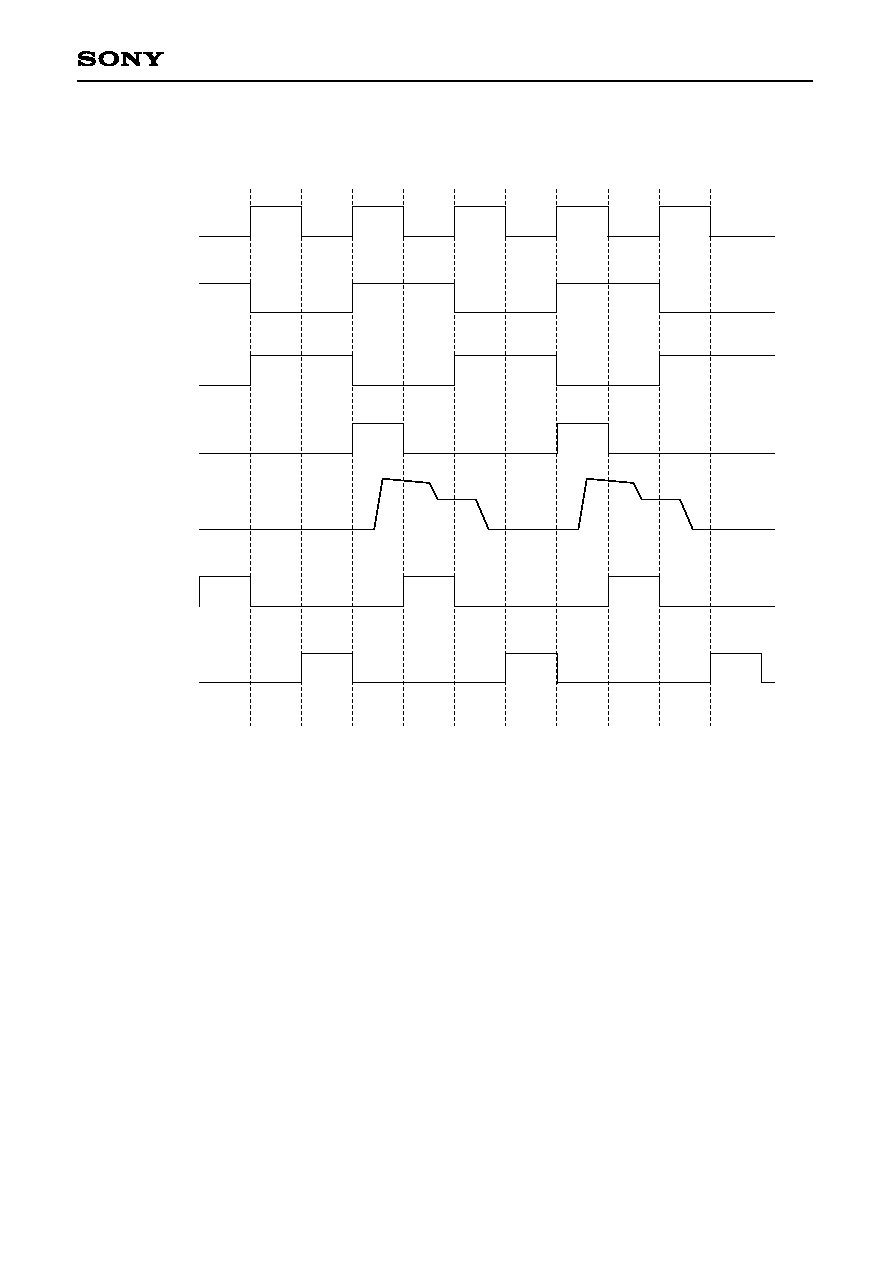

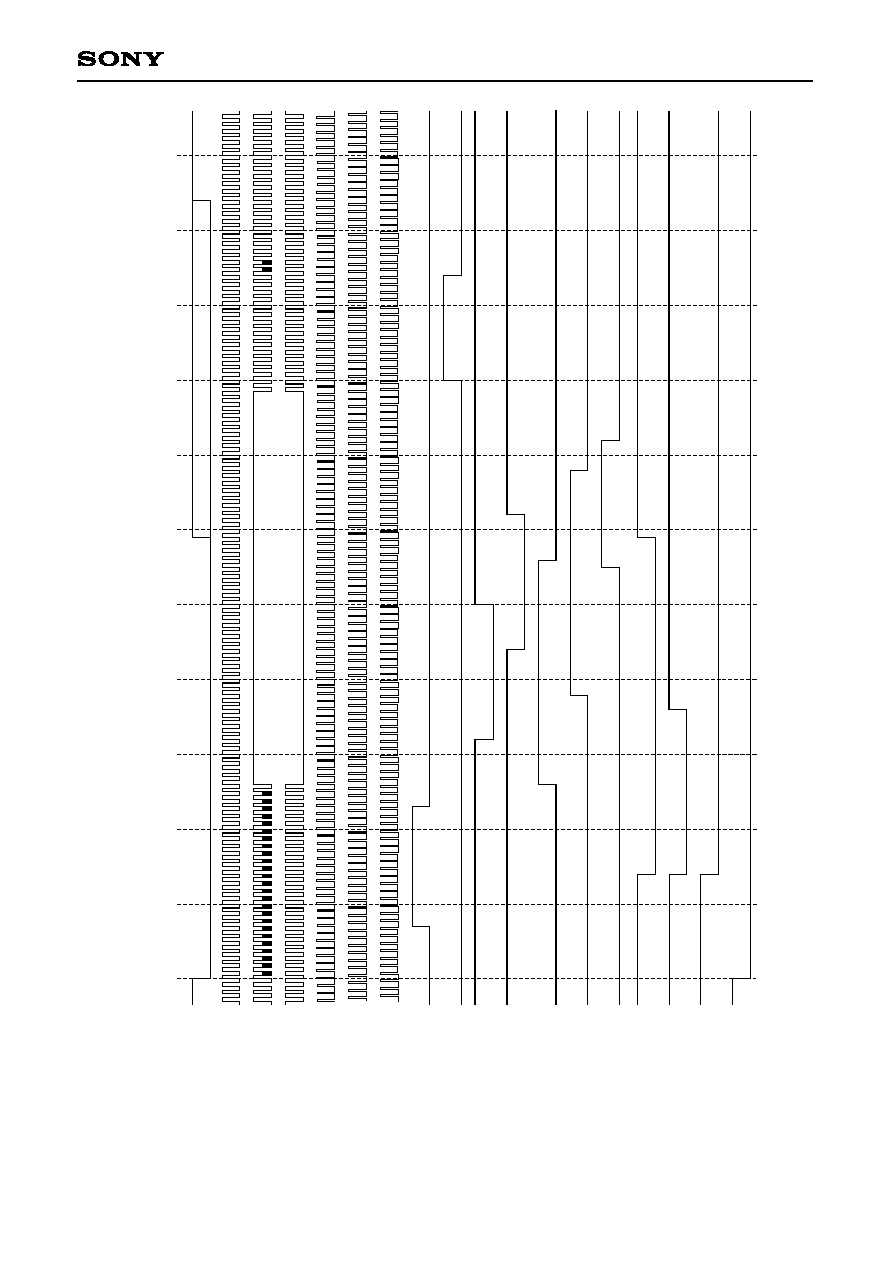

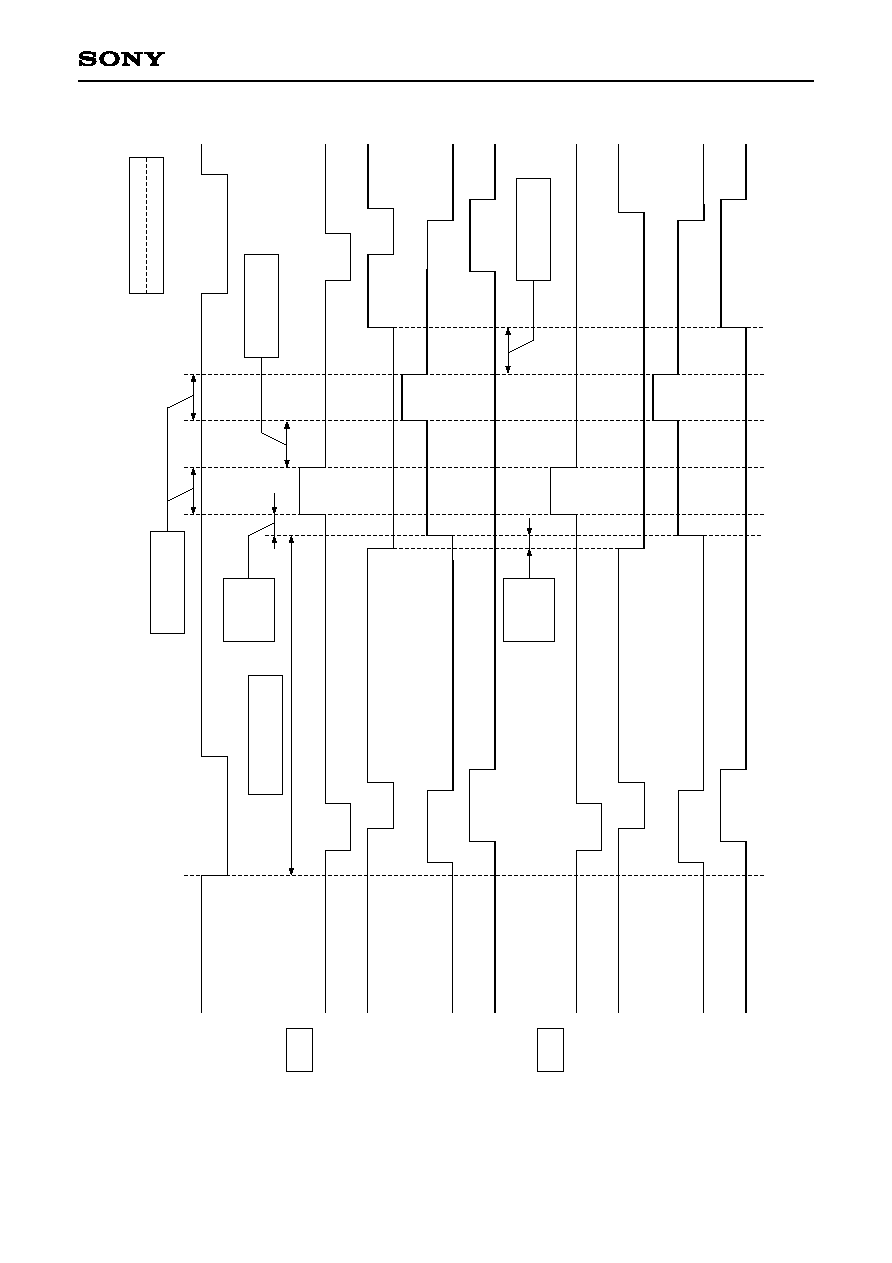

Timing Generator + Sync Generator Block Timing Chart

Charge Readout Timing

Field Accumulation (during 510H CCD drive)

≠ 30 ≠

CXD2463R

H

D

E

:

2

.

5

1

µ

s

C

:

2

.

5

4

µ

s

(

3

6

C

K

)

V

1

O

D

D

V

2

V

3

V

4

V

1

E

V

E

N

V

2

V

3

V

4

E

:

2

.

5

1

µ

s

C

:

2

.

5

4

µ

s

(

3

6

C

K

)

E

:

2

.

5

1

µ

s

C

:

2

.

5

4

µ

s

(

3

6

C

K

)

E

:

E

I

A

1

C

K

=

6

9

.

8

4

n

s

C

:

C

C

I

R

1

C

K

=

7

0

.

4

8

n

s

E

:

4

0

.

5

6

µ

s

C

:

4

0

.

9

5

µ

s

(

5

8

1

C

K

)

(

2

3

C

K

)

E

:

1

.

6

1

µ

s

C

:

1

.

6

2

µ

s

(

3

C

K

)

E

:

0

.

2

1

µ

s

C

:

0

.

2

1

µ

s

Timing Generator + Sync Generator Block Timing Chart

Charge Readout Timing

Field Accumulation (during 760H CCD drive)

≠ 31 ≠

CXD2463R

H

D

3

1

.

7

8

µ

s

(

3

0

3

C

K

)

1

.

4

7

µ

s

(

1

4

C

K

)

1

/

2

H

E

I

A

H

S

Y

N

C

E

Q

V

S

Y

N

C

B

L

K

(

H

D

)

B

L

K

(

O

D

D

)

B

L

K

(

E

V

E

N

)

V

D

(

E

V

E

N

)

V

D

(

O

D

D

)

6

.

1

9

µ

s

(

5

9

C

K

)

4

.

7

2

µ

s

(

4

5

C

K

)

2

.

3

0

µ

s

(

2

2

C

K

)

4

.

7

2

µ

s

(

4

5

C

K

)

2

.

3

0

µ

s

(

2

2

C

K

)

1

.

4

7

µ

s

(

1

4

C

K

)

1

C

K

=

1

0

4

.

8

8

n

s

4

.

7

2

µ

s

(

4

5

C

K

)

1

0

.

9

0

µ

s

(

1

0

4

C

K

)

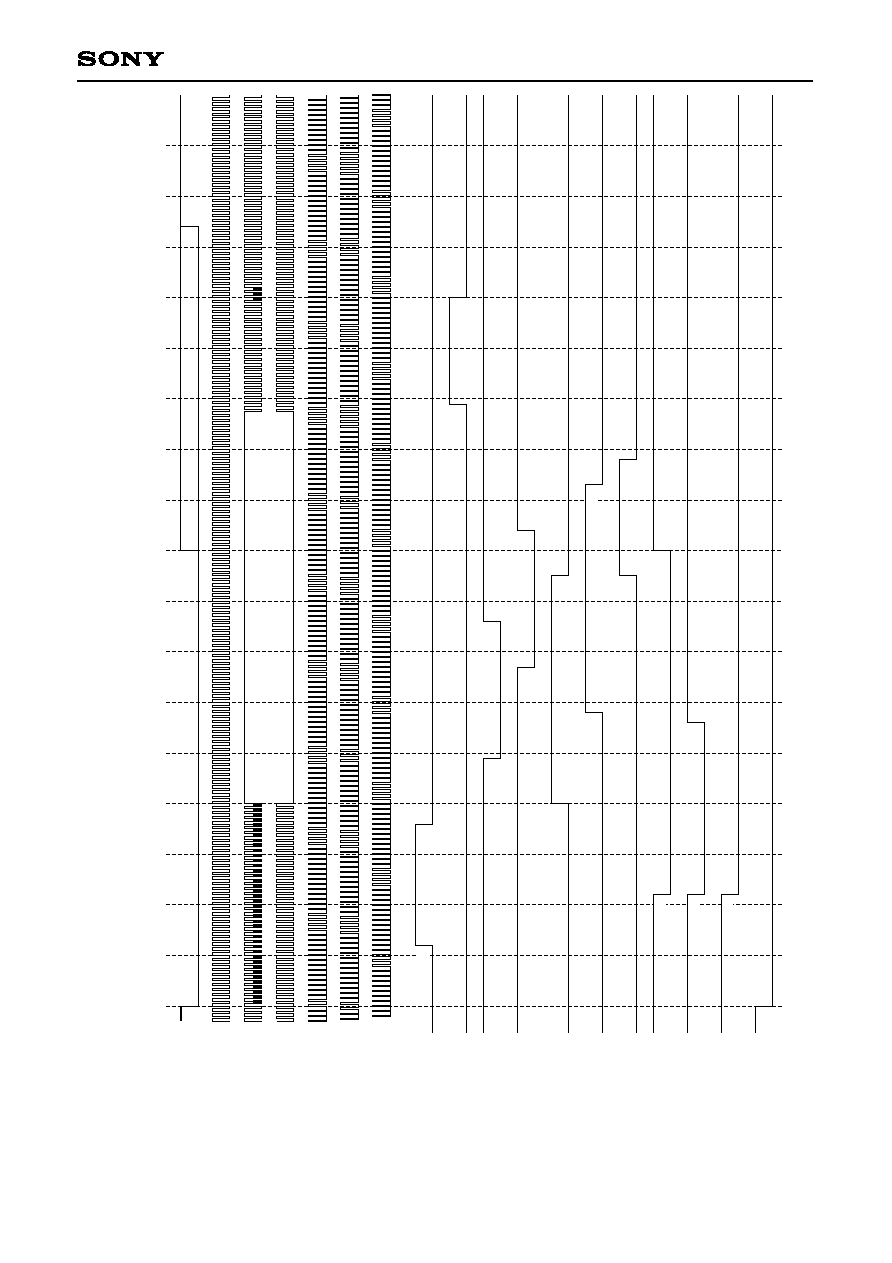

Timing Generator + Sync Generator Block Timing Chart

Effective Horizontal Period (during 510H CCD drive)

≠ 32 ≠

CXD2463R

H

D

3

2

.

0

0

µ

s

(

3

0

3

C

K

)

1

.

4

8

µ

s

(

1

4

C

K

)

1

/

2

H

C

C

I

R

H

S

Y

N

C

E

Q

V

S

Y

N

C

B

L

K

(

H

D

)

B

L

K

(

O

D

D

)

V

D

(

E

V

E

N

)

V

D

(

O

D

D

)

B

L

K

(

E

V

E

N

)

6

.

2

3

µ

s

(

5

9

C

K

)

4

.

7

5

µ

s

(

4

5

C

K

)

2

.

3

0

µ

s

(

2

2

C

K

)

4

.

7

5

µ

s

(

4

5

C

K

)

2

.

3

0

µ

s

(

2

2

C

K

)

1

.

4

8

µ

s

(

1

4

C

K

)

1

C

K

=

1

0

5

.

6

1

n

s

4

.

7

5

µ

s

(

4

5

C

K

)

1

2

.

0

4

µ

s

(

1

1

4

C

K

)

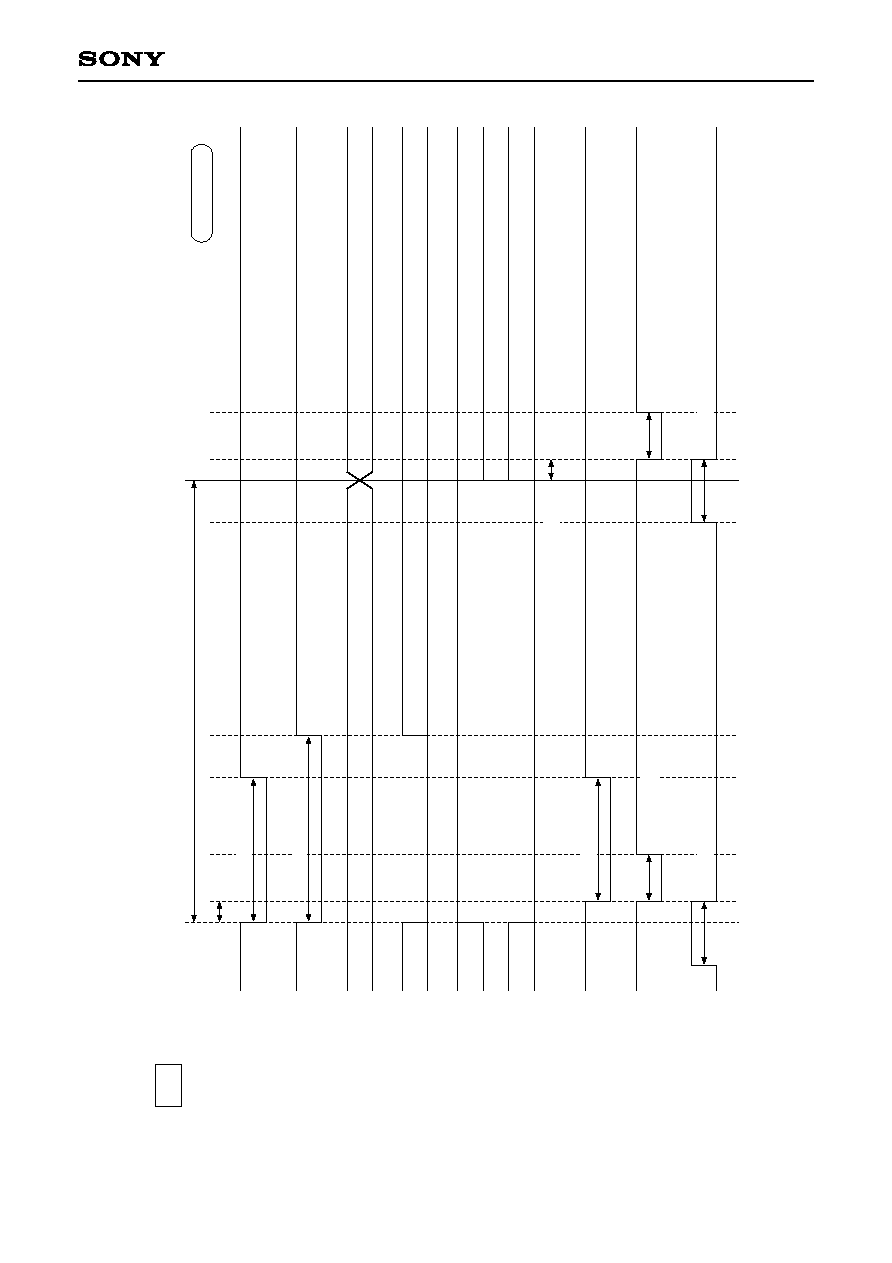

Timing Generator + Sync Generator Block Timing Chart

Effective Horizontal Period (during 510H CCD drive)

≠ 33 ≠

CXD2463R

H

D

3

1

.

7

8

µ

s

(

4

5

5

C

K

)

1

.

5

4

µ

s

(

2

2

C

K

)

1

/

2

H

E

I

A

H

S

Y

N

C

E

Q

V

S

Y

N

C

B

L

K

(

H

D

)

B

L

K

(

O

D

D

)

B

L

K

(

E

V

E

N

)

V

D

(

E

V

E

N

)

V

D

(

O

D

D

)

6

.

2

9

µ

s

(

9

0

C

K

)

4

.

7

5

µ

s

(

6

8

C

K

)

2

.

3

7

µ

s

(

3

4

C

K

)

4

.

7

5

µ

s

(

6

8

C

K

)

2

.

3

7

µ

s

(

3

4

C

K

)

1

.

5

4

µ

s

(

2

2

C

K

)

1

C

K

=

6

9

.

8

4

n

s

4

.

7

5

µ

s

(

6

8

C

K

)

1

0

.

7

6

µ

s

(

1

5

4

C

K

)

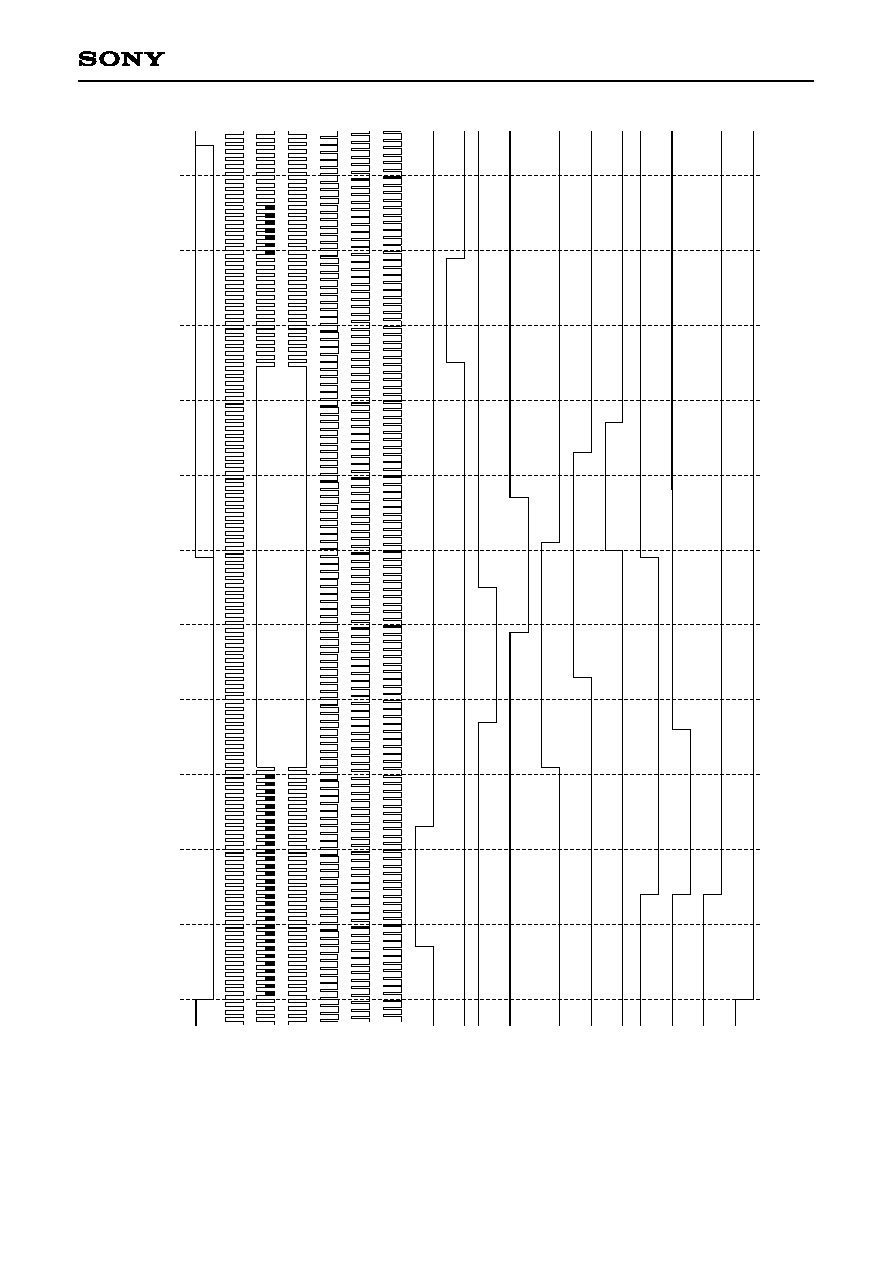

Timing Generator + Sync Generator Block Timing Chart

Effective Horizontal Period (during 760H CCD drive)

≠ 34 ≠

CXD2463R

H

D

3

2

.

0

0

µ

s

(

4

5

4

C

K

)

1

.

5

5

µ

s

(

2

2

C

K

)

1

/

2

H

C

C

I

R

H

S

Y

N

C

E

Q

V

S

Y

N

C

B

L

K

(

H

D

)

B

L

K

(

O

D

D

)

V

D

(

E

V

E

N

)

V

D

(

O

D

D

)

B

L

K

(

E

V

E

N

)

6

.

3

4

µ

s

(

9

0

C

K

)

4

.

7

9

µ

s

(

6

8

C

K

)

2

.

4

0

µ

s

(

3

4

C

K

)

4

.

7

9

µ

s

(

6

8

C

K

)

2

.

4

0

µ

s

(

3

4

C

K

)

1

.

5

5

µ

s

(

2

2

C

K

)

1

C

K

=

7

0

.

4

8

n

s

4

.

7

9

µ

s

(

6

8

C

K

)

1

1

.

9

1

µ

s

(

1

6

9

C

K

)

Timing Generator + Sync Generator Block Timing Chart

Effective Horizontal Period (during 760H CCD drive)

≠ 35 ≠

CXD2463R

H1

H2

RG

CCD OUT

MCK

(Internal clock)

SHP

SHD

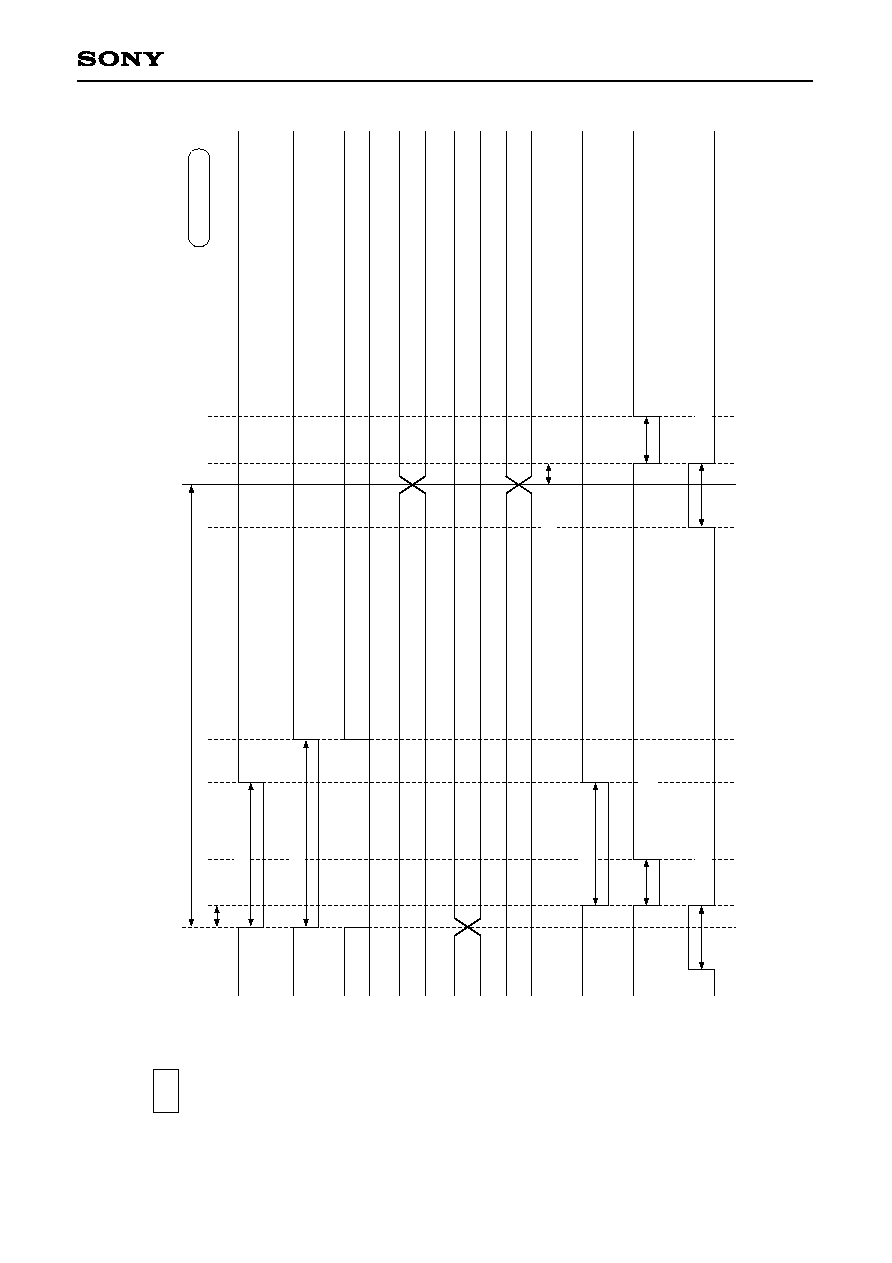

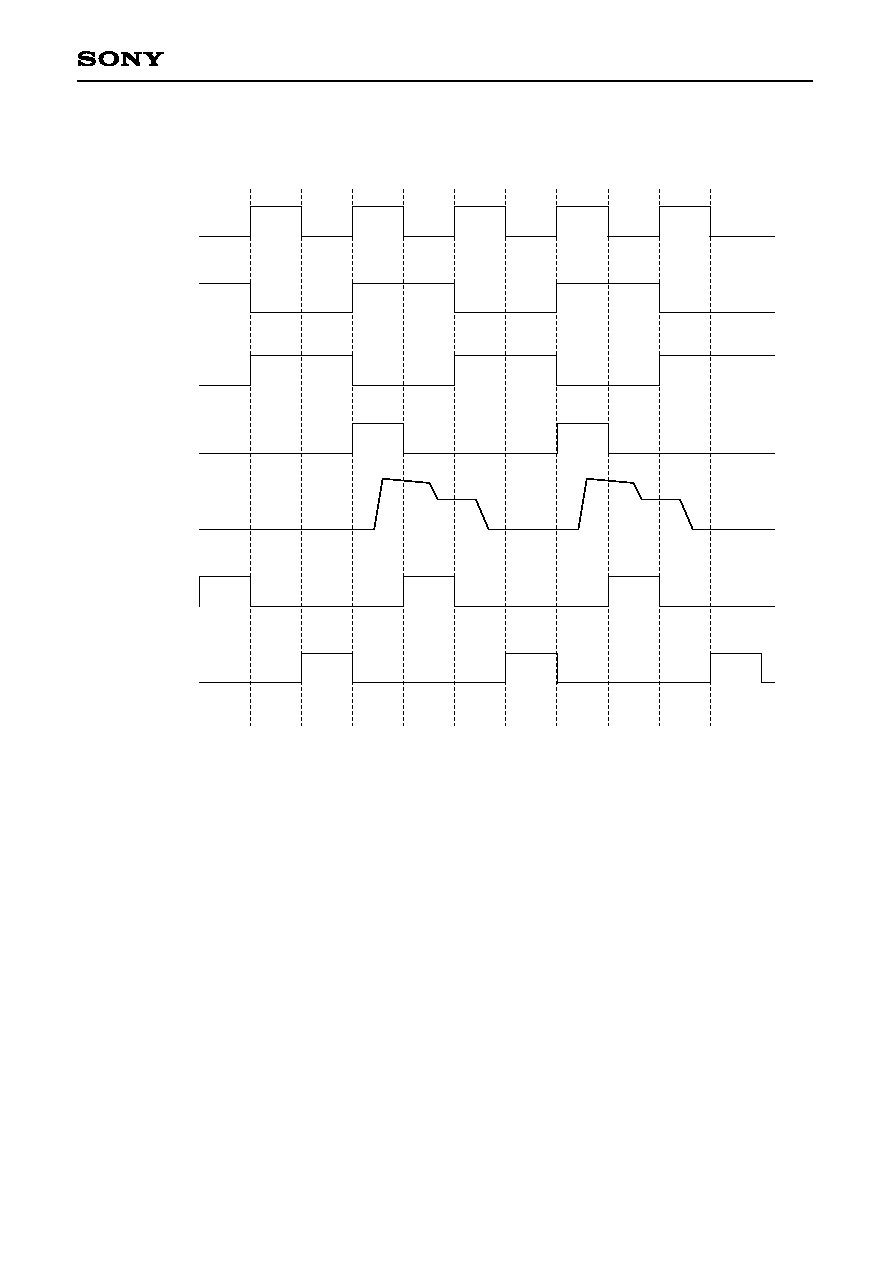

High-Speed Phase Timing Chart for the Timing Generator Block

≠ 36 ≠

CXD2463R

V

S

U

B

A

D

J

3

6

k

5

0

k

5

0

k

1

0

k

3

.

9

k

1

0

0

+

5

V

1

0

0

1

0

k

1

0

µ

V

I

D

E

O

O

U

T

C

C

D

O

U

T

1

0

µ

1

0

0

k

1

0

k

≠

9

.

0

t

o

≠

8

.

0

V

+

1

4

.

5

5

t

o

+

1

5

.

4

5

V

R

e

s

e

t

c

i

r

c

u

i

t

H

s

h

i

f

t

e

r

R

G

A

D

J

1

0

0

0

p

1

0

p

1

0

k

1

0

k

1

0

k

1

0

0

k

1

0

0

0

p

1

M

0

.

0

1

µ

S

Y

N

C

I

N

0

.

1

µ

1

M

1

p

3

9

k

C

X

A

1

3

1

0

A

Q

C

X

D

2

4

6

3

R

1

3

1

4

1

5

1

6

1

7

1

8

1

9

2

0

2

1

2

2

2

3

2

4

2

5

2

6

2

7

2

8

2

9

3

0

3

1

3

2

3

3

3

4

3

5

3

6

3

7

3

8

3

9

4

0

4

1

4

2

4

3

4

4

4

5

4

6

4

7

4

8

1

2

3

4

5

6

7

8

9

1

0

1

1

1

2

2

5

3

0

2

7

2

4

2

0

2

1

2

9

4

5

1

0

H

/

7

6

0

H

b

l

a

c

k

-

a

n

d

-

w

h

i

t

e

C

C

D

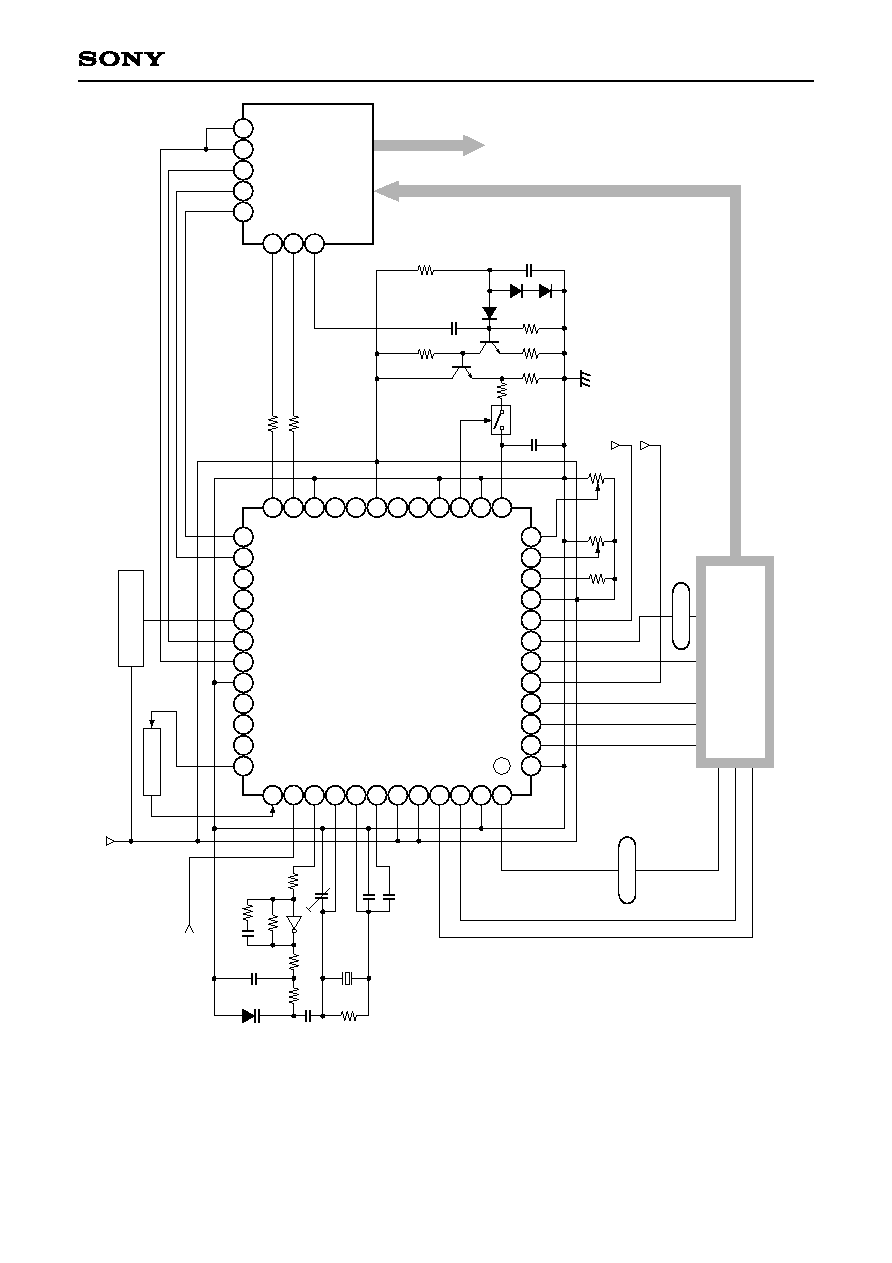

Application Circuit

∑ SYNC input external synchronization

∑ Electronic iris mode

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility fo

r

any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same

.

≠ 37 ≠

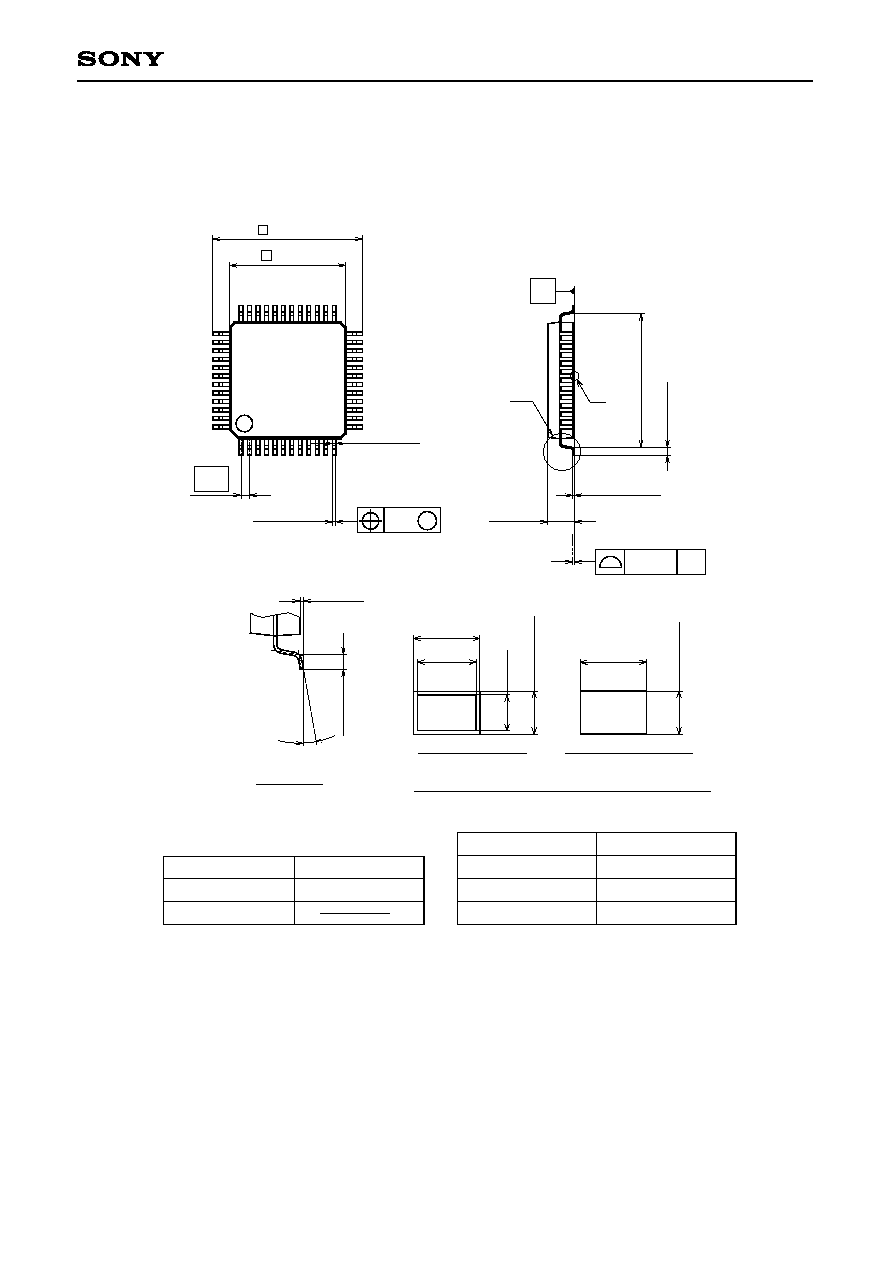

CXD2463R

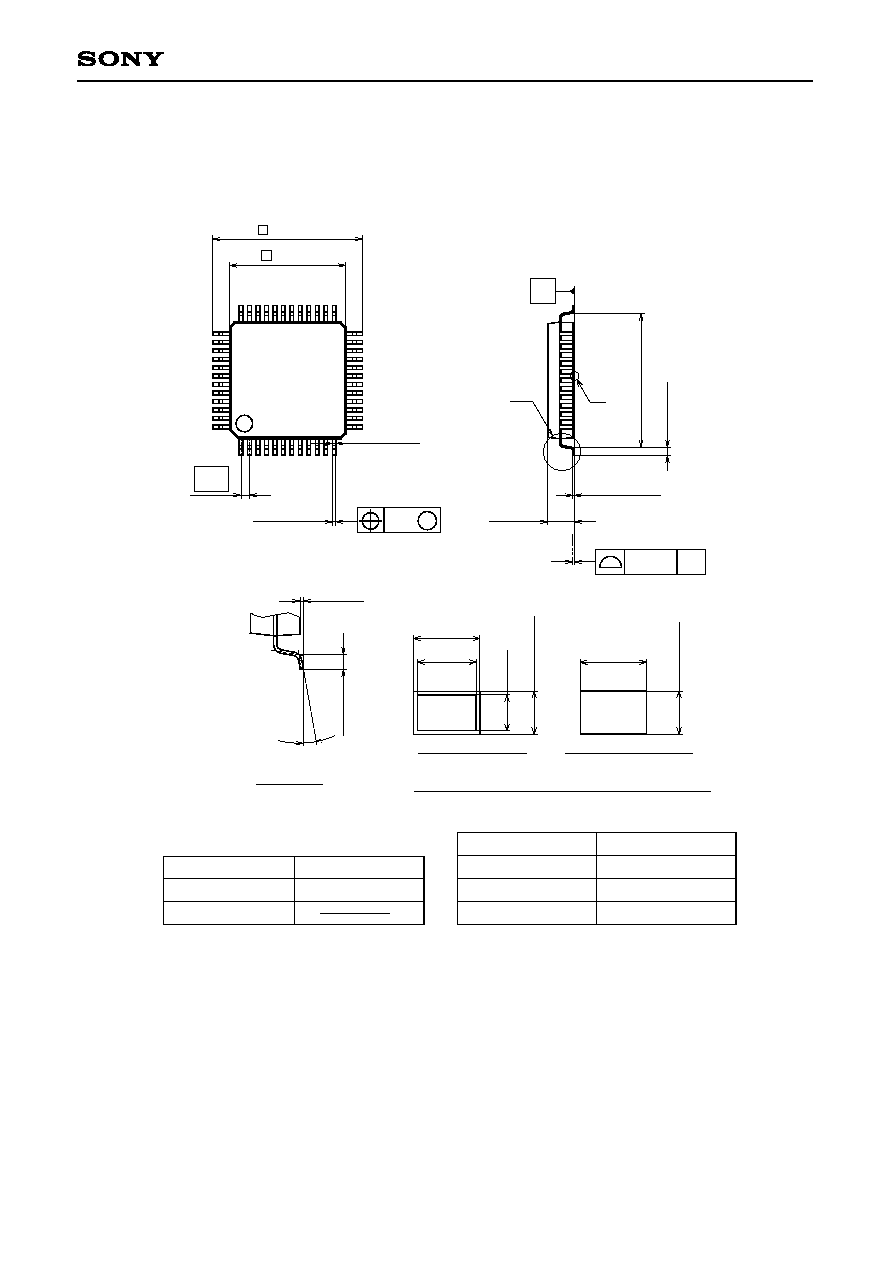

SONY CODE

EIAJ CODE

JEDEC CODE

PACKAGE MATERIAL

LEAD TREATMENT

LEAD MATERIAL

PACKAGE MASS

EPOXY RESIN

PLATING

42/COPPER ALLOY

PACKAGE STRUCTURE

48PIN LQFP (PLASTIC)

9.0 ± 0.2

7.0 ± 0.1

1

12

13

24

25

36

37

48

(0.22)

0.18 ≠ 0.03

+ 0.08

0.2g

LQFP-48P-L01

LQFP048-P-0707

(

8

.

0

)

0

.

5

±

0

.

2

0.127 ≠ 0.02

+ 0.05

A

1.5 ≠ 0.1

+ 0.2

0.1

SOLDER/PALLADIUM

NOTE: Dimension "

" does not include mold protrusion.

0.1 ± 0.1

0

.

5

±

0

.

2

0∞ to 10∞

DETAIL A

0.13 M

0.5

S

S

B

DETAIL B:SOLDER

(0.18)

(

0

.

1

2

7

)

DETAIL B:PALLADIUM

0

.

1

2

7

±

0

.

0

4

0.18 ≠ 0.03

+ 0.08

0

.

1

2

7

≠

0

.

0

2

+

0

.

0

5

0.18 ± 0.03

Package Outline

Unit: mm