≠ 1 ≠

CXP832P40A

E94X39A1Y-PS

CMOS 8-bit Single Chip Microcomputer

Description

The CXP832P40A is a CMOS 8-bit single chip

microcomputer integrating on a single chip an A/D

converter, serial interface, timer/counter, time base

timer, 32kHz timer/counter, capture timer counter,

LCD controller/driver, remote control reception circuit

and 14-bit PWM output besides the basic

configurations of 8-bit CPU, PROM, RAM, and I/O port.

Also the CXP832P40A provides sleep/stop function

which enables to lower power consumption.

The CXP832P40A is the PROM-incorporated

version of the CXP83240A with built-in mask ROM.

This provides the additional feature of being able to

write directry into the program. Thus, it is most

suitable for evaluation use during system

development and for small-quantity production.

Features

∑ Wide-range instruction system (213 instructions) to cover various types of data.

-- 16-bit arithmetic/multiplication and division/boolean bit operation instructions

∑ Minimum instruction cycle

400ns at 10MHz operation

8Ķs at 500kHz operation

122Ķs at 32kHz operation

∑ Incorporated PROM capacity 40K bytes

∑ Incorporated RAM capacity

1120 bytes (includes LCD display data area)

∑ Peripheral functions

-- A/D converter

8-bit, 8-channel, successive approximation method

(Conversion time of 32Ķs/10MHz)

-- Serial interface

8-bit, 8-stage FIFO incorporated

(Auto transfer for 1 to 8 bytes), 1 channel

8-bit clock synchronized type, 1 channel

-- Timer

8-bit timer, 8-bit timer/counter, 19-bit time base timer,

16-bit capture timer/counter, 32kHz timer/counter

-- LCD controller/driver

Maximum 160 segment display possible (during 1/4 duty)

4 common output, 40 segment output

Display method static, 1/2, 1/3, 1/4 duty

Bias method 1/2, 1/3 bias

-- Remote control reception circuit

8-bit pulse measurement counter with on-chip, 6-stage FIFO

-- PWM output circuit

14 bits, 1 channel

∑ Interruption

15 factors, 15 vectors, multi-interruption possible

∑ Standby mode

SLEEP/STOP

∑ Package

100-pin plastic QFP/LQFP

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

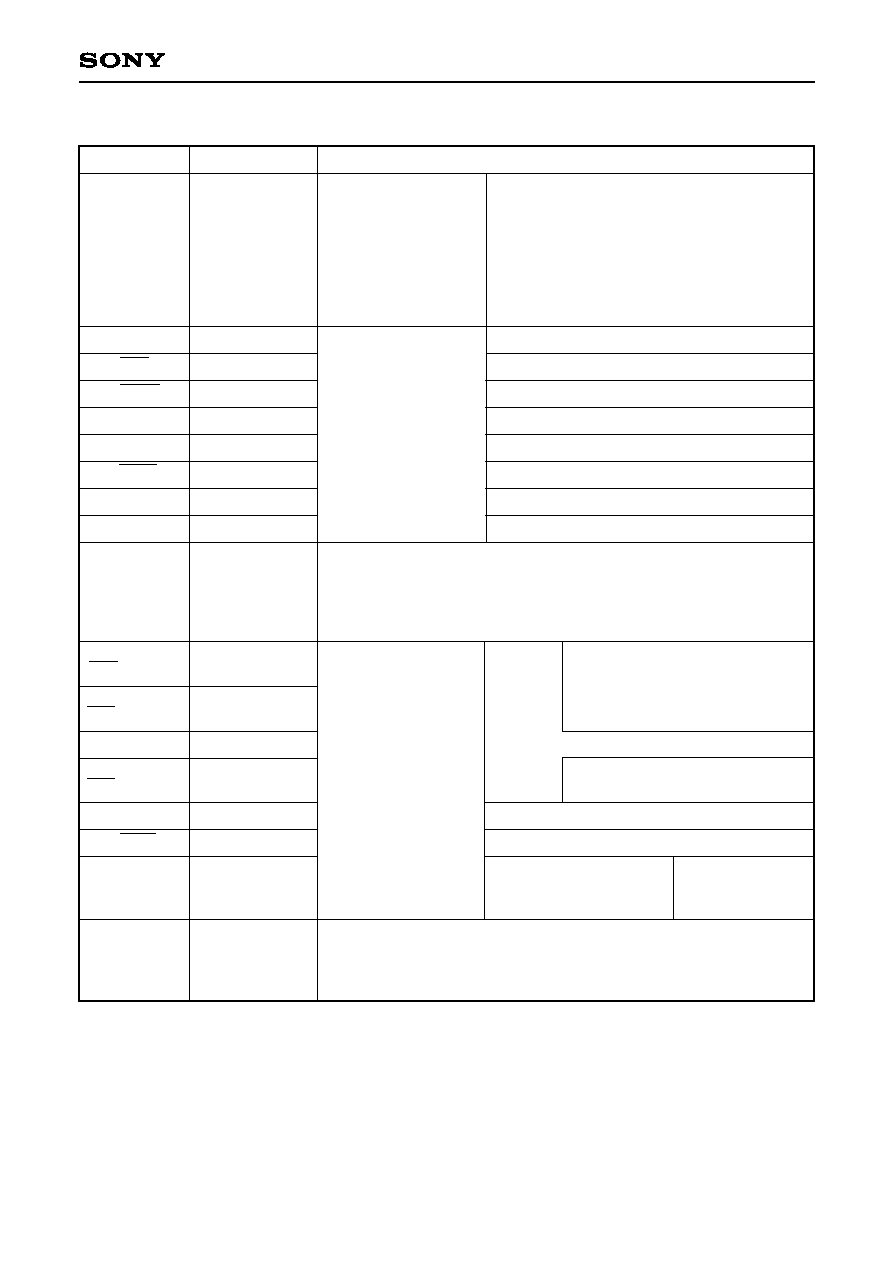

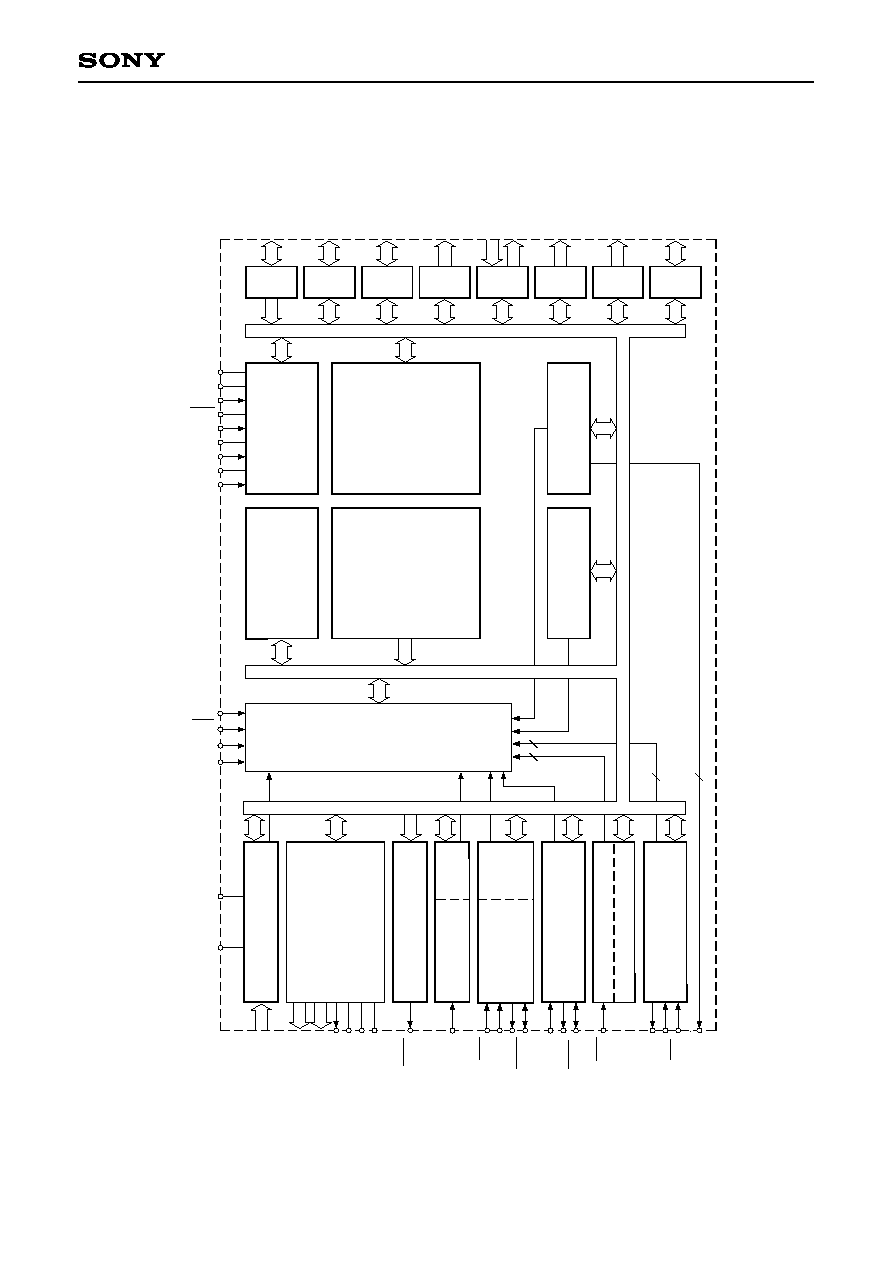

Structure

Silicon gate CMOS IC

100 pin QFP (Plastic)

100 pin LQFP (Plastic)

≠ 2 ≠

CXP832P40A

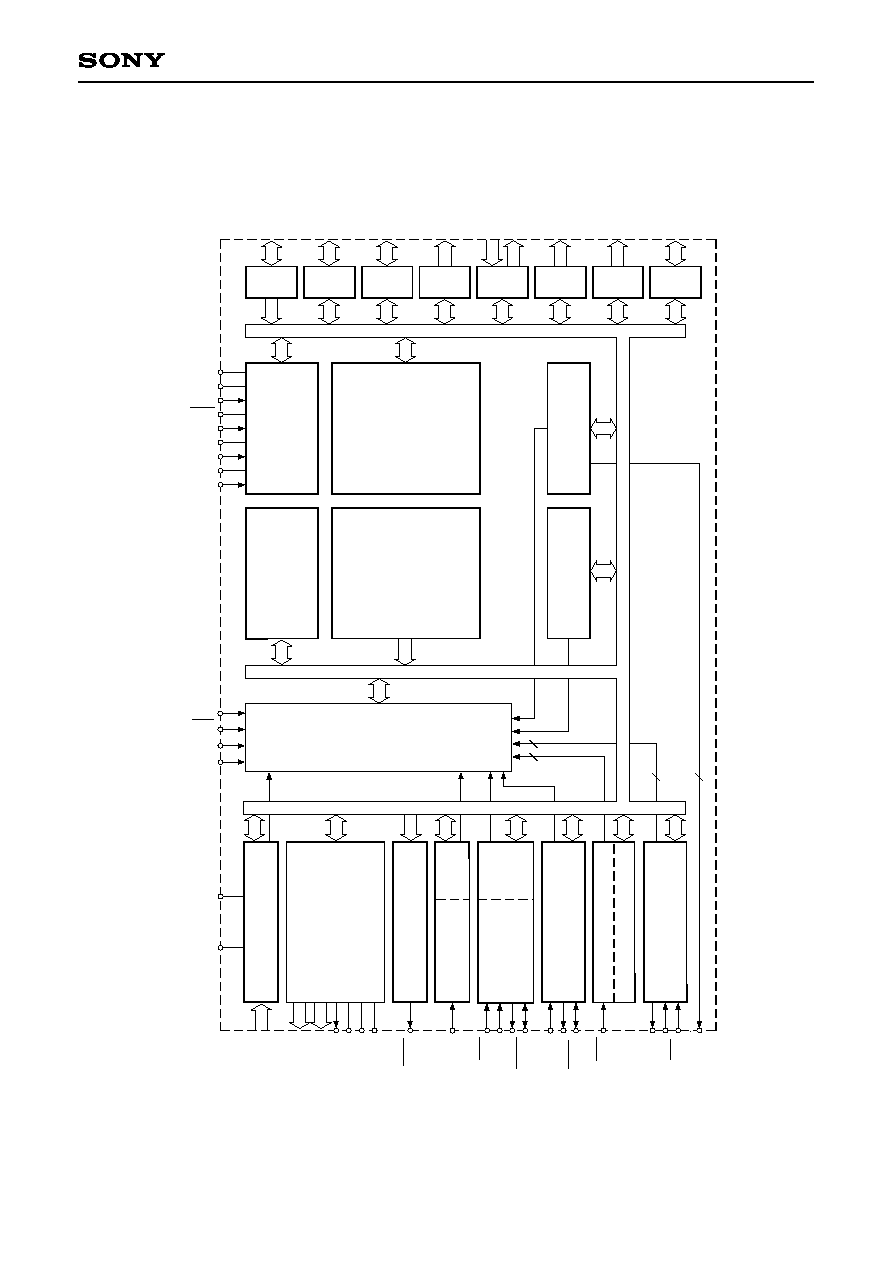

RAM

1120 BYTES

CLOCK GEN/

SYSTEM CONTROL

SPC 700

CPU CORE

INTERRUPT CONTROLLER

A/D CONVERTER

SERIAL

INTERFACE

UNIT 0

SERIAL INTERFACE UNIT 1

8-BIT TIMER/COUNTER 0

8-BIT TIMER 1

14-BIT PWM GENERATOR

16-BIT CAPTURE

TIMER/COUNTER 2

V

SS

RST

XTAL1

EXTAL1

V

DD

NMI/INT3

INT1

INT0

INT2

AN0 to AN7

8

PA0 to PA7

FIFO

FIFO

REMOCON

LCD

CONTROLLER/

DRIVER

32kHz

TIMER/COUNTER

PRESCALER/

TIME BASE TIMER

PORT A

PORT B

PORT C

PORT D

PORT E

PORT F

PORT G

PORT H

8

8

5

2

8

8

8

8

PB0 to PB7

PC0 to PC7

PD0 to PD7

PE0 to PE4

PF0 to PF7

PG0 to PG7

PH0 to PH7

PE5 to PE6

TEX

EXTAL2

XTAL2

TX

AV

REF

AV

SS

SEG0 to SEG39

VL

COM0 to COM3

VLC1

VLC2

VLC3

PWM

RMC

CS0

SI0

SO0

SCK0

SI1

SO1

SCK1

EC0

TO

CINT

EC1

ADJ

2

2

2

2

40

4

PROM

40K BYTES

8

Block Diagram

≠ 3 ≠

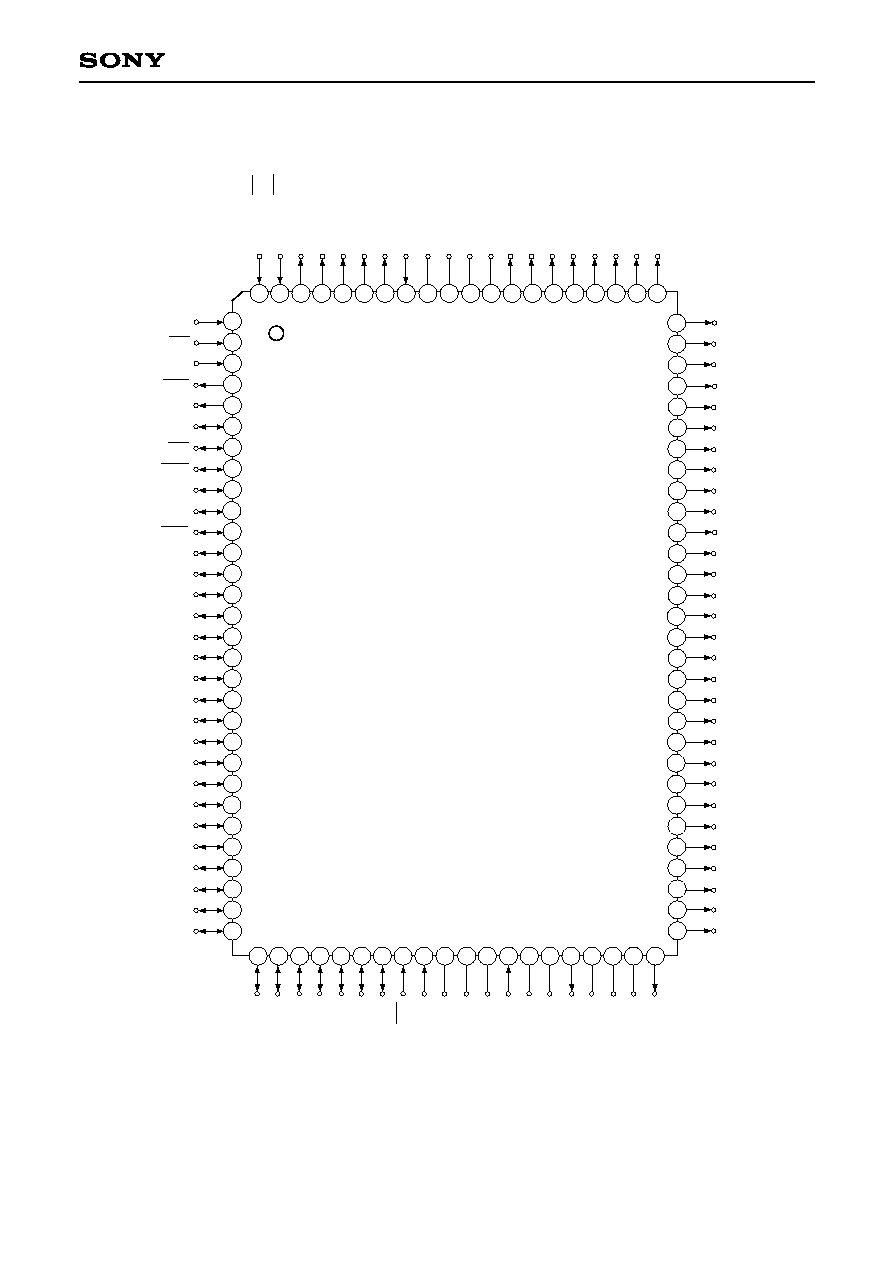

CXP832P40A

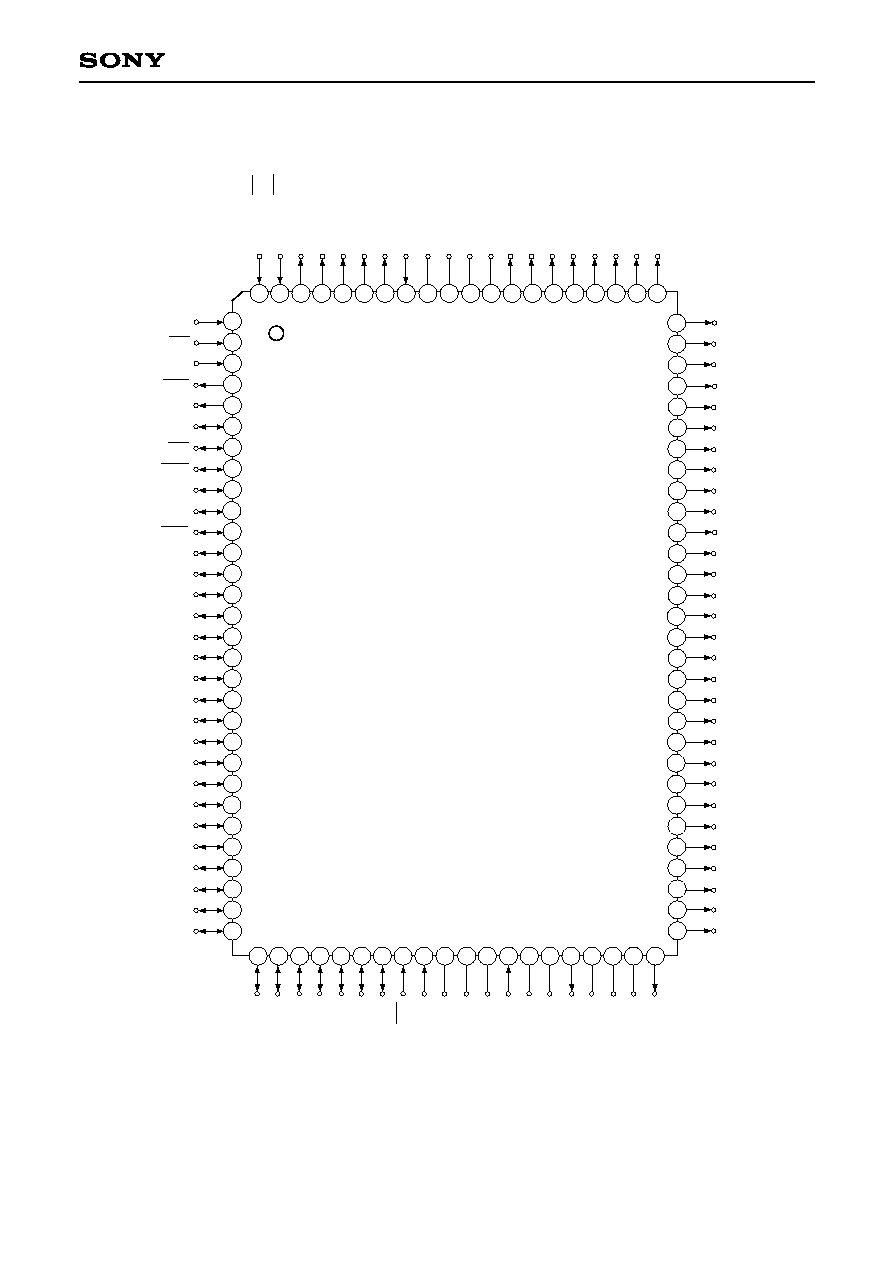

Pin Assignment (Top View) (QFP package)

PE2/INT2

PE3/INT3/NMI

PE4/RMC

PE5/PWM

PE6/TO/ADJ

PB0/CINT

PB1/CS0

PB2/SCK0

PB3/SI0

PB4/SO0

PB5/SCK1

PB6/SI1

PB7/SO1

PC0

PC1

PC2

PC3

PC4

PC5

PC6

PC7

PH0

PH1

PH2

PH3

PH4

PH5

PH6

PH7

PA0/AN0

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

40

39

38

37

36

35

34

31 32 33

41 42 43 44 45 46 47 48 49 50

51

52

53

54

55

56

57

58

59

60

70

69

68

67

63

64

65

66

61

62

71

72

73

74

81

82

83

84

75

76

77

78

88 87 86 85

79

80

89

90

100 99 98 97 96 95 94

91

92

93

1

PA1/AN1

PA2/AN2

PA3/AN3

PA4/AN4

PA5/AN5

PA6/AN6

PA7/AN7

RST

EXTAL1

XTAL1

Vss

XTAL2

EXTAL2

AV

REF

AVss

V

L

V

LC3

V

LC2

V

LC1

COM0

SEG26/PF2

SEG25/PF1

SEG24/PF0

SEG23/PD7

SEG22/PD6

SEG21/PD5

SEG20/PD4

SEG19/PD3

SEG18/PD2

SEG17/PD1

SEG16/PD0

SEG15

SEG14

SEG13

SEG12

SEG11

SEG10

SEG9

SEG8

SEG7

SEG6

SEG5

SEG4

SEG3

SEG2

SEG1

SEG0

COM3

COM2

COM1

PE1/INT1/EC1

PE0/INT0/EC0

SEG39/PG7

SEG38/PG6

SEG37/PG5

SEG36/PG4

SEG35/PG3

TEX

TX

Vss

Vpp

V

DD

SEG34/PG2

SEG33/PG1

SEG32/PG0

SEG31/PF7

SEG30/PF6

SEG29/PF5

SEG28/PF4

SEG27/PF3

Note)

1. Vpp (Pin 90) is always connected to V

DD

.

2. V

SS

(Pin 41 and 91) are both connected to GND.

≠ 4 ≠

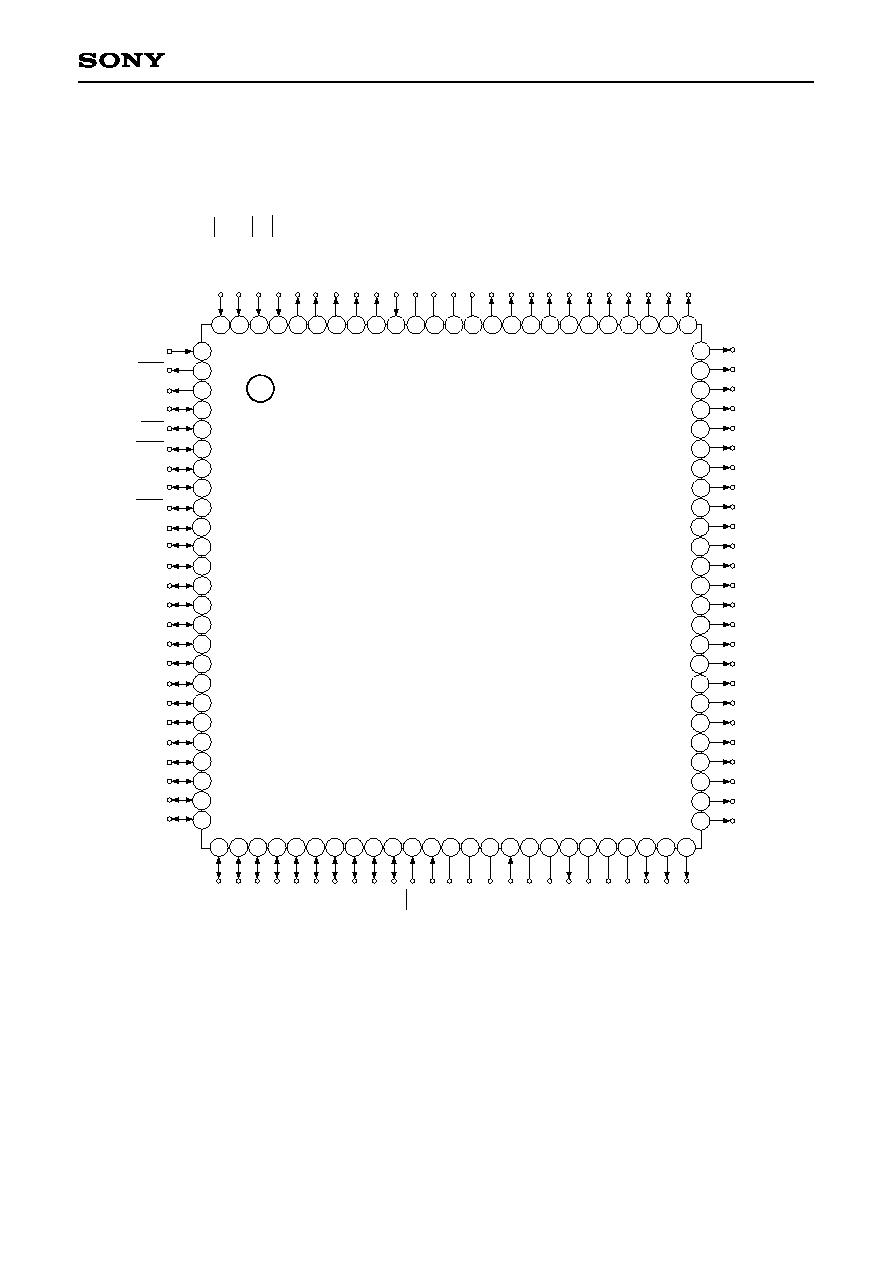

CXP832P40A

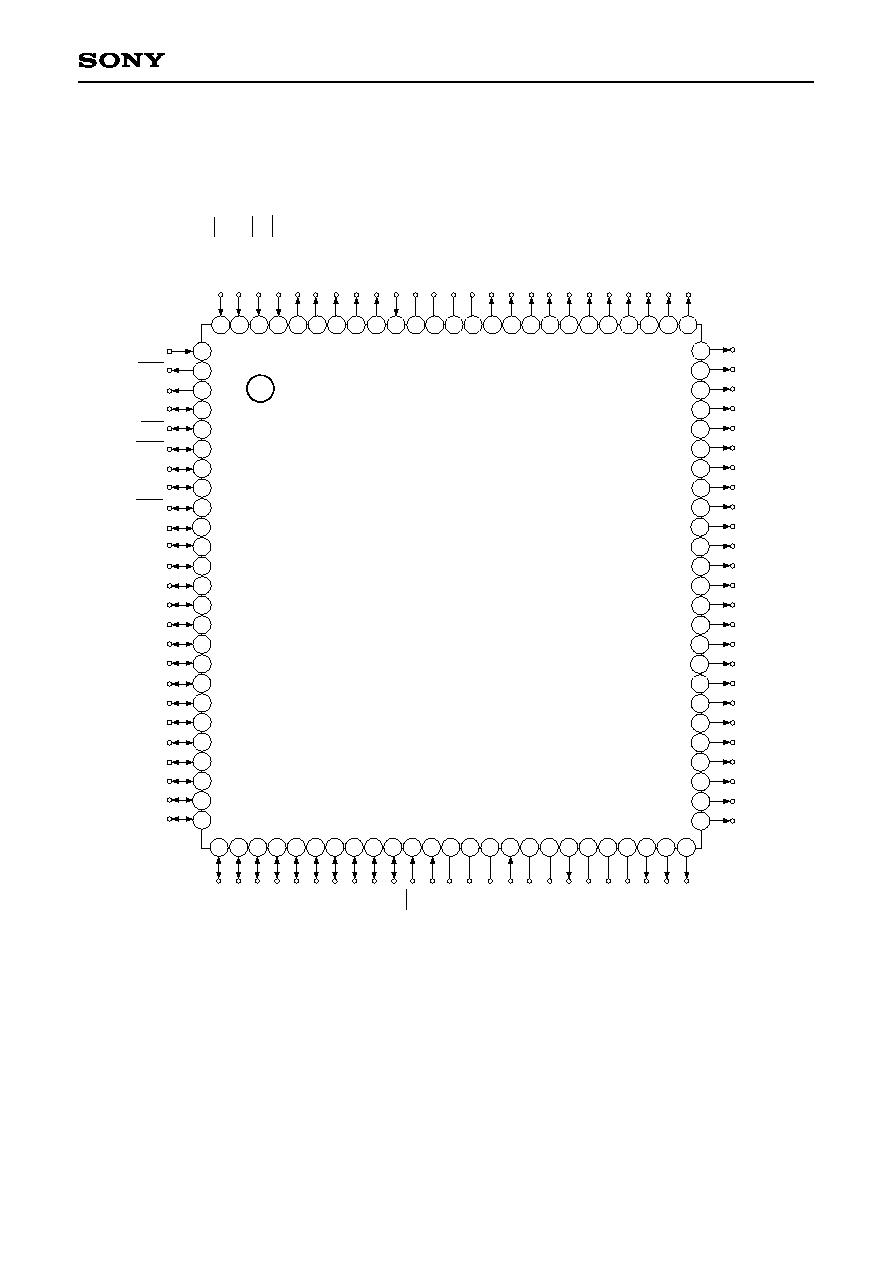

Pin Assignment (Top View) (LQFP package)

PE4/RMC

PE5/PWM

PE6/TO/ADJ

PB0/CINT

PB1/CSO

PB2/SCK0

PB3/SI0

PB4/SO0

PB5/SCK1

PB6/SI1

PB7/SO1

PC0

PC1

PC2

PC3

PC4

PC5

PC6

PC7

PH0

PH1

PH2

PH3

PH4

PH5

PH6

PH7

PA0/AN0

PA1/AN1

PA2/AN2

PA3/AN3

PA4/AN4

PA5/AN5

PA6/AN6

PA7/AN7

RST

EXTAL1

XTAL1

Vss

XTAL2

EXTAL2

AV

REF

AVss

V

L

V

LC3

V

LC2

V

LC1

COM0

COM1

COM2

PE3/INT3/NMI

PE2/INT2

PE1/INT1/EC1

PE0/INT0/EC0

SEG39/PG7

SEG38/PG6

SEG37/PG5

SEG36/PG4

SEG35/PG3

TEX

TX

Vss

Vpp

V

DD

SEG34/PG2

SEG33/PG1

SEG32/PG0

SEG31/PF7

SEG30/PF6

SEG29/PF5

SEG28/PF4

SEG27/PF3

SEG26/PF2

SEG25/PF1

SEG24/PF0

SEG23/PD7

SEG22/PD6

SEG21/PD5

SEG20/PD4

SEG19/PD3

SEG18/PD2

SEG17/PD1

SEG16/PD0

SEG15

SEG14

SEG13

SEG12

SEG11

SEG10

SEG9

SEG8

SEG7

SEG6

SEG5

SEG4

SEG3

SEG2

SEG1

SEG0

COM3

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

1

81

82

83

84

76

77

78

88 87 86 85

79

80

89

90

100 99 98 97 96 95 94

91

92

93

51

52

53

54

55

56

57

58

59

60

70

69

68

67

63

64

65

66

61

62

71

72

73

74

75

26 27 28 29 30

40

39

38

37

36

35

34

31 32 33

41 42 43 44 45 46 47 48 49 50

Note)

1. Vpp (Pin 88) is always connected to V

DD

.

2. V

SS

(Pin 39 and 89) are both connected to GND.

≠ 5 ≠

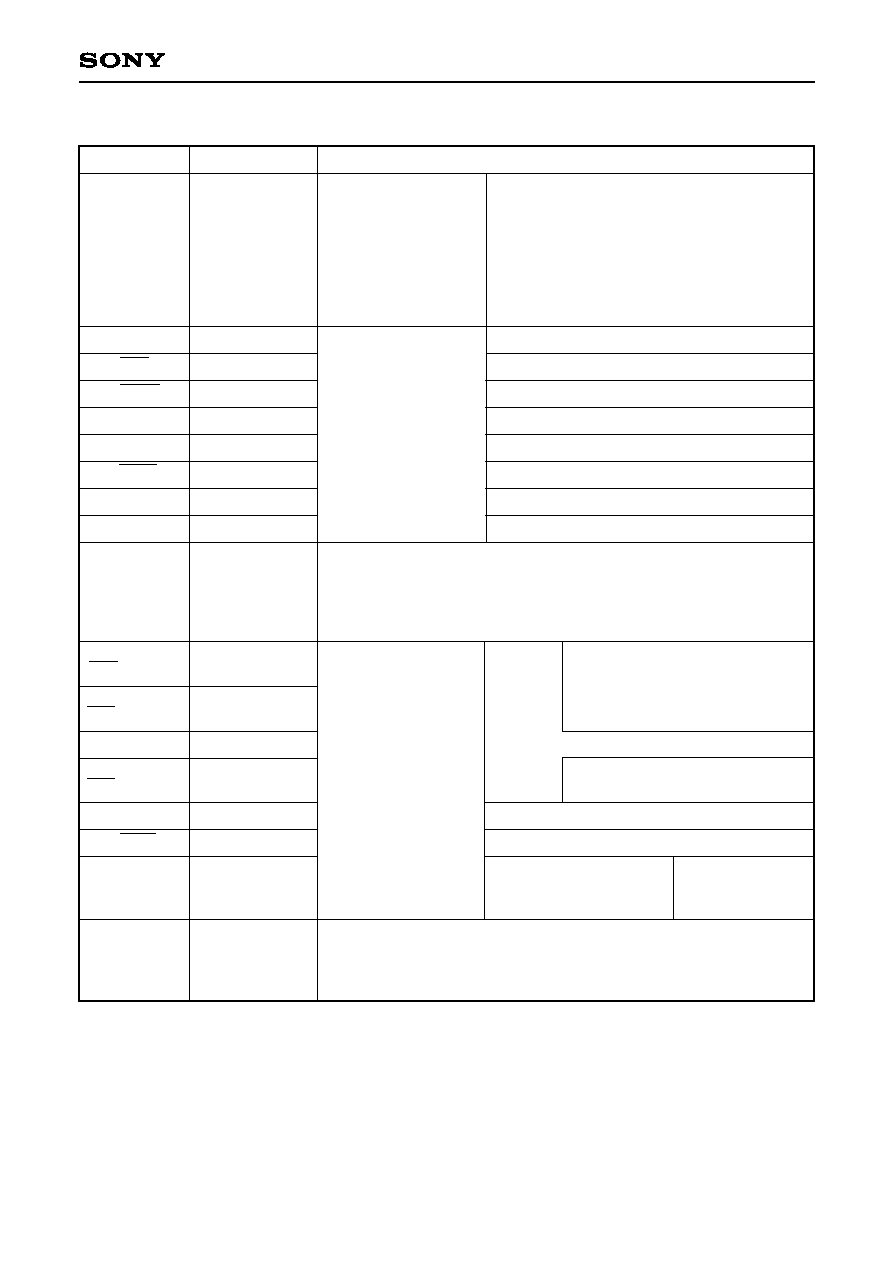

CXP832P40A

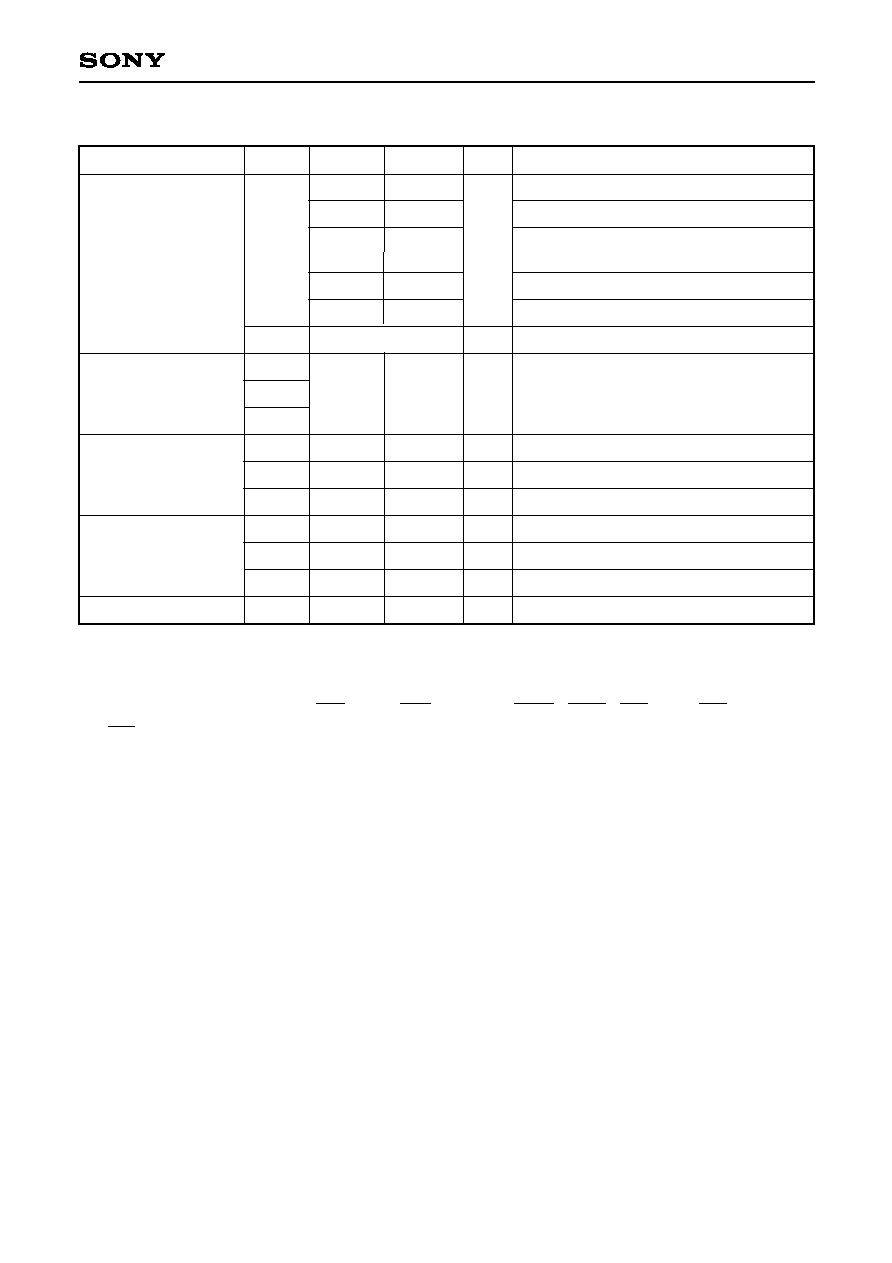

Pin Description

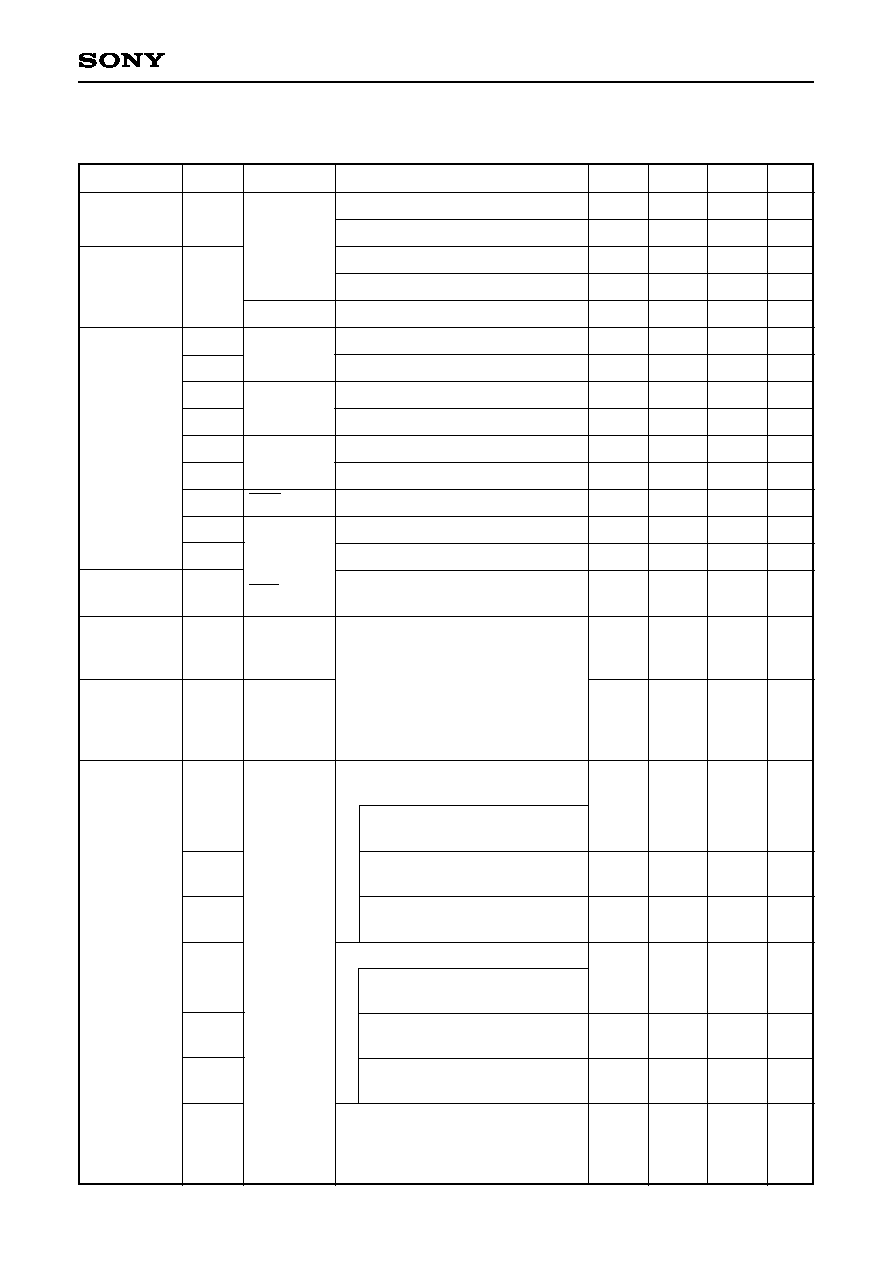

Symbol

I/O

Functions

I/O/Analog input

PA0/AN0

to

PA7/AN7

(Port A)

8-bit I/O port. I/O can

be set in a single bit

unit.

Incorporation of pull-up

resistor can be set

through the software in

a unit of 4 bits. (8 pins)

Analog inputs to A/D converter.

(8 pins)

I/O

PC0 to PC7

PE0/INT0/

EC0

PE1/INT1/

EC1

PE2/INT2

PE3/INT3/

NMI

PE4/RMC

PE5/PWM

PE6/TO/

ADJ

PH0 to PH7

Input/Input/Input

Input/Input/Input

Input/Input

Input/Input/Input

Input/Input

Output/Output

Output/Output/

Output

I/O

(Port C)

8-bit I/O port. I/O can be set in a single bit unit. Capable of driving 12mA

sync current. Incorporation of pull-up resistor can be set through the

software in a unit of 4 bits.

(8 pins)

(Port E)

7-bit port. lower 5 bits

are for inputs; upper 2

bits are for outputs.

(7 pins)

(Port H)

8-bit I/O port. I/O can be set in a single bit unit. Incorporation of pull-up

resistor can be set through the software in a unit of 4 bits.

(8 pins)

External event inputs for

timer/counter.

(2 pins)

External interruption request inputs.

(4 pins)

Non-maskable interruption request

input.

Remote control reception circuit input.

14-bit PWM output.

Rectangular wave output

for 16-bit timer/counter

(duty output 50%).

Output for 32kHz

oscillation

frequency division.

I/O/Input

I/O/Input

I/O/I/O

I/O/Input

I/O/Output

I/O/I/O

I/O/input

I/O/Output

PB0/CINT

PB1/CS0

PB2/SCK0

PB3/SI0

PB4/SO0

PB5/SCK1

PB6/SI1

PB7/SO1

(Port B)

8-bit I/O port. I/O can

be set in a single bit

unit.

Incorporation of pull-up

resistor can be set

through the software in

a unit of 4 bits.

(8 pins)

External capture input to 16-bit timer/counter.

Chip select input for serial interface (CH0).

Serial clock I/O (CH0).

Serial data input (CH0).

Serial data output (CH0).

Serial clock I/O (CH1).

Serial data input (CH1).

Serial data output (CH1).

≠ 6 ≠

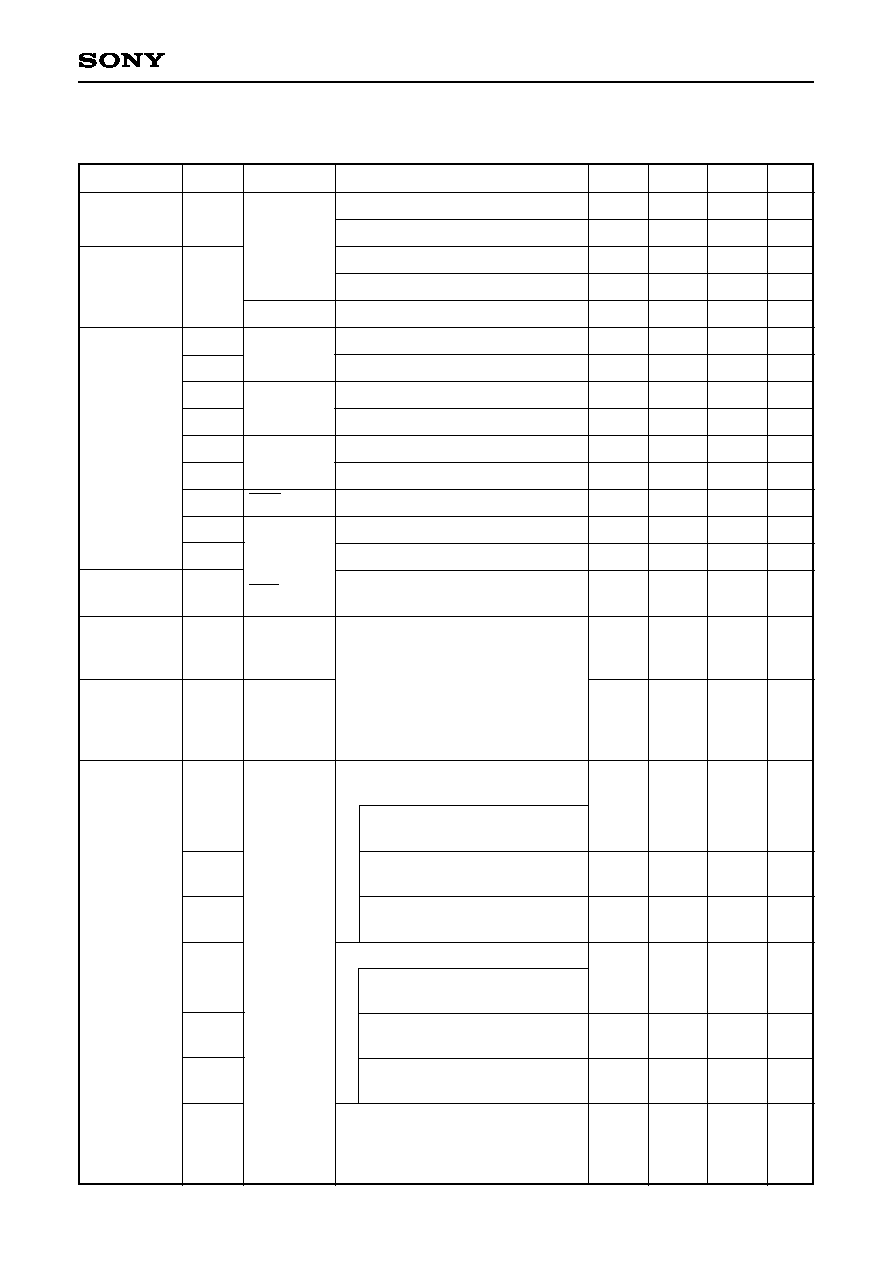

CXP832P40A

Symbol

I/O

Functions

Output/Output

PF0/SEG24

to

PF7/SEG31

(Port F)

8-bit output port.

(8 pins)

Output/Output

PG0/SEG32

to

PG7/SEG39

(port G)

8-bit output port.

(8 pins)

Output/Output

PD0/SEG16

to

PD7/SEG23

(Port D)

8-bit output port.

(8 pins)

Output

SEG0 to SEG15

LCD segment signal output.

Input

Crystal connectors for system clock oscillation. When the clock is

supplied externally, input to EXTAL1; opposite phase clock should be

input to XTAL1. System clock oscillation of EXTAL1 and XTAL1 is used

for normal operation mode (Max. 10MHz).

EXTAL1

Output

COM0 to COM3

LCD common signal output.

V

LC1

to V

LC3

LCD bias power supply.

Output

V

L

Control pin to cut off the current flowing to external LCD bias resistor

during standby.

XTAL1

Input

Crystal connectors for system clock oscillation. When the clock is

supplied externally, input to EXTAL2; opposite phase clock should be

input to XTAL2. System clock oscillation of EXTAL2 and XTAL2 is used

for sub clock mode (Typ. 500kHz).

EXTAL2

XTAL2

Input

Crystal connectors for 32kHz timer/counter clock generation circuit.

Connect a 32.768kHz crystal oscillator between TEX and TX. For usage

as event input, connect clock oscillation source to TEX, and leave TX

open.

TEX

Output

TX

Input

Input

Low-level active system reset.

Positive power supply for built-in PROM writing.

Under normal operating conditions, connect to V

DD

.

Reference voltage input for A/D converter.

A/D converter GND.

Positive power supply.

GND. Two V

SS

are connected to GND.

RST

Vpp

AV

REF

AV

SS

V

DD

V

SS

LCD segment signal output.

≠ 7 ≠

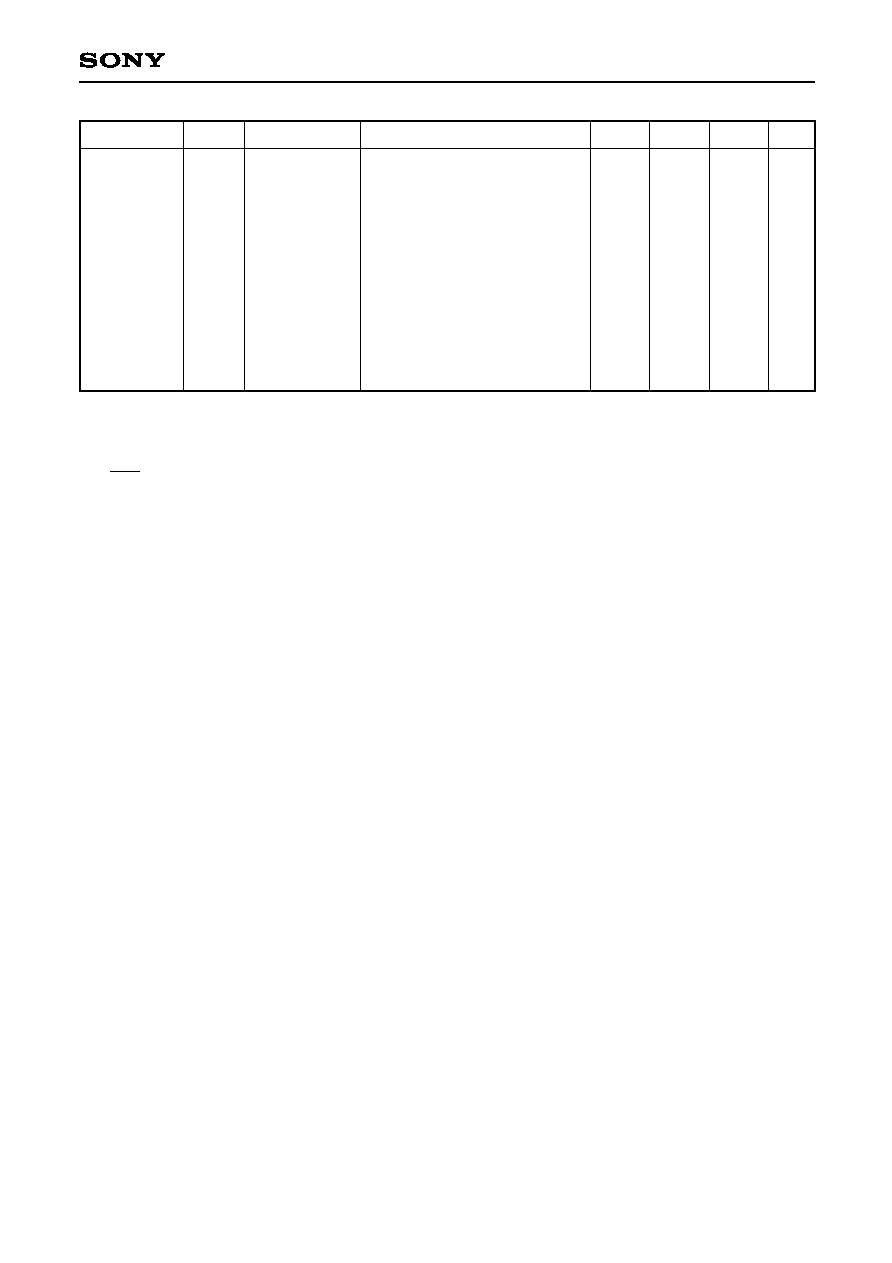

CXP832P40A

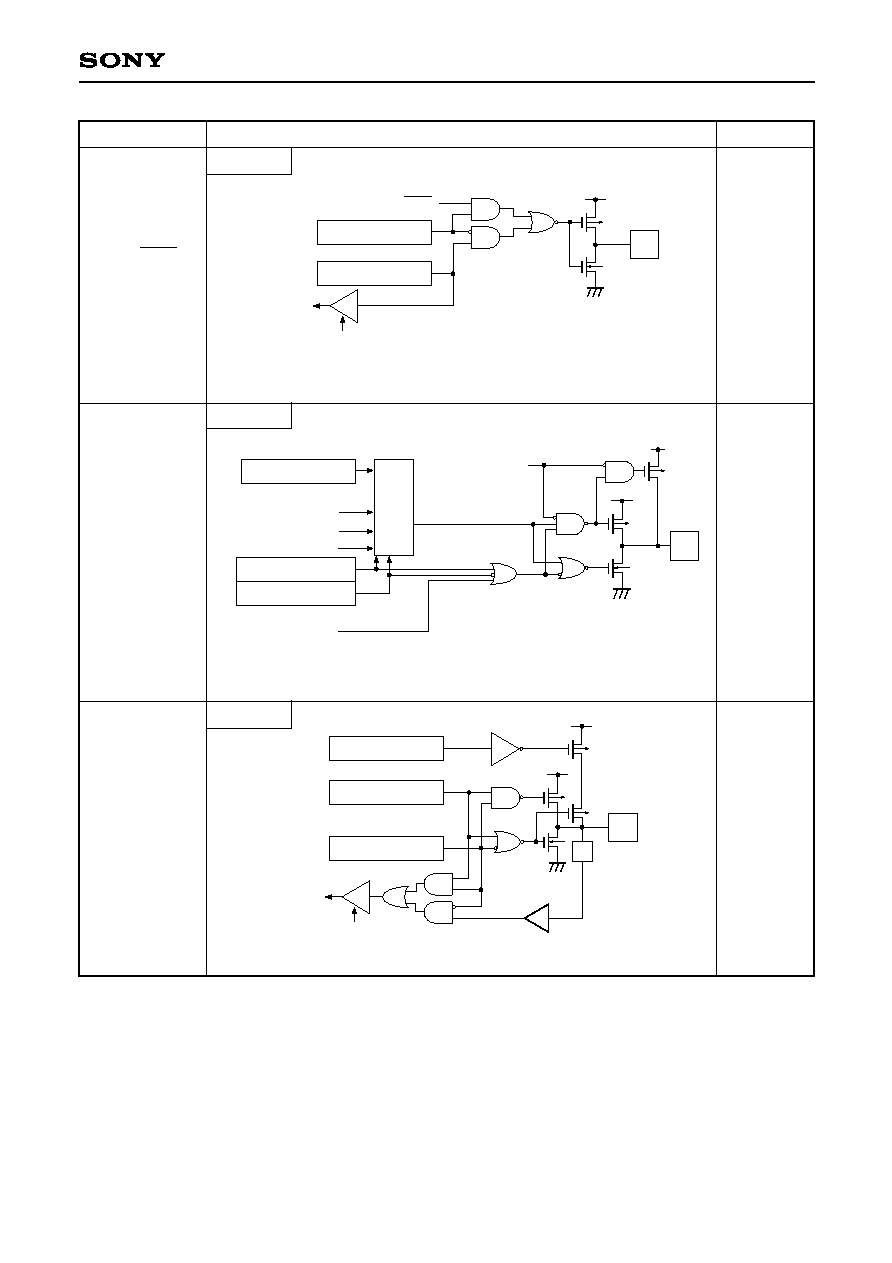

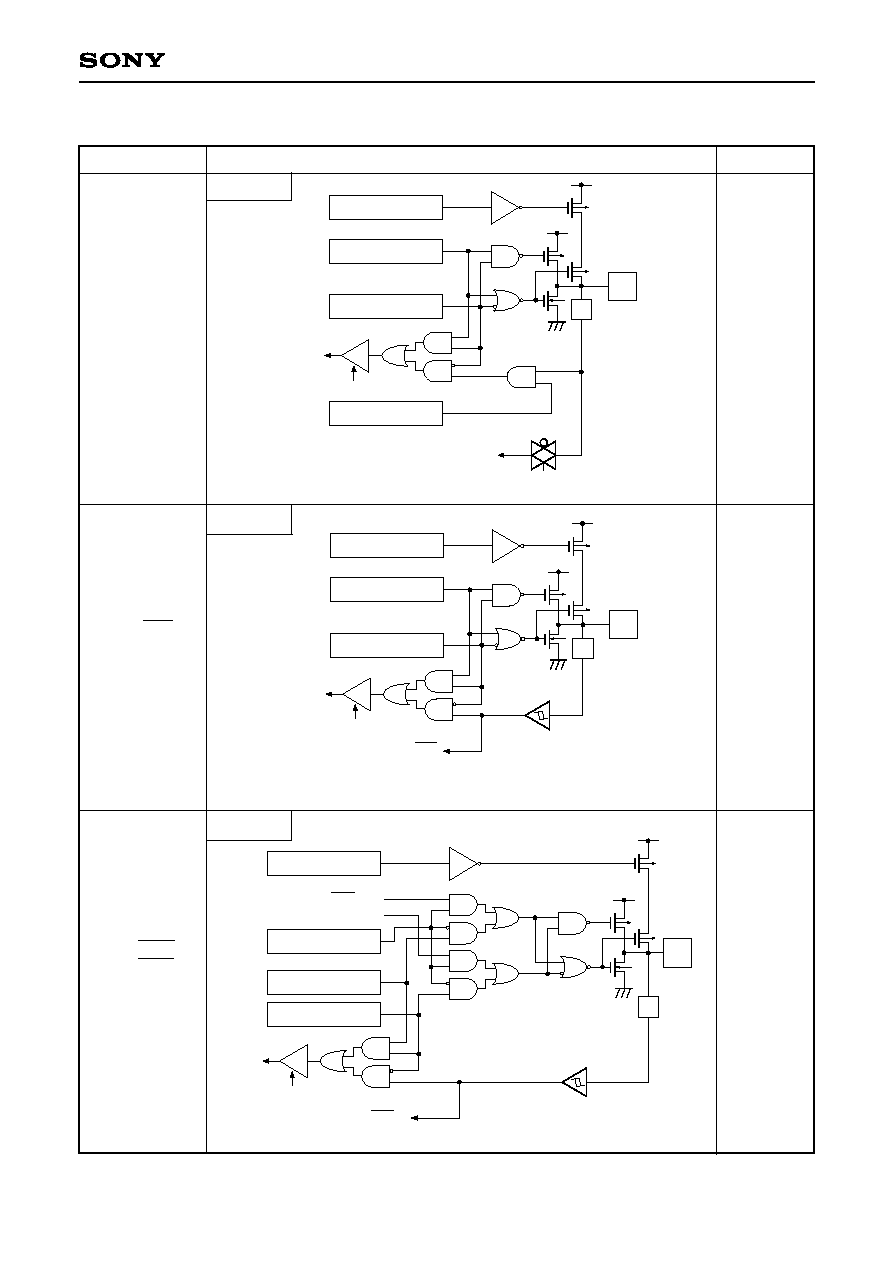

IP

Pull-up resistor

Port B data

Port B direction

"0" when reset

RD (Port B)

Data bus

Pull-up transistors

approx. 100k

"0" when reset

Schmitt input

CINT

CS0

SI0

SI1

Pull-up transistors

approx. 100k

Pull-up resistor

Port B data

Port B direction

"0" when reset

RD (Port B)

Data

bus

IP

"0" when reset

Schmitt input

SCK in

Output enable

"0" when reset

SCK OUT

Port B output selection

Port B

8 pins

Hi-Z

Hi-Z

When reset

PA0/AN0

to

PA7/AN7

PB0/CINT

PB1/CS0

PB3/SI0

PB6/SI1

Port B

4 pins

2 pins

Hi-Z

PB2/SCK0

PB5/SCK1

IP

Pull-up resistor

Port A data

Port A direction

"0" when reset

Port A input selection

"0" when reset

RD (Port A)

Data bus

A/D converter

Pull-up transistors

approx. 100k

Input multiplexer

"0" when reset

Input protection

circuit

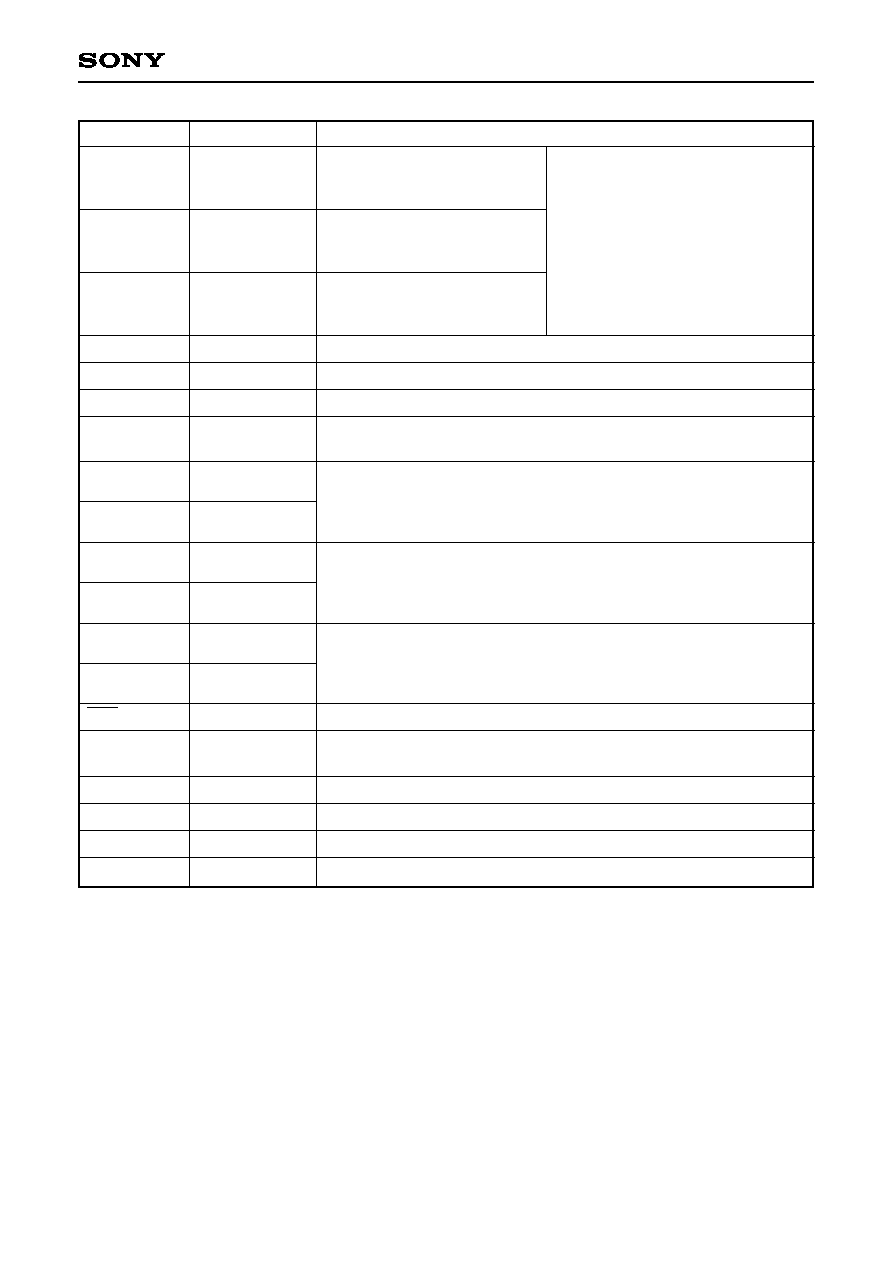

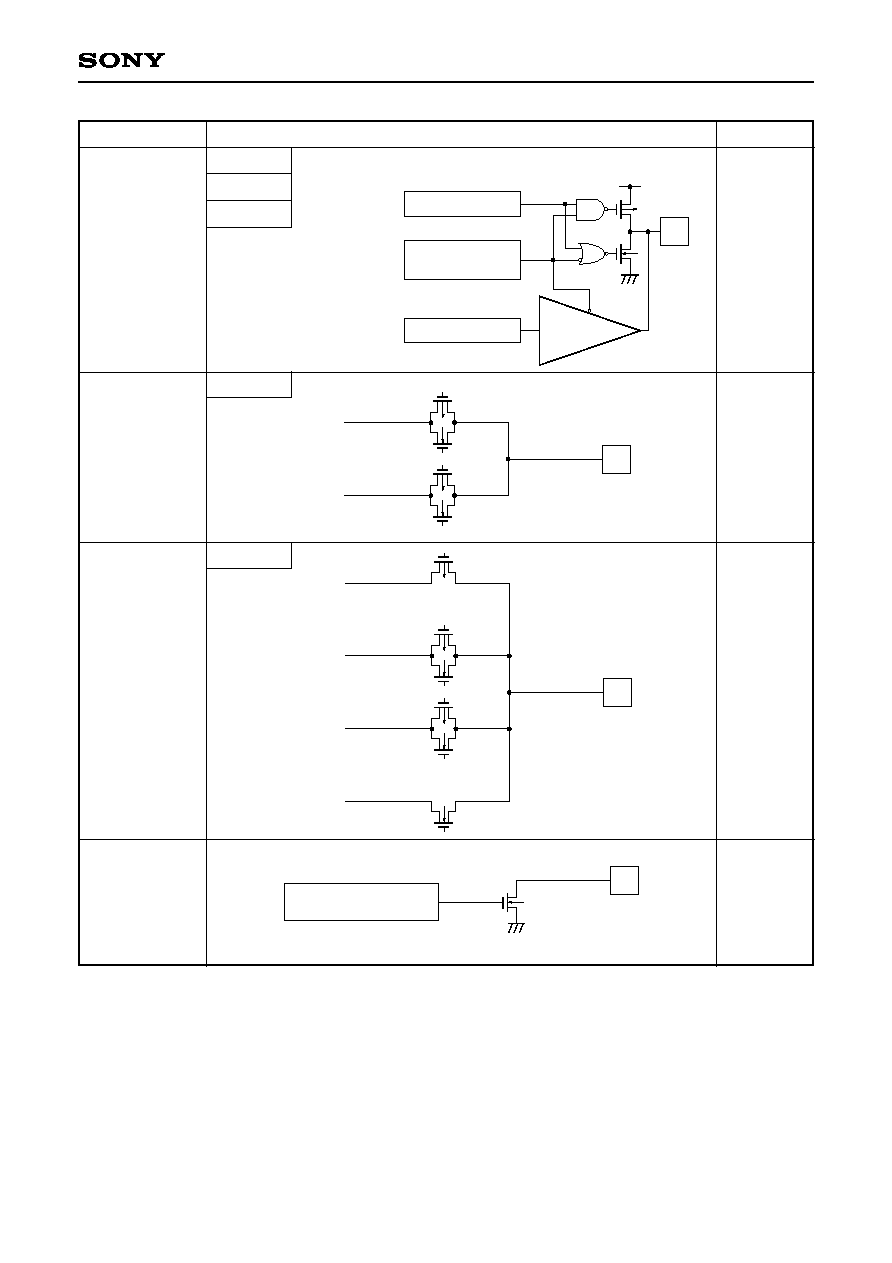

I/O Circuit Format for Pins

Port A

Pin

Circuit format

≠ 8 ≠

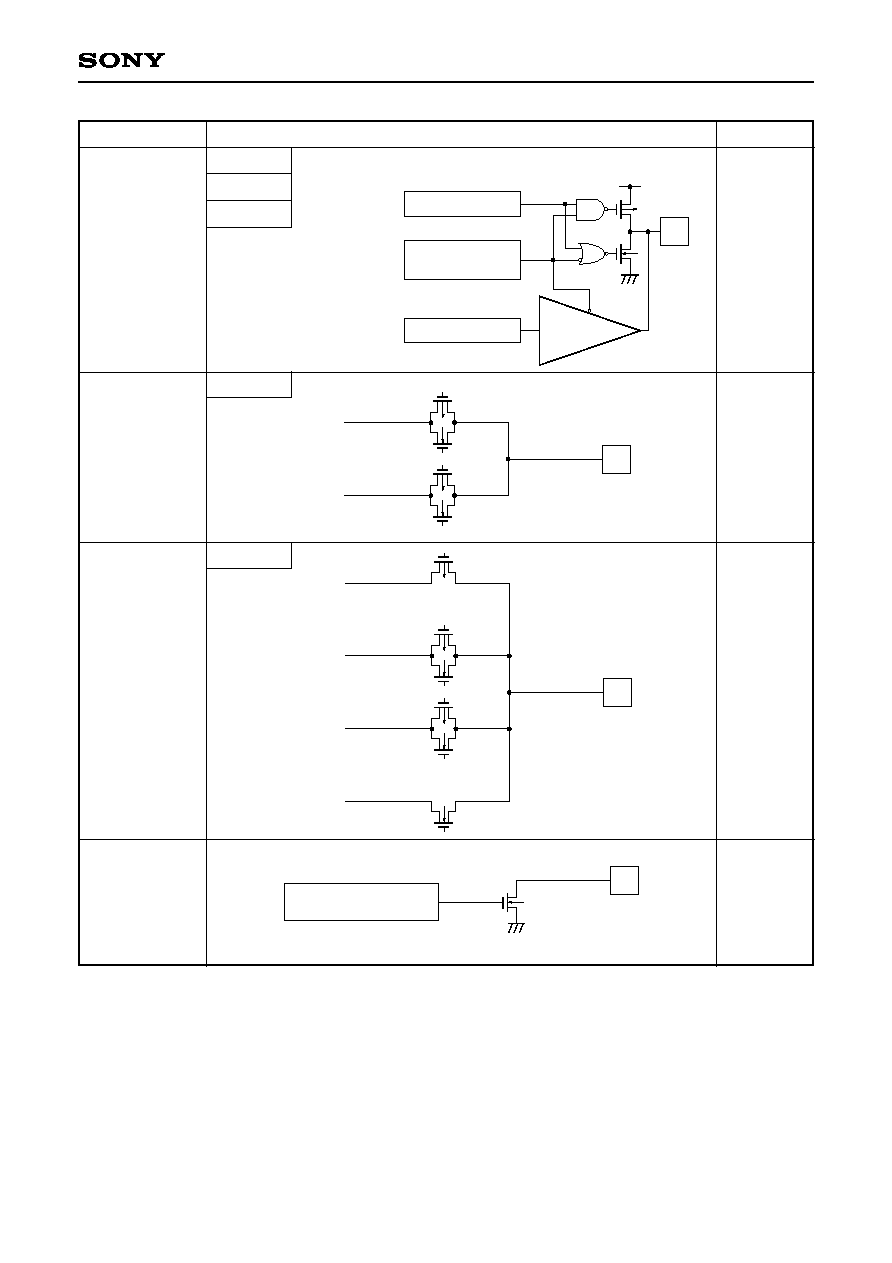

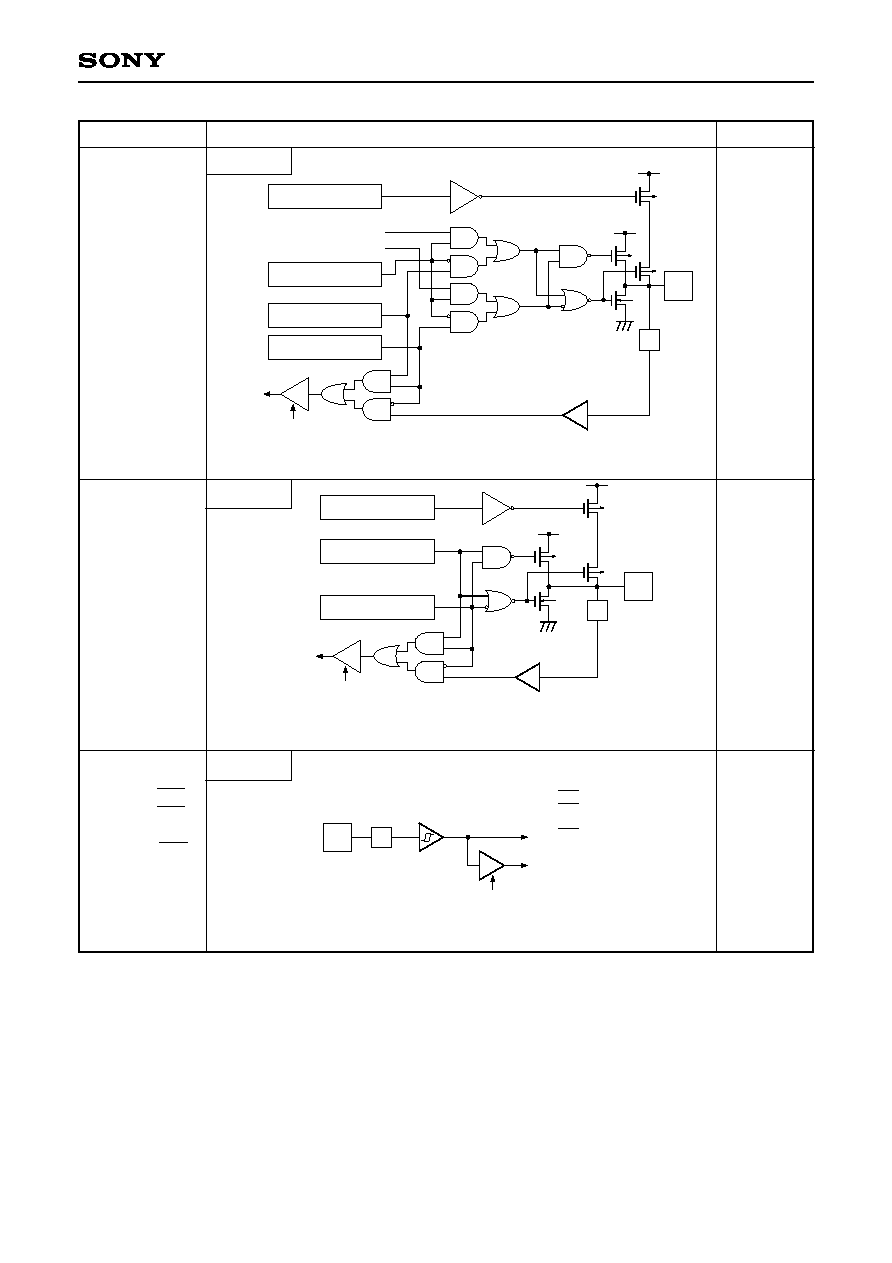

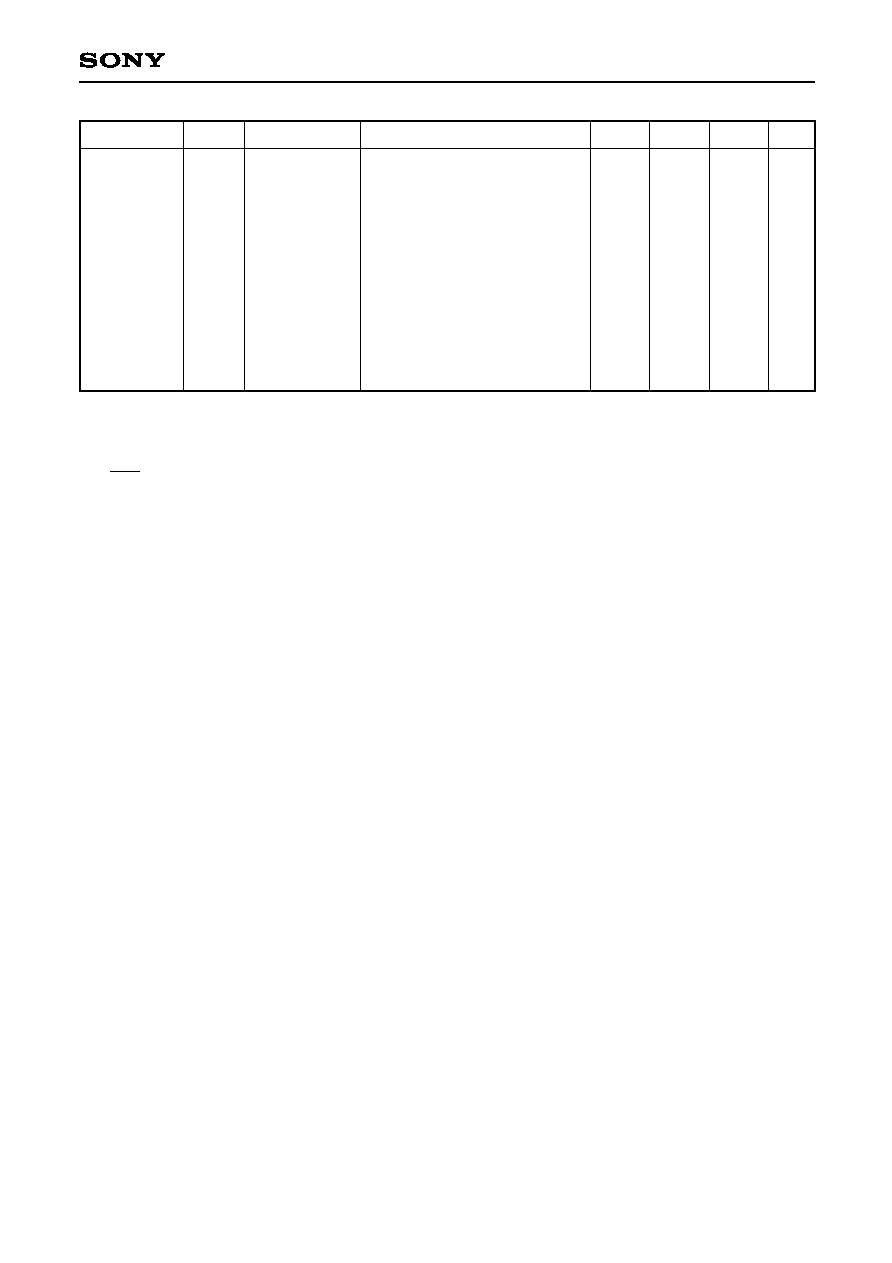

CXP832P40A

2 pins

Hi-Z

Hi-Z

Pin

When reset

Circuit format

PB4/SO0

PB7/SO1

PC0 to PC7

8 pins

5 pins

Hi-Z

PE0/INT0/EC0

PE1/INT1/EC1

PE2/INT2

PE3/INT3/NMI

PE4/RMC

IP

Schmitt input

INT0/EC0

INT1/EC1

INT2

INT3/NMI

RMC

Data bus

RD (Port E)

IP

Pull-up resistor

Port C data

Port C direction

"0" when reset

RD (Port C)

Data bus

1 Large current drive

of 12mA possible

2 Pull-up transistors

approx. 100k

2

"0" when reset

1

Pull-up transistors

approx. 100k

Pull-up resistor

Port B data

Port B direction

"0" when reset

RD (Port B)

Data

bus

IP

"0" when reset

Output enable

Port B output selection

"0" when reset

SO

Port E

Port C

Port B

≠ 9 ≠

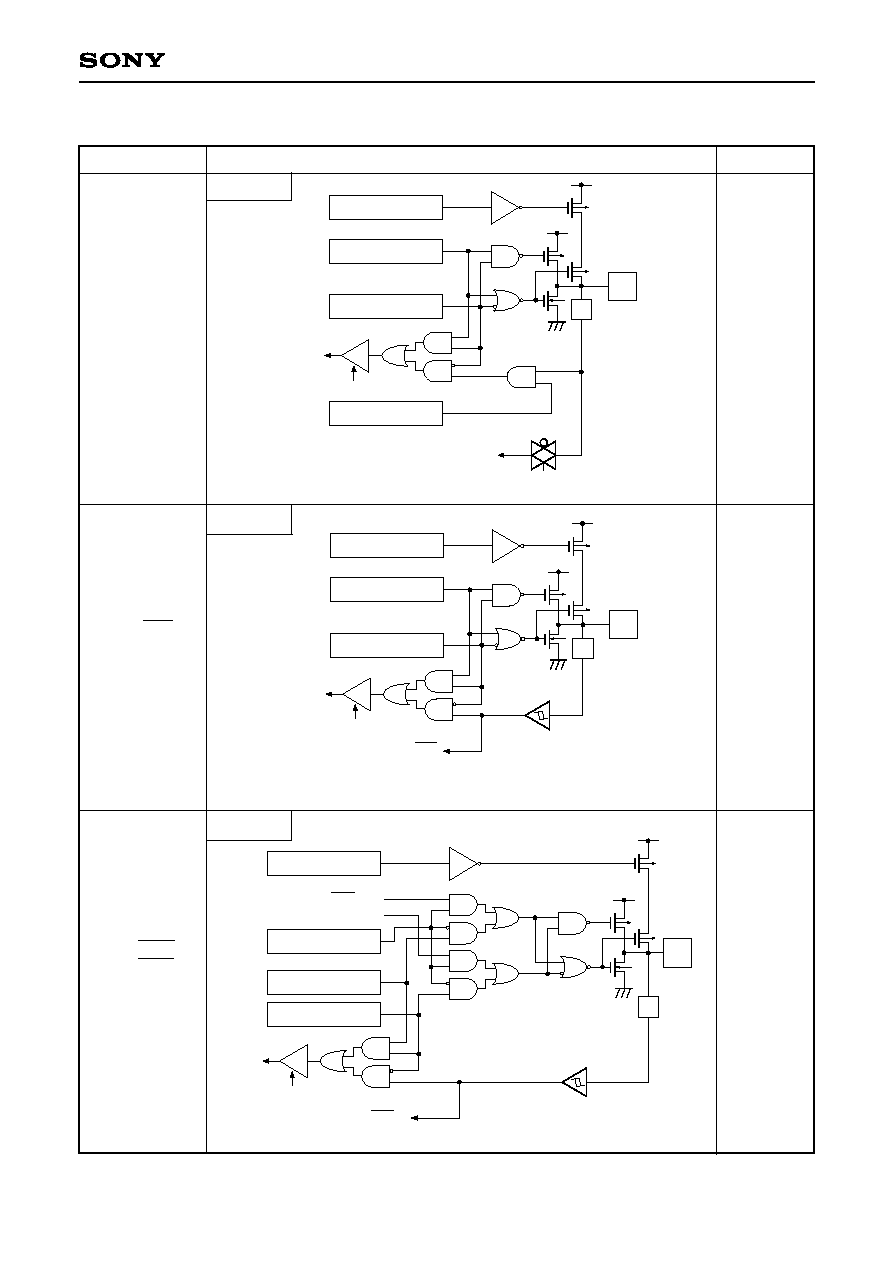

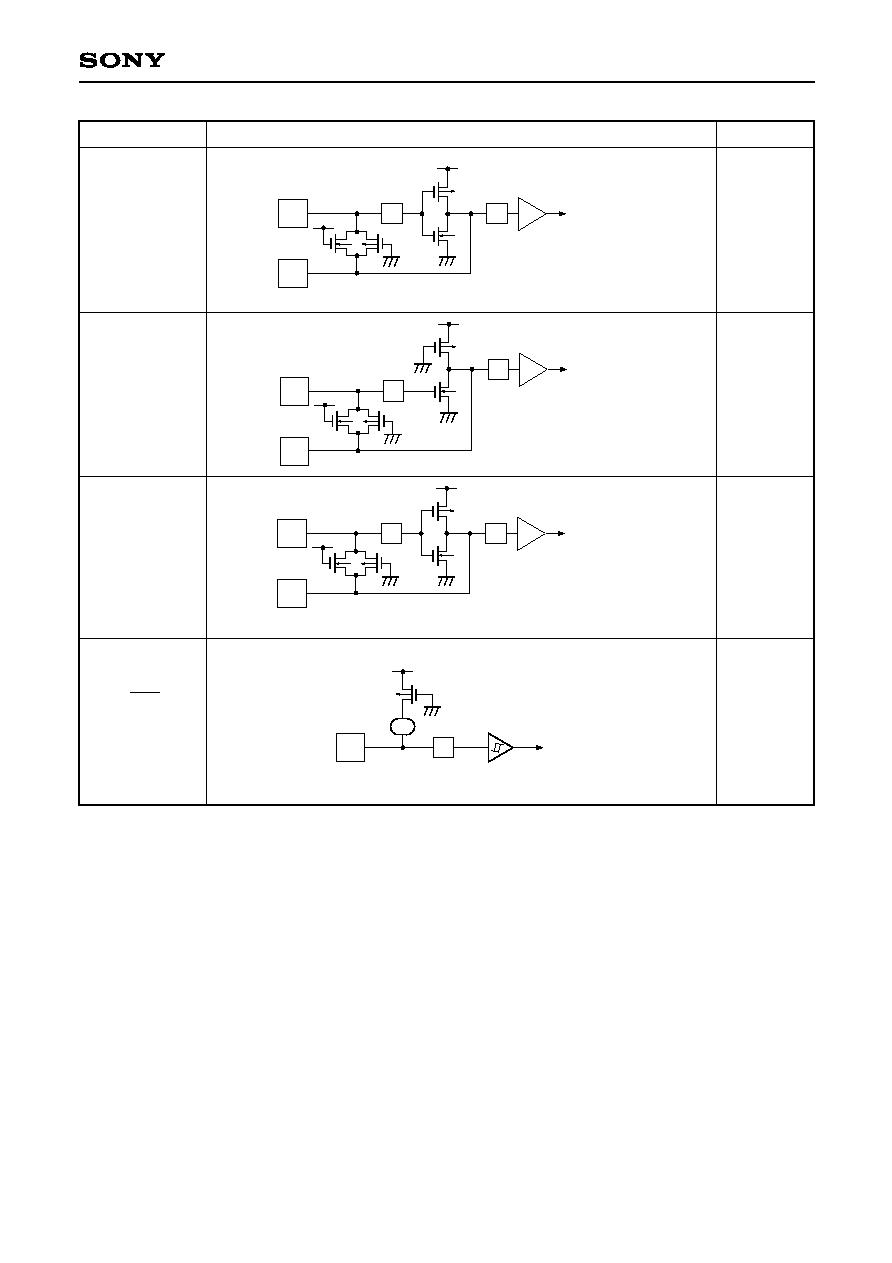

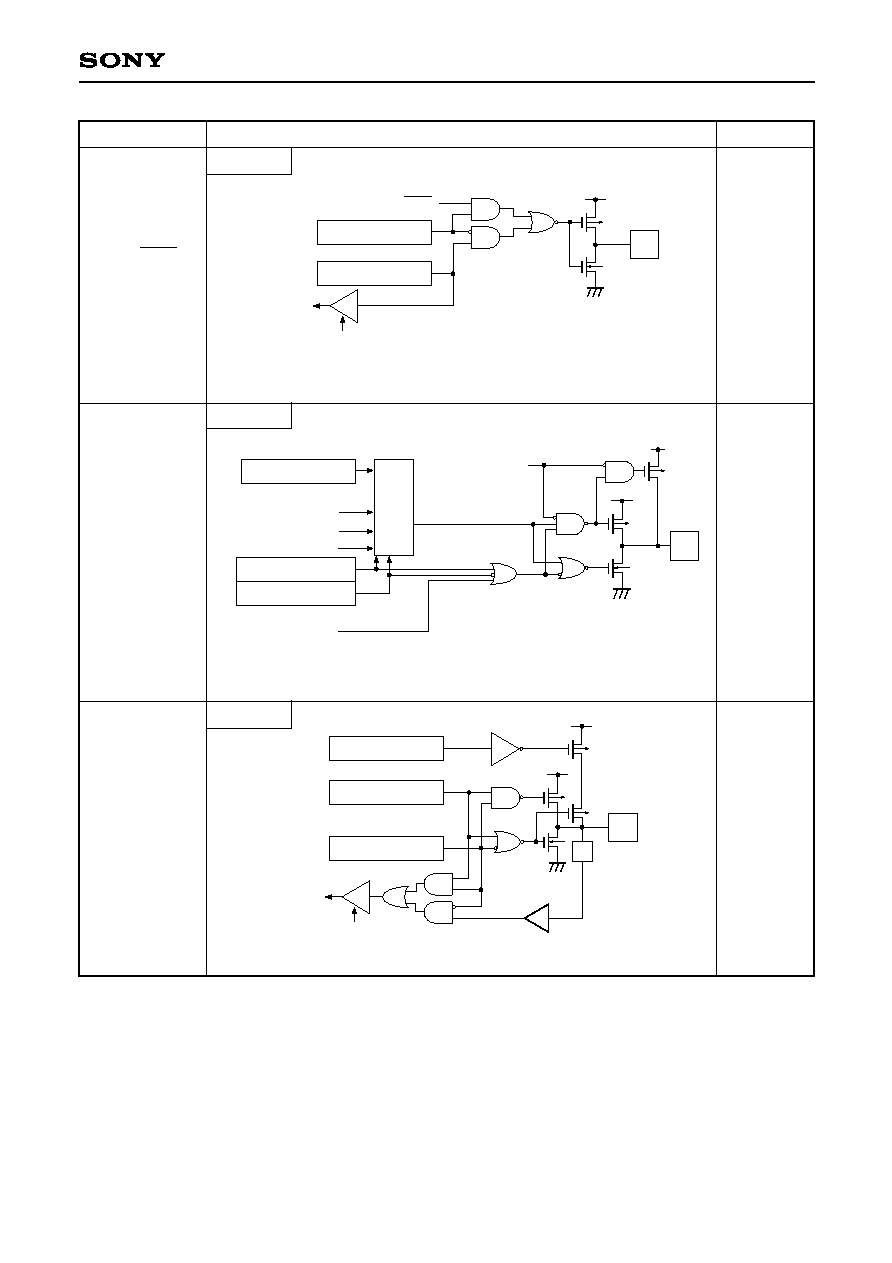

CXP832P40A

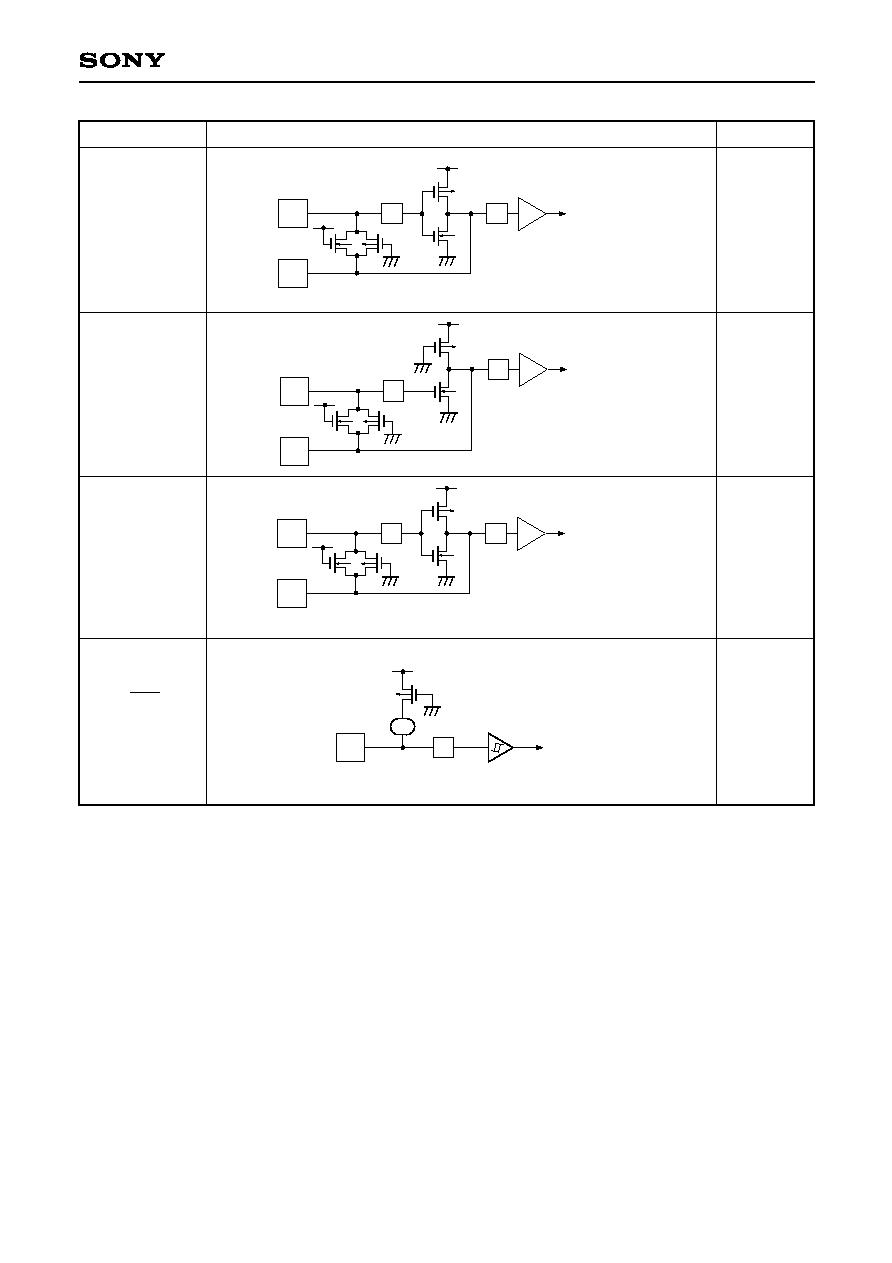

1 pin

P in

When reset

Circuit format

PE5/PWM

Port E output selection

RD (Port E)

Data bus

"0" when reset

Reset E data

"1" when reset

PWM

Port E

1 pin

High level

PE6/TO/ADJ

1

2

Port E data

"1" when reset

Port E output selection

MPX

Port E output selection

ADJ2K

ADJ16K

TO

Internal reset signal

1

Pull-up transistors approx. 150k

.

ADJ signals are frequency divider outputs

for 32kHz oscillation frequency adjustment.

ADJ2K provides usage as buzzer output.

2

TO Output enable

"00" when reset

Port E

8 pins

Hi-Z

PH0 to PH7

IP

Pull-up resistor

Port H data

Port H direction

"0" when reset

RD (Port H)

Data bus

Pull-up transistors approx. 100k

"0" when reset

Port H

High level

(High level

with 150k

resistor

when reset)

≠ 10 ≠

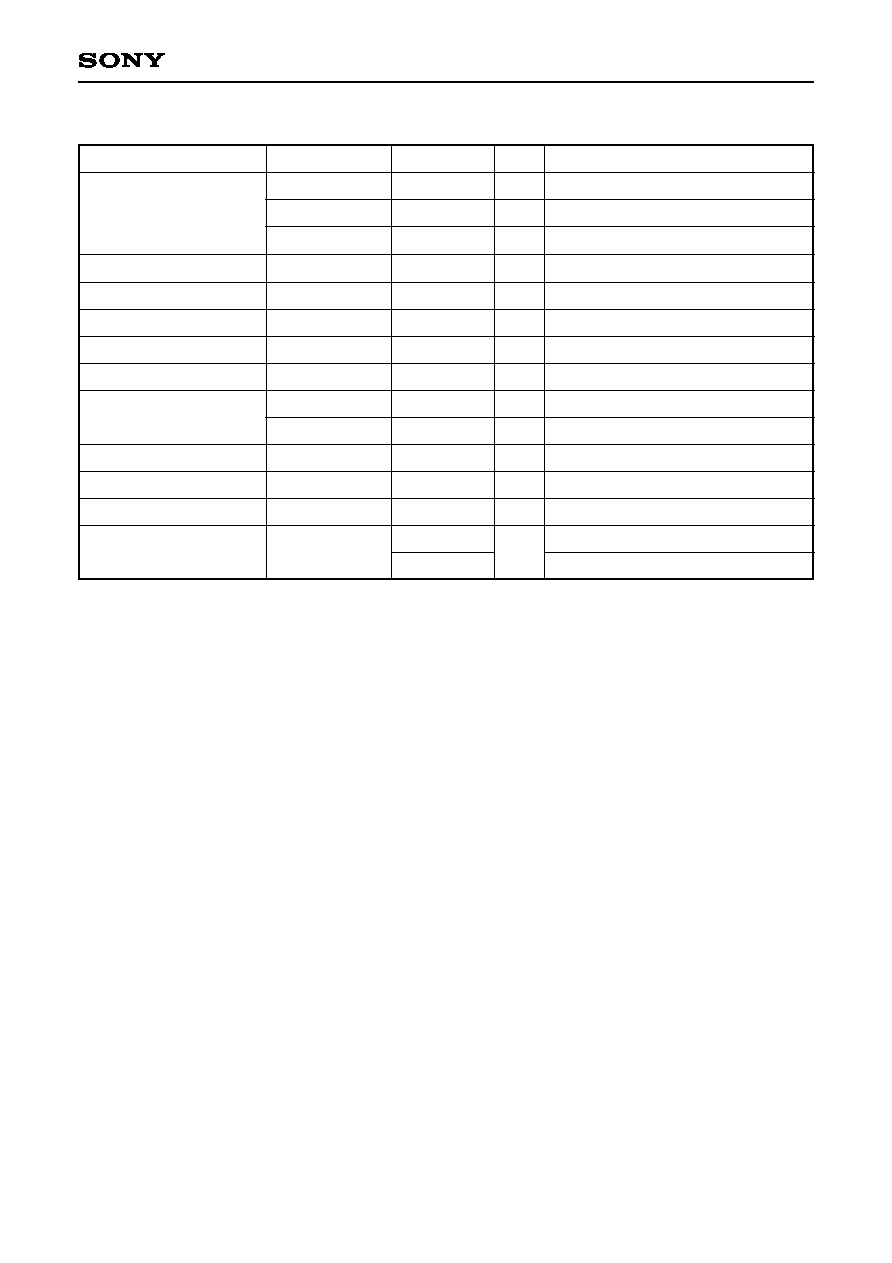

CXP832P40A

24 pins

Segment

output

(V

DD

level)

Pin

When reset

Circuit format

PD0 to PD7

PF0 to PF7

PG0 to PG7

Segment data

Segment

driver

Port/segment output

selection

"0" when reset

Port data

PD7 to PD4

PD3 to PD0

PF7 to PF0

PG7 to PG0

by a single bit unit

by 4-bit unit

by 8-bit unit

16 pins

SEG0 to

SEG15

V

CH

V

CL

4 pins

V

DD

level

COM0 to

COM3

V

LC1

V

LC2

V

LC3

V

DD

1 pin

Hi-Z

V

L

LCD control

(DSP bit)

"0" when reset

V

DD

level

Port D

Port F

Port G

Segment

Common

≠ 11 ≠

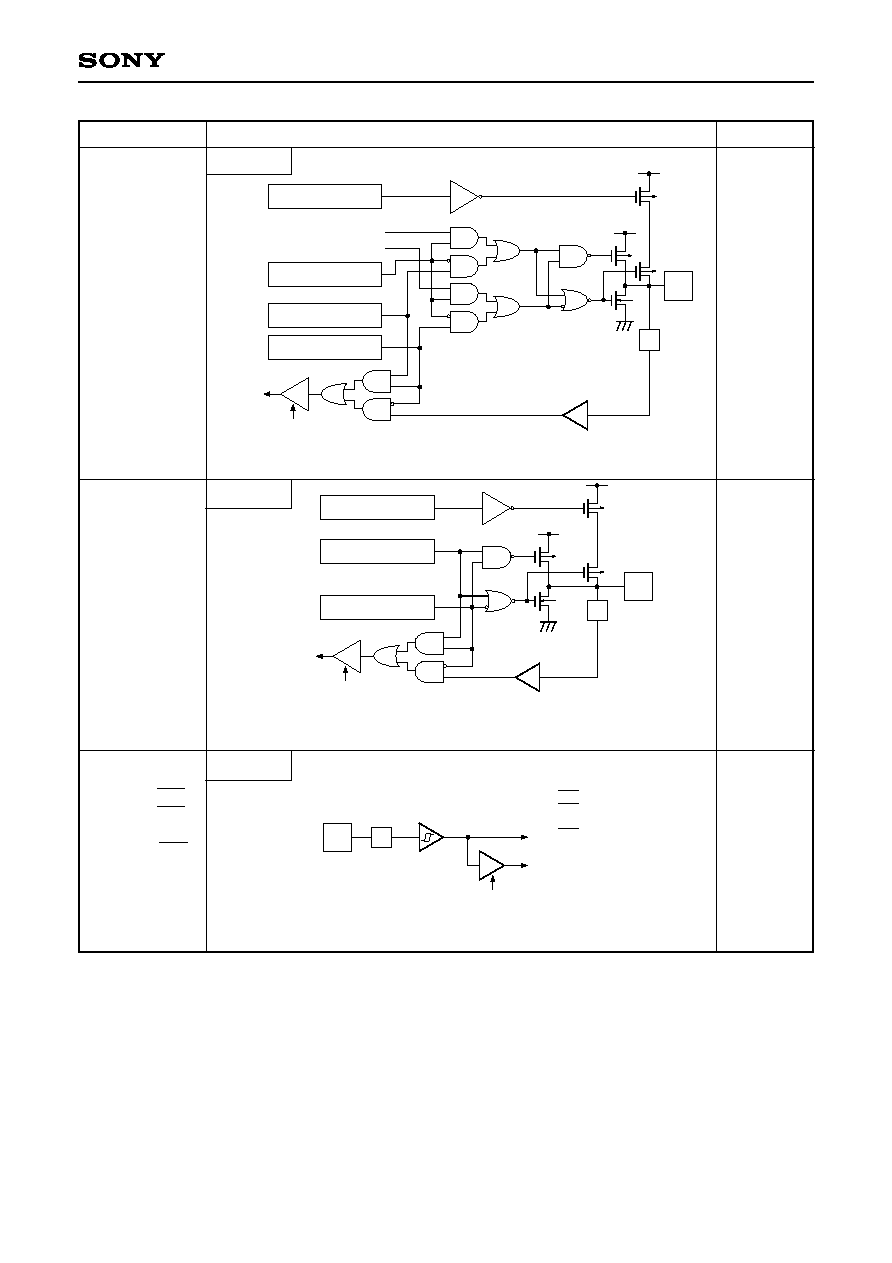

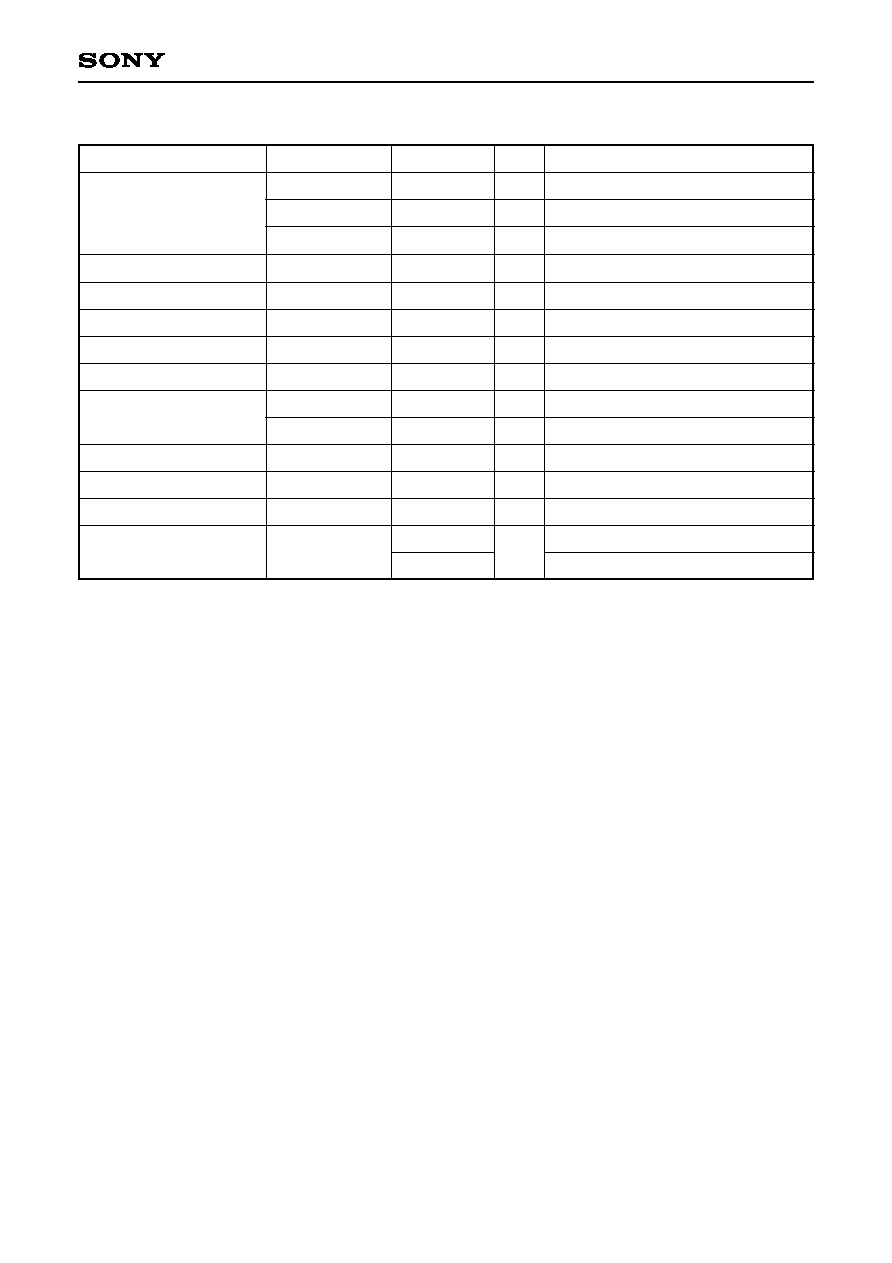

CXP832P40A

2 pins

Oscillation

Pin

When reset

Circuit format

EXTAL1

XTAL1

2 pins

EXTAL2

Hi-Z

XTAL2

High level

EXTAL2

XTAL2

2 pins

Oscillation

TEX

TX

1 pin

Low level

RST

EXTAL1

XTAL1

IP

IP

EXTAL2

XTAL2

IP

IP

TEX

TX

IP

IP

IP

OP

Schmitt input

Mask option

Pull-up resistor

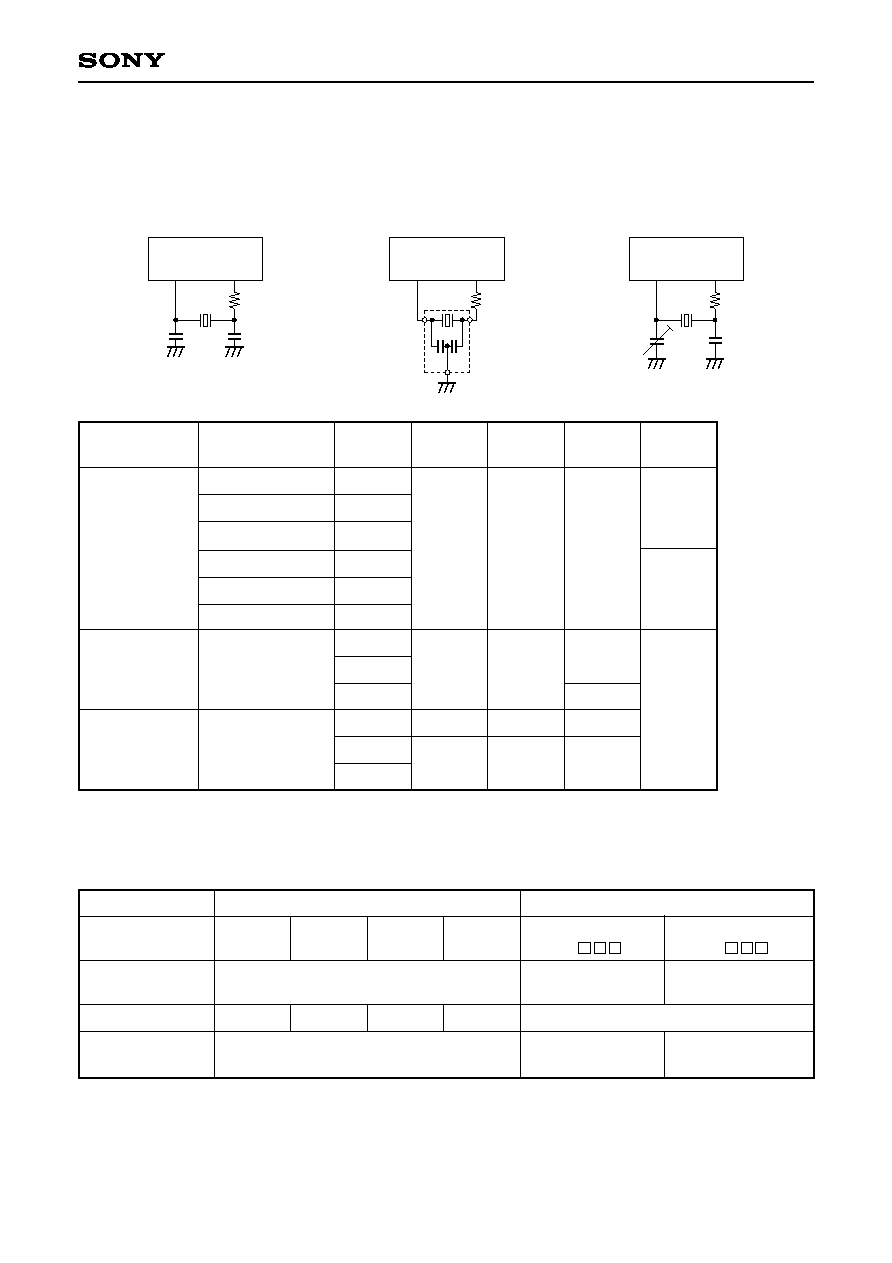

∑ Diagram shows circuit

composition during

oscillation.

∑ Feedback resistor is

removed during stop.

XTAL1 becomes "High"

level.

∑ Diagram shows circuit

composition during

oscillation.

∑ Feedback resistor is

removed during stop.

XTAL2 becomes "High"

level.

∑ Diagram shows circuit

composition during

oscillation.

∑ When the operation of the oscillation

circuit is stopped by the software, the

feedback resistor is removed and TEX

and TX become "Low" level and "High"

level respectively.

≠ 12 ≠

CXP832P40A

1) V

IN

and V

OUT

must not exceed V

DD

+ 0.3V.

2) The large current drive transistor is the N-ch transistor of Port C (PC)

Note) Usage exceeding absolute maximum ratings may permanently impair the LSI. Normal operation should

be conducted under the recommended operating conditions. Exceeding these conditions may

adversely affect the reliability of the LSI.

Supply voltage

LCD bias voltage

Input voltage

Output voltage

High level output current

High level total output current

Low level total output current

Operating temperature

Storage temperature

Allowable power dissipation

V

DD

Vpp

AV

SS

V

LC1

, V

LC2

, V

LC3

V

IN

V

OUT

I

OH

I

OH

I

OL

I

OLC

I

OL

Topr

Tstg

P

D

Low level output current

≠0.3 to +7.0

≠0.3 to +13.0

≠0.3 to +0.3

≠0.3 to +7.0

1

≠0.3 to +7.0

1

≠0.3 to +7.0

1

≠5

≠50

15

20

100

≠10 to +75

≠55 to +150

600

380

V

V

V

V

V

V

mA

mA

mA

mA

mA

įC

įC

mW

Incorporated PROM

Output per pin

Total for all output pins

Value per pin, excluding large current outputs

Value per pin

2

for large current outputs

Total for all output pins

QFP package

LQFP package

Iem

Symbol

Rating

Unit

Remarks

Absolute Maximum Ratings

(Vss = 0V)

≠ 13 ≠

CXP832P40A

LCD bias voltage

High level

input voltage

Low level

input voltage

Operating temperature

Supply voltage

5.5

5.5

5.5

5.5

5.5

V

DD

V

DD

V

DD

V

DD

+ 0.3

0.3V

DD

0.2V

DD

0.4

+75

V

V

V

V

V

V

V

V

įC

V

Item

Symbol

Min.

Max.

Unit

Remarks

4.5

3.5

3.0

2.7

2.5

Vss

0.7V

DD

0.8V

DD

V

DD

≠ 0.4

0

0

≠0.3

≠10

V

LC1

V

LC2

V

LC3

V

IH

V

IHS

V

IHEX

V

IL

V

ILS

V

ILEX

Topr

High-speed mode guaranteed operation range

1

Low-speed mode guaranteed operation range

1

Guaranteed operation range during

EXTAL2 clock (sub clock mode)

Guaranteed operation range with TEX clock

Guaranteed data hold range during STOP

6

LCD power supply range

5

2

Hysteresis input

3

EXTAL

4

2

Hysteresis input

3

EXTAL

4

V

DD

1) During EXTAL1 clock (main clock mode), high-speed mode is 1/2 frequency division clock selection; low-

speed mode is 1/16 frequency division clock selection.

2) Value for each pin of normal input ports (PA, PB4, PB7, PC and PH).

3) Value of the following pins; RST, CINT CS0, SI0, SI1, SCK0, SCK1, EC0/INT0, EC1/INT1, INT2,

NMI/INT3, and RMC.

4) Specifies only during external clock input.

5) Optimal values are determined by LCD used.

6) Vpp and V

DD

should be set to same voltage.

Recommended Operating Conditions

(Vss = 0V)

Vpp = V

DD

Vpp

≠ 14 ≠

CXP832P40A

V

DD

= 4.5V, I

OH

= ≠0.5mA

V

DD

= 4.5V, I

OH

= ≠1.2mA

V

DD

= 4.5V, I

OL

= 1.8mA

V

DD

= 4.5V, I

OL

= 3.6mA

V

DD

= 4.5V, I

OL

= 12.0mA

V

DD

= 5.5V, V

IH

= 5.5V

V

DD

= 5.5V, V

IL

= 0.4V

V

DD

= 5.5V, V

IH

= 5.5V

V

DD

= 5.5V, V

IL

= 0.4V

V

DD

= 5.5V, V

IH

= 5.5V

V

DD

= 5.5V, V

IL

= 0.4V

V

DD

= 5.5V, V

IL

= 0.4V

V

DD

= 4.5V, V

IH

= 4.0V

V

DD

= 5.5V, V

IL

= 0.4V

V

DD

= 5.5V,

V

I

= 0, 5.5V

V

DD

= 5V,

V

LC1

= 3.75V

V

LC2

= 2.5V

V

LC3

= 1.25V

High level

output voltage

I/O leakage

current

Supply

current

4

4.0

3.5

0.5

≠0.5

0.3

≠0.3

0.1

≠0.1

≠1.5

≠3.33

V

V

V

V

V

ĶA

ĶA

ĶA

ĶA

ĶA

ĶA

ĶA

ĶA

ĶA

ĶA

k

k

PC

PA, PB, PC,

PD

1

, PE5,

PE6

PF to PG

1

V

L

(V

OL

only)

EXTAL1

EXTAL2

TEX

RST

2

Item

Symbol

Pins

Conditions

Min.

PA to PC

3

,

PH

3

PE0 to PE4,

RST

2

V

DD

I

IZ

Common

output

impedance

R

COM

Segment

output

impedance

R

SEG

COM0 to

COM3

SEG0 to

SEG15

SEG16 to

SEG39

1

I

DD1

High-speed mode operation

(1/2 frequency division clock)

I

DD3

I

DDS1

I

DDS3

I

DDSS

V

OH

V

OL

I

IHE1

I

ILE1

I

IHE2

I

ILE2

I

IHT

I

ILT

I

ILR

I

IH

I

IL

Low level

output voltage

Input current

3

5

Typ.

0.4

0.6

1.5

40

≠40

30

≠30

10

≠10

≠400

≠50

Ī10

5

15

Max.

Unit

I

DD2

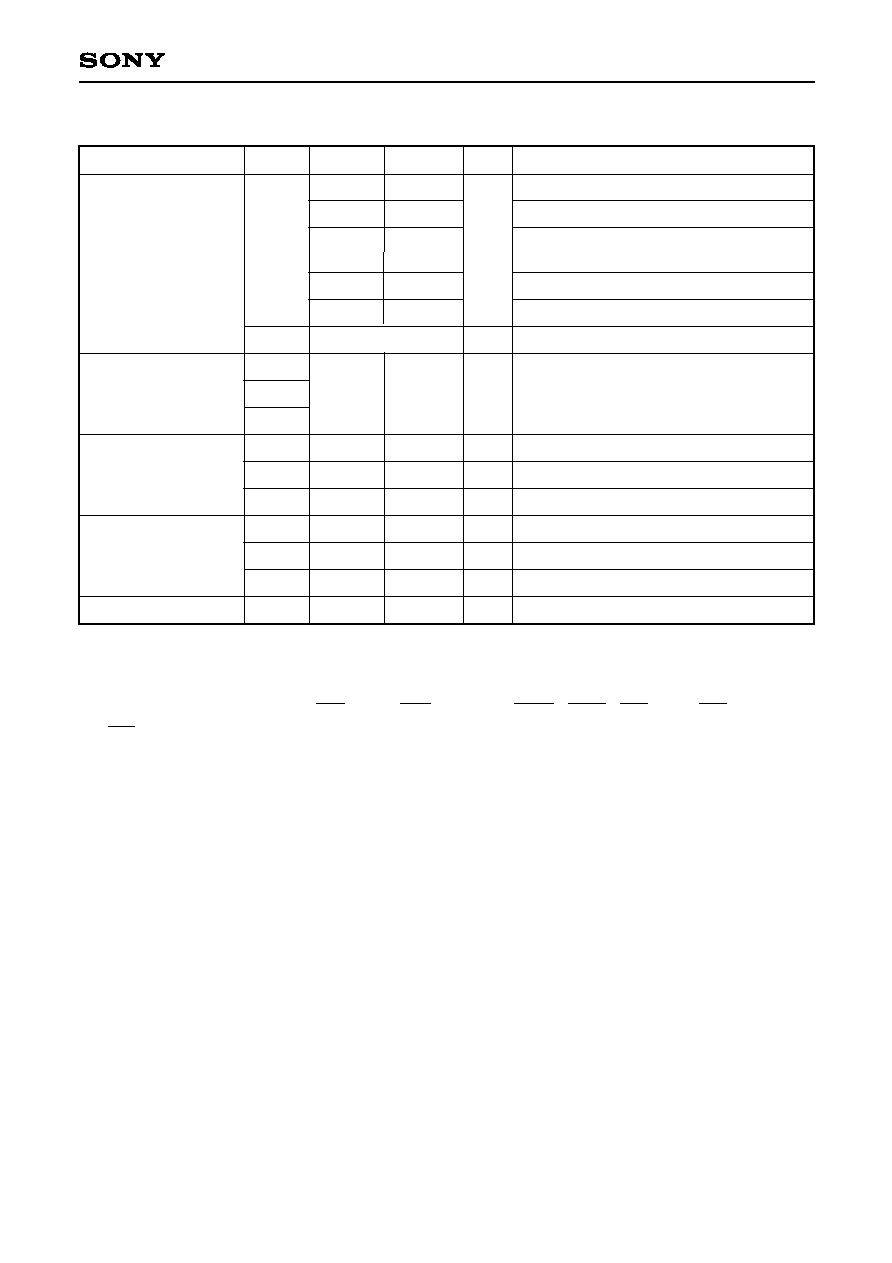

DC Characteristics

Electrical Characteristics

(Ta = ≠10 to +75įC, Vss = 0V)

V

DD

= 5.5V, 10MHz crystal oscillation

(C

1

= C

2

= 15pF)

V

DD

= 3.5V, 500kHz crystal oscillation

(C

1

= C

2

= 22pF)

V

DD

= 3V, 32kHz crystal oscillation

(C

1

= C

2

= 47pF)

SLEEP mode

STOP mode

V

DD

= 5.5V, 10MHz, 500kHz crystal

oscillation and termination of 32kHz

oscillation

V

DD

= 5.5V, 10MHz crystal oscillation

(C

1

= C

2

= 15pF)

V

DD

= 3V, 32kHz crystal oscillation

(C

1

= C

2

= 47pF)

20

45

mA

0.6

1.3

mA

2.0

3.8

mA

1.5

8

mA

9

30

ĶA

I

DDS2

V

DD

= 3.5V, 500kHz crystal oscillation

(C

1

= C

2

= 22pF)

0.5

1.0

mA

30

ĶA

≠ 15 ≠

CXP832P40A

1) Common pins of PD0/SEG16 to PD7/SEG23, PF0/SEG24 to PF7/SEG31, PG0/SEG32 to PG7/SEG39,

PD, PF and PG are the case when the common pin is selected as port; SEG16 to SEG39 are when the

common pin is selected as segment output.

2) RST specifies the input current when pull-up resitor has been selected; leakage current when no resistor

has been selected.

3) PA to PC, and PH specify the input current when a pull-up resistor has been selected; leakage current

when no resistor has been selected. (PE0 to PE4 specify the leakage current.)

4) When all output pins are left open.

Clock 1MHz

0V for all pins excluding

measured pins

Input capacity

10

20

pF

Pins other than

PB7, PE5, PE6

V

LC1

to V

LC3

COM0 to COM3

SEG0 to SEG15

PD0/SEG16 to

PD7/SEG23

PF0/SEG24 to

PF7/SEG31

PG0/SEG32 to

PG7/SEG39

AV

REF

, AV

SS

,

V

DD

, V

SS

Item

Symbol

Pins

Conditions

Min.

C

IN

Typ.

Max.

Unit

≠ 16 ≠

CXP832P40A

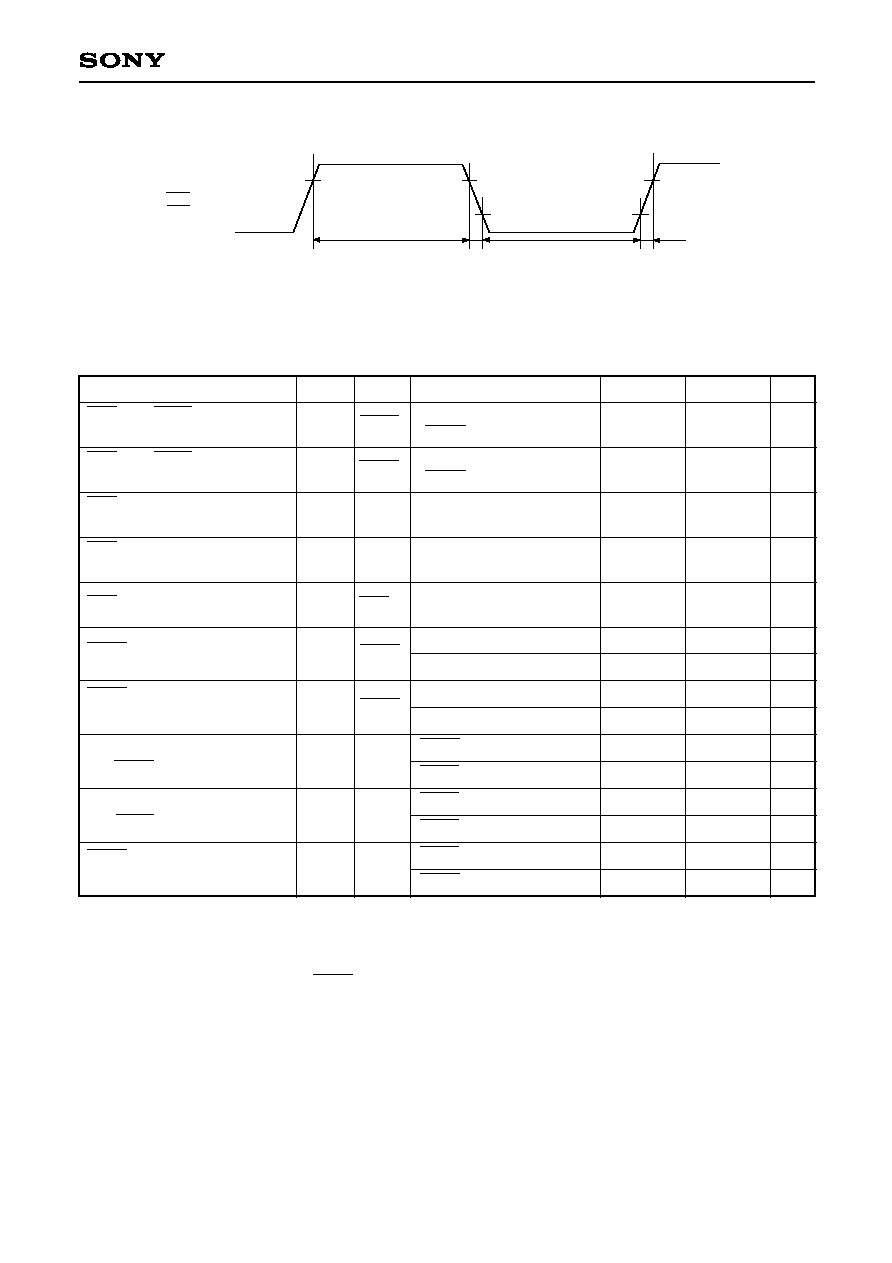

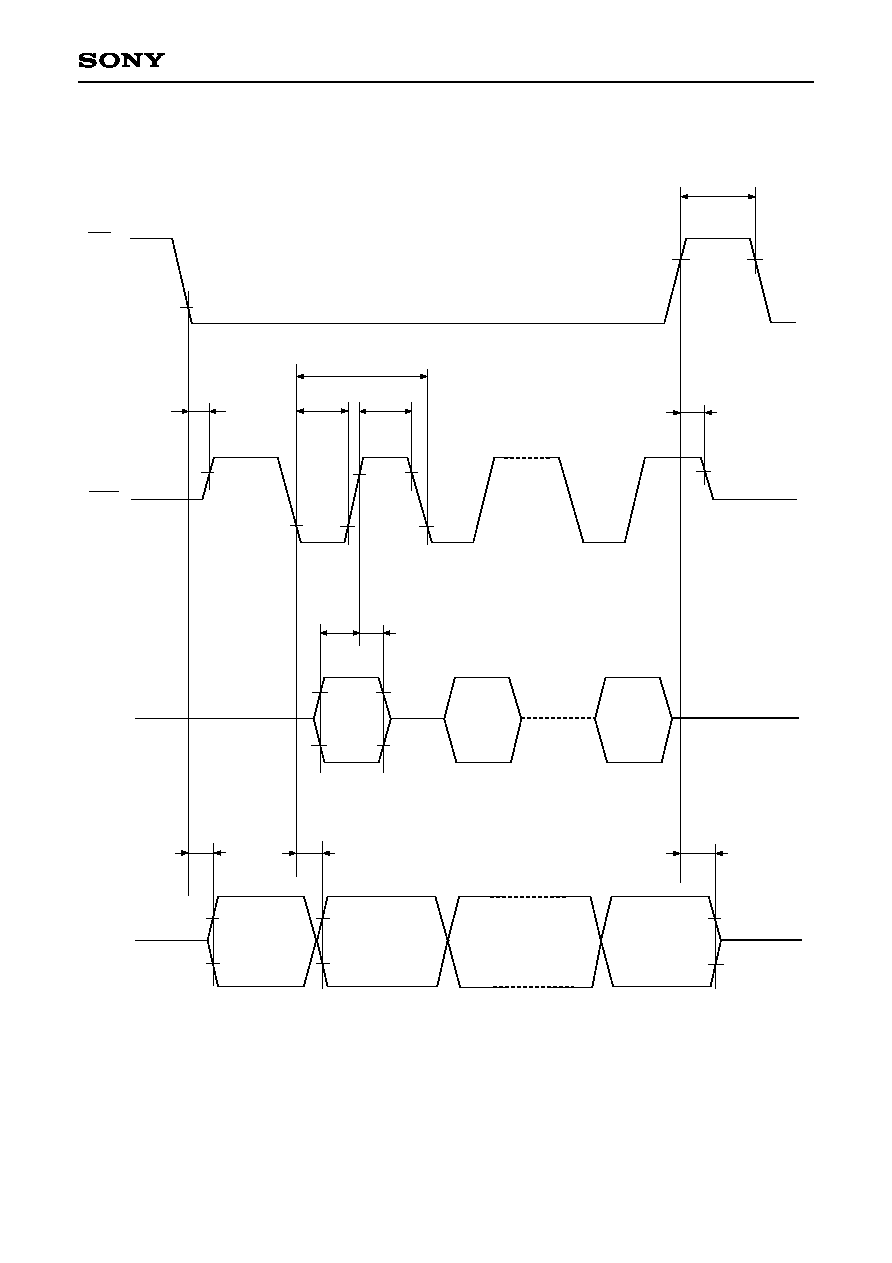

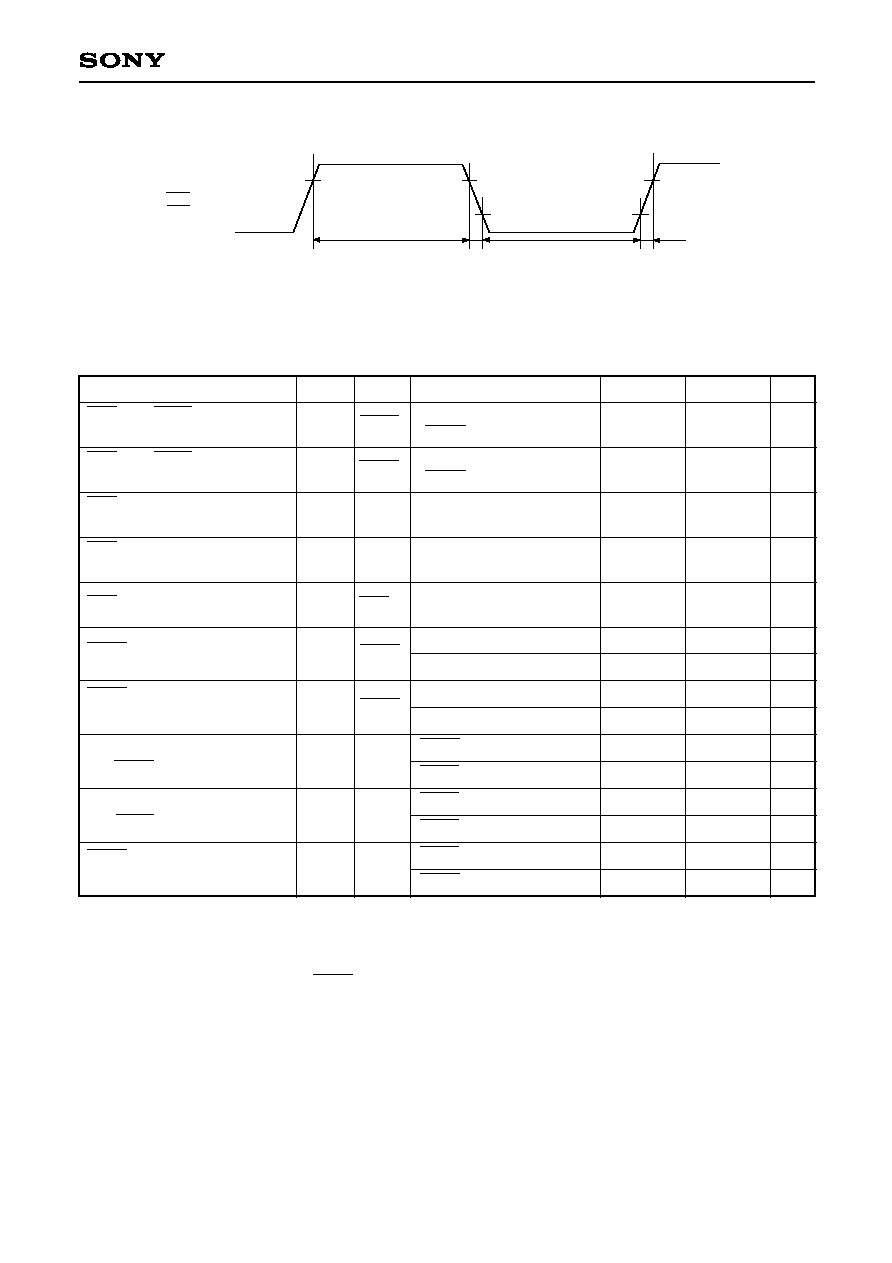

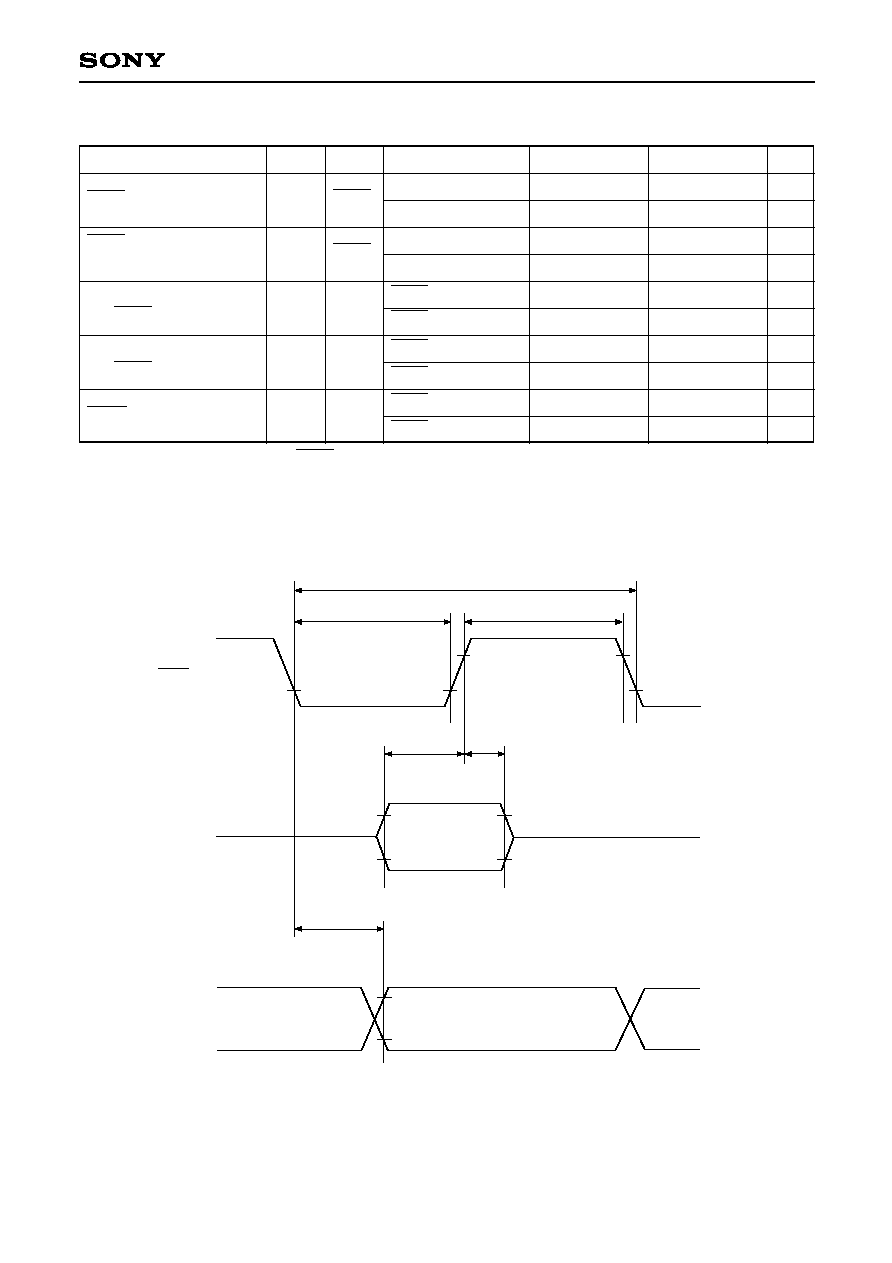

t

sys indicates the three values below according to the upper two bits (CPU clock selection) of the clock

control register (address: 00FE

H

).

t

sys [ns] = 2000/fc (upper two bits = "00"), 4000/fc (upper two bits = "01"), 16000/fc (upper two bits = "11").

EXTAL1

EXTAL2

t

XH

t

XL

t

CF

t

CR

0.4V

V

DD

≠ 0.4V

1/fc

Crystal oscillation

Ceramic oscillation

EXTAL

XTAL

External clock

EXTAL

XTAL

74HC04

C

1

C

2

32kHz clock applied condition

Crystal oscillation

TEX

TX

C

1

C

2

AC Characteristics

(1) Clock timing

System clock frequency

System clock input

pulse width

System clock input rise and

fall time

System clock frequency

System clock input pulse width

System clock input rise and

fall time

Event count input clock pulse

width

Event count input clock rise

and fall time

System clock frequency

Event count input clock input

pulse width

Event count input clock rise

and fall time

f

C

t

XL

,

t

XH

t

CR

,

t

CF

f

C

t

XL

,

t

XH

t

CR

,

t

CF

t

EH

,

t

EL

t

ER

,

t

EF

f

C

t

TL

,

t

TH

t

TR

,

t

TF

XTAL1

EXTAL1

EXTAL1

EXTAL1

XTAL2

EXTAL2

EXTAL2

EXTAL2

EC0

EC1

EC0

EC1

TEX

TX

TEX

TEX

MHz

ns

ns

MHz

ns

ns

ns

ms

kHz

Ķs

ms

Item

Symbol

Pin

Conditions

Min.

Unit

Fig. 1, Fig. 2

Fig. 1, Fig. 2

external clock drive

Fig. 1, Fig. 2

external clock drive

V

DD

= 3.0 to 5.5V

Fig. 1, Fig. 2

V

DD

= 3.0 to 5.5V

Fig. 1, Fig. 2

external clock drive

V

DD

= 3.0 to 5.5V

Fig. 1, Fig. 2

external clock drive

Fig. 3

Fig. 3

V

DD

= 2.7 to 5.5V

Fig. 2 (32kHz clock

applied condition)

Fig. 3

Fig. 3

1

37.5

0.3

450

t

sys + 50

10

Typ.

0.5

32.768

Max.

10

200

0.7

200

20

20

(Ta = ≠10 to +75įC, V

DD

= 4.5 to 5.5V, Vss = 0V)

Fig. 2. Clock applied conditions

Fig. 1. Clock timing

≠ 17 ≠

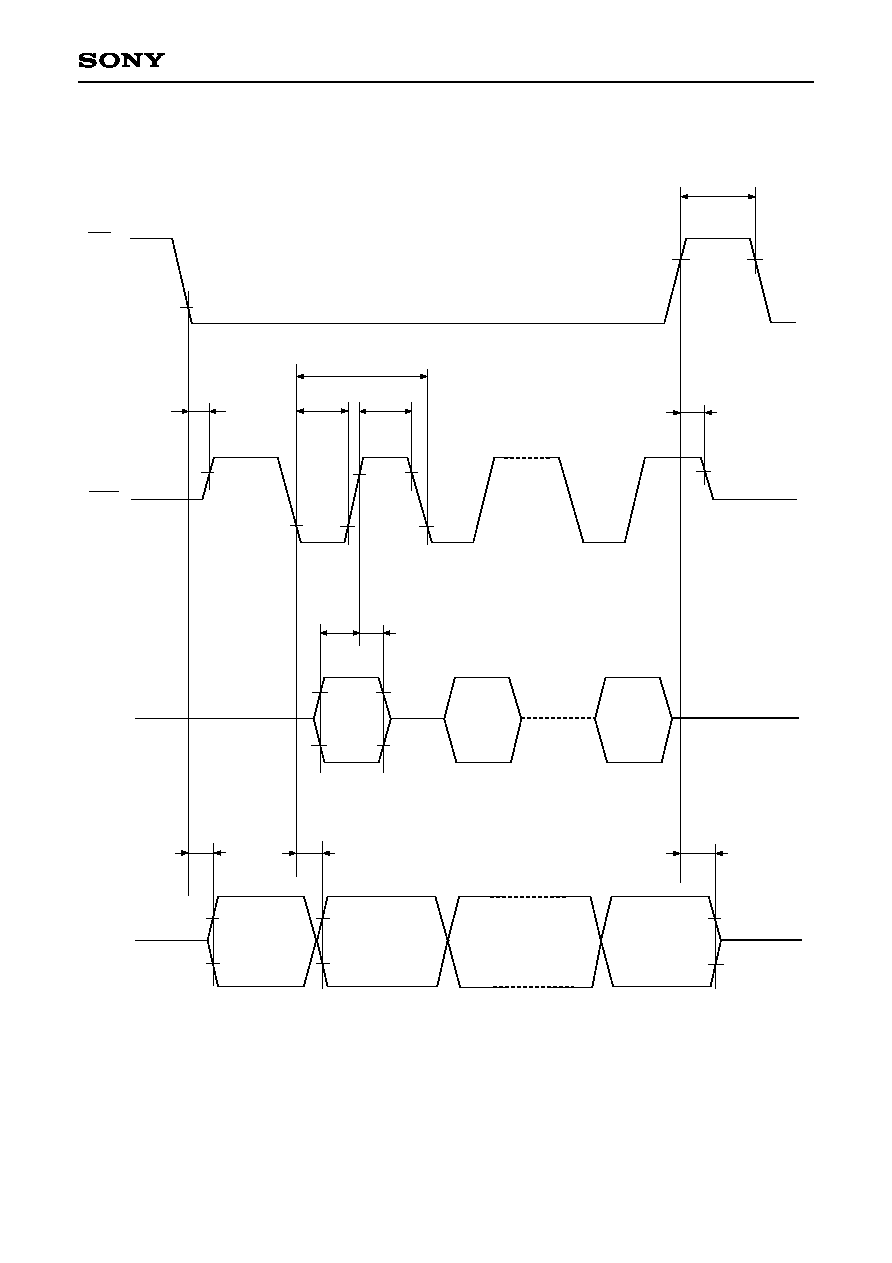

CXP832P40A

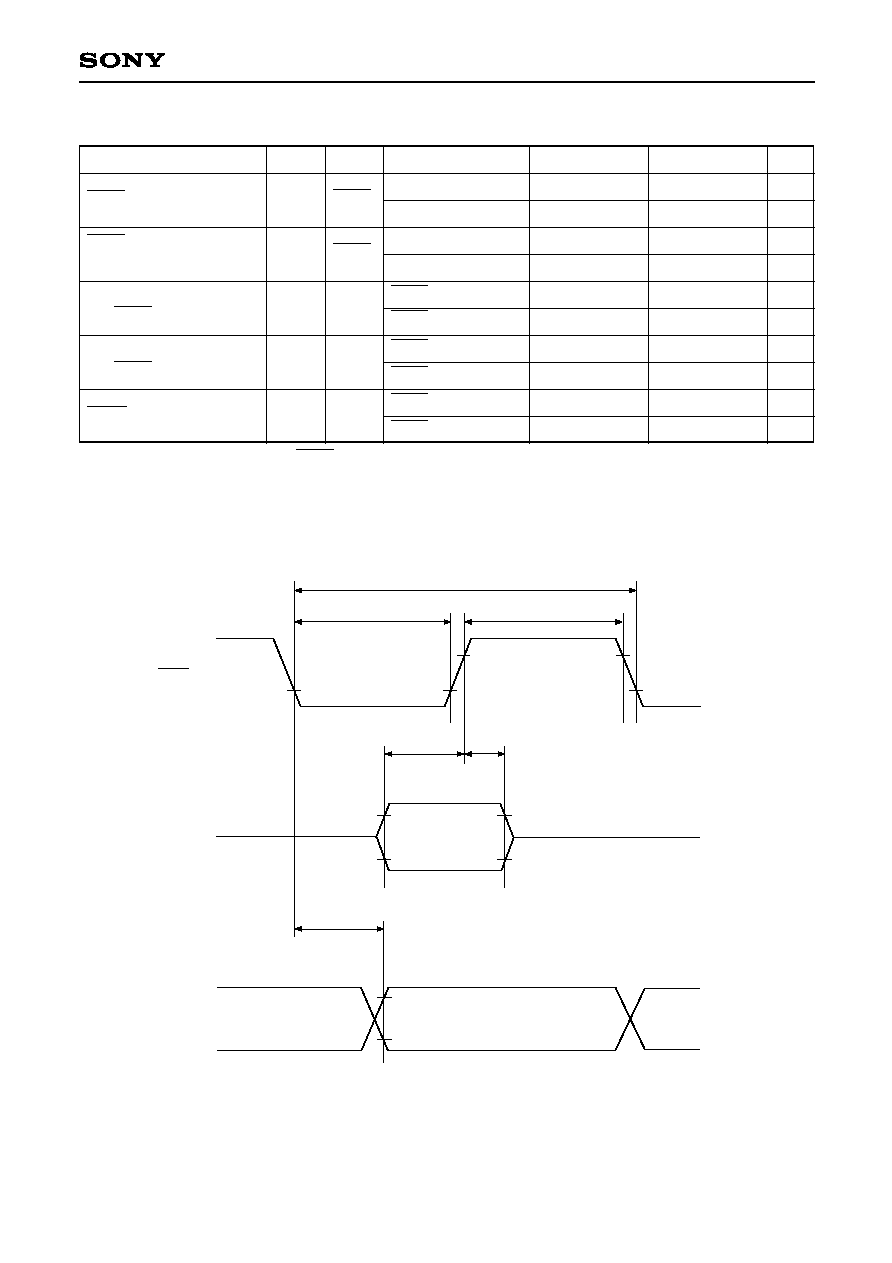

Chip select transfer mode

(SCK0 = output mode)

Chip select transfer mode

(SCK0 = output mode)

Chip select transfer mode

Chip select transfer mode

Chip select transfer mode

Note 1)

t

sys indicates the three values below according to the upper two bits (CPU clock selection) of the

clock control register (address: 00FE

H

).

t

sys [ns] = 2000/fc (upper two bits = "00"), 4000/fc (upper two bits = "01"), 16000/fc (upper two bits = "11")

Note 2) The load condition for the SCK0 output mode, SO0 output delay time is 50pF + 1TTL.

(2) Serial transfer (CH0)

(Ta = ≠10 to +75įC, V

DD

= 4.5 to 5.5V, Vss = 0V)

Item

CS0

SCK0

delay time

CS0

SCK0

float delay time

CS0

SO0

delay time

CS0

SO0

float delay time

CS0 high level width

SCK0 cycle time

SCK0 high and low level

widths

SI0 input setup time

(for SCK0

)

SI0 input hold time

(for SCK0

)

SCK0

SO0

delay time

t

DCSK

t

DCSKF

t

DCSO

t

DCSOF

t

WHCS

t

KCY

t

KH

t

KL

t

SIK

t

KSI

t

KSO

SCK0

SCK0

SO0

SO0

CS0

SCK0

SCK0

SI0

SI0

SO0

Input mode

Output mode

Input mode

Output mode

SCK0 input mode

SCK0 output mode

SCK0 input mode

SCK0 output mode

SCK0 input mode

SCK0 output mode

ns

ns

ns

ns

ns

Symbol

Pin

Min.

t

sys + 200

t

sys + 200

t

sys + 200

t

sys + 200

t

sys + 200

2

t

sys + 200

16000/fc

t

sys + 100

8000/fc ≠ 50

100

200

t

sys + 200

100

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

t

sys + 200

100

Max.

Unit

Conditions

TEX

EC0

EC1

t

EH

t

EL

t

EF

t

ER

0.2V

DD

0.8V

DD

t

TH

t

TL

t

TF

t

TR

Fig. 3. Event count clock timing

≠ 18 ≠

CXP832P40A

Fig. 4. Serial transfer CH0 timing

CS0

SCK0

0.2V

DD

0.8V

DD

t

WHCS

t

DCSK

t

DCSKF

0.8V

DD

0.2V

DD

0.8V

DD

t

KCY

t

KL

t

KH

0.8V

DD

0.2V

DD

SI0

t

SIK

t

KSI

Input data

t

DCSO

t

KSO

t

DCSOF

Output data

0.8V

DD

0.2V

DD

SO0

≠ 19 ≠

CXP832P40A

Serial Transfer (CH1)

(Ta = ≠10 to +75įC, V

DD

= 4.5 to 5.5V, Vss = 0V)

Item

SCK1 cycle time

t

KCY

SCK1

Input mode

Output mode

input mode

Output mode

SCK1 input mode

SCK1 output mode

SCK1 input mode

SCK1 output mode

SCK1 input mode

SCK1 output mode

1000

16000/fc

400

8000/fc ≠ 50

100

200

200

100

200

100

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

SCK1

SI1

SI1

SO1

t

KH

t

KL

t

SIK

t

KSI

t

KSO

SCK1 high and low level

widths

SI1 input setup time

(for SCK1

)

SI1 input hold time

(for SCK1

)

SCK1

SO1 delay time

Symbol

Pin

Conditions

Min.

Max.

Unit

Note) The load condition for the SCK1 output mode and SO1 output delay time is 50pF + 1TTL.

Fig. 5. Serial transfer CH1 timing

0.2V

DD

0.8V

DD

t

KL

t

KH

SO1

t

KCY

t

SIK

t

KSI

0.2V

DD

0.8V

DD

t

KSO

0.2V

DD

0.8V

DD

Output data

Input data

SI1

SCK1

≠ 20 ≠

CXP832P40A

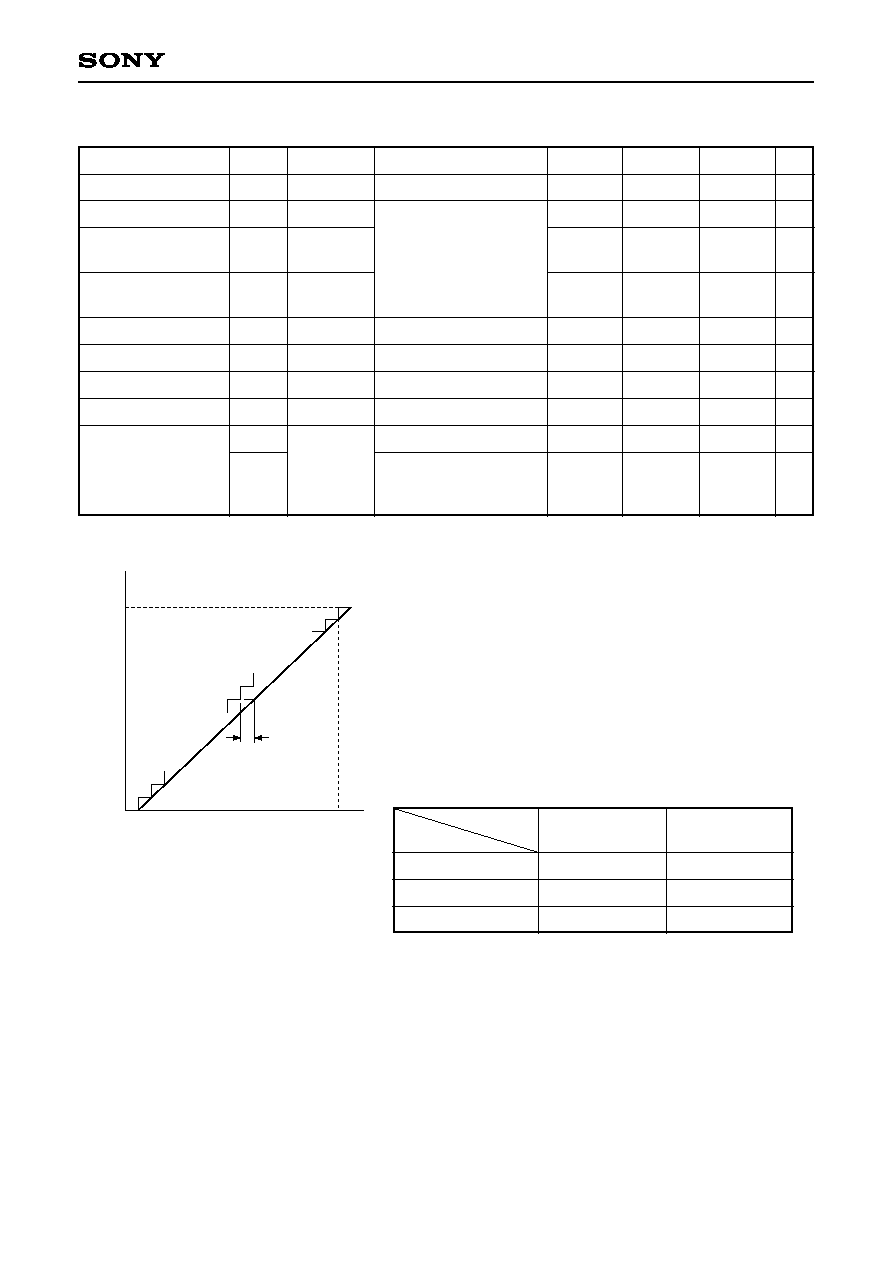

Conversion time

Sampling time

Reference input voltage

Analog input voltage

t

CONV

t

SAMP

V

REF

V

IAN

V

ZT

1

V

FT

2

I

REF

AV

REF

AN0 to AN7

Ta = 25įC

V

DD

= AV

REF

= 5.0V

V

SS

= AV

SS

= 0V

Operation mode

SLEEP mode

STOP mode

32kHz operation mode

Linearity error

Zero transition

voltage

Full-scale transition

voltage

Resolution

AV

REF

current

AV

REF

I

REFS

Ķs

Ķs

V

V

V

DD

AV

REF

1.0

mA

10

ĶA

0.6

160/f

ADC

3

12/f

ADC

3

V

DD

≠ 0.5

0

Item

Symbol

Pin

Conditions

Min.

Typ.

Max.

Unit

Bits

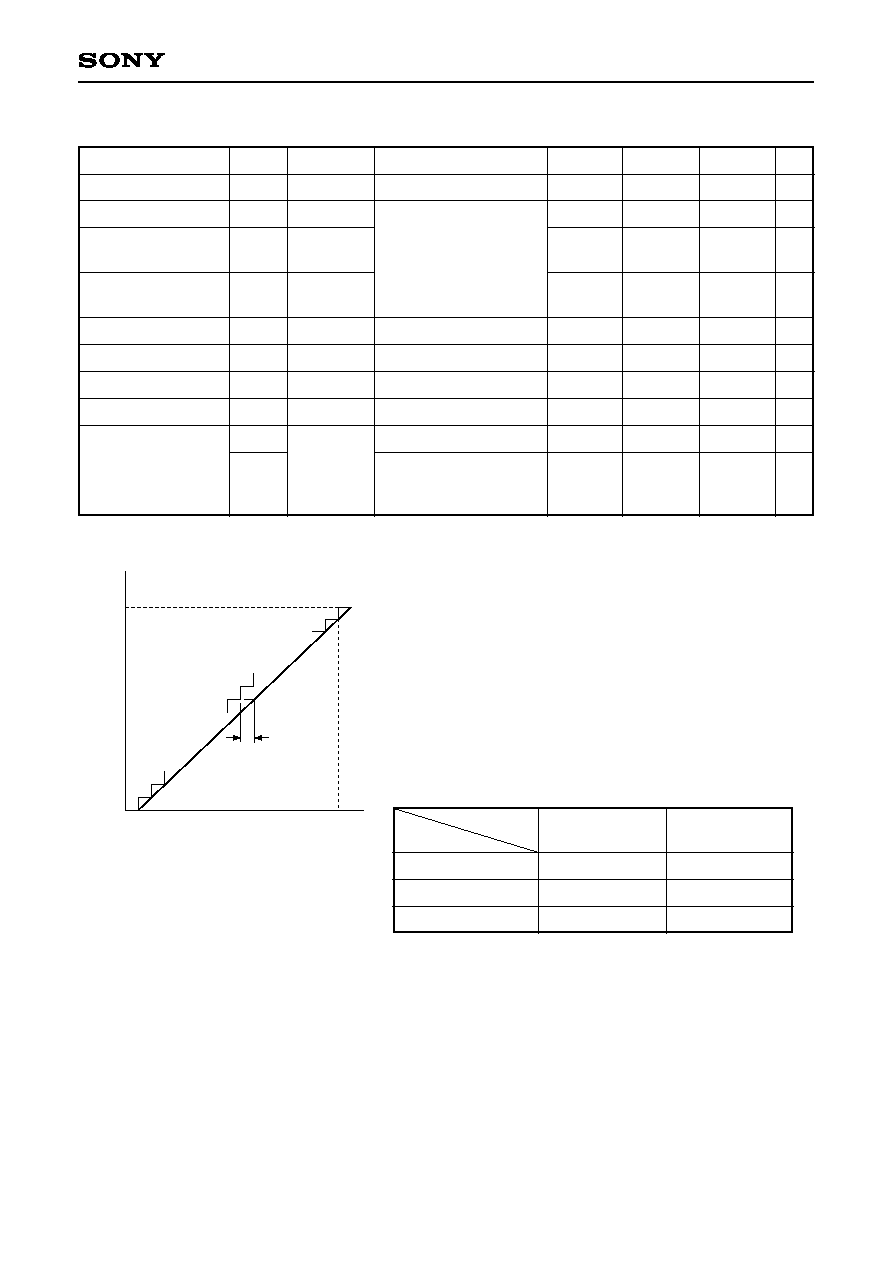

(3) A/D converter characteristics

(Ta = ≠10 to +75įC, V

DD

= 4.5 to 5.5V, Vss = AV

SS

= 0V)

8

Ī3

LSB

70

mV

5030

10

4970

≠10

4910

mV

Fig. 6. Definition of A/D converter terms

Analog input

Linearity error

V

FT

V

ZT

00

H

01

H

FE

H

FF

H

Digital conversion value

1) V

ZT

: Value at which the digital conversion value changes

from 00

H

to 01

H

and vice versa.

2) V

FT

: Value at which the digital conversion value changes

from FE

H

to FF

H

and vice versa.

3) f

ADC

indicates the below values due to the Bit 6 (CKS) of

A/D control register (address: 00F9

H

) and the Bit 7 (PCK1)

and Bit 6 (PCK0) of clock control register (address: 00FF

H

).

00 (

= f

EX

/2)

01 (

= f

EX

/4)

11 (

= f

EX

/16)

f

ADC

= f

C

/2

f

ADC

= f

C

/4

f

ADC

= f

C

/16

0 (

/2 selection)

CKS

PCK1, PCK0

f

ADC

= f

C

f

ADC

= f

C

/2

f

ADC

= f

C

/8

1 (

selection)

≠ 21 ≠

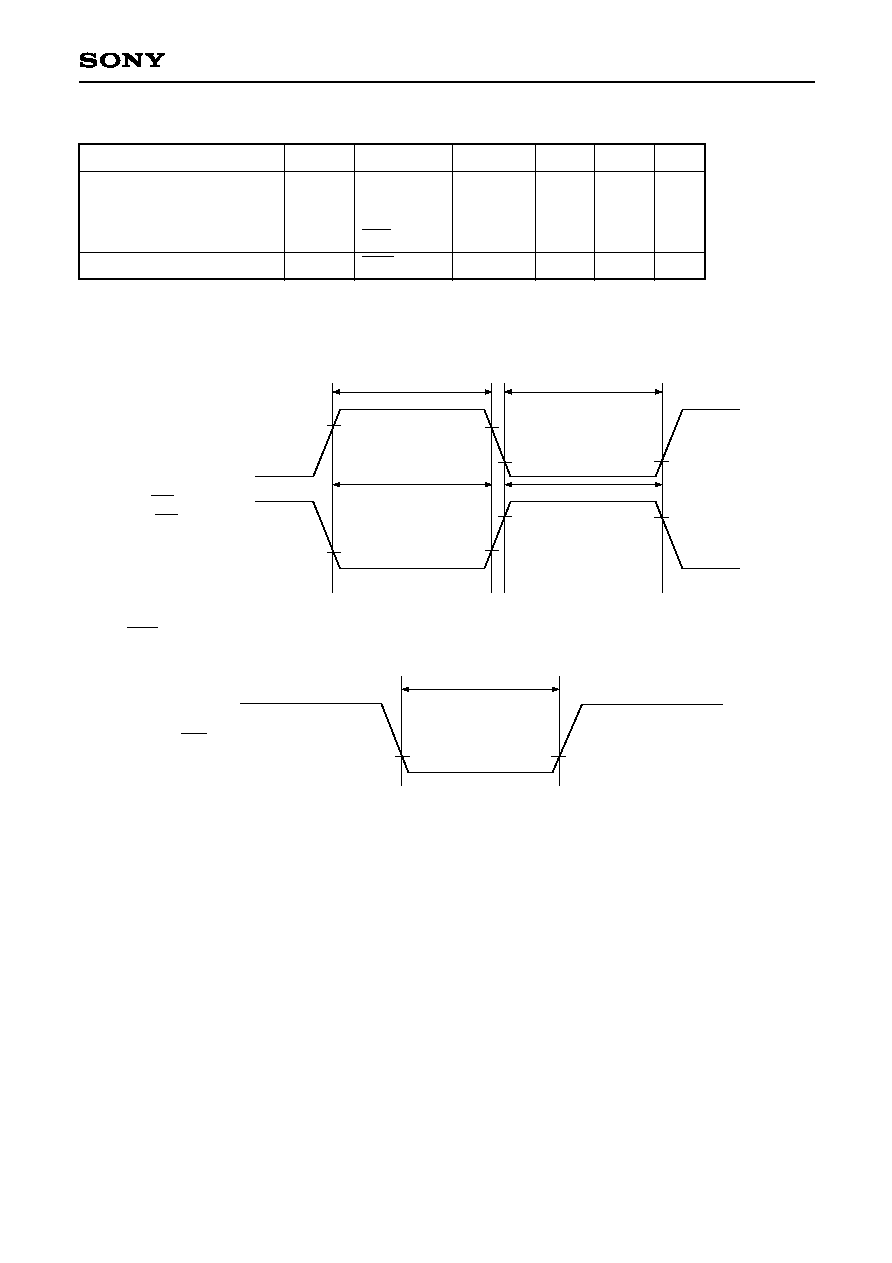

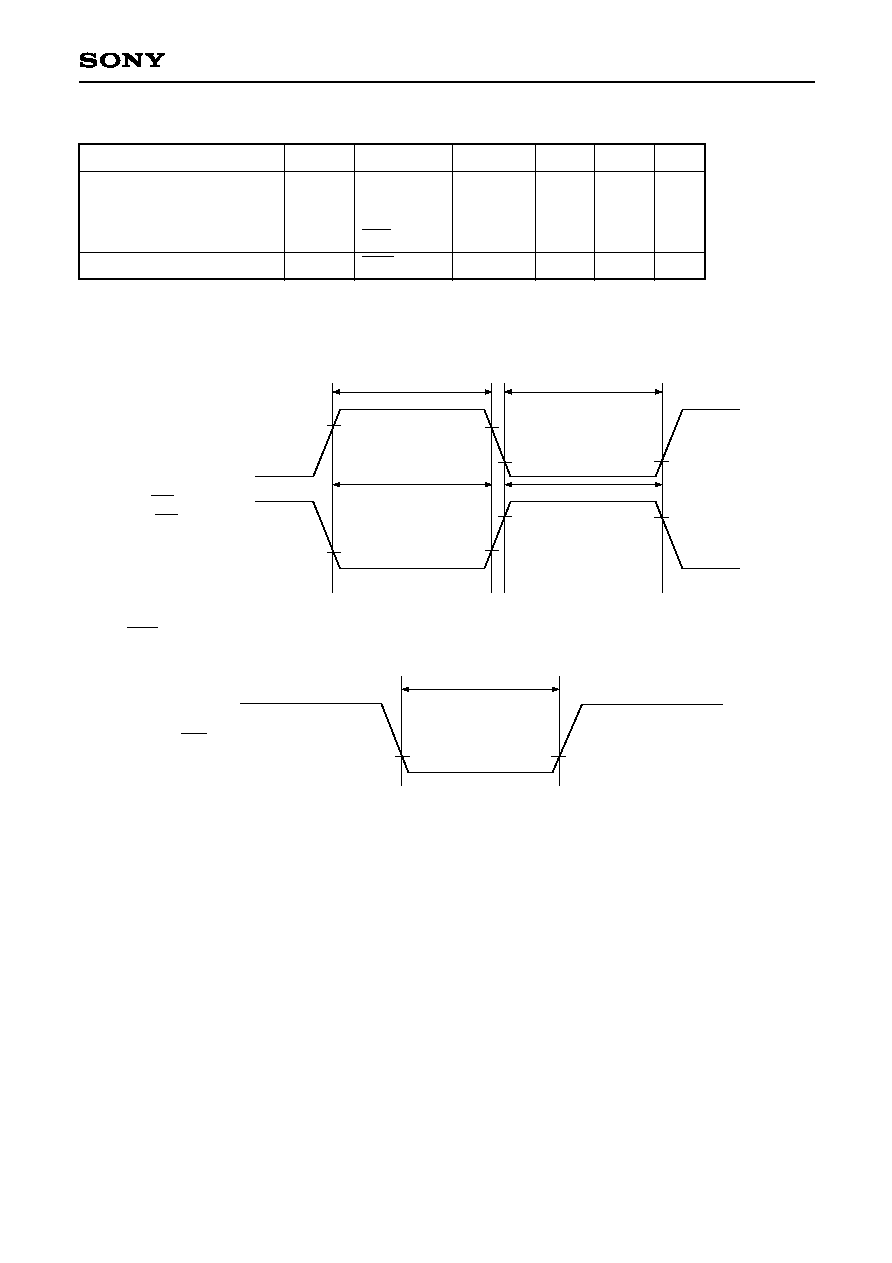

CXP832P40A

External interruption

high and low level widths

Reset input low level width

INT0

INT1

INT2

NMI/INT3

RST

1

32/fc

Ķs

Ķs

Item

Syymbol

Pin

Conditions

Min.

Max.

Unit

t

IH

t

IL

t

RSL

(4) Interruption, reset input

(Ta = ≠10 to +75įC, V

DD

= 4.5 to 5.5V, Vss = 0V)

0.2V

DD

0.8V

DD

t

IH

t

IL

INT0

INT1

INT2

NMI/INT3

(NMI specifies only

for the falling edge)

t

IL

t

IH

Fig. 7. Interruption input timing

t

RSL

0.2V

DD

RST

Fig. 8. RST input timing

≠ 22 ≠

CXP832P40A

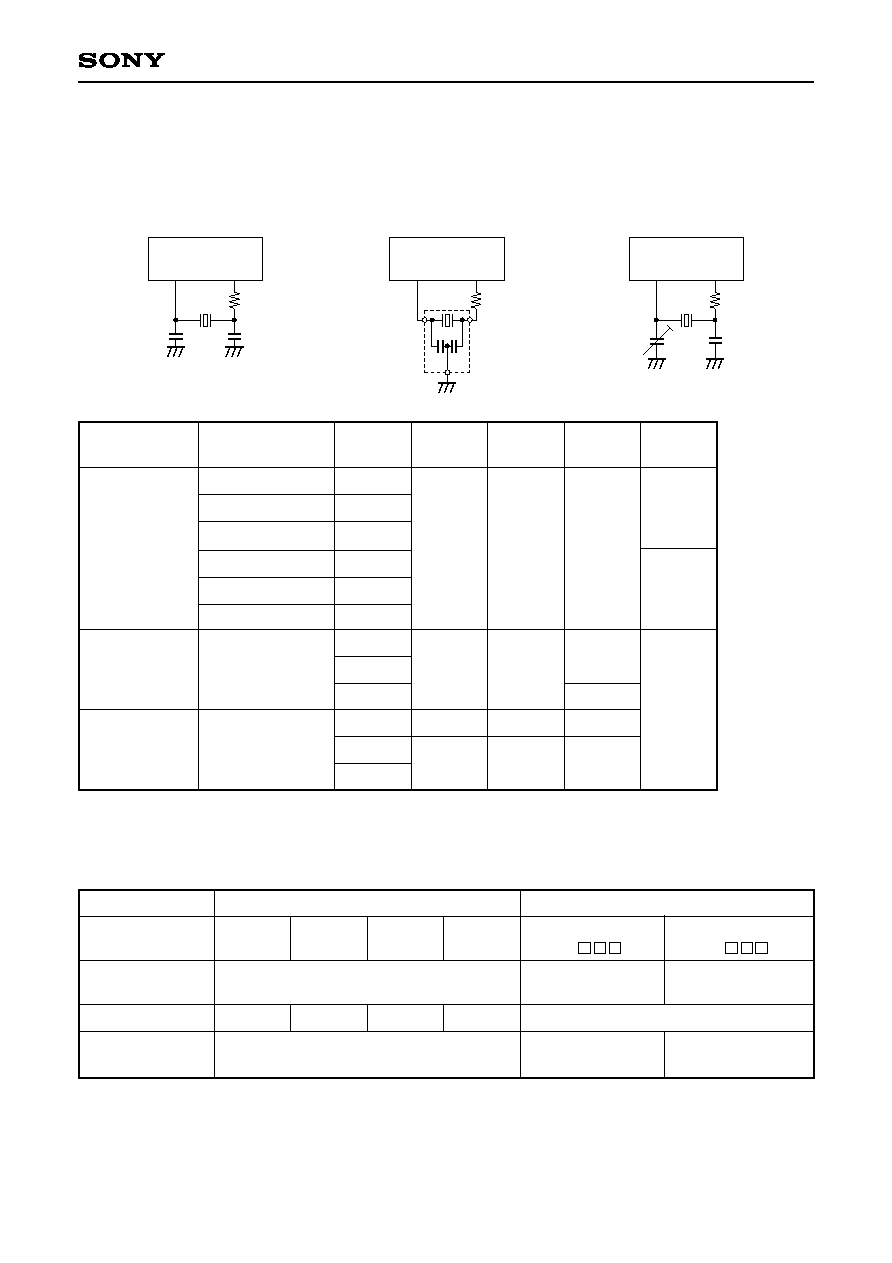

Appendix

Fig. 9. SPC700 series recommended oscillation circuit

C

1

EXTAL

XTAL

C

2

Rd

EXTAL

XTAL

Rd

(i) Main clock

500kHz sub clock

EXTAL

XTAL

C

1

C

2

Rd

XTAL

(ii) Main clock

500kHz sub clock

EXTAL

XTAL

C

1

C

2

Rd

TEX

TX

(iii) 32kHz sub clock

Manufacturer

MURATA MFG

CO., LTD.

RIVER

ELETEC

CO., LTD.

KINSEKI LTD.

Model

CSA4.19MG

CSA8.00MG

CST4.19MGW

CST8.00MTW

HC-49/U03

HC-49/U (-S)

fc (MHz)

4.19

8.00

10.00

4.19

8.00

10.00

4.19

8.00

10.00

4.19

8.00

10.00

18

18

30

15

22

30

15

22

560

470

0

2.2k

0

C

1

(pF)

C

2

(pF)

Rd (

)

Circuit

example

(i)

CSA10.0MT

(ii)

CST10.00MTW

(i)

Those marked with an asterisk (

) signify types with built-in ground capacitance (C

1

, C

2

).

Option item

Product name

Package

ROM capacitance

Reset pin

pull-up resistor

Selection Guide

CXP83120A CXP83124A CXP83232A CXP83240A

CXP832P40AQ-

1-

CXP832P40AR-

1-

Mask product

Incorporated PROM product

100-pin plastic QFP/LQFP

100-pin plastic QFP 100-pin plastic LQFP

20K bytes 24K bytes 32K bytes 40K bytes

PROM 40K bytes

Existent/Non-existent

Existent

Existent

≠ 23 ≠

CXP832P40A

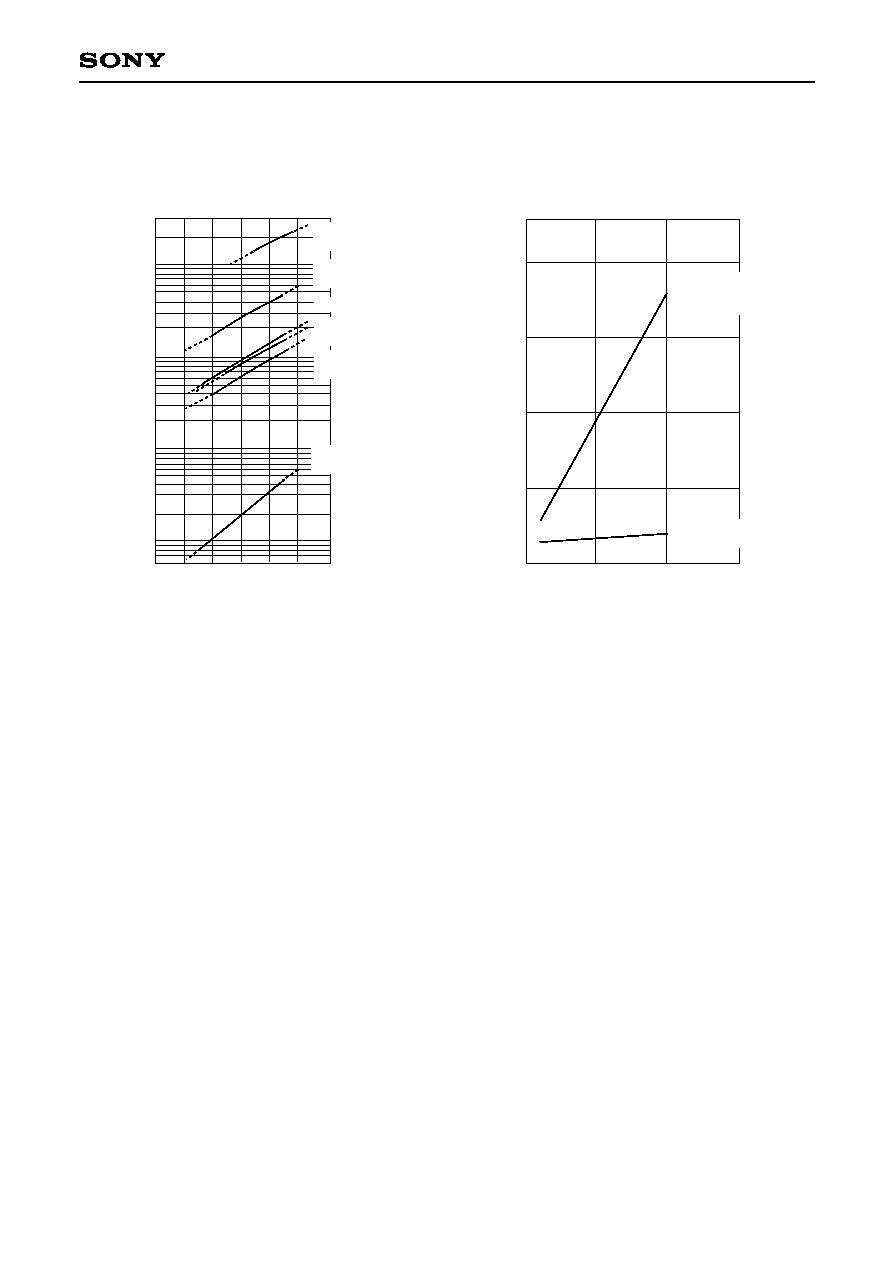

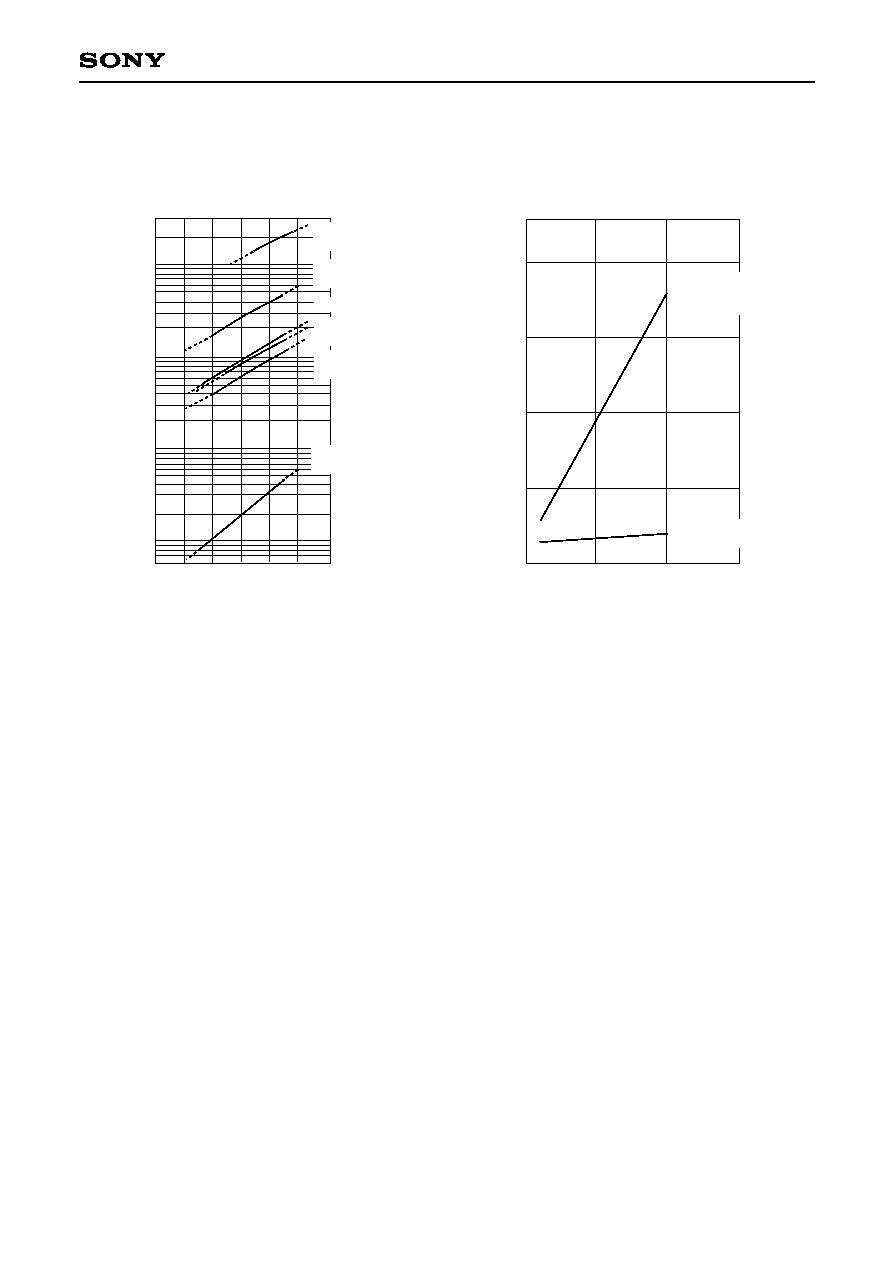

0

15

10

5

5

10

15

20

(100ĶA)

3

4

5

6

0.1

5.0

1.0

7

2

0.05

(50ĶA)

0.01

(10ĶA)

0.5

10.0

20.0

V

DD

≠ Supply voltage [V]

I

DD

vs. V

DD

(Ta = 25įC, typical)

fc ≠ System clock [MHz]

I

DD

≠

Supply current [mA]

I

DD

vs. fc

(V

DD

= 5V, Ta = 25įC, typical)

Main clock

1/2 frequency

dividing mode

Main clock

SLEEP mode

I

DD

≠

Supply current [mA]

fc = 500kHz sub clock

1/2 frequency dividing mode

32kHz

SLEEP mode

fc = 10MHz

main clock

1/2 frequency dividing mode

fc = 10MHz main clock

SLEEP mode

fc = 500kHz sub clock

SLEEP mode

32kHz mode (Instruction)

Characteristics Curves

≠ 24 ≠

CXP832P40A

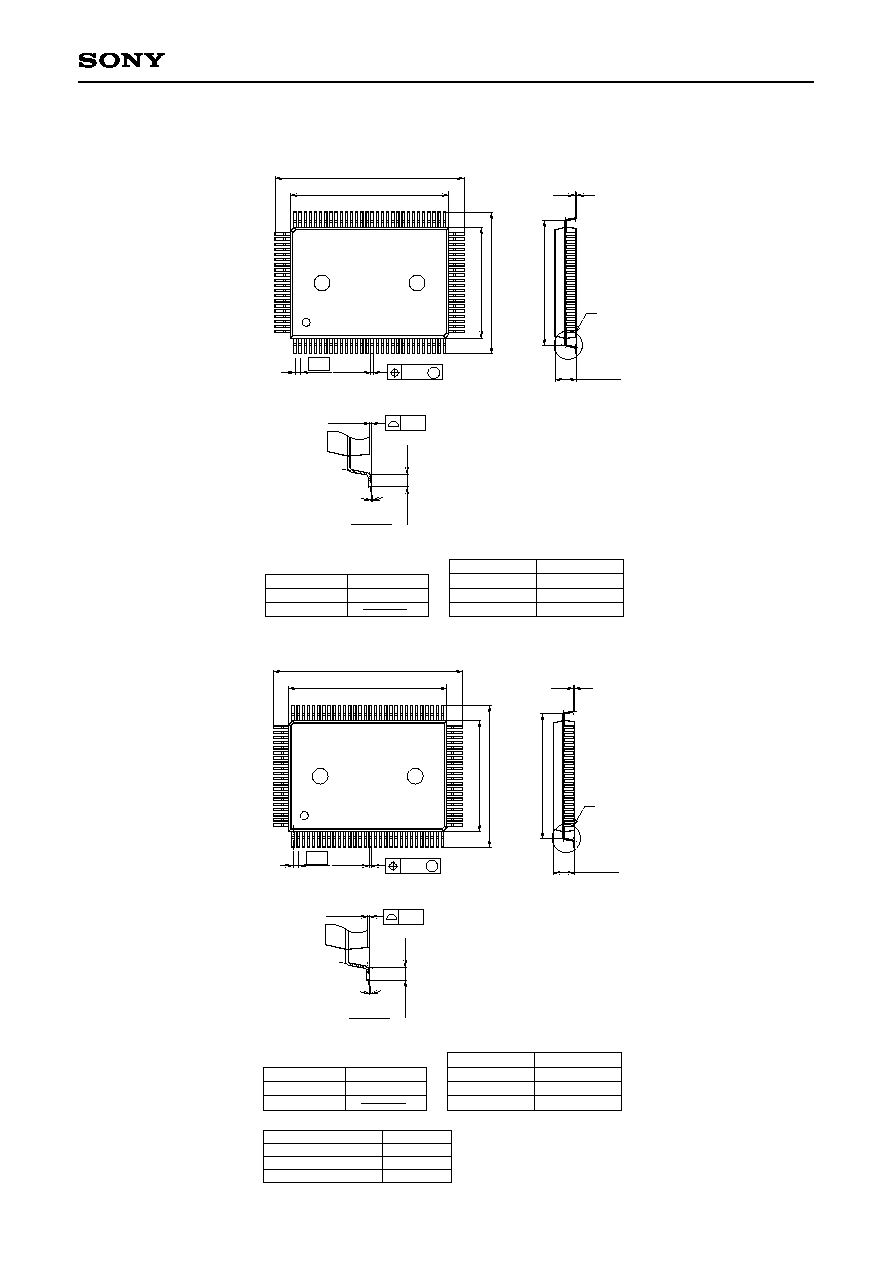

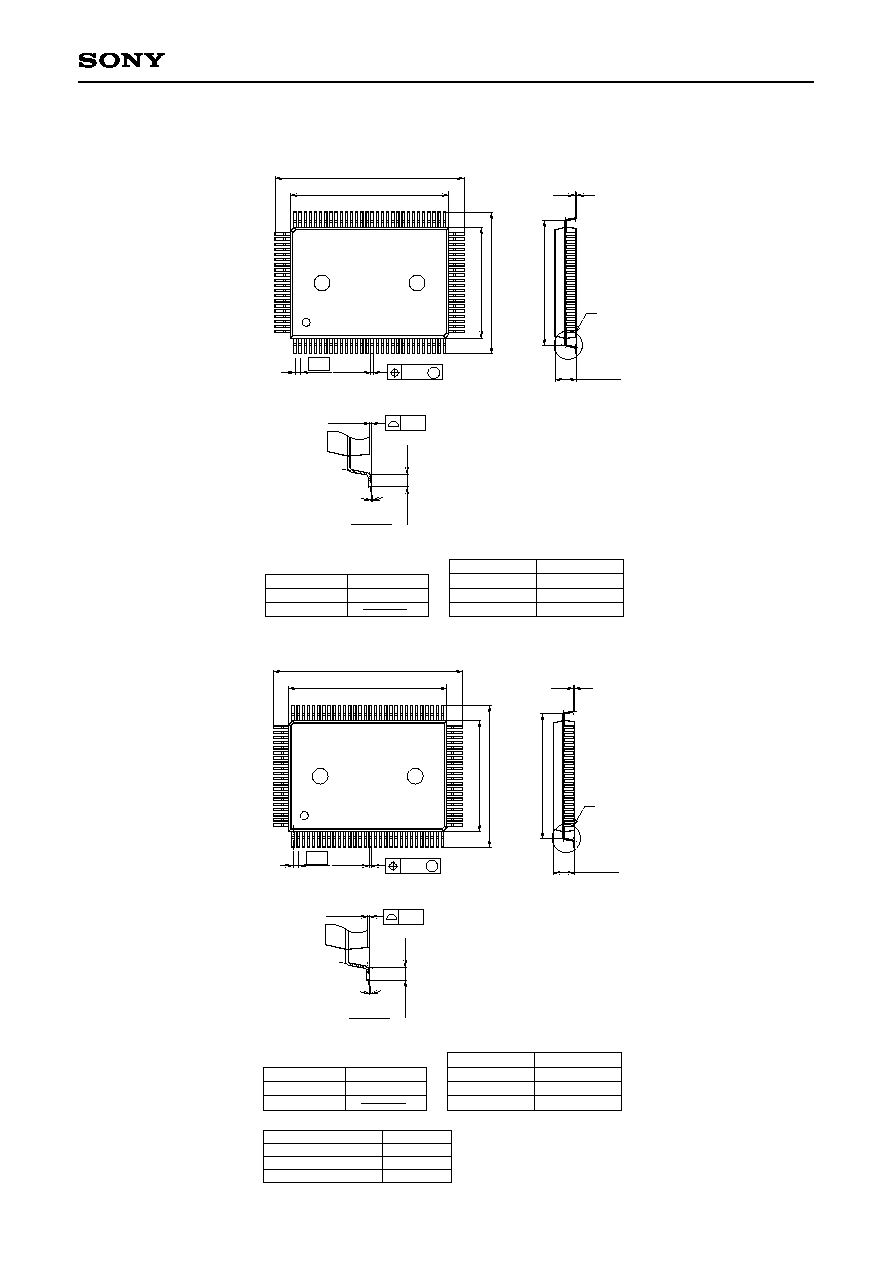

Package Outline Unit : mm

SONY CODE

EIAJ CODE

JEDEC CODE

PACKAGE MATERIAL

LEAD TREATMENT

LEAD MATERIAL

PACKAGE MASS

EPOXY RESIN

SOLDER PLATING

42/COPPER ALLOY

PACKAGE STRUCTURE

23.9

Ī

0.4

QFP-100P-L01

100PIN QFP (PLASTIC)

20.0 ≠ 0.1

+ 0.4

0.15 ≠ 0.05

+ 0.1

15.8

Ī

0.4

17.9

Ī

0.4

14.0

≠

0.1

+ 0.4

2.75 ≠ 0.15

+ 0.35

A

0.65

M

0.13

QFP100-P-1420

1.7g

1

100

81

80

51

50

31

30

0.3 ≠ 0.1

+ 0.15

DETAIL A

0į to 10į

0.8

Ī

0.2

(16.3)

0.15

0.1 ≠ 0.05

+ 0.2

SONY CODE

EIAJ CODE

JEDEC CODE

PACKAGE MATERIAL

LEAD TREATMENT

LEAD MATERIAL

PACKAGE MASS

EPOXY RESIN

SOLDER PLATING

42/COPPER ALLOY

PACKAGE STRUCTURE

23.9

Ī

0.4

QFP-100P-L01

100PIN QFP (PLASTIC)

20.0 ≠ 0.1

+ 0.4

0.15 ≠ 0.05

+ 0.1

15.8

Ī

0.4

17.9

Ī

0.4

14.0

≠

0.1

+ 0.4

2.75 ≠ 0.15

+ 0.35

A

0.65

M

0.13

QFP100-P-1420

1.7g

1

100

81

80

51

50

31

30

0.3 ≠ 0.1

+ 0.15

DETAIL A

0į to 10į

0.8

Ī

0.2

(16.3)

0.15

0.1 ≠ 0.05

+ 0.2

LEAD PLATING SPECIFICATIONS

ITEM

LEAD MATERIAL

42 ALLOY

SOLDER COMPOSITION

Sn-Bi Bi:1-4wt%

PLATING THICKNESS

5-18

Ķ

m

SPEC.

≠ 25 ≠

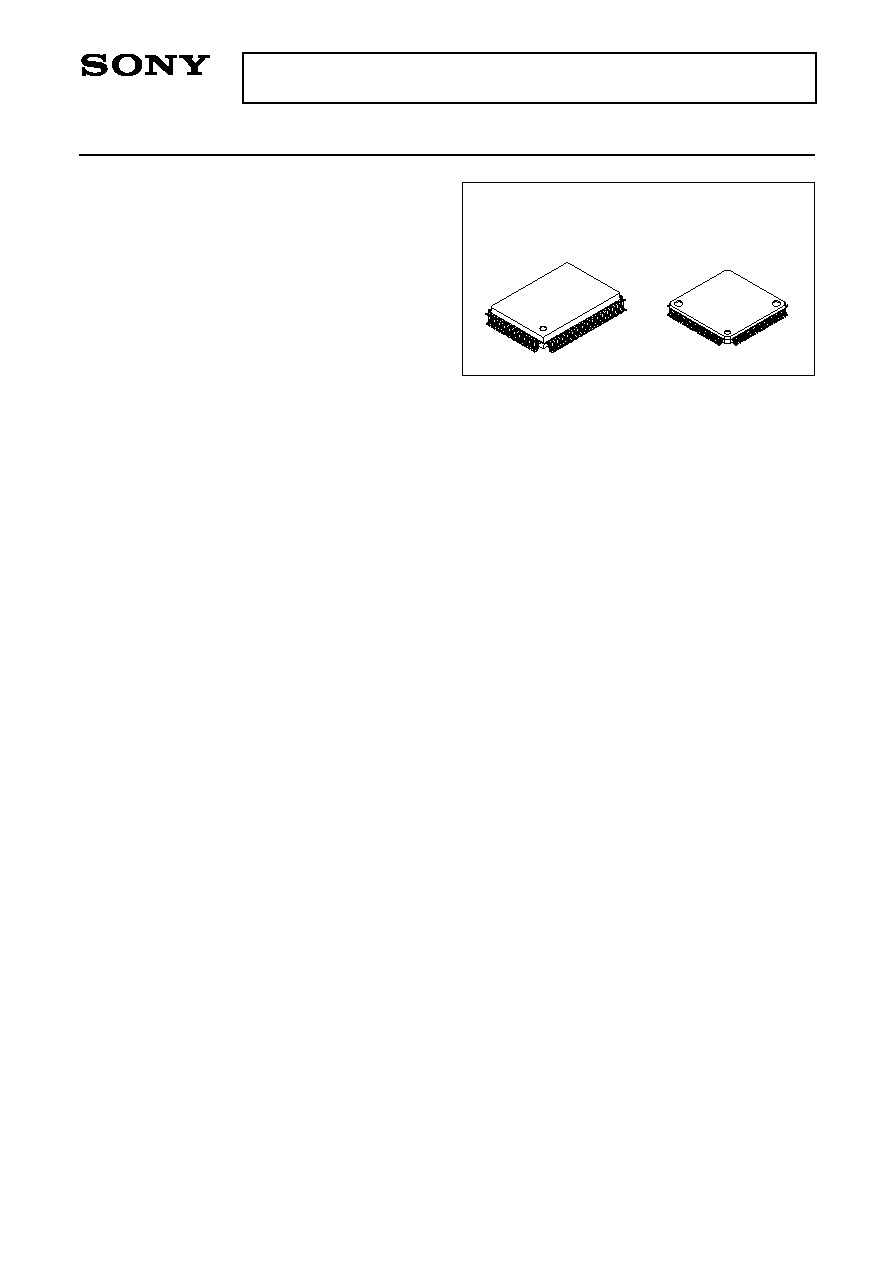

CXP832P40A

Package Outline Unit : mm

100PIN LQFP (PLASTIC)

25

26

51

50

75

76

1

100

SONY CODE

EIAJ CODE

JEDEC CODE

PACKAGE MATERIAL

LEAD TREATMENT

LEAD MATERIAL

PACKAGE MASS

EPOXY RESIN

SOLDER PLATING

42 / COPPER ALLOY

PACKAGE STRUCTURE

DETAIL A

LQFP-100P-L01

P-LQFP100-14x14-0.5

16.0

Ī

0.2

14.0

Ī

0.1

0.5

b

(0.22)

A

1.5 ≠ 0.1

+ 0.2

0.5

Ī

0.2

(15.0)

0į to 10į

0.1

Ī

0.1

0.5

Ī

0.2

0.1

NOTE: Dimension "

" does not include mold protrusion.

0.7g

0.13 M

b = 0.18 ≠ 0.03

( 0.18 )

(0.127)

+ 0.08

0.127 ≠ 0.02

+ 0.05

DETAIL B

B

100PIN LQFP (PLASTIC)

25

26

51

50

75

76

1

100

SONY CODE

EIAJ CODE

JEDEC CODE

PACKAGE MATERIAL

LEAD TREATMENT

LEAD MATERIAL

PACKAGE MASS

EPOXY RESIN

SOLDER PLATING

42 / COPPER ALLOY

PACKAGE STRUCTURE

DETAIL A

LQFP-100P-L01

P-LQFP100-14x14-0.5

16.0

Ī

0.2

14.0

Ī

0.1

0.5

b

(0.22)

A

1.5 ≠ 0.1

+ 0.2

0.5

Ī

0.2

(15.0)

0į to 10į

0.1

Ī

0.1

0.5

Ī

0.2

0.1

NOTE: Dimension "

" does not include mold protrusion.

0.7g

0.13 M

b = 0.18 ≠ 0.03

( 0.18 )

(0.127)

+ 0.08

0.127

≠

0.02

+ 0.05

DETAIL B

B

LEAD PLATING SPECIFICATIONS

ITEM

LEAD MATERIAL

42 ALLOY

SOLDER COMPOSITION

Sn-Bi Bi:1-4wt%

PLATING THICKNESS

5-18

Ķ

m

SPEC.

Sony Corporation