| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: CXP86541 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

≠ 1 ≠

E96Z15A86

CMOS 8-bit Single Chip Microcomputer

Description

The CXP86541/86549/86561 are the CMOS 8-bit

microcomputer integrating on a single chip an A/D

converter, serial interface, timer/counter, time-base

timer, on-screen display function, I

2

C bus interface,

PWM output, remote control reception circuit,

HSYNC counter, watchdog timer, 32kHz timer/counter

besides the basic configurations of 8-bit CPU, ROM,

RAM, I/O ports.

The CXP86541/86549/86561 also provide a sleep

function that enables to lower the power consumption.

Features

∑ A wide instruction set (213 instructions) which

covers various types of data

≠ 16-bit operation/multiplication and division/

Boolean bit operation instructions

∑ Minimum instruction cycle 250ns at 16MHz operation (4.5 to 5.5V)

122µs at 32kHz operation (2.7 to 5.5V)

∑ Incorporated ROM

40K bytes (CXP86541)

48K bytes (CXP86549)

60K bytes (CXP86561)

∑ Incorporated RAM

1536 bytes

(Excludes VRAM for on-screen display and sprite RAM)

∑ Peripheral functions

≠ A/D converter

8-bit 6-channel successive approximation method

(Conversion time of 3.25µs at 16 MHz)

≠ Serial interface

8-bit clock sync type, 1 channel

≠ Timer

8-bit timer

8-bit timer/counter

19-bit time-base timer

32kHz timer/counter

≠ On-screen display (OSD) function

12

◊

16 dots,

512 character types,

15 character colors, 2 lines

◊

24 characters,

frame background 8 colors/ half blanking,

background on full screen 15 colors/ half blanking

edging/ shadowing/ rounding for every line,

background with shadow for every character,

double scanning,

sprite OSD,

12

◊

16 dots, 1 screen, 8 colors for every dot

≠ I

2

C bus interface

≠ PWM output

8 bits, 6 channels

14 bits, 1 channel

≠ Remote control reception circuit

8-bit pulse measurement counter, 6-stage FIFO

≠ HSYNC counter

2 channels

≠ Watchdog timer

∑ Interruption

13 factors, 13 vectors, multi-interruption possible

∑ Standby mode

Sleep

∑ Package

52-pin plastic SDIP

∑ Piggyback/evaluator

CXP86490 64-pin ceramic PSDIP (Supports custom font)

Perchase of Sony's I

2

C components conveys a licence under the Philips I

2

C Patent Rights to use these components

in an I

2

C system, provided that the system conforms to the I

2

C Standard Specifications as defined by Philips.

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

Structure

Silicon gate CMOS IC

CXP86541/86549/86561

52 pin SDIP (Plastic)

≠ 2 ≠

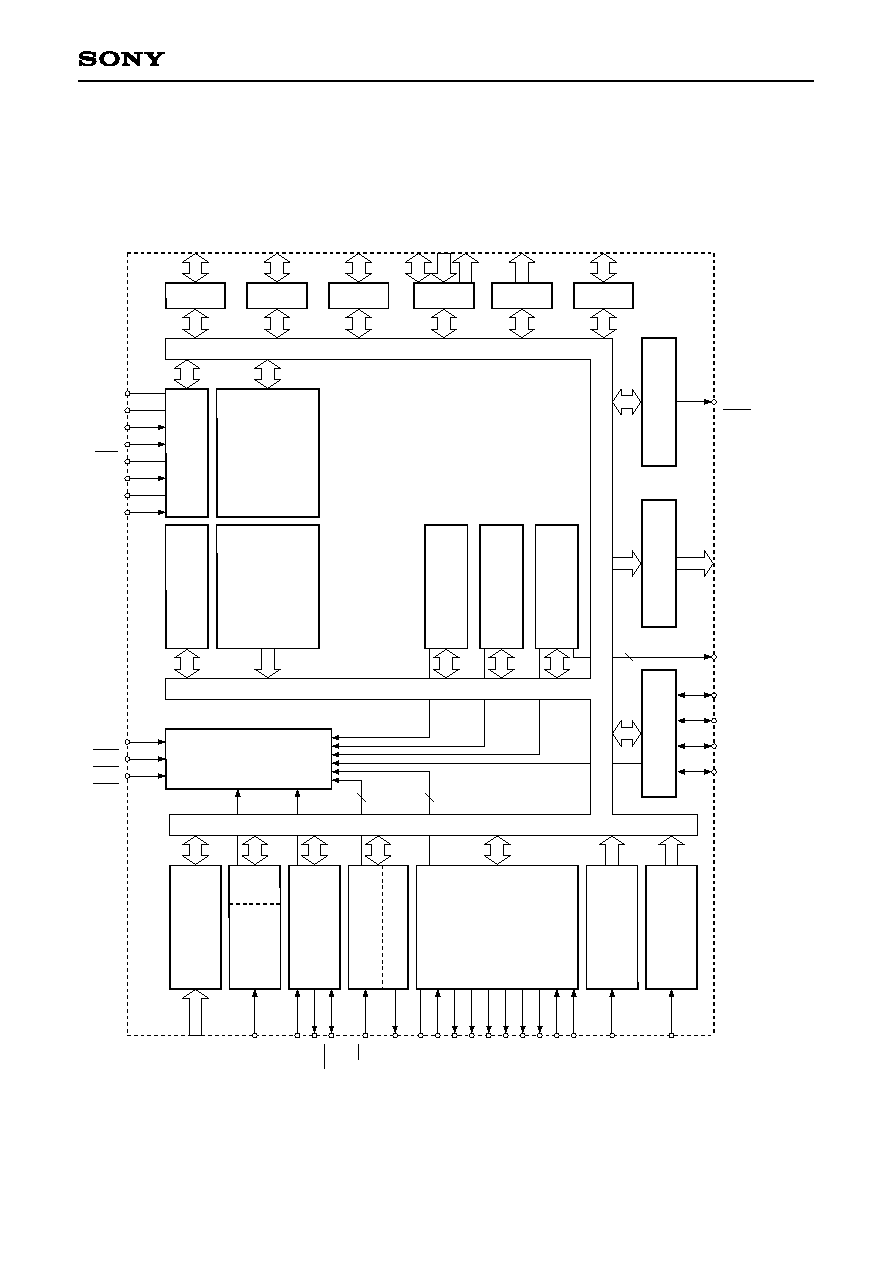

CXP86541/86549/86561

A

/

D

C

O

N

V

E

R

T

E

R

6

C

H

F

I

F

O

R

E

M

O

C

O

N

S

E

R

I

A

L

I

N

T

E

R

F

A

C

E

U

N

I

T

8

B

I

T

T

I

M

E

R

1

8

B

I

T

T

I

M

E

R

/

C

O

U

N

T

E

R

0

O

N

S

C

R

E

E

N

D

I

S

P

L

A

Y

H

S

Y

N

C

C

O

U

N

T

E

R

0

H

S

Y

N

C

C

O

U

N

T

E

R

1

I

2

C

B

U

S

I

N

T

E

R

F

A

C

E

U

N

I

T

8

B

I

T

P

W

M

1

4

B

I

T

P

W

M

P

R

E

S

C

A

L

E

R

/

T

I

M

E

B

A

S

E

T

I

M

E

R

W

A

T

C

H

D

O

G

T

I

M

E

R

3

2

k

H

z

T

I

M

E

R

/

C

O

U

N

T

E

R

R

O

M

1

2

K

/

1

6

K

/

2

4

K

/

3

2

K

/

4

0

K

/

4

8

K

/

6

0

K

B

Y

T

E

S

R

A

M

3

5

2

/

7

0

4

/

1

5

3

6

B

Y

T

E

S

S

P

C

7

0

0

C

P

U

C

O

R

E

C

L

O

C

K

G

E

N

E

R

A

T

O

R

/

S

Y

S

T

E

M

C

O

N

T

R

O

L

IN

TE

RR

UP

T C

ON

TR

OL

LE

R

PW

M

PO

RT

G

P

G

7

1

PO

RT

E

P

E

4

t

o

P

E

6

3

P

E

2

t

o

P

E

3

2

P

E

0

t

o

P

E

1

2

PO

RT

D

P

D

0

t

o

P

D

7

8

PO

RT

B

P

B

0

t

o

P

B

7

8

PO

RT

A

P

A

0

t

o

P

A

7

8

PW

M0

to

P

WM

5

AD

J

SC

L1

SC

L0

SD

A1

SD

A0

H

S

1

H

S

0

V

S

Y

N

C

H

S

Y

N

C

Y

M

Y

S

I

B

G

R

E

X

L

C

X

L

C

T

O

E

C

S

C

K

S

O

S

I

R

M

C

A

N

0

t

o

A

N

5

6

2

2

2

IN

T0

IN

T1

IN

T2

TE

X

TX

EX

TA

L

XT

AL

RS

T

MP

V

DD

V

SS

6

PO

RT

F

P

F

0

t

o

P

F

7

8

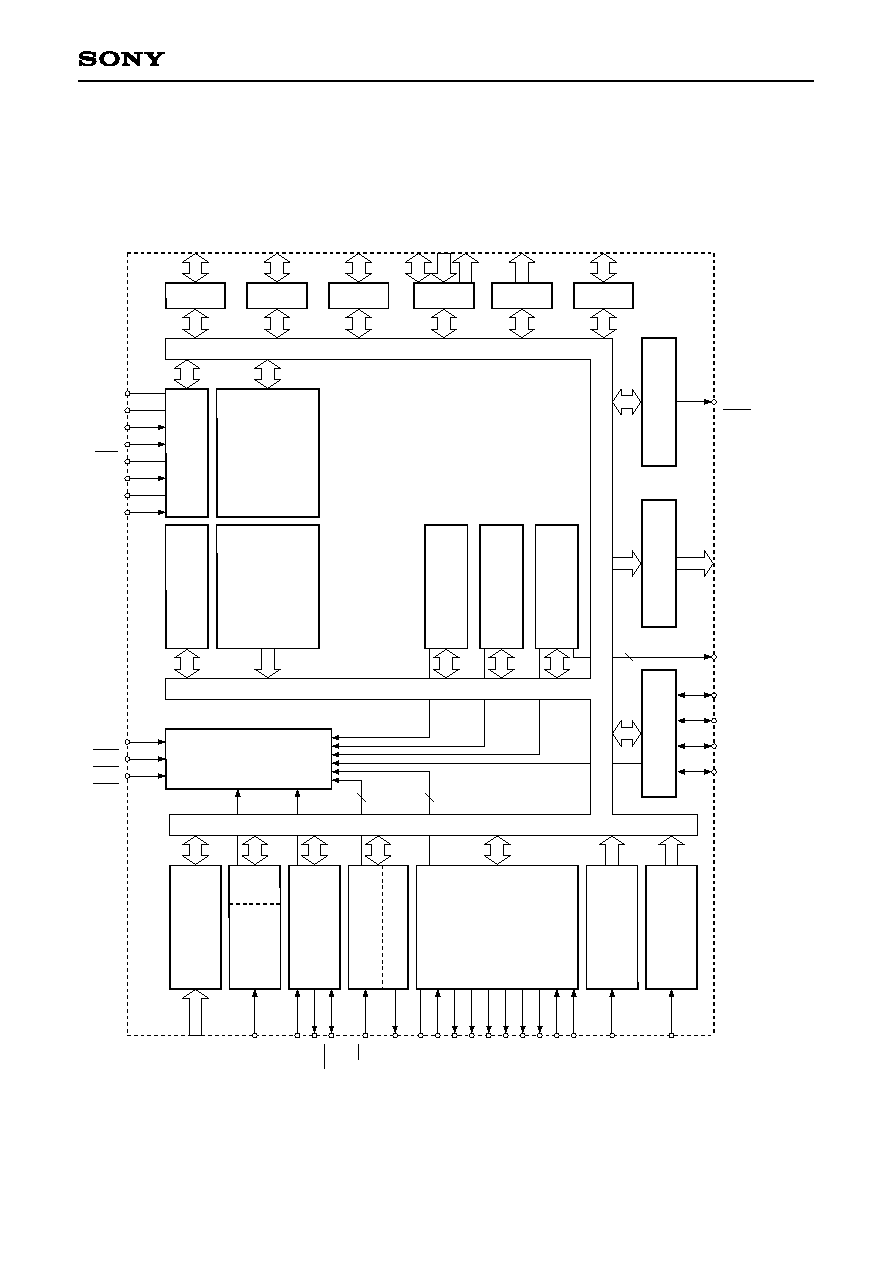

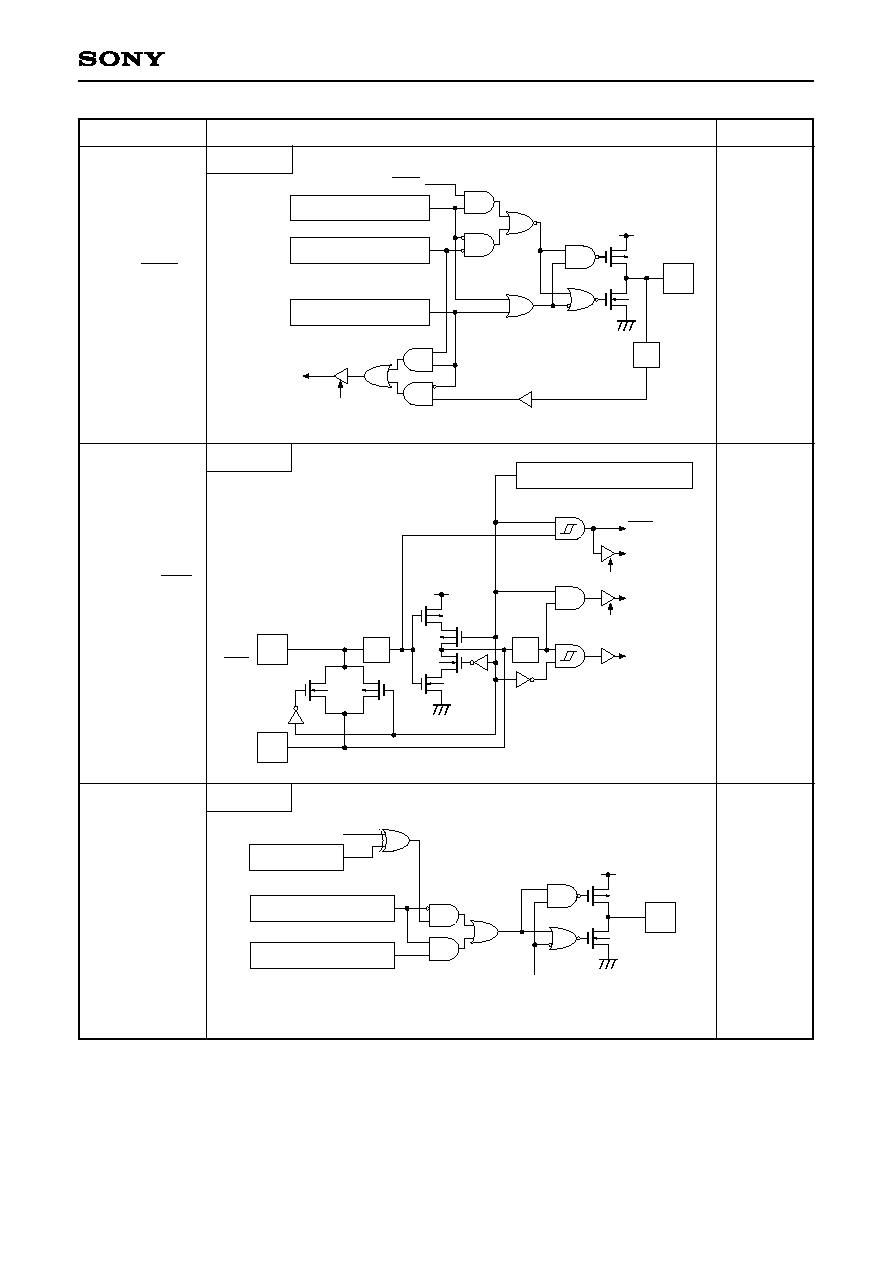

Block Diagram

≠ 3 ≠

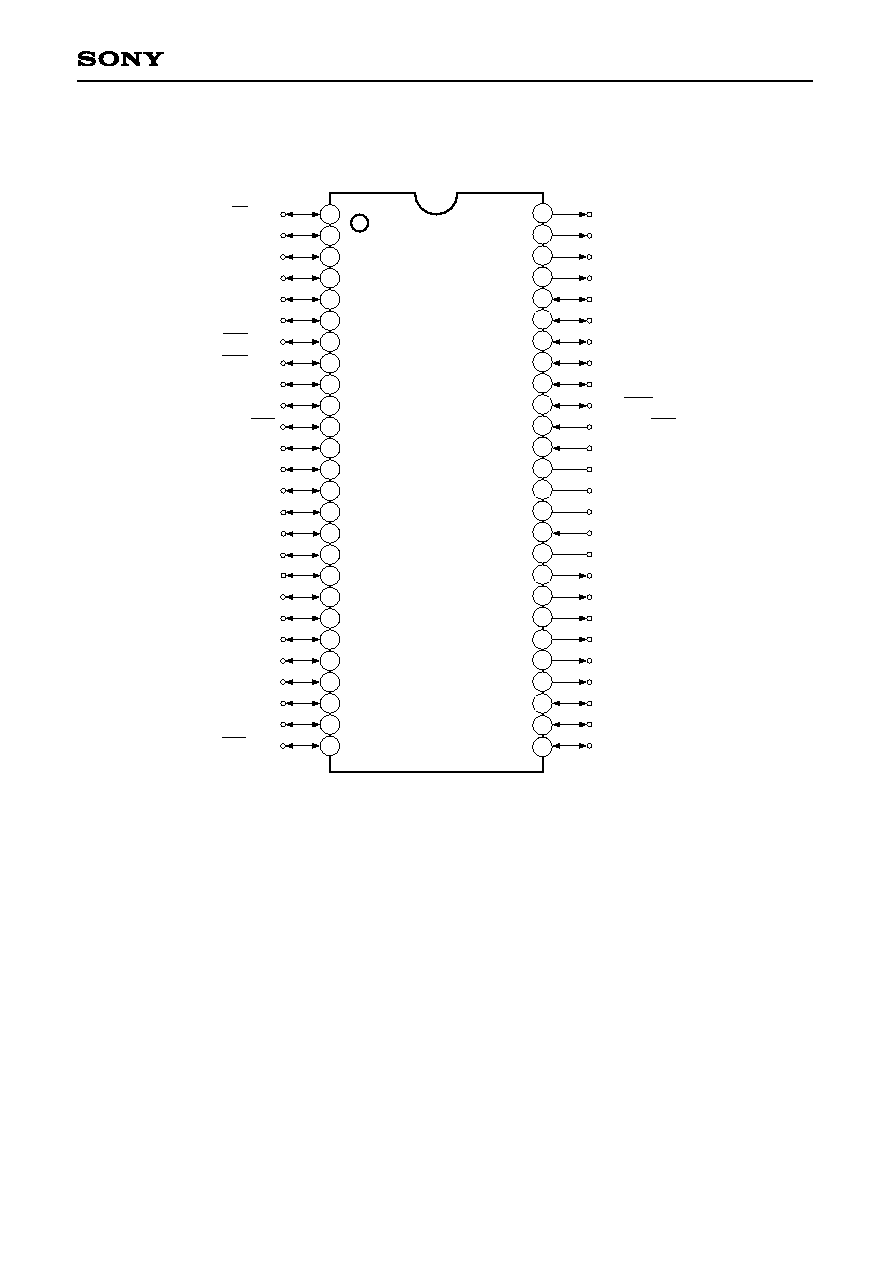

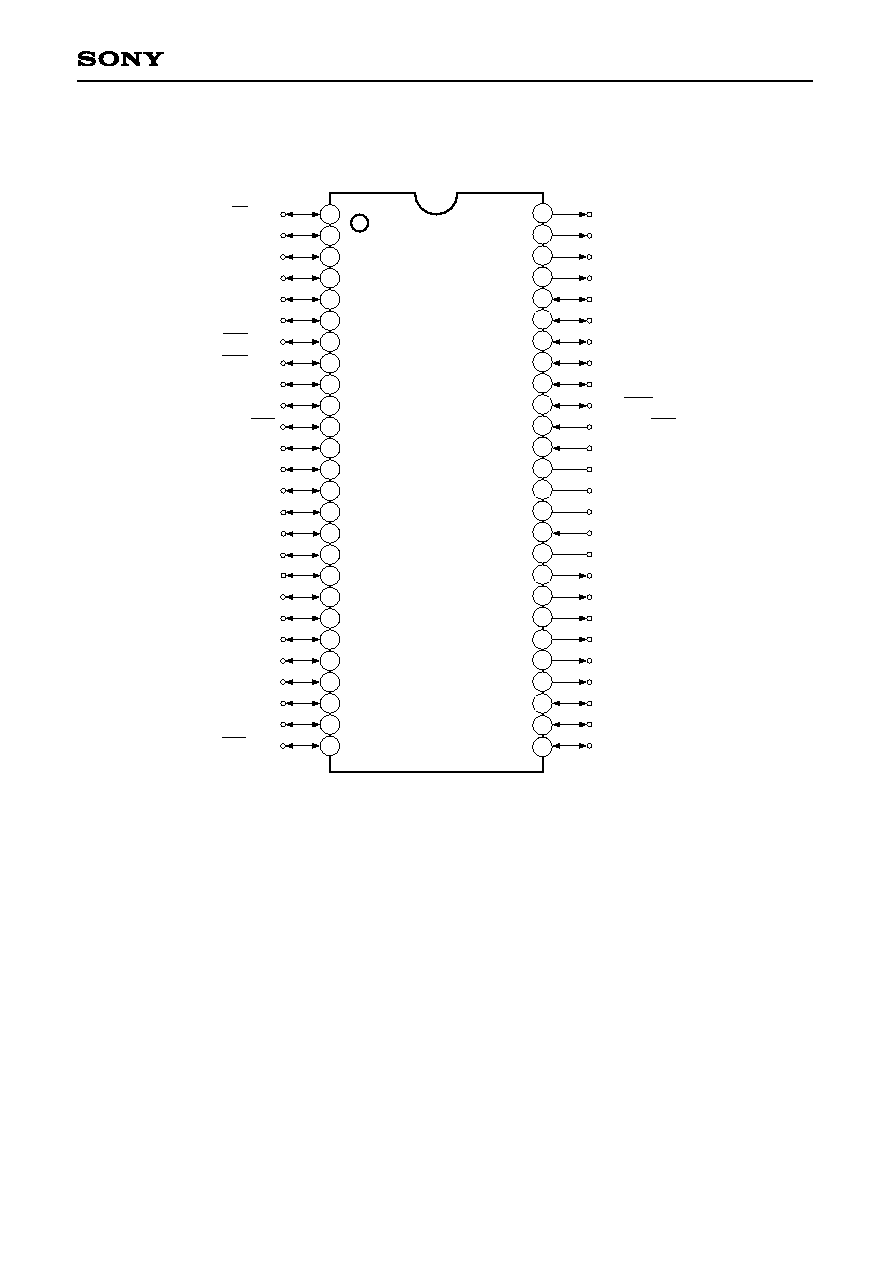

CXP86541/86549/86561

40

39

38

37

36

35

34

33

41

42

43

44

45

46

47

48

49

50

51

52

31

32

27

28

29

30

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

1

HS0/PD4

EC/PD7

RMC/PD6

HS1/PD5

SI/PD3

SO/PD2

SCK/PD1

INT2/PD0

HSYNC/PA7

VSYNC/PA6

RST

V

SS

PA0/AN0

XTAL

EXTAL

PA5/AN5

PA4/AN4

PA3/AN3

PA2/AN2

PA1/AN1

PB7

PB6

PB5

PB4

PB3

INT1/PG7

V

SS

V

DD

NC

EXLC

XLC

PE4/YM

PE5/YS

PE6/I

B

G

R

PB0

PB1

PB2

PF0/PWM0

PF1/PWM1

PF2/PWM2

PF3/PWM3

PF4/SCL0

PF5/SCL1/PWM4

PF6/SDA0

PF7/SDA1/PWM5

PE0/TO/ADJ

PE1/PWM

PE2/TEX/INT0

PE3/TX

Pin Assignment (Top View)

Note)

1. NC (Pin 38) is left open.

2. Vss (Pins 12 and 40) are both connected to GND.

≠ 4 ≠

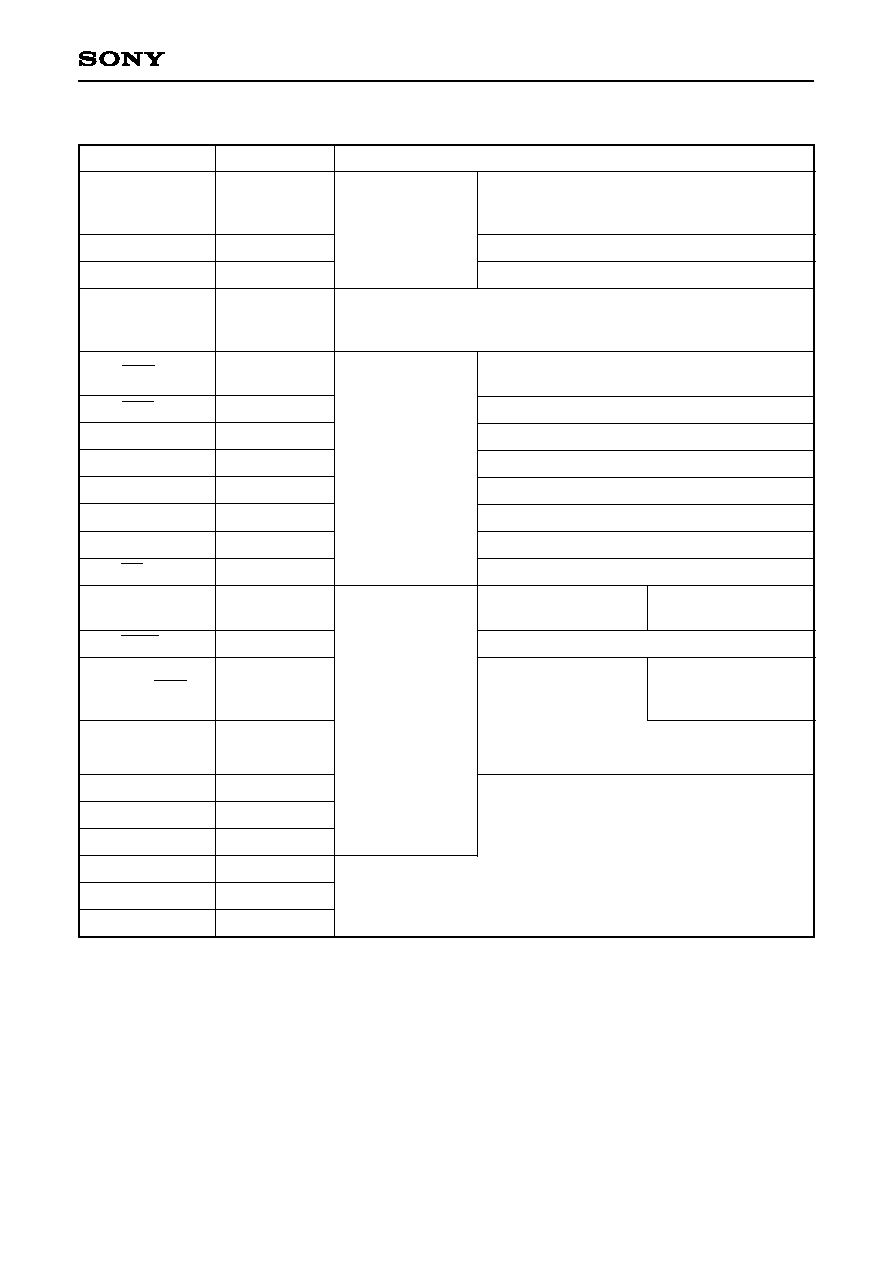

CXP86541/86549/86561

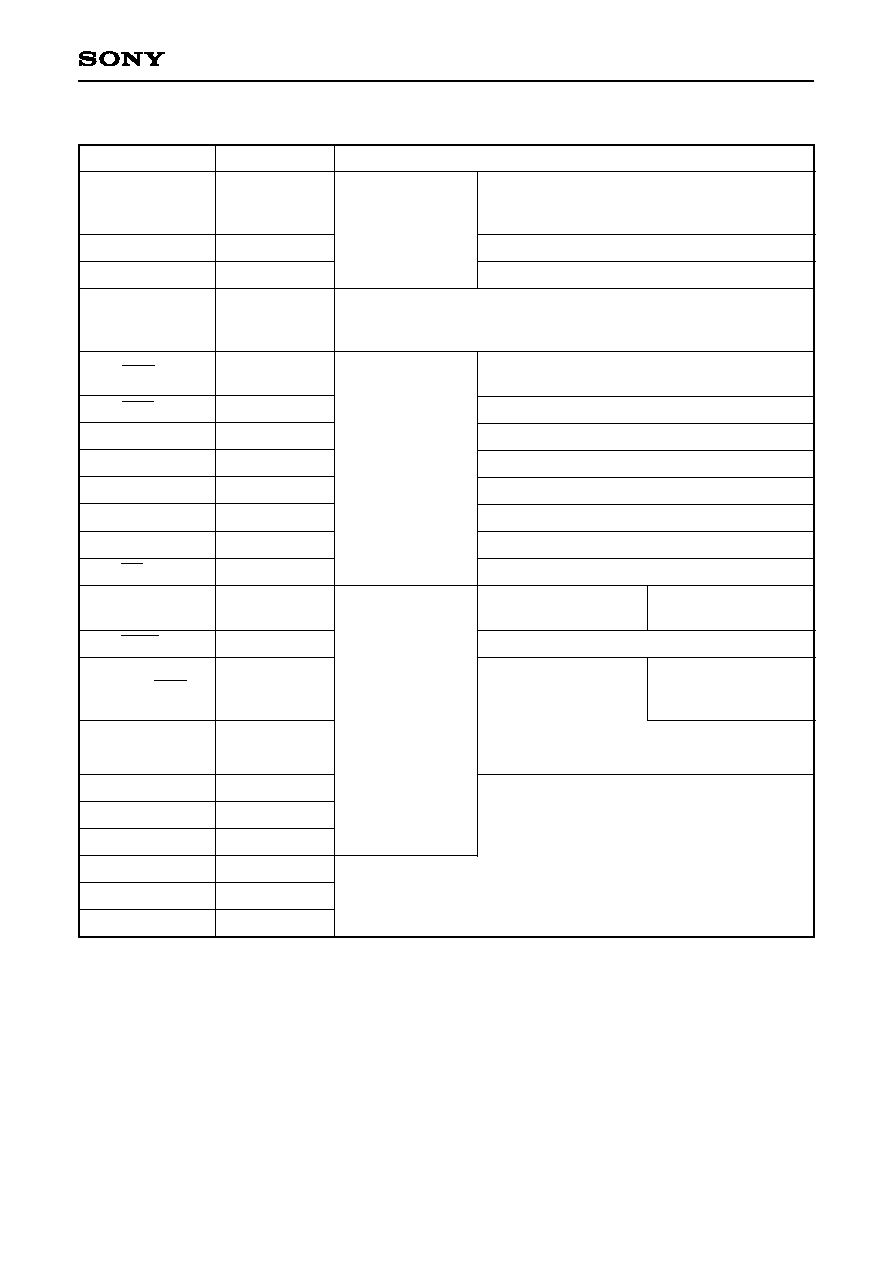

(Port A)

8-bit I/O port.

I/O can be set in a

unit of single bits.

(8 pins)

(Port B)

8-bit I/O port. I/O can be set in a unit of single bits.

(8 pins)

(Port D)

8-bit I/O port. I/O

can be set in a

unit of single bits.

Can drive 12mA

synk current.

(8 pins)

(Port E)

Bits 0 and 1 are I/O

port; I/O can be set

in a unit of single bits.

Bits 2 and 3 are for

input. Bits 4, 5 and

6 are for output.

(7 pins)

Pin Description

Symbol

PA0/AN0

to

PA5/AN5

PA6/VSYNC

PA7/HSYNC

PB0 to PB7

PD0/INT2

PD1/SCK

PD2/SO

PD3/SI

PD4/HS0

PD5/HS1

PD6/RMC

PD7/EC

PE0/TO/ADJ

PE1/PWM

PE2/TEX/INT0

PE3/TX

PE4/YM

PE5/YS

PE6/I

B

G

R

I/O/

Analog input

I/O/Input

I/O/Input

I/O

I/O/Input

I/O/I/O

I/O/Output

I/O/Input

I/O/Input

I/O/Input

I/O/Input

I/O/Input

I/O/Output/

Output

I/O/Output

Input/Input/

Input

Input/Output

Output/Output

Output/Output

Output/Output

Output

Output

Output

I/O

Description

Analog inputs to A/D converter.

(6 pins)

OSD display vertical sync signal input.

OSD display horizontal sync signal input.

External interruption request input. Active at the

falling edge.

Serial clock I/O.

Serial data output.

Serial data input.

HSYNC counter (CH0) input.

HSYNC counter (CH1) input.

Remote control reception circuit input.

External event input for timer/counter.

Rectangular wave output

for 8-bit timer/counter.

14-bit PWM output.

Connects a crystal for

32kHz timer/counter

clock oscillation. When

used as an event

counter, input to TEX pin and leave TX pin open.

32kHz oscillation

frequency dividing output.

External interruption

request input. Active at

the falling edge.

OSD display 6-bit output.

(6 pins)

≠ 5 ≠

CXP86541/86549/86561

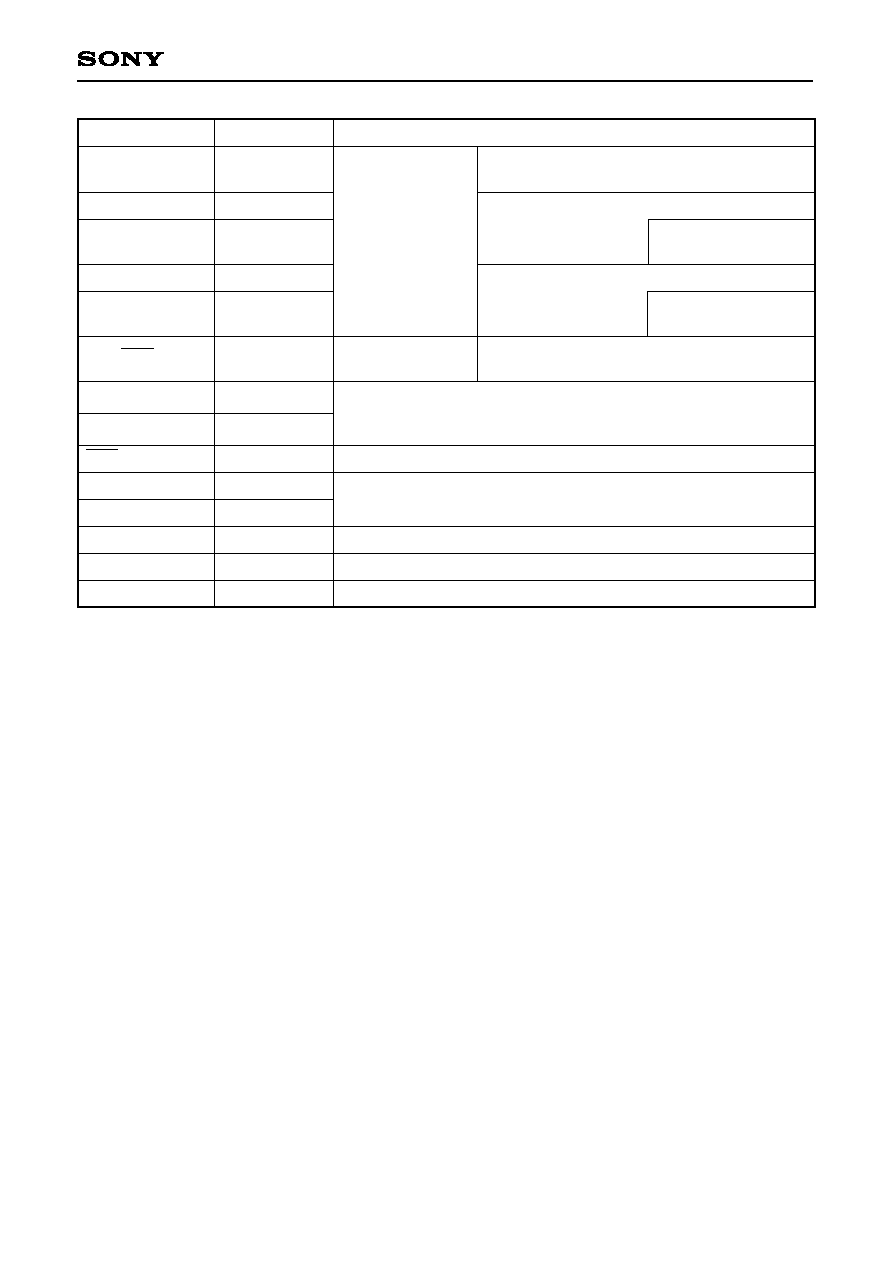

(Port F)

8-bit output port

and large current

(12mA) N-channel

open drain output.

Lower 4 bits are

midium drive voltage

(12V); upper 4 bits

are 5V drive.

(8 pins)

(Port G)

1-bit I/O port.

Connects a crystal for system clock oscillation. When a clock is

supplied externally, input it to EXTAL pin and input a reversed phase

clock to XTAL pin.

System reset; active at Low level.

OSD display clock oscillation I/O. Oscillation frequency is determined

by the external L and C.

No connected.

Positive power supply.

GND. Connect two Vss pins to GND.

8-bit PWM output.

(4 pins)

I

2

C bus interface transfer clock I/O.

(2 pins)

I

2

C bus interface transfer data I/O.

(2 pins)

Symbol

PF0/PWM0 to

PF3/PWM3

PF4/SCL0

PF5/SCL1/

PWM4

PF6/SDA0

PF7/SDA1/

PWM5

PG7/INT1

EXTAL

XTAL

RST

EXLC

XLC

NC

V

DD

Vss

Output/Output

Output/I/O

Output/I/O/

Output

Output/I/O

Output/I/O/

Output

I/O/Input

Input

Output

Input

Input

Output

I/O

Description

8-bit PWM output.

8-bit PWM output.

External interruption request input.

Active at the falling edge.

≠ 6 ≠

CXP86541/86549/86561

Port A data

Port A direction

IP

RD (Port A)

Data bus

"0" when reset

Port A function selection

"0" when reset

A/D converter

Input multiplexer

Input

protection

circuit

Port A data

Port A direction

IP

Input polarity

RD (Port A)

Data bus

HSYNC, VSYNC

"0" when reset

"0" when reset

Schmitt input

Ports B, G data

Ports B, G direction

IP

RD (Ports B, G)

Data bus

INT1

"0" when reset

Schmitt input

for PB0, PB1, PB2,

PG7

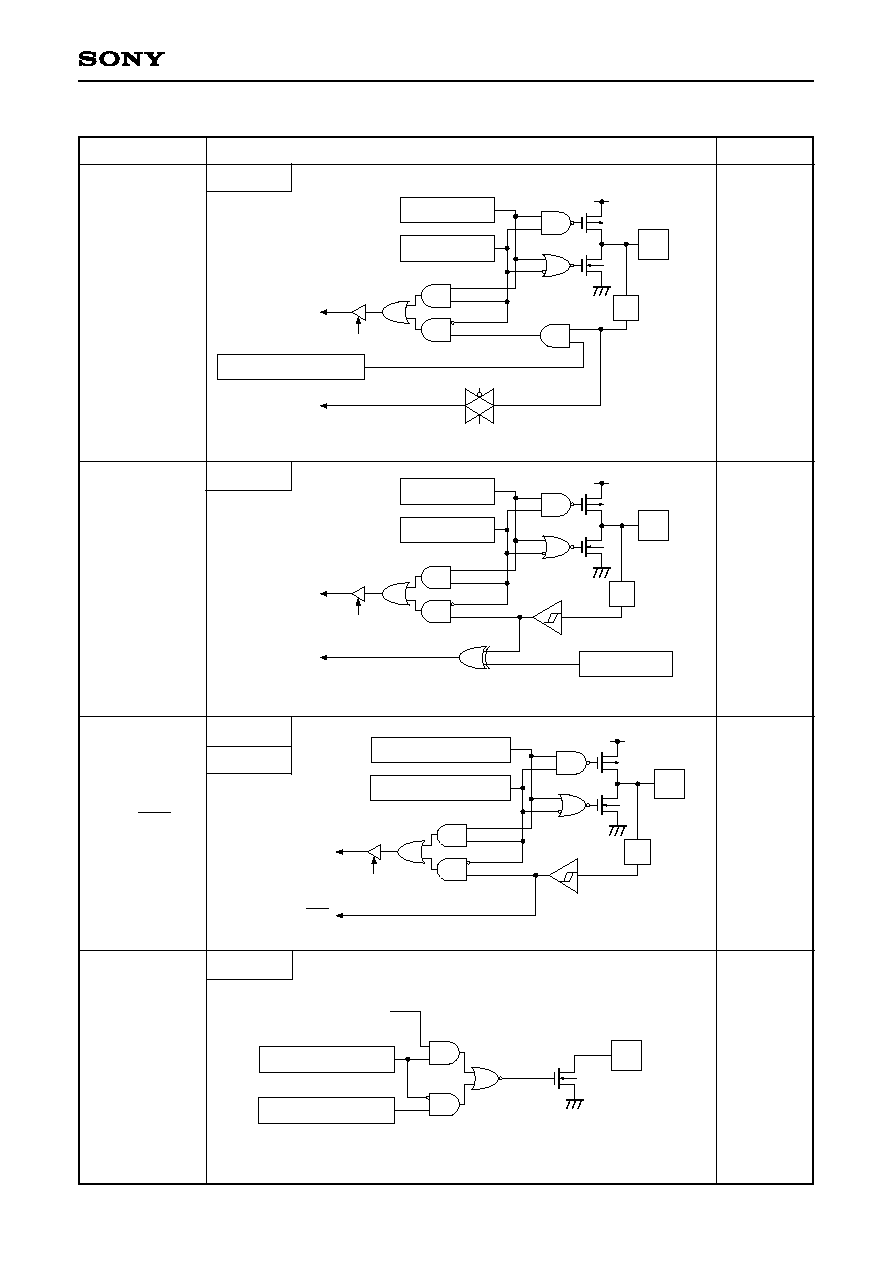

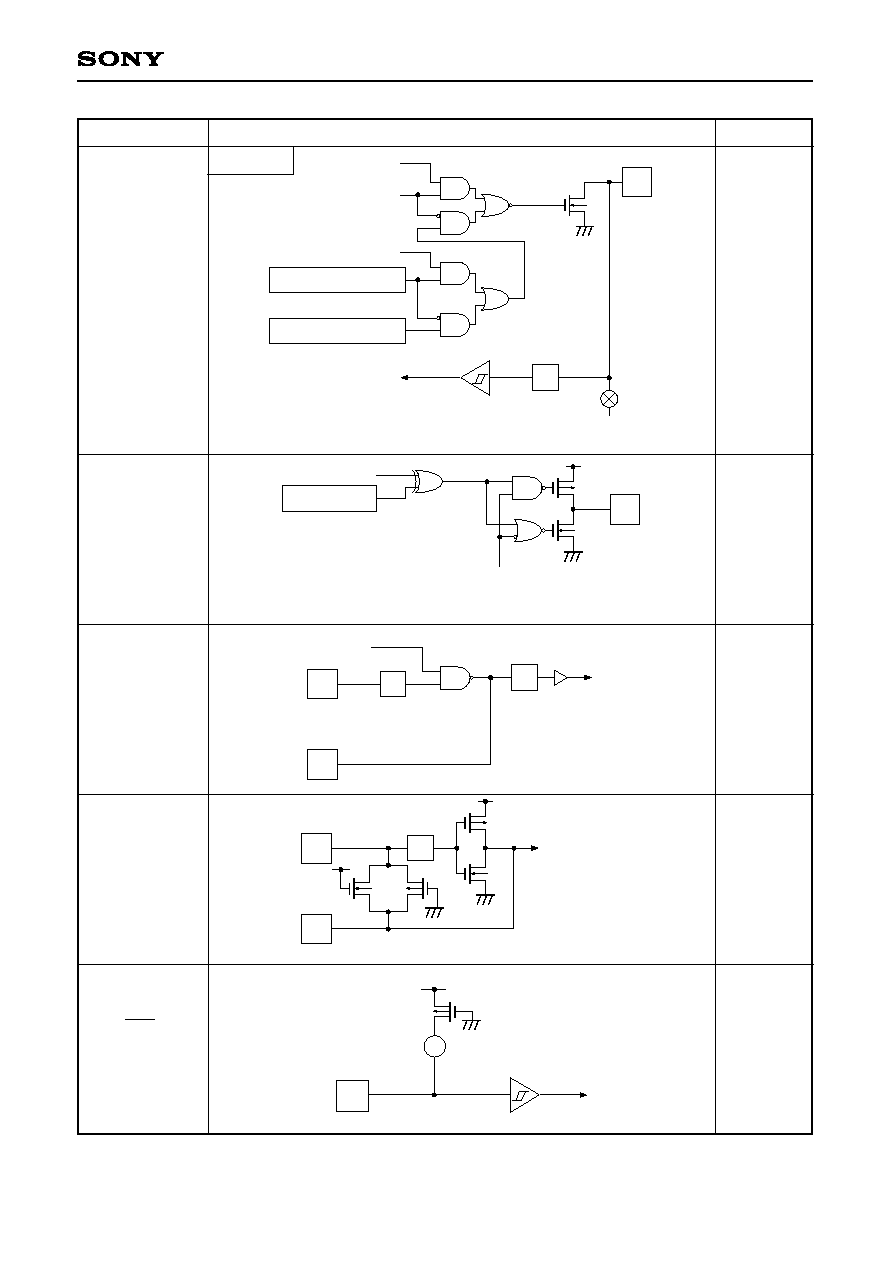

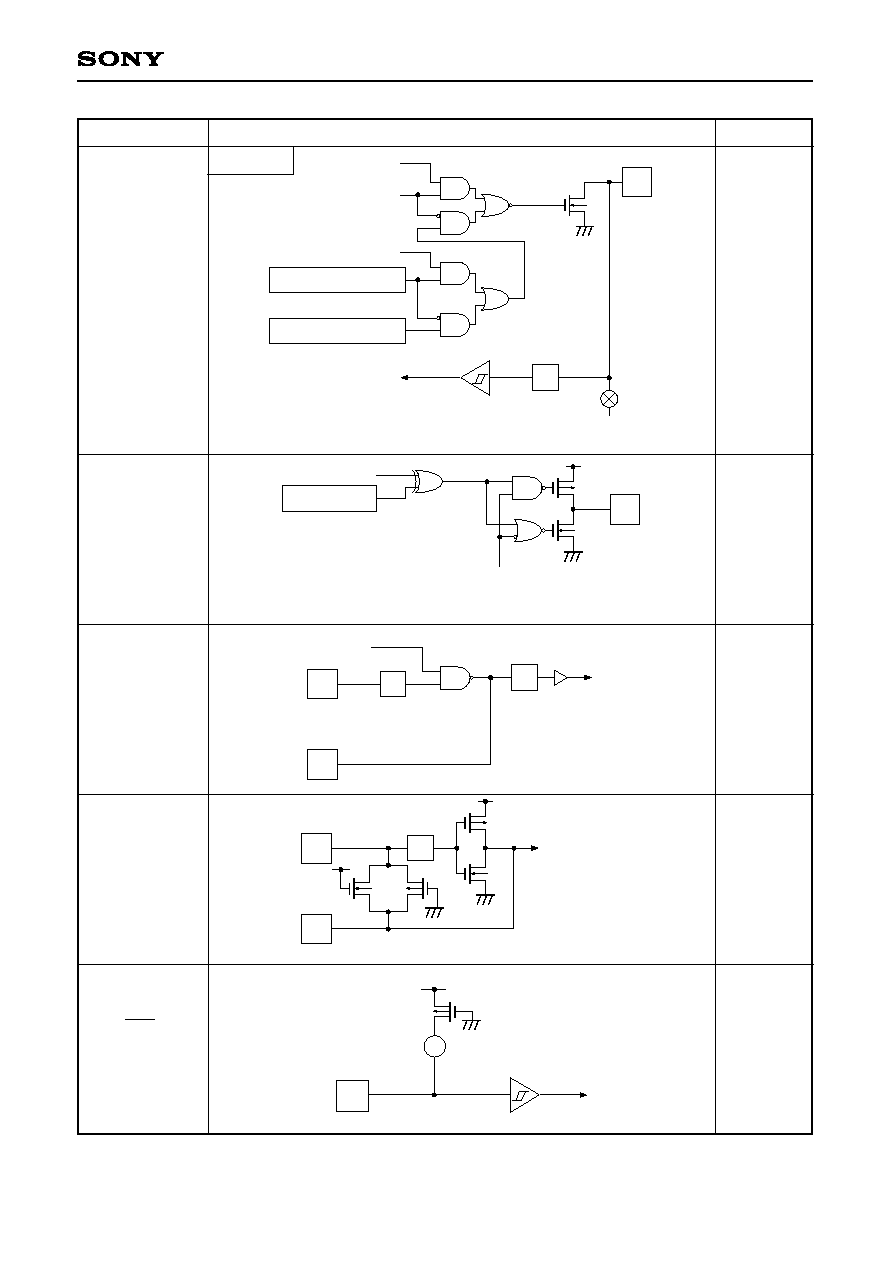

Input/Output Circuit Formats for Pins

Port A

Port A

Port B

Port G

6 pins

2 pins

9 pins

Hi-Z

Hi-Z

Hi-Z

Pin

When reset

Circuit format

PA6/VSYNC

PA7/HSYNC

PB0 to PB7

PG7/INT1

PA0/AN0

to

PA5/AN5

Port F data

Port F function selection

"0" when reset

"1" when reset

PWM0 to PWM3

12V drive voltage

Large current 12mA

Port F

4 pins

PF0/PWM0

to

PF3/PWM3

Hi-Z

≠ 7 ≠

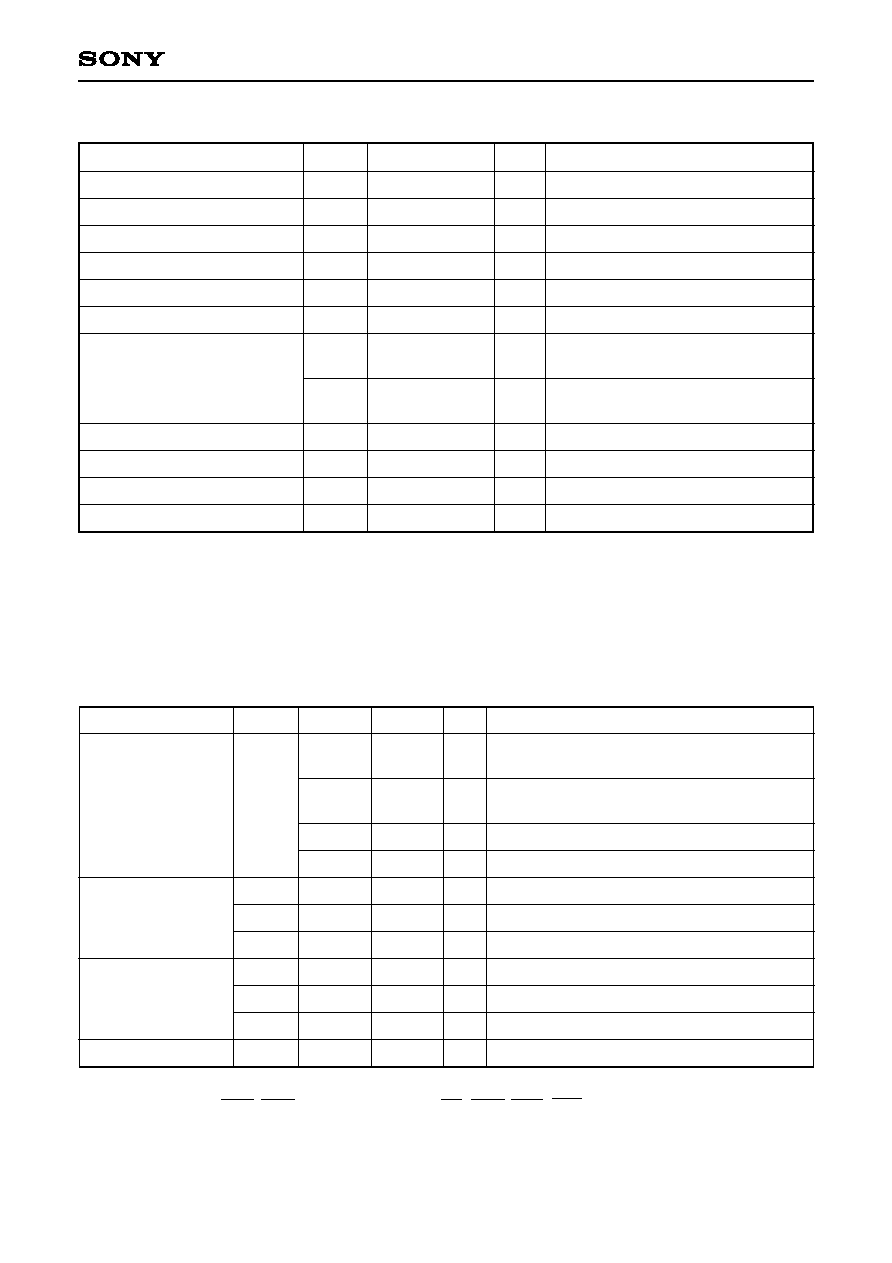

CXP86541/86549/86561

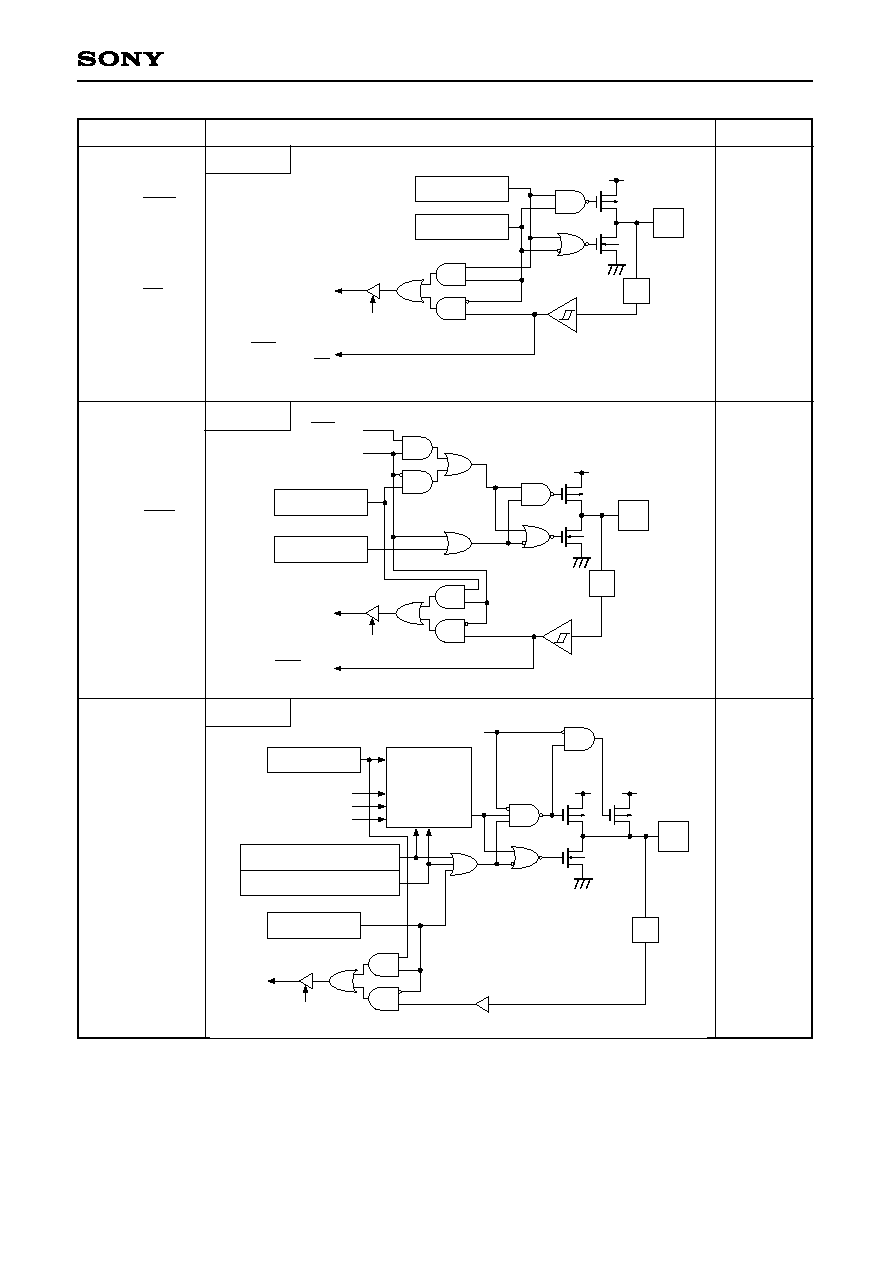

Port D data

Port D direction

IP

RD (Port D)

Data bus

INT2, SI, HS0,

HS1, RMC, EC

"0" when reset

Schmitt input

Large current 12mA

Port D data

Port D direction

IP

RD (Port D)

Data bus

"0" when reset

Schmitt input

only for PD1

SCK, SO

SIO output enable

SCK only

Large current 12mA

Port E data

"1" when reset

TO

ADJ16K

1

ADJ2K

1

01

00

10

11

MPX

Data bus

Port E direction

"1" when reset

Port E function selection (Lower)

"00" when reset

IP

Port E function selection (Upper)

Internal reset signal

2

1

ADJ signals are frequency

dividing outputs for 32kHz

oscillation frequency

adjustment. ADJ2K provides

usage as buzzer output.

2

Pull-up resistors approx. 150k

RD (Port E)

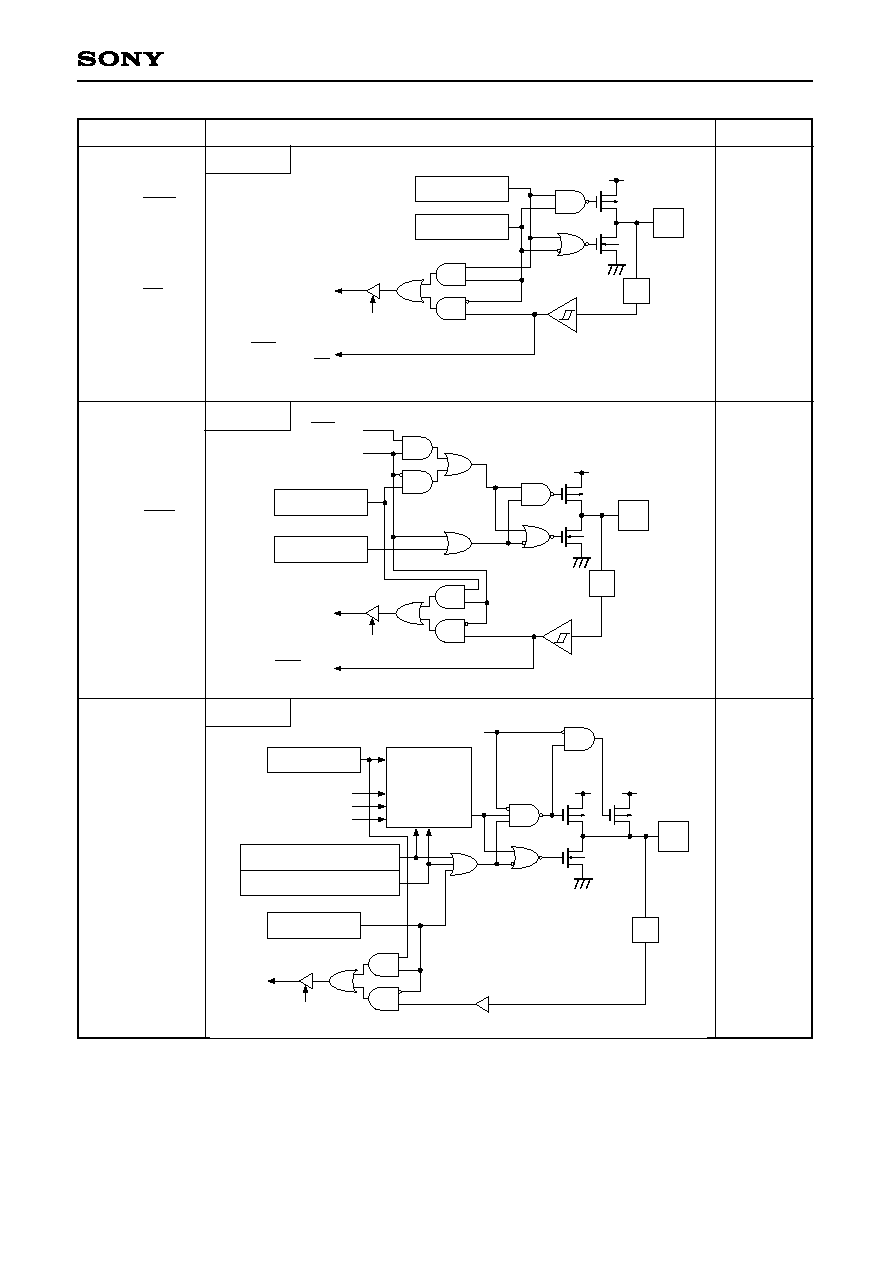

Port D

Port D

Port E

6 pins

2 pins

1 pin

Hi-Z

Hi-Z

High level

(with

approximately

150k

resistor when

reset)

Pin

When reset

Circuit format

PD1/SCK

PD2/SO

PE0/TO/ADJ

PD0/INT2

PD3/SI

PD4/HS0

PD5/HS1

PD6/RMC

PD7/EC

≠ 8 ≠

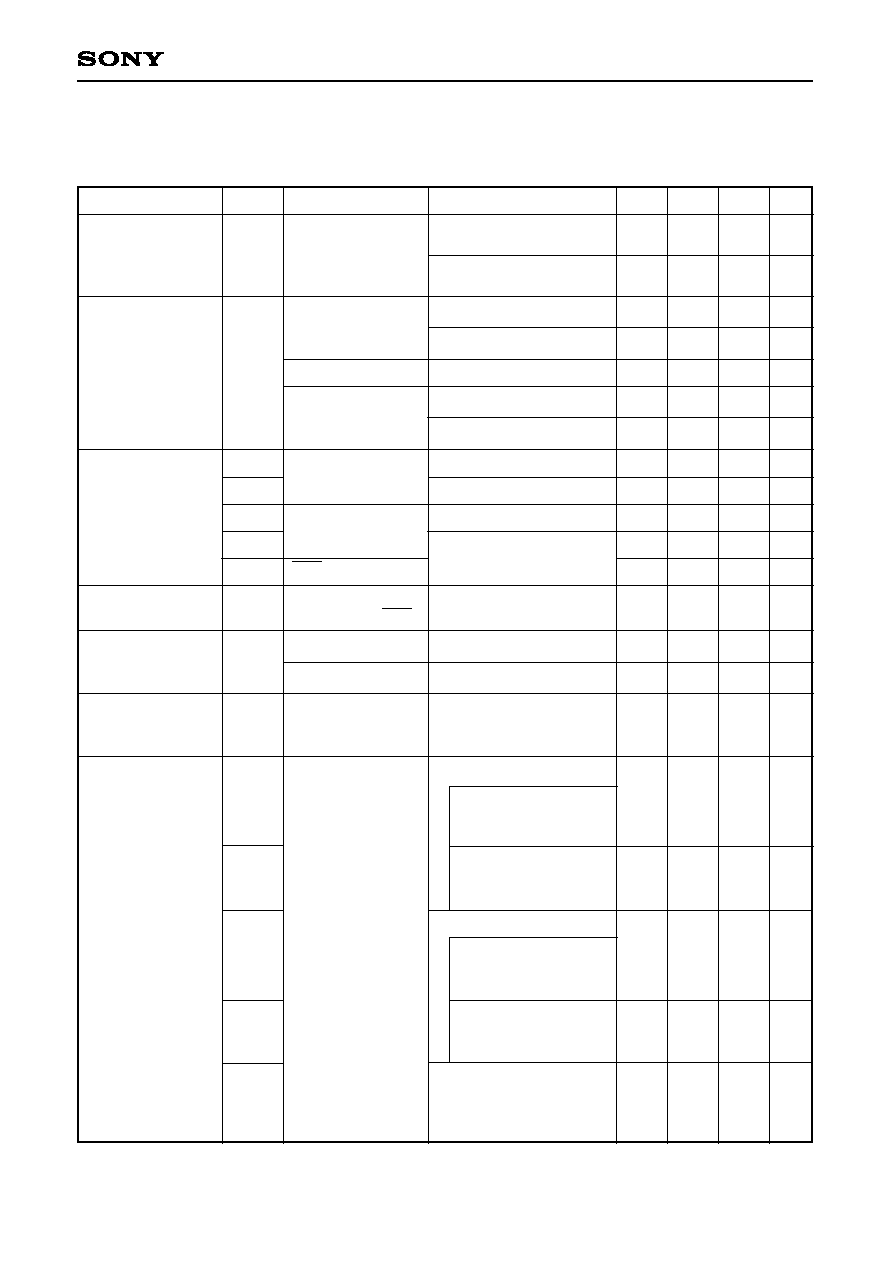

CXP86541/86549/86561

IP

IP

32kHz oscillation circuit control

RD (Port E)

Schmitt input

Schmitt input

Clock input

Data bus

Data bus

INT0

"1" when reset

PE2/

TEX/

INT0

PE3/

TX

RD (Port E)

Port E data

Port E direction

IP

RD (Port E)

Data bus

"1" when reset

PWM

"1" when reset

Port E function selection

"0" when reset

Port E

Port E

1 pin

2 pins

3 pins

Pin

When reset

Circuit format

PE2/TEX/INT0

PE3/TX

High level

Oscillation

halted

Port input

Hi-Z

PE1/PWM

PE4/YM

PE5/YS

PE6/I

Port E data

Port E function selection

"0" when reset

YM, YS, I

Output polarity

"0" when reset

Writing data to output polarity

register and port data register

brings output to active.

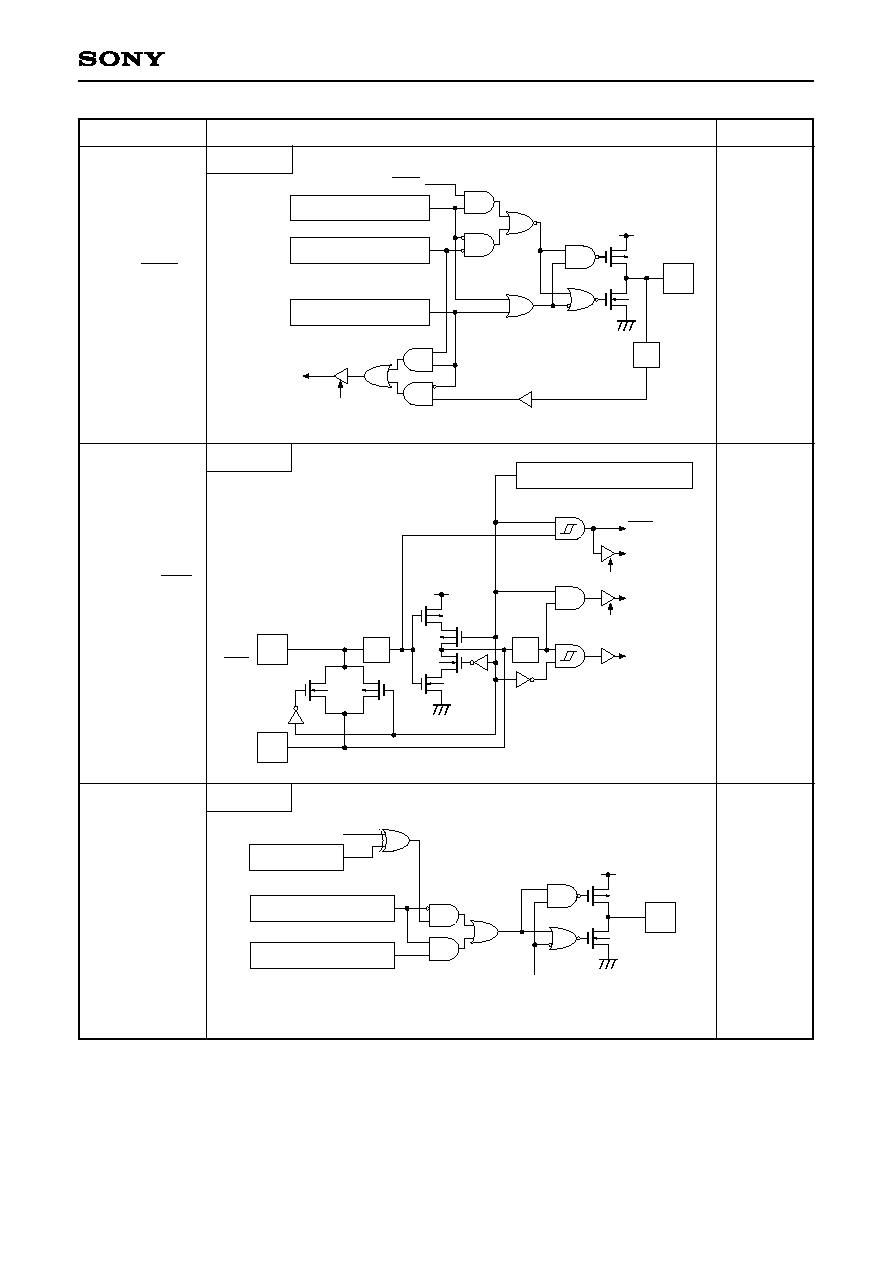

Port E

≠ 9 ≠

CXP86541/86549/86561

4 pins

3 pins

Pin

When reset

Circuit format

R

G

B

Hi-Z

Hi-Z

I

2

C bus enable

Port F data

Port F function selection

"0" when reset

"1" when reset

PWM4, PWM5

SCL, SDA

SCL, SDA

(I

2

C bus circuit)

IP

Schmitt input

Large current 12mA

To internal I

2

C pins

(SCL1 for SCL0)

BUS SW

R, G, B

Output polarity

"0" when reset

Writing data to output

polarity register brings

output to active.

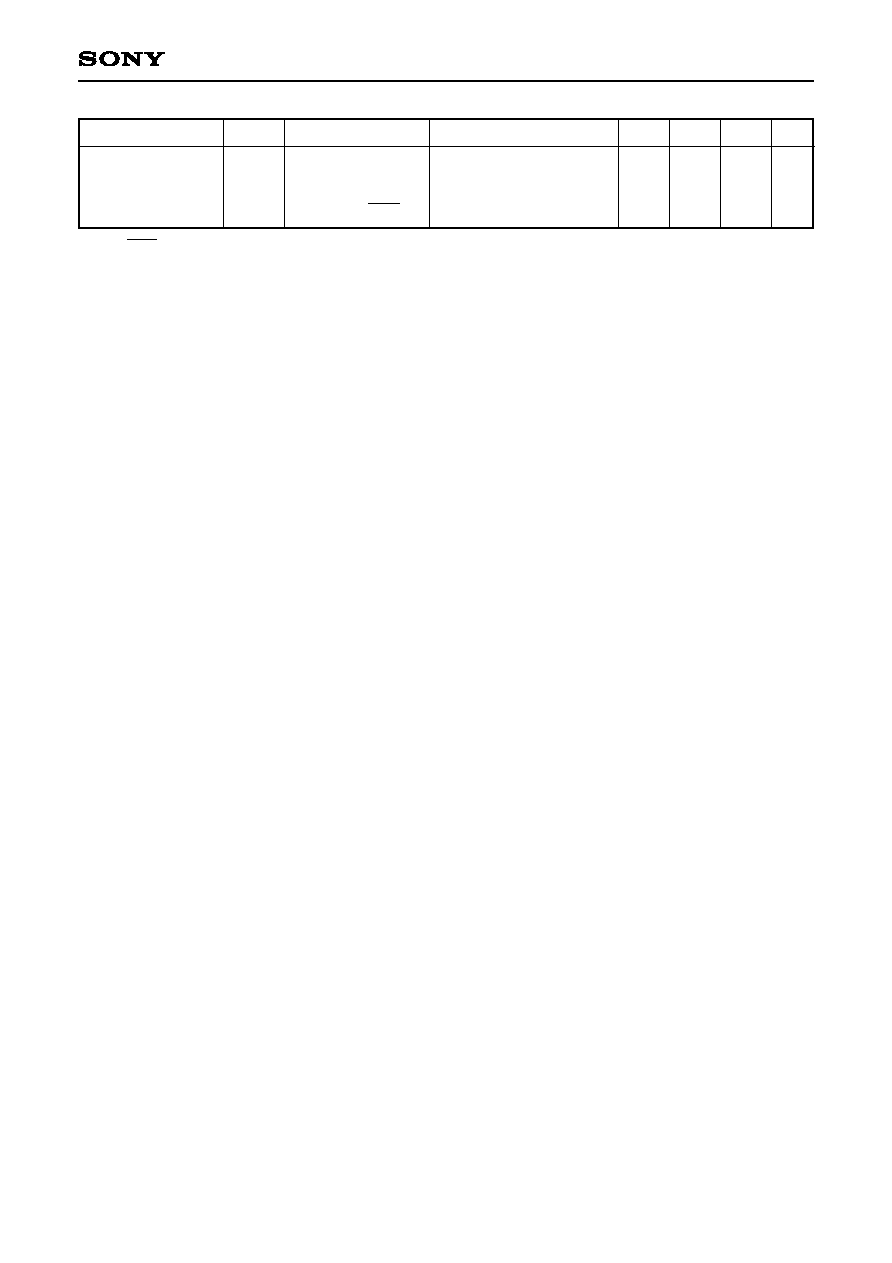

Port F

PF4/SCL0

PF5/SCL1/PWM4

PF6/SDA0

PF7/SDA1/PWM5

EXLC

XLC

IP

Oscillation control

IP

OSD display clock

IP

EXTAL

XTAL

∑ Diagram shows the

circuit composition

during oscillation.

∑ Feedback resistor is

removed during stop mode.

(This device does not

enter stop mode.)

Schmitt input

Pull-up resistor

OP Mask option

2 pins

EXLC

XLC

2 pins

EXTAL

XTAL

1 pin

RST

Oscillation

halted

Oscillation

Low level

≠ 10 ≠

CXP86541/86549/86561

1

V

IN

and V

OUT

should not exceed V

DD

+ 0.3V.

2

The large current output port is Port D (PD) and Port F (PF).

Note) Usage exceeding absolute maximum ratings may permanently impair the LSI. Normal operation should

be conducted under the recommended operating conditions. Exceeding those conditions may

adversely affect the reliability of the LSI.

V

DD

V

IN

V

OUT

V

OUTP

I

OH

I

OH

I

OL

I

OLC

I

OL

Topr

Tstg

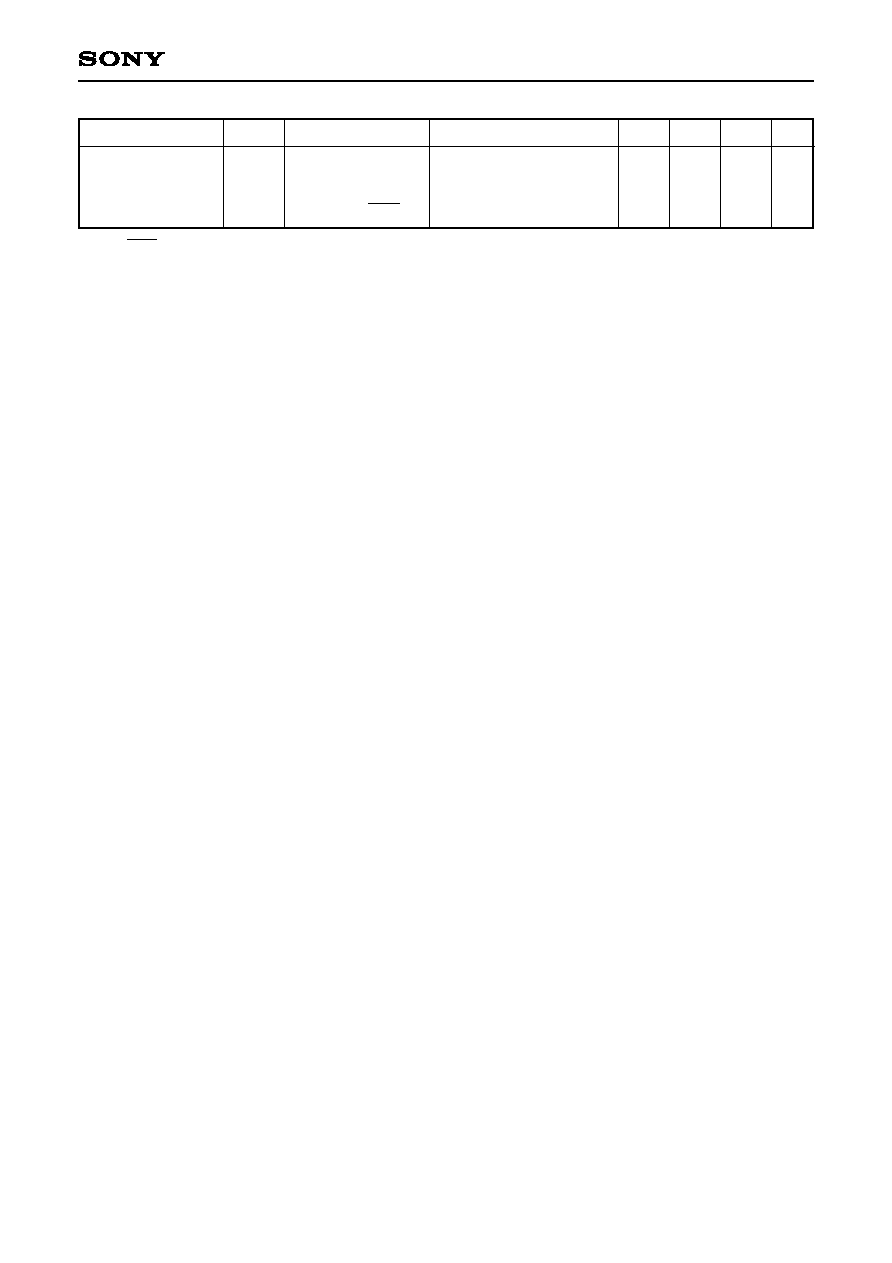

P

D

≠0.3 to +7.0

≠0.3 to +7.0

1

≠0.3 to +7.0

1

≠0.3 to +15.0

≠5

≠50

15

20

130

≠20 to +75

≠55 to +150

375

V

V

V

V

mA

mA

mA

mA

mA

∞C

∞C

mW

Total of all output pins

Ports excluding large current output

(value per pin)

Large current output ports

(value per pin

2

)

Total of all output pins

SDIP-52P-01

Item

Symbol

Ratings

Unit

Remarks

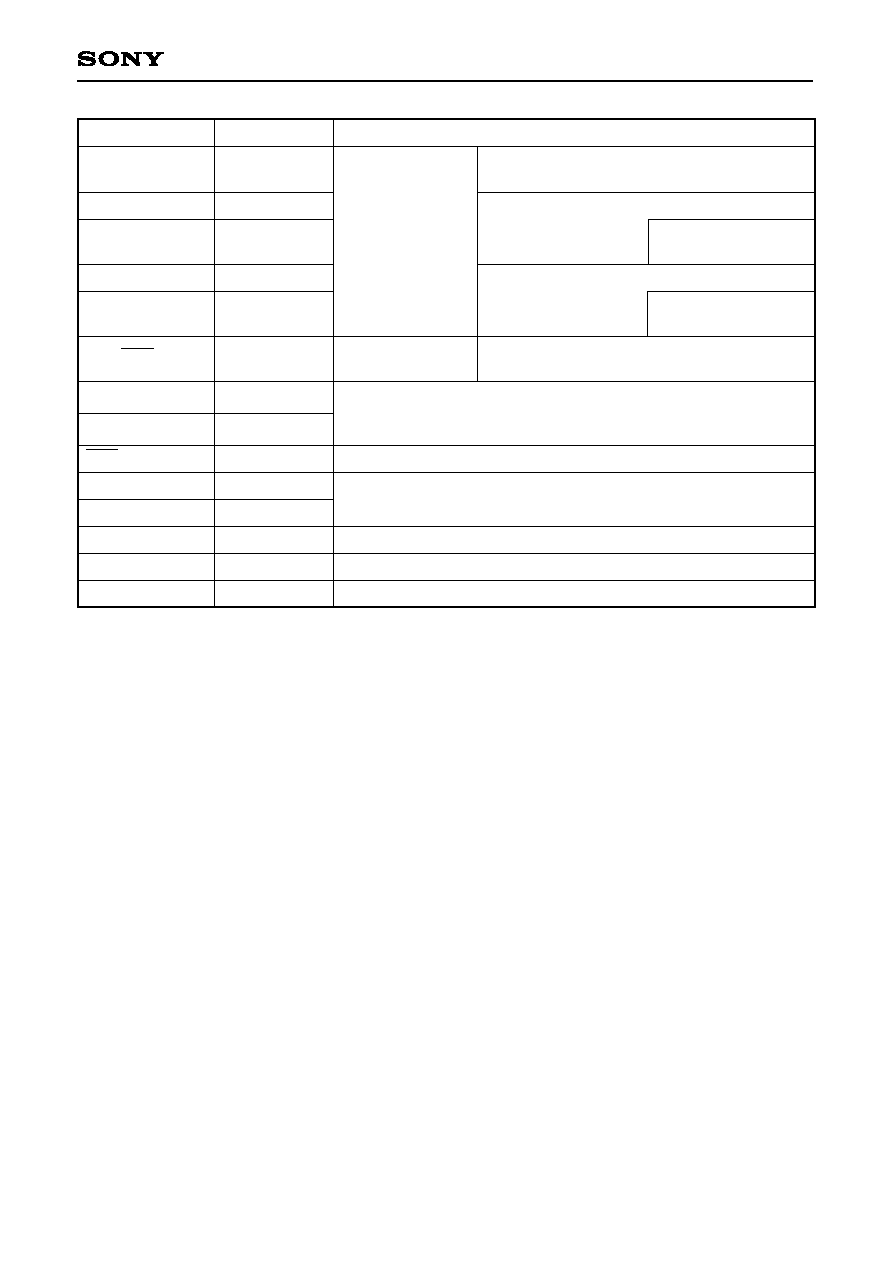

Absolute Maximum Ratings

(Vss = 0V reference)

Supply voltage

High level input

voltage

Low level input

voltage

Operating temperature

5.5

5.5

5.5

--

V

DD

V

DD

V

DD

+ 0.3

0.3V

DD

0.2V

DD

0.4

+75

V

V

V

V

V

V

V

V

V

V

∞C

Item

Symbol

Min.

Max.

Unit

Remarks

4.5

3.5

2.7

--

0.7V

DD

0.8V

DD

V

DD

≠ 0.4

0

0

≠0.3

≠20

V

IH

V

IHS

V

IHEX

V

IL

V

ILS

V

ILEX

Topr

Guaranteed operation range for 1/2 and 1/4

frequency dividing modes

Guaranteed operation range for 1/16 frequency

dividing mode or sleep mode

Guaranteed operation range for TEX mode

Guaranteed data hold range for stop mode

5

1

2

EXTAL pin

3

, TEX pin

4

1

2

EXTAL pin

3

, TEX pin

4

V

DD

1

PA1 to PA5, PB3 to PB7, PD2, PE0, PE1, PE3, SCL0, SCL1, SDA0, SDA1 pins

2

VSYNC, HSYNC, INT2, SCK, SI, HS0, HS1, RMC, EC, INT0, INT1, RST, PB0, PB1, PB2 pins

3

Specifies only during external clock input.

4

Specifies only during external event count input.

5

This device does not enter the stop mode.

Recommended Operating Conditions

(Vss = 0V reference)

Supply voltage

Input voltage

Output voltage

Mid-voltage drive output voltage

High level output current

High level total output current

Low level output current

Low level total output current

Operating temperature

Storage temperature

Allowable power dissipation

≠ 11 ≠

CXP86541/86549/86561

V

DD

= 4.5V, I

OH

= ≠0.5mA

V

DD

= 4.5V, I

OH

= ≠1.2mA

V

DD

= 4.5V, I

OL

= 1.8mA

V

DD

= 4.5V, I

OL

= 3.6mA

V

DD

= 4.5V, I

OL

= 3.0mA

V

DD

= 4.5V, I

OL

= 4.0mA

V

DD

= 5.5V, V

IH

= 5.5V

V

DD

= 5.5V, V

IL

= 0.4V

V

DD

= 5.5V, V

IH

= 5.5V

V

DD

= 4.5V, I

OL

= 12.0mA

High level output

voltage

Low level output

voltage

Input current

I/O leakage current

Open drain I/O

leakage current

(in N-ch Tr off state)

Supply current

2

4.0

3.5

18

30

1.2

12

--

--

µA

mA

µA

µA

50

10

120

28

80

2.1

35

--

mA

µA

µA

0.4

0.6

1.5

0.4

0.6

40

≠40

10

≠10

≠400

±10

V

V

V

V

V

µA

µA

µA

µA

µA

µA

0.5

≠0.5

0.1

≠0.1

≠1.5

V

V

PA, PB, PD,

PE0 to PE1,

PE4 to PE6, PG7,

R, G, B

PA, PB, PD, PE0 to PE1,

PE4 to PE6, PF0 to PF3,

PG7, R, G, B

PD, PF

PF4 to PF7

(SCL0, SCL1,

SDA0, SDA1)

EXTAL

RST

1

PA, PB, PD, PE,

PG7, R, G, B, RST

1

PF0 to PF3

PF4 to PF7

SCL0: SCL1

SDA0: SDA1

V

DD

= 5.5V, V

IL

= 0.4V

V

DD

= 5.5V,

V

I

= 0, 5.5V

V

DD

= 5.5V, V

OH

= 12.0V

V

DD

= 5.5V, V

OH

= 5.5V

V

DD

= 4.5V

V

SCL0

= V

SCL1

= 2.25V

V

SDA0

= V

SDA1

= 2.25V

V

DD

V

DD

= 3.3V,

32MHz crystal oscillation

(C

1

= C

2

= 47pF)

Item

Symbol

Pins

Conditions

Min.

Typ.

Max.

Unit

V

OH

V

OL

I

IZ

I

LOH

R

BS

I

DD1

I

DD2

I

DDS1

I

DDS2

I

DDS3

I

IHE

I

ILE

I

IHT

I

ILT

I

ILR

Electrical Characteristics

DC characteristics

(Ta = ≠20 to +75∞C, Vss = 0V reference)

1/2 frequency dividing mode

TEX

V

DD

= 5.5V,

16MHz crystal oscillation

(C

1

= C

2

= 15pF)

V

DD

= 3.3V,

32MHz crystal oscillation

(C

1

= C

2

= 47pF)

SLEEP mode

V

DD

= 5.5V,

16MHz crystal oscillation

(C

1

= C

2

= 15pF)

STOP mode

3

V

DD

= 5.5V,

termination of 16MHz

and 32MHz oscillation

I

2

C bus switch

connection impedance

(in output Tr off state)

≠ 12 ≠

CXP86541/86549/86561

1

For RST pin, specifies the input current when pull-up resistance is selected, and specifies the leakage

current when non-resistor is selected.

2

When all output pins are left open. Specifies only when the OSD oscillation is halted.

3

This device does not enter the stop mode.

Input capacitance

10

20

pF

PA, PB, PD,PE0 to

PE3, R, G, B, PF4 to

PF7 ,PG7 ,EXTAL,

TEX, EXLC, RST

Clock 1 MHz

0V other than the

measured pins

Item

Symbol

Pins

Conditions

Min.

Typ.

Max.

Unit

C

IN

≠ 13 ≠

CXP86541/86549/86561

1

Indicates three values according to the contents of the clock control register (CLC: 00FE

h

) upper 2 bits

(CPU clock selection).

t

sys (ns) = 2000/fc (Upper 2 bits = "00"), 4000/fc (Upper 2 bits = "01"), 16000/fc (Upper 2 bits = "11")

EXTAL

t

XH

t

XL

t

CF

t

CR

0.4V

V

DD

≠ 0.4V

1/fc

Crystal oscillation

Ceramic oscillation

EXTAL

XTAL

External clock

EXTAL

XTAL

74HC04

C

1

C

2

32kHz clock applied condition

Crystal oscillation

TEX

TX

C

1

C

2

TEX

EC

t

EH

t

EL

t

EF

t

ER

0.2V

DD

0.8V

DD

t

TH

t

TL

t

TF

t

TR

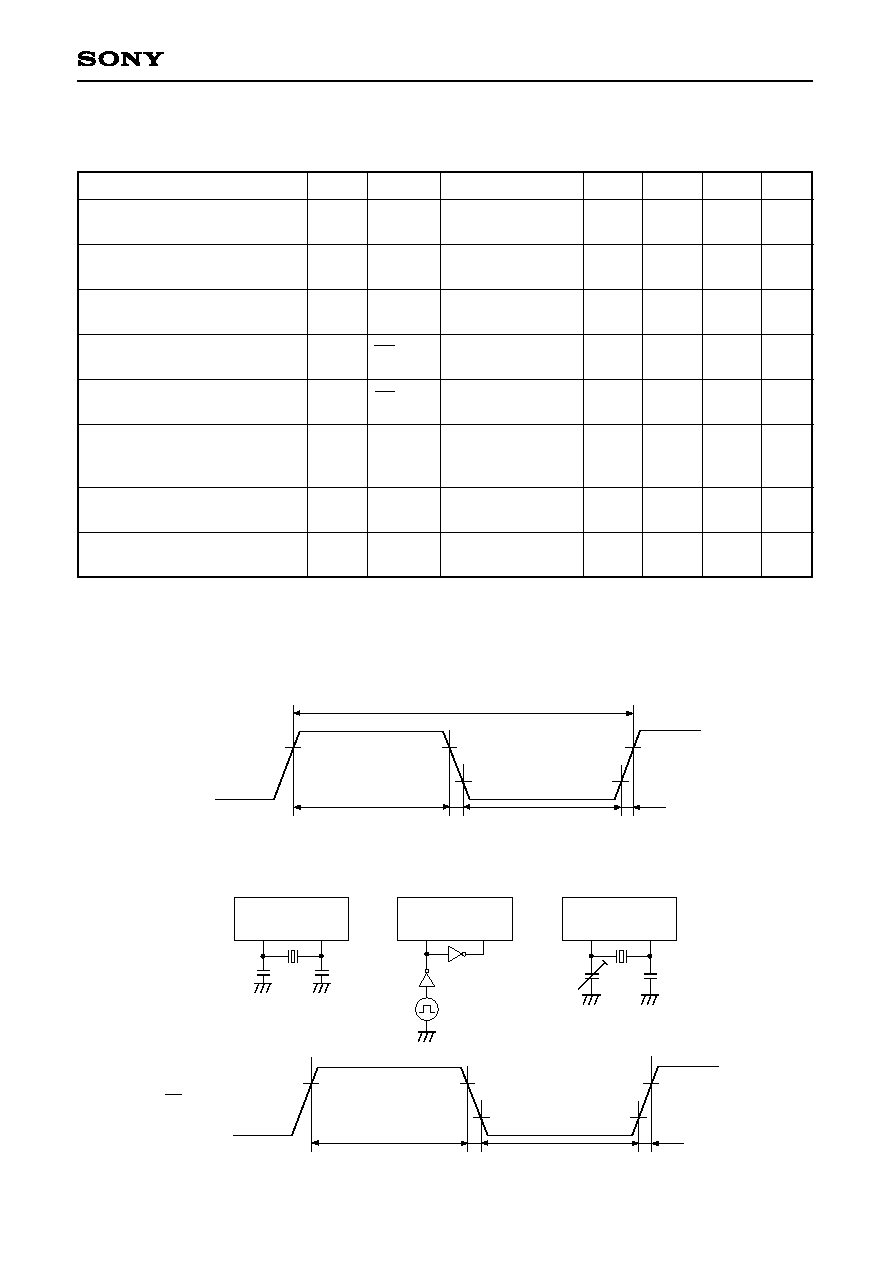

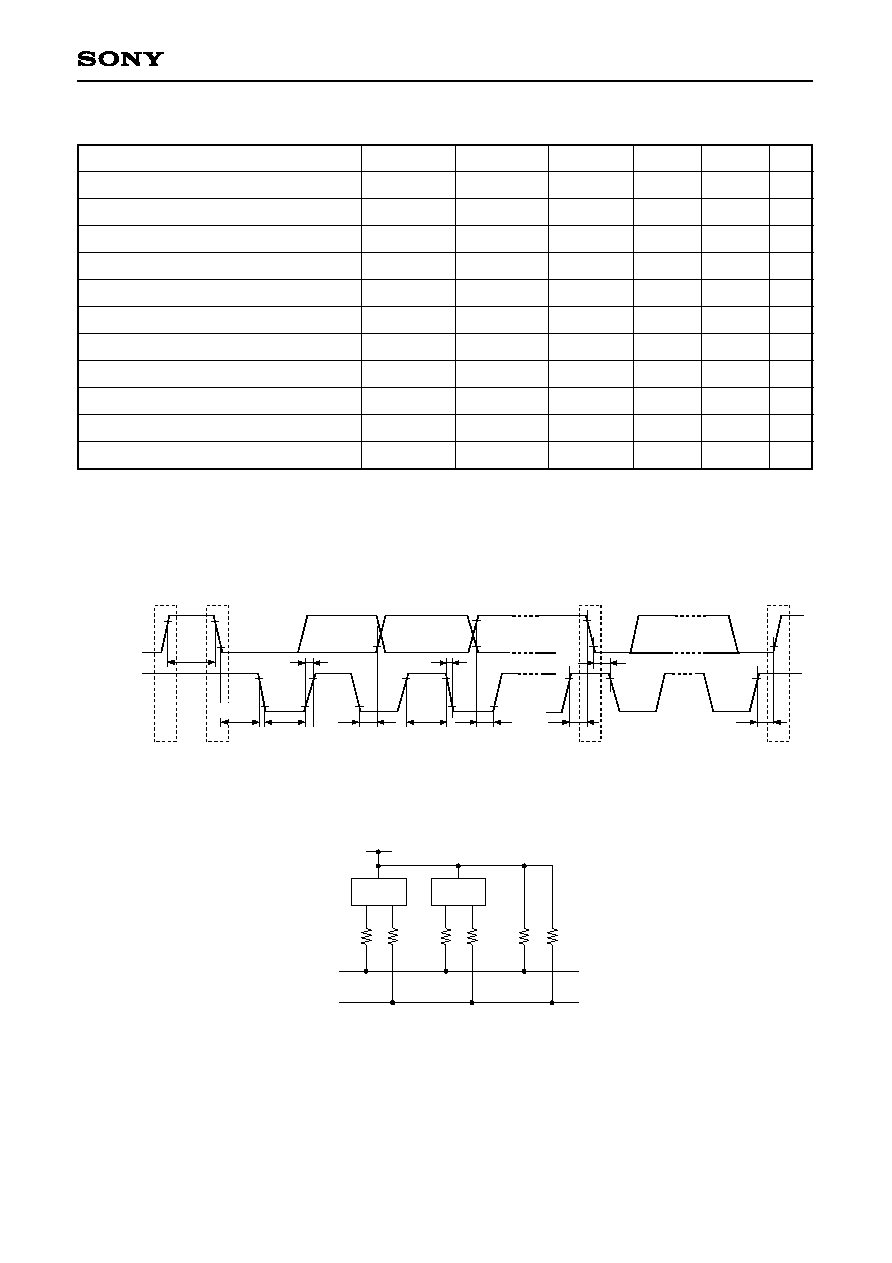

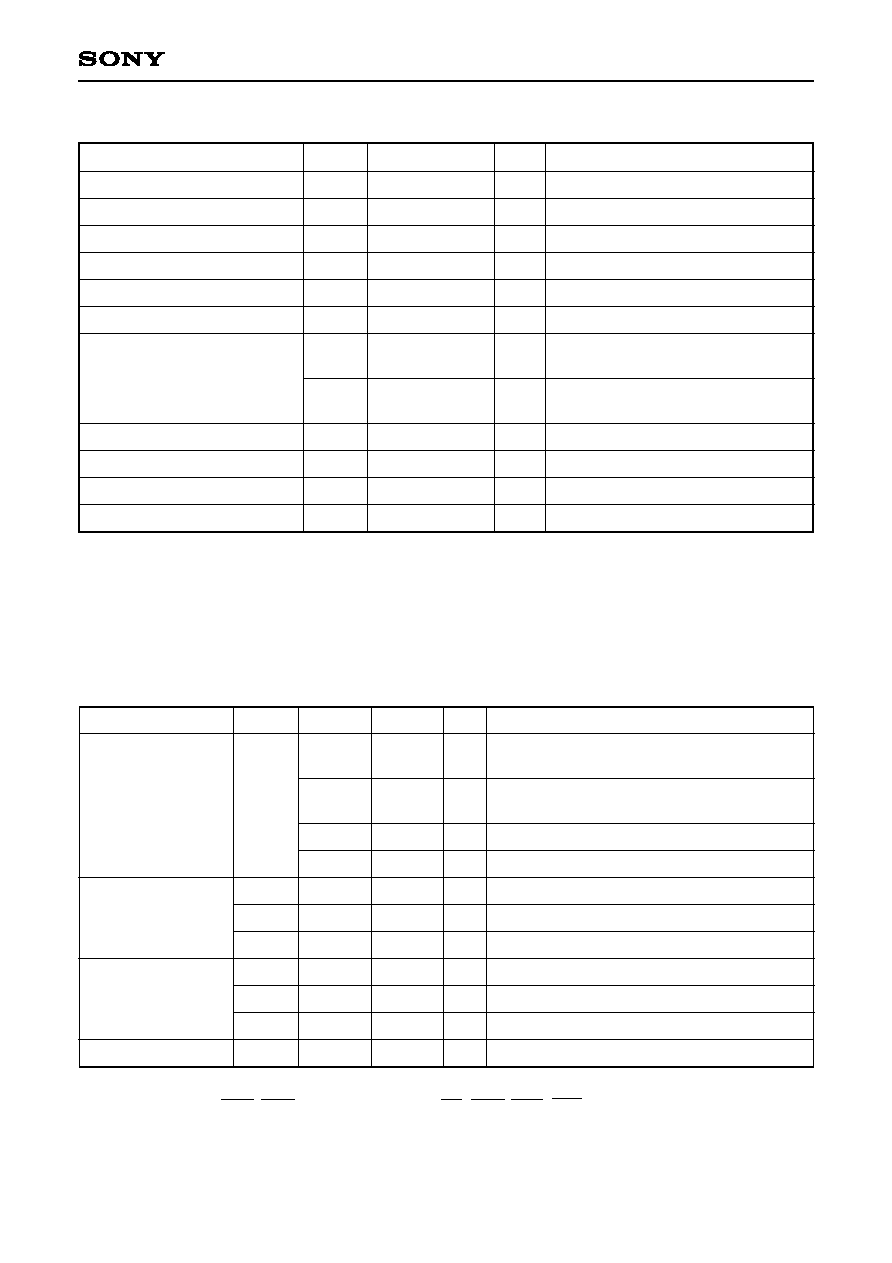

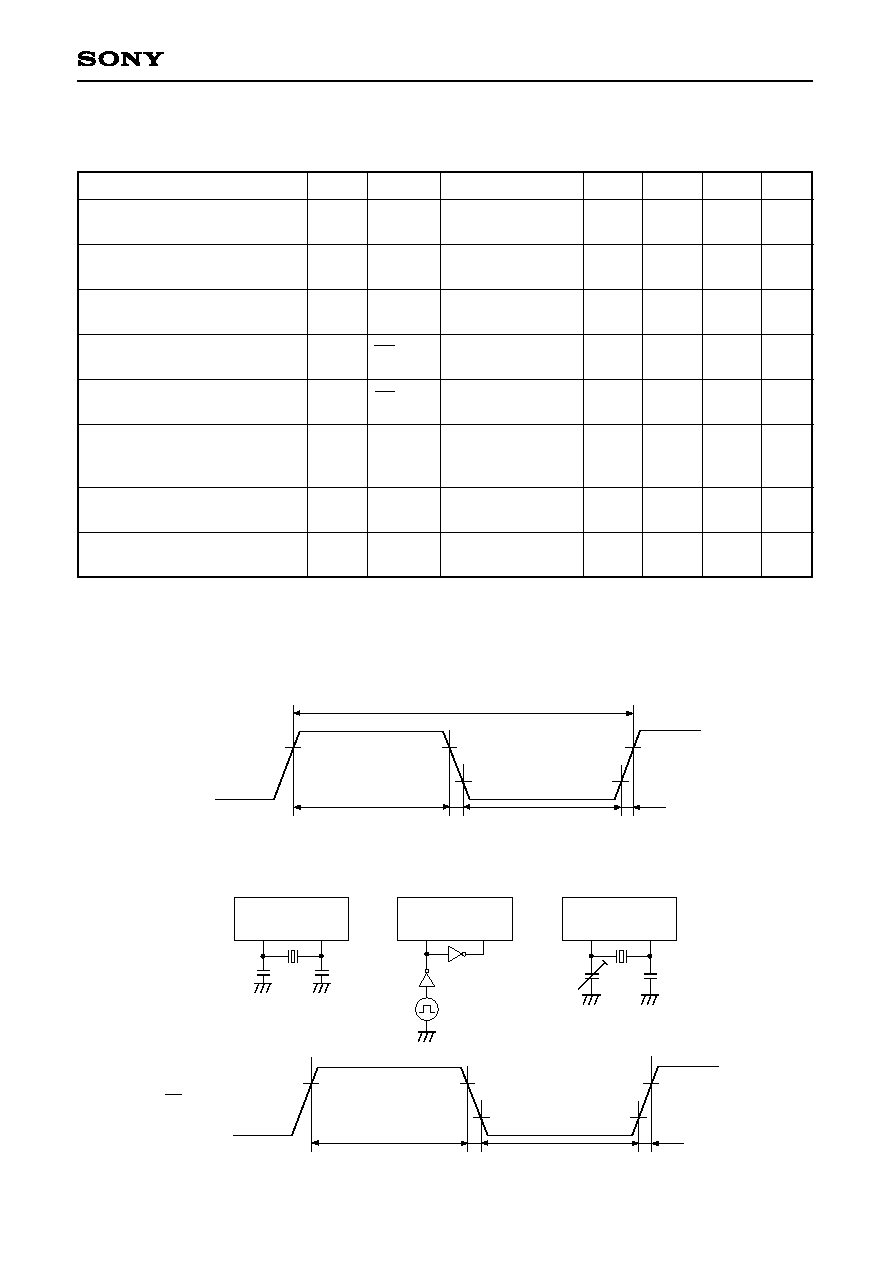

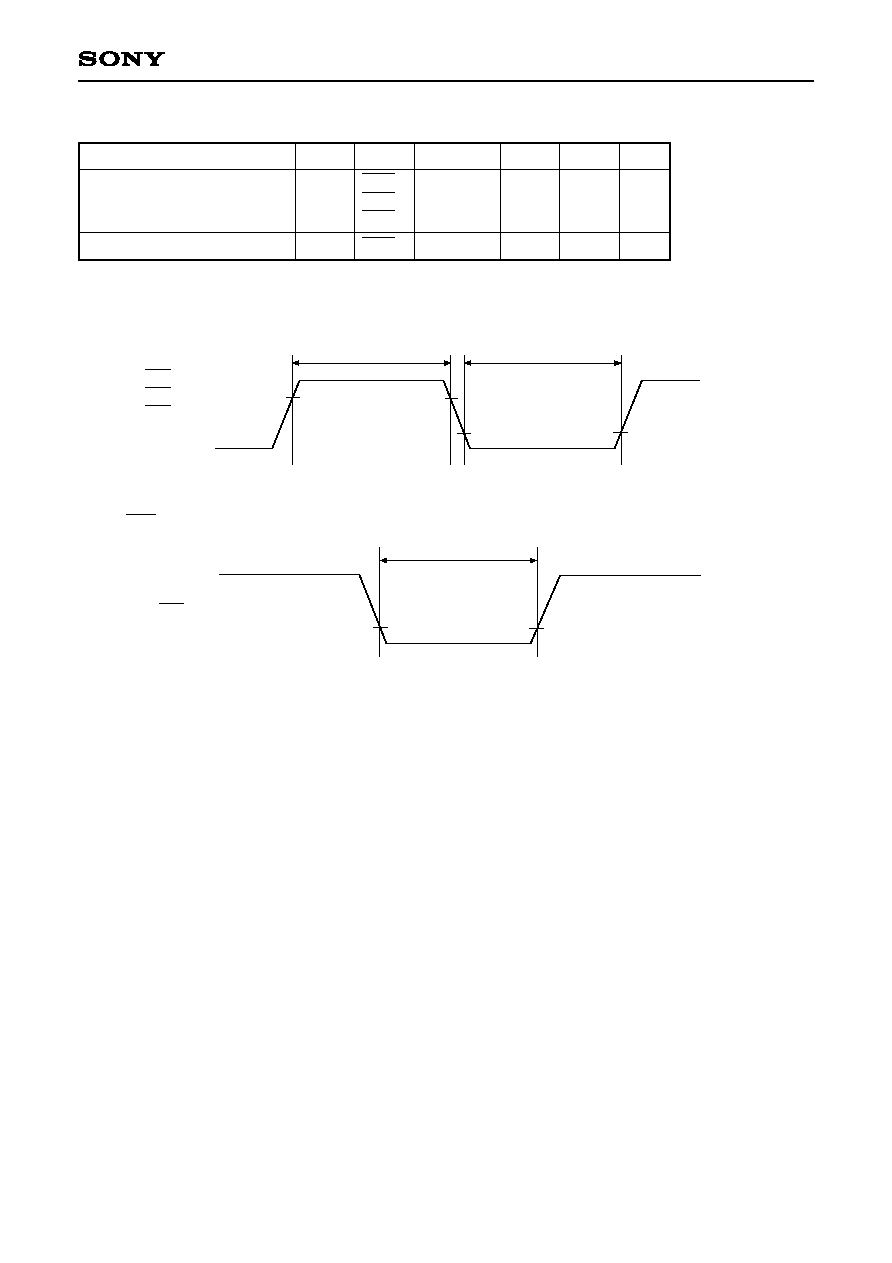

AC Characteristics

(1) Clock timing

System clock frequency

System clock input pulse width

System clock input rise and fall

times

Event count input clock pulse

width

Event count input clock rise

and fall times

System clock frequency

Event count input clock

pulse width

Event count input clock rise

and fall times

f

C

t

XL

,

t

XH

t

CR

,

t

CF

t

EH

,

t

EL

t

ER

,

t

EF

f

C

t

TL

,

t

TH

t

TR

,

t

TF

XTAL

EXTAL

EXTAL

EXTAL

EC

EC

TEX

TX

TEX

TEX

MHz

ns

ns

ns

ms

kHz

µs

ms

Item

Symbol

Pins

Conditions

Min.

Unit

Fig. 1, Fig.2

Fig. 1, Fig.2

External clock drive

Fig. 1, Fig.2

External clock drive

Fig. 3

Fig. 3

V

DD

= 2.7 to 5.5 V

Fig. 2 (32kHz clock

applied conditions)

Fig. 3

Fig. 3

8

28

4

t

sys

1

10

Typ.

32.768

Max

16

200

20

20

(Ta = ≠20 to +75∞C, V

DD

= 4.5 to 5.5V, Vss = 0V reference)

Fig.2. Clock applied conditions

Fig. 1. Clock timing

Fig. 3. Event count clock timing

≠ 14 ≠

CXP86541/86549/86561

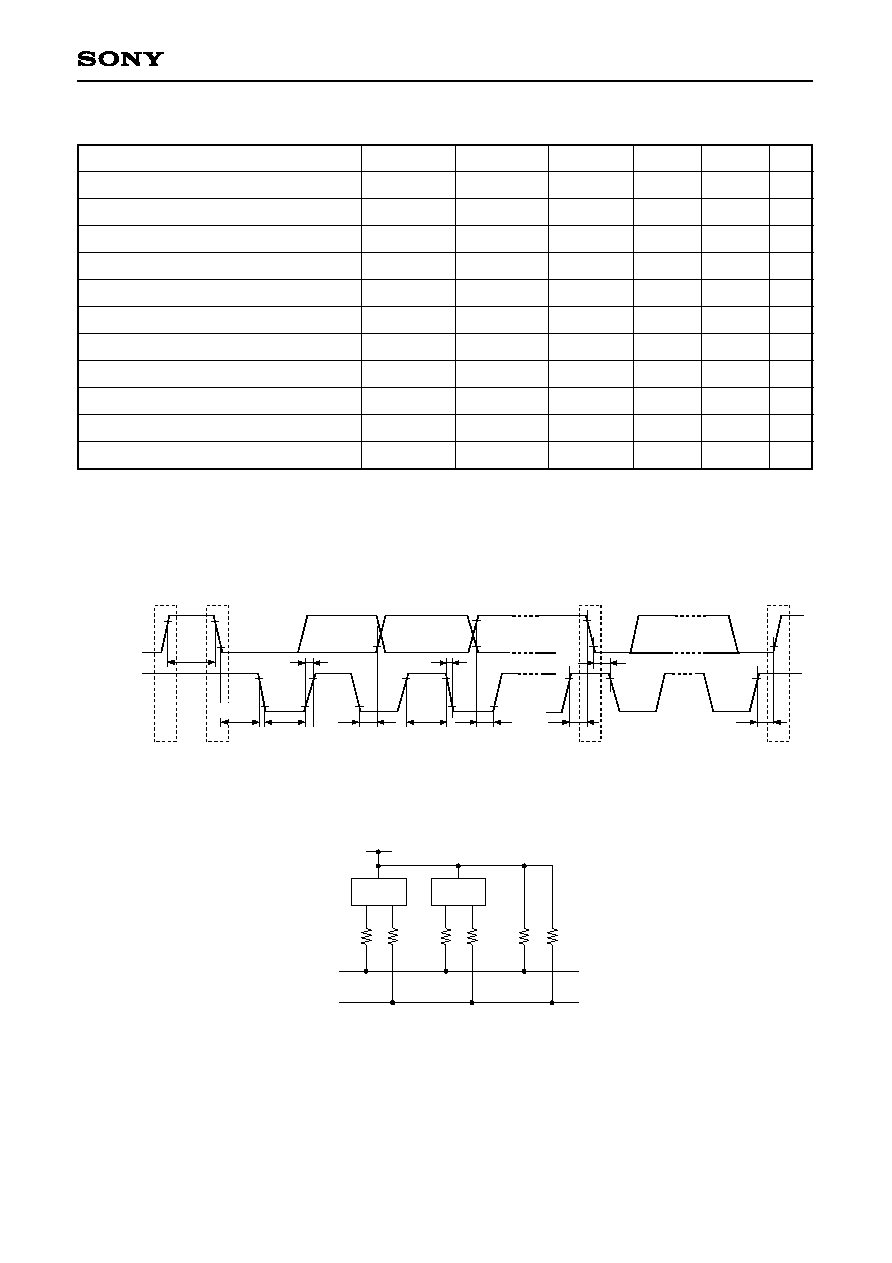

(2) Serial transfer

(Ta = ≠20 to +75∞C, V

DD

= 4.5 to 5.5V, Vss = 0V reference)

Item

SCK cycle time

t

KCY

SCK

Input mode

Output mode

SCK input mode

SCK output mode

SCK input mode

SCK output mode

SCK input mode

SCK output mode

SCK input mode

SCK output mode

1000

8000/fc

400

4000/fc ≠ 50

100

200

200

100

200

100

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

SCK

SI

SI

SO

t

KH

t

KL

t

SIK

t

KSI

t

KSO

SCK High and Low level

widths

SI input setup time

(for SCK

)

SI hold time

(for SCK

)

SCK

SO delay time

Symbol

Pins

Conditions

Min.

Max.

Unit

Note) The load of SCK output mode and SO output delay time is 50pF + 1TTL.

Fig. 4. Serial transfer timing

0.2V

DD

0.8V

DD

t

KL

t

KH

SO

t

KCY

t

SIK

t

KSI

0.2V

DD

0.8V

DD

t

KSO

0.2V

DD

0.8V

DD

Output data

Input data

SI

SCK

≠ 15 ≠

CXP86541/86549/86561

Resolution

Linearity error

Zero transition

voltage

Full-scale transition

voltage

Conversion time

Sampling time

Analog input voltage

V

ZT

1

V

FT

2

t

CONV

t

SAMP

V

IAN

AN0 to AN5

Ta = 25∞C

V

DD

= 5.0V

Vss = 0V

≠10

4910

26/f

ADC

3

6/f

ADC

3

0

10

4970

8

±3

70

5030

V

DD

Bits

LSB

mV

mV

µs

µs

V

Item

Symbol

Pins

Conditions

Min.

Typ.

Max.

Unit

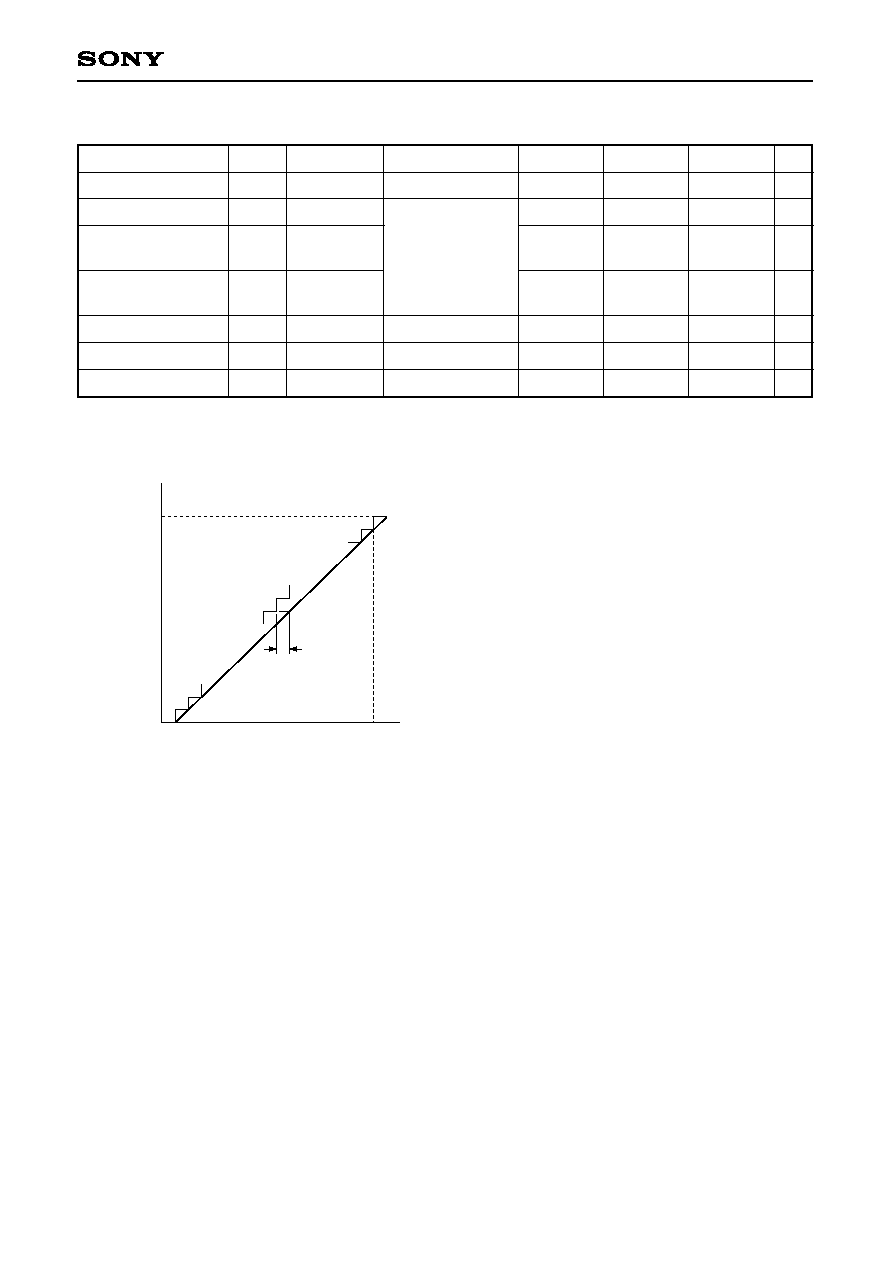

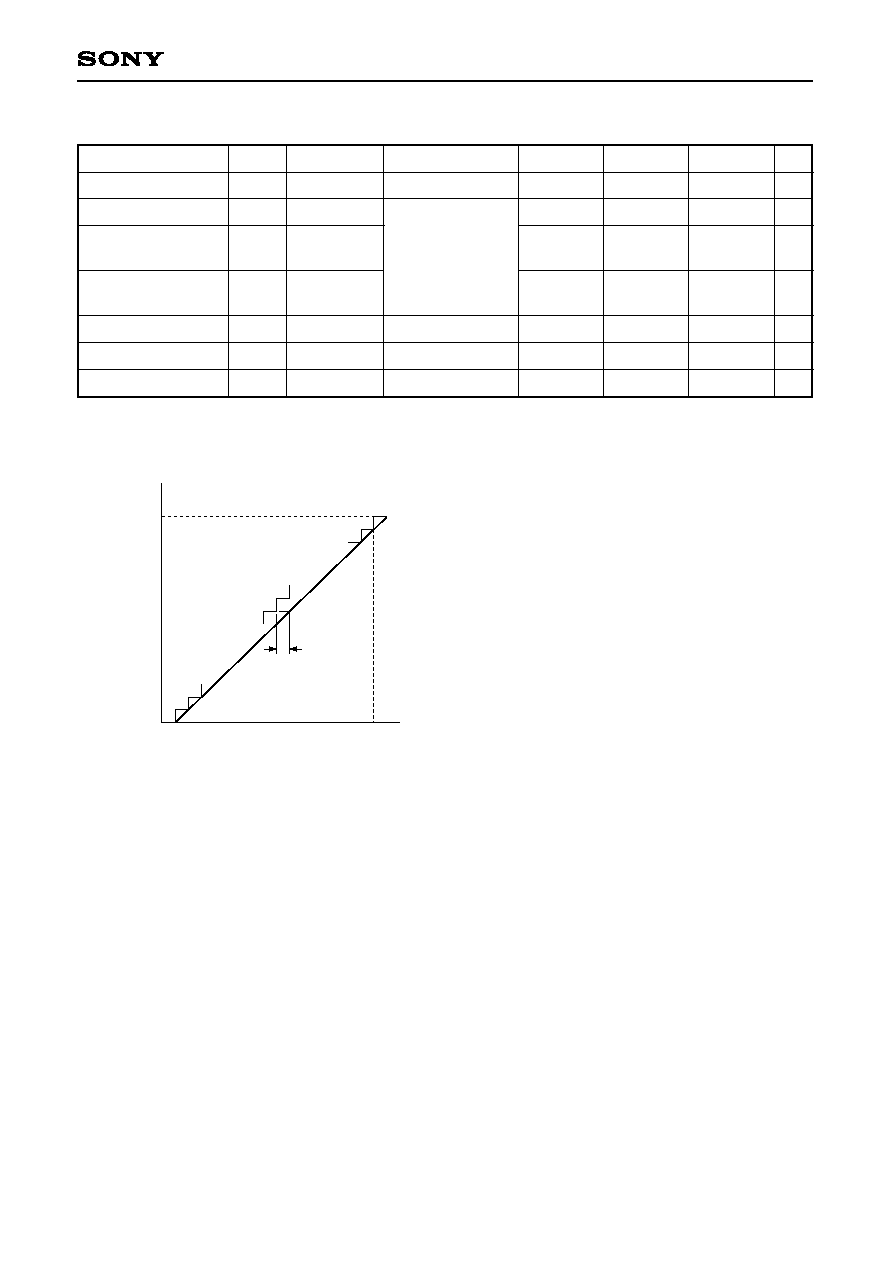

(3) A/D converter

(Ta = ≠20 to +75∞C, V

DD

= 4.5 to 5.5V, Vss = 0V reference)

Linearity error

V

ZT

V

FT

Analog input

FF

h

FE

h

01

h

00

h

D

i

g

i

t

a

l

c

o

n

v

e

r

s

i

o

n

v

a

l

u

e

Fig. 5. Definitions for A/D converter terms

1

V

ZT

: Value at which the digital conversion value changes

from 00

h

to 01

h

and vice versa.

2

V

FT

: Value at which the digital conversion value changes

from FE

h

to FF

h

and vice versa.

3

f

ADC

indicates the below values due to the contents of bit

6 (CKS) of the A/D control register (ADC: 00F6

h

):

f

ADC

= fc (CKS = "0"), fc/2 (CKS = "1")

≠ 16 ≠

CXP86541/86549/86561

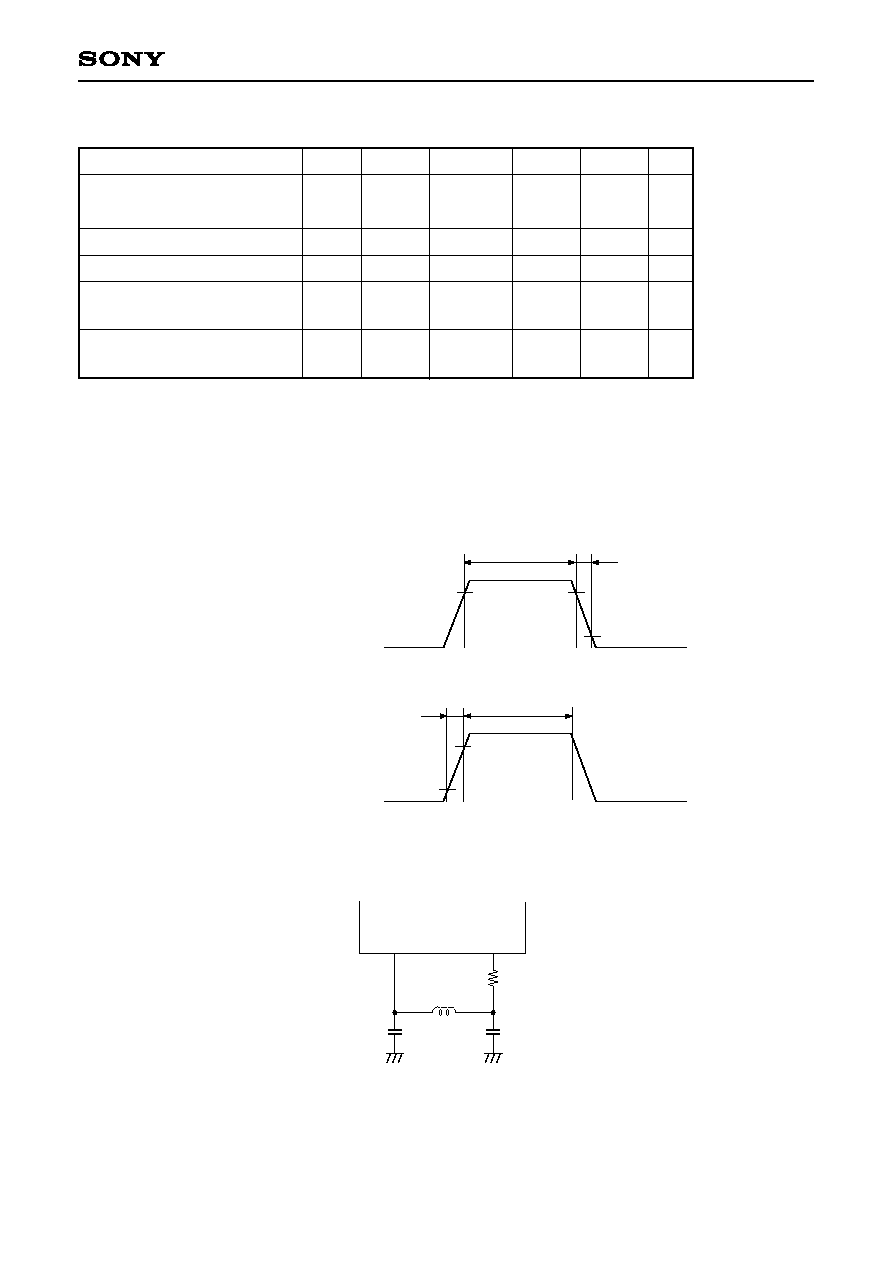

External interruption High,

Low level widths

Reset input Low level width

INT0

INT1

INT2

RST

1

32/fc

µs

µs

Item

Symbol

Pins

Conditions

Min.

Max.

Unit

t

IH

t

IL

t

RSL

(4) Interruption, reset input (Ta = ≠20 to +75∞C, V

DD

= 4.5 to 5.5V, Vss = 0V reference)

0.2V

DD

0.8V

DD

t

IH

t

IL

INT0

INT1

INT2

(falling edge)

Fig. 6. Interruption input timing

t

RSL

0.2V

DD

RST

Fig. 7. RST input timing

≠ 17 ≠

CXP86541/86549/86561

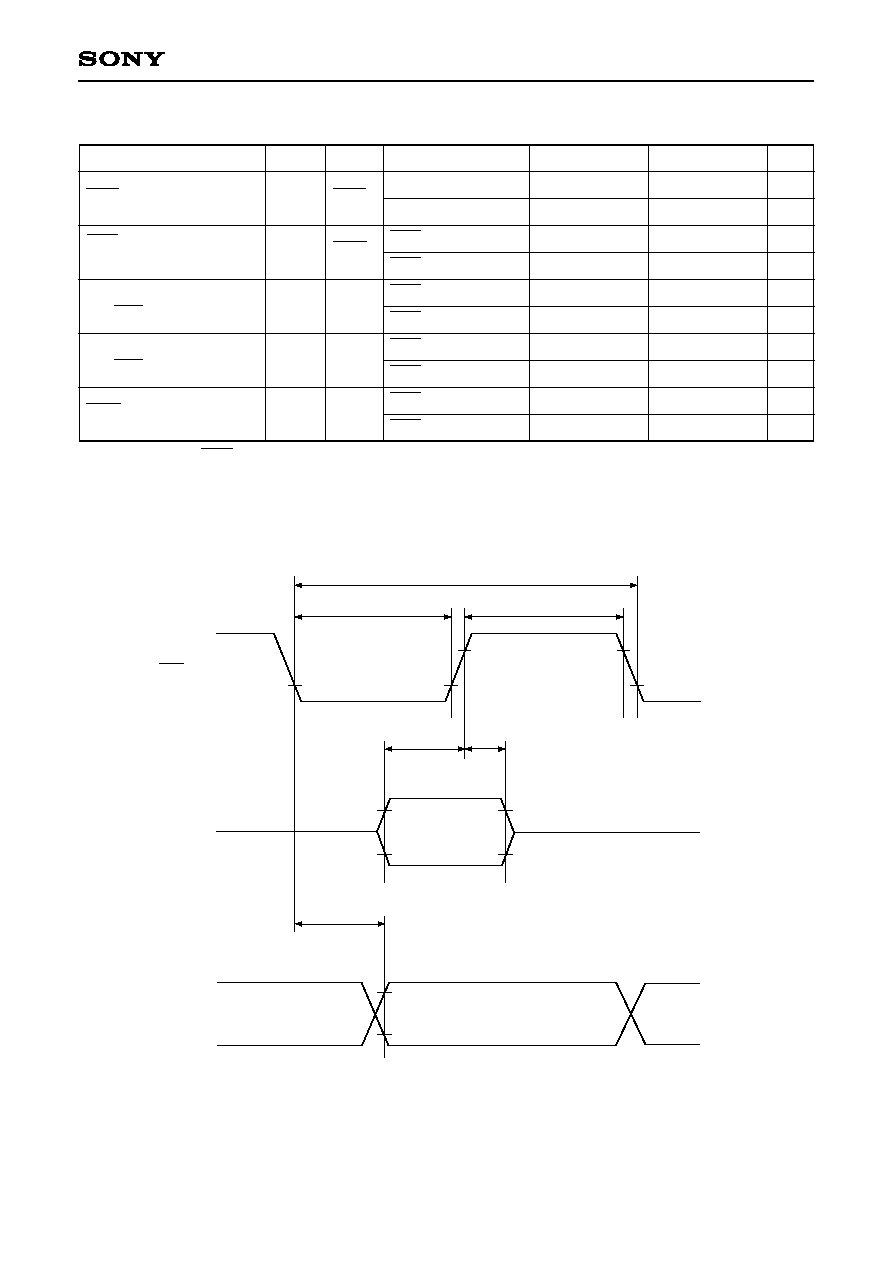

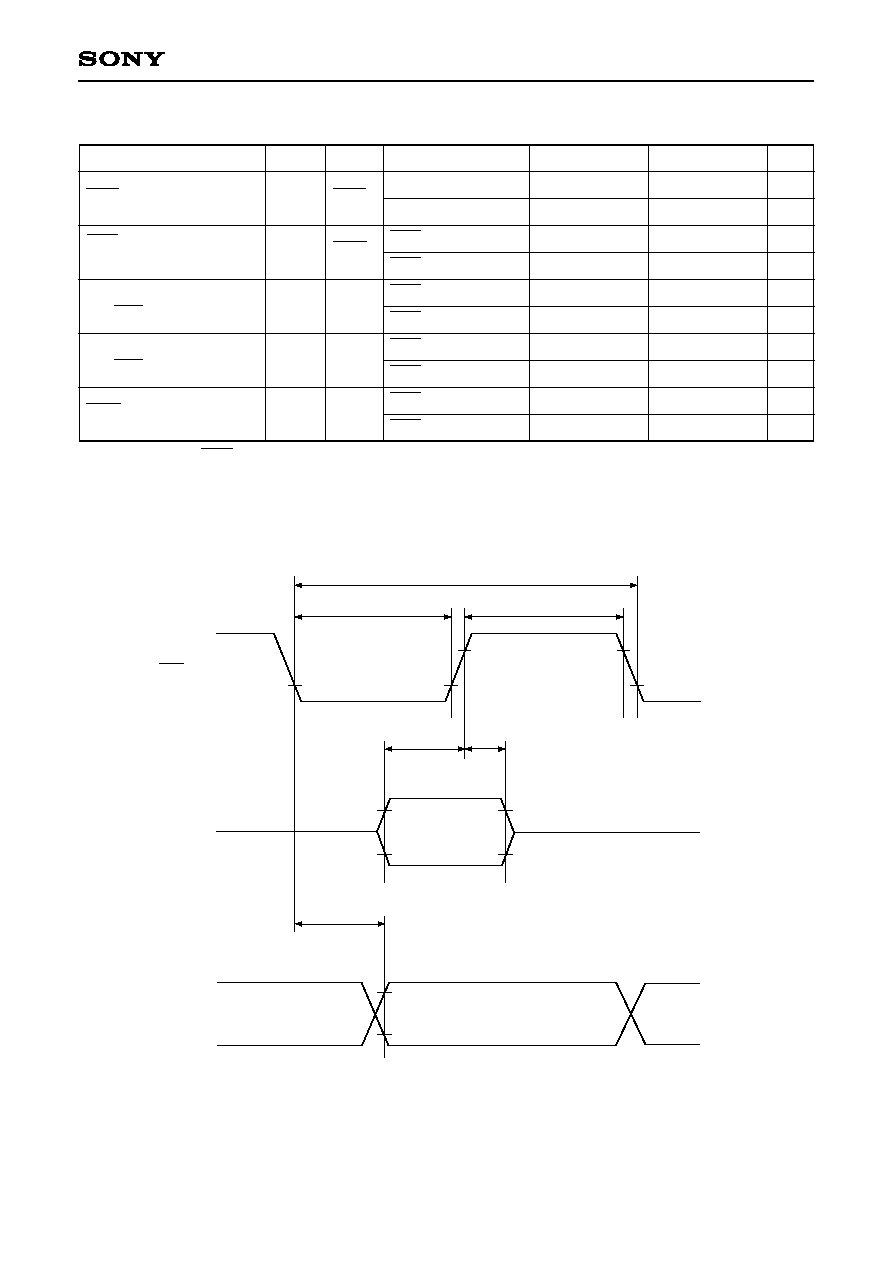

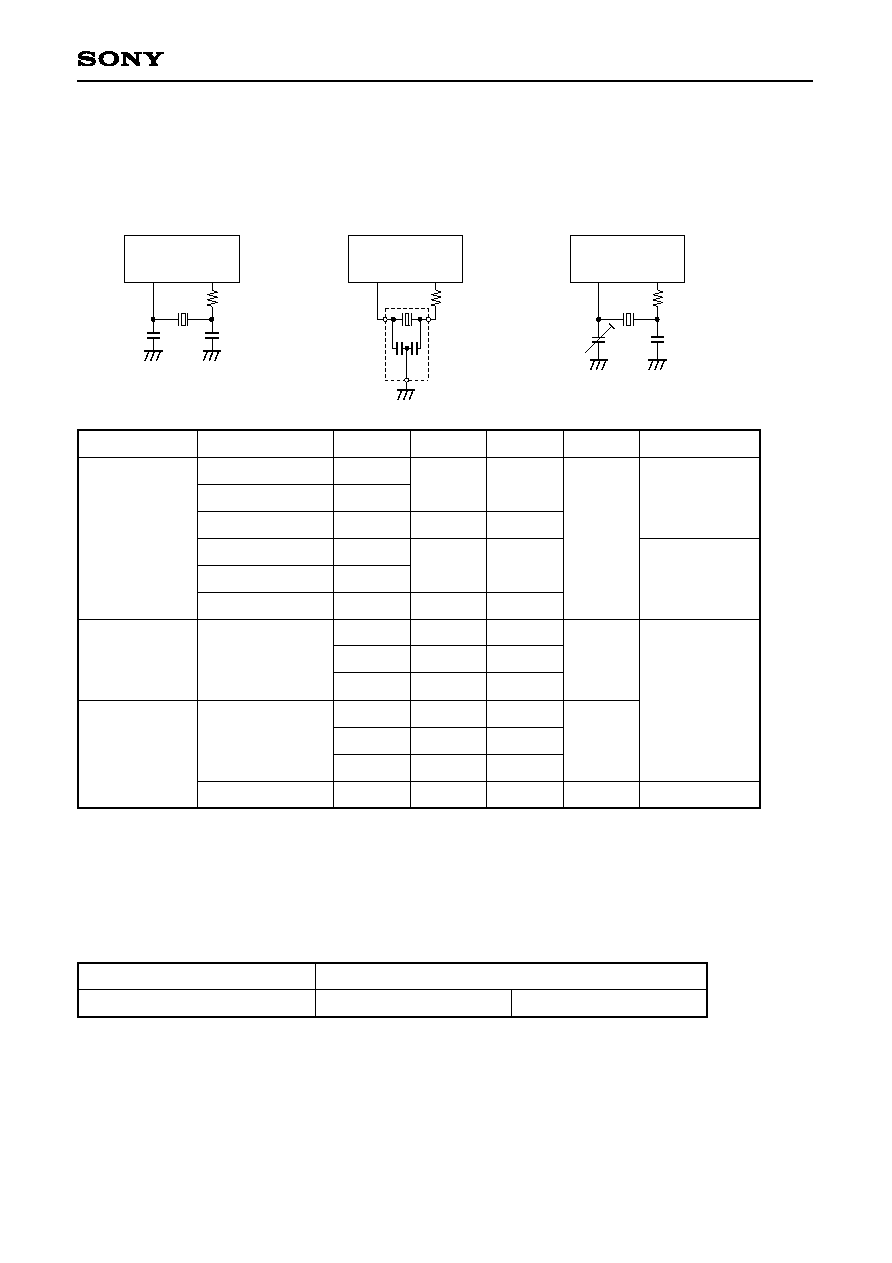

(5) I

2

C bus timing

(Ta = ≠20 to +75∞C, V

DD

= 4.5 to 5.5V, Vss = 0V reference)

Item

SCL clock frequency

Bus-free time before starting transfer

Hold time for starting transfer

Clock Low level width

Clock High level width

Setup time for repeated transfers

Data hold time

Data setup time

SDA, SCL rise time

SDA, SCL fall time

Setup time for transfer completion

f

SLC

t

BUF

t

HD; STA

t

LOW

t

HIGH

t

SU; STA

t

HD; DAT

t

SU; DAT

t

R

t

F

t

SU; STO

SCL

SDA, SCL

SDA, SCL

SCL

SCL

SDA, SCL

SDA, SCL

SDA, SCL

SDA, SCL

SDA, SCL

SDA, SCL

0

4.7

4.0

4.7

4.0

4.7

0

1

250

4.7

100

1

300

kHz

µs

µs

µs

µs

µs

µs

ns

µs

ns

µs

Symbol

Pins

Conditions

Min.

Max.

Unit

1

The data hold time should be 300ns or more because the SCL rise time (300ns Max.) is not included in it.

Fig. 8. I

2

C bus transfer timing

P

St

t

SU

;

STO

t

SU

;

STA

t

HD

;

STA

t

SU

;

DAT

t

HIGH

t

HD

;

DAT

t

F

t

R

t

LOW

t

HD

;

STA

S

P

t

BUF

SDA

SCL

Fig. 9. I

2

C bus device recommended circuit

I

2

C bus

device

I

2

C bus

device

R

S

R

S

R

S

R

S

R

P

R

P

SDA0

(or SDA1)

SCL0

(or SCL1)

∑ A pull-up resistor (Rp) must be connected to SDA0 (or SDA1) and SCL0 (or SCL1).

∑ The SDA0 (or SDA1) and SCL0 (or SCL1) series resistance can be used to reduce the spike noise caused

by CRT flashover.

≠ 18 ≠

CXP86541/86549/86561

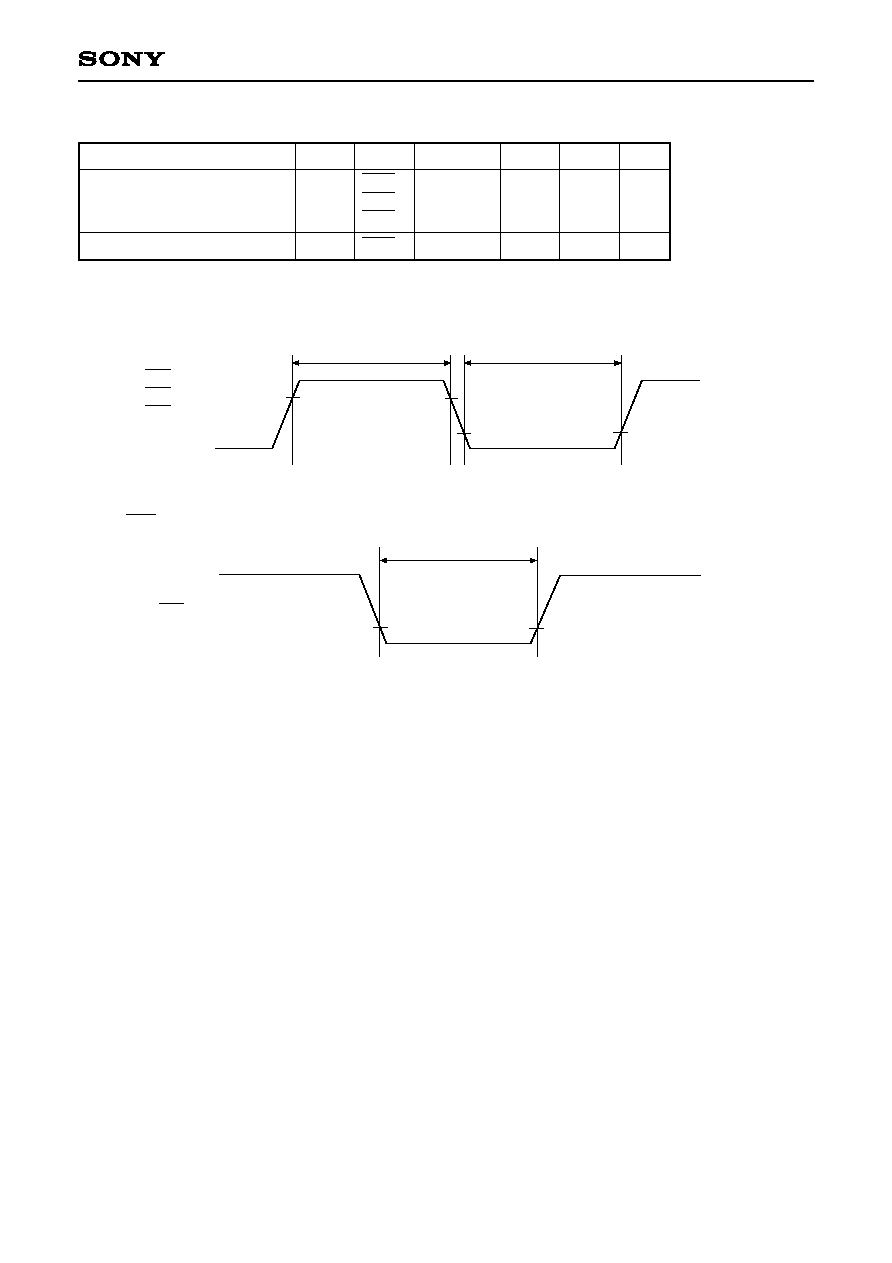

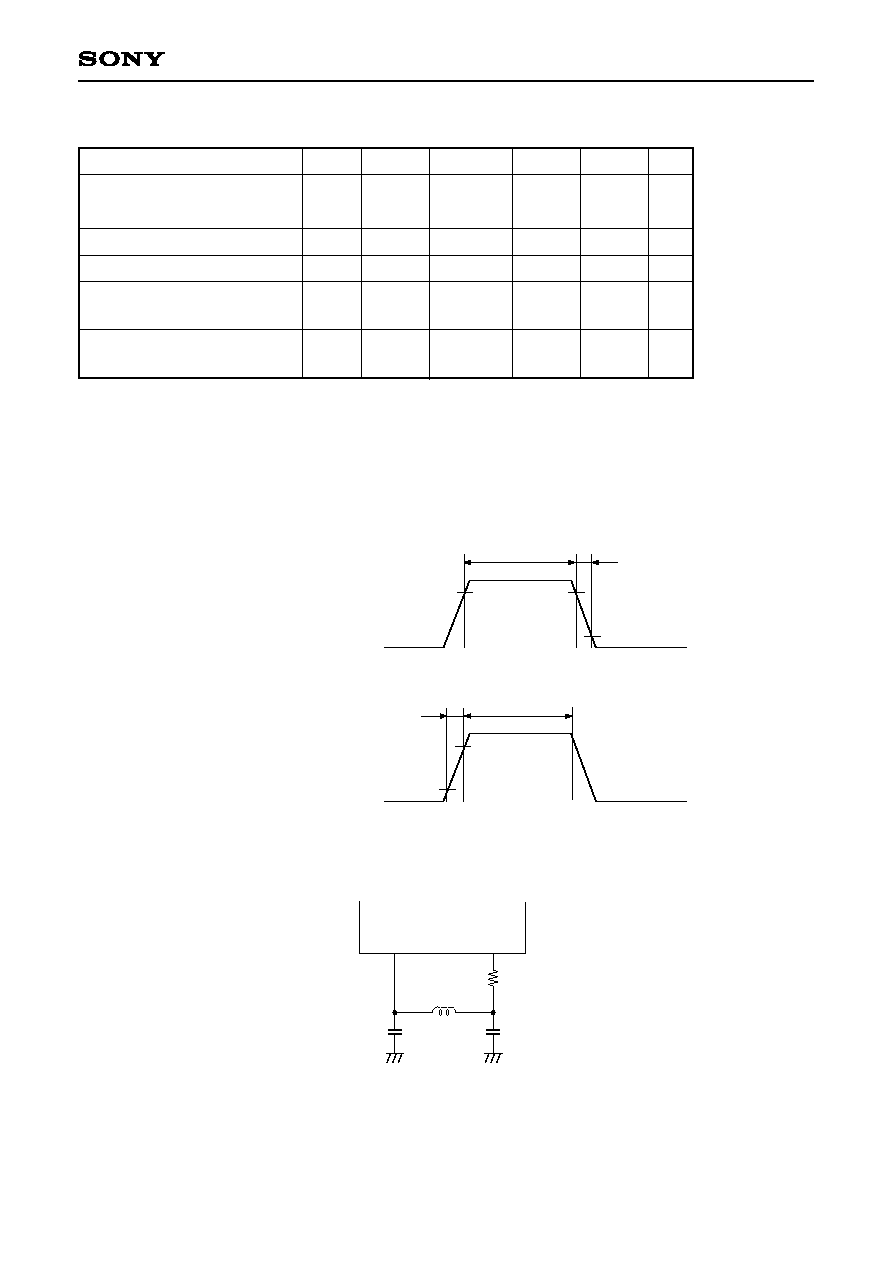

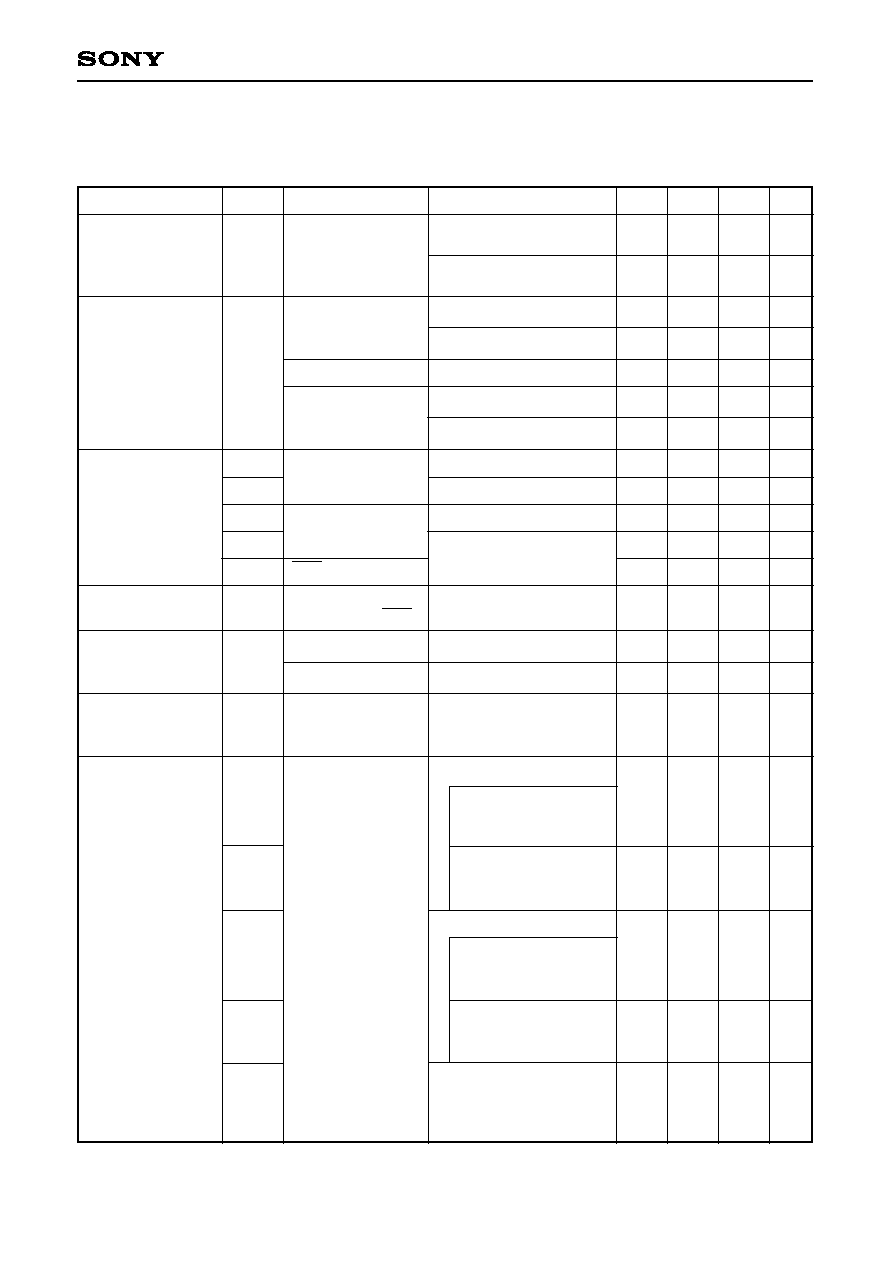

(6) OSD timing

(Ta = ≠20 to +75∞C, V

DD

= 4.5 to 5.5V, Vss = 0V reference)

Item

OSD clock frequency

HSYNC pulse width

VSYNC pulse width

HSYNC afterwrite rise and fall

times

VSYNC beforewrite rise and fall

times

f

OSC

t

HWD

t

VWD

t

HCG

t

VCG

EXLC

XLC

HSYNC

VSYNC

HSYNC

VSYNC

Fig. 11

Fig. 10

Fig. 10

Fig. 10

Fig. 10

4

2

1

28

1

200

1.0

MHz

µs

H

2

ns

µs

Symbol

Pins

Conditions

Unit

Min.

Max

Fig. 10. OSD timing

0.8V

DD

0.2V

DD

t

HCG

t

HWD

HSYNC

For OSD I/O polarity register

(OPOL: 01FE

h

)

bit 7 at "0"

0.8V

DD

0.2V

DD

t

VCG

VSYNC

For OSD I/O polarity register

(OPOL: 01FE

h

)

bit 6 at "0"

t

VWD

Fig. 11. LC oscillation circuit connection

L

C

2

C

1

EXLC

XLC

R

1

1

The series resistor for XLC is used to reduce the frequency of occurrence of the undesired radiation.

1

The maximum value of fosc is specified with the following equation.

fosc [max]

fc

◊

1.9

2

H indicates 1HSYNC period.

≠ 19 ≠

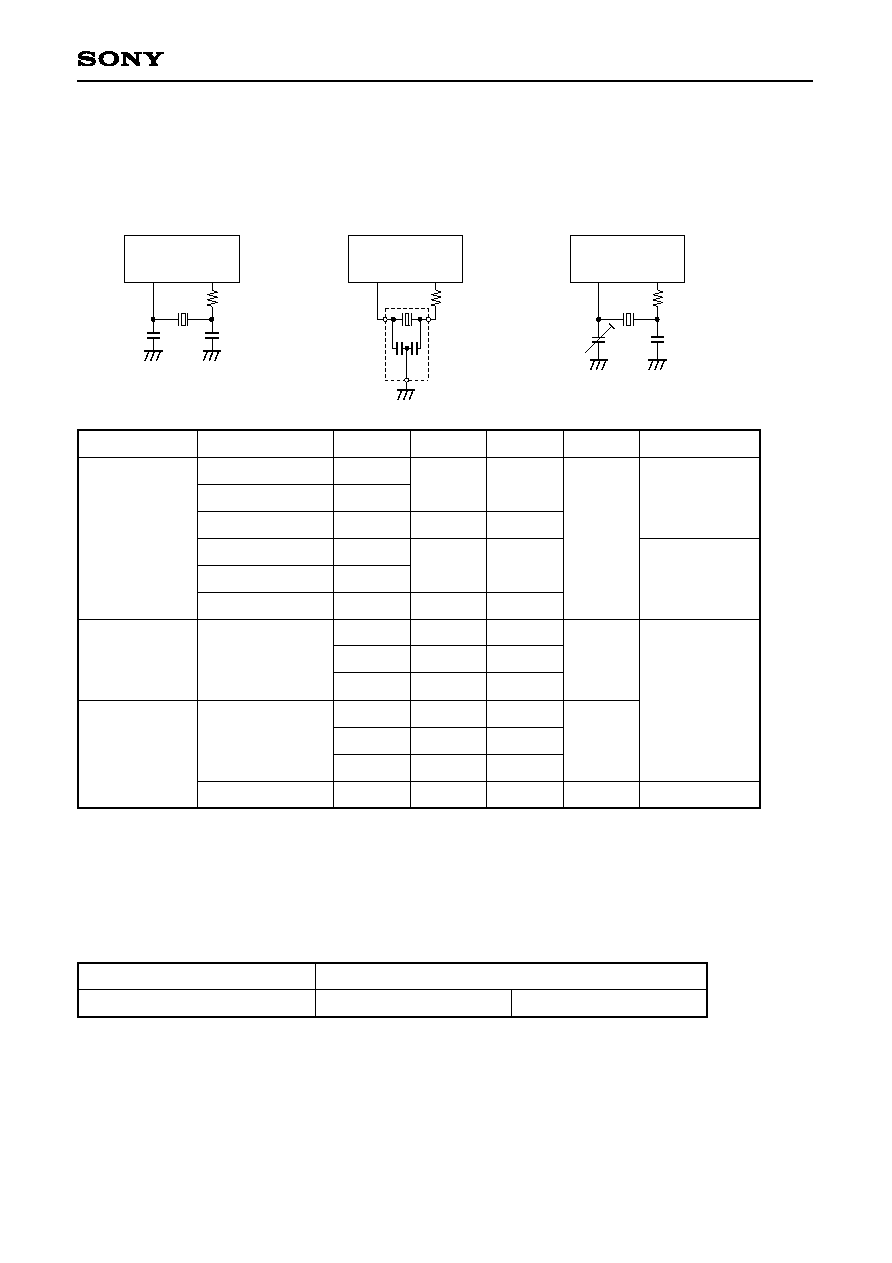

CXP86541/86549/86561

Reset pin pull-up resistor

Non-existent

Existent

Item

Content

Mask Option Table

Appendix

Fig. 12. Recommended oscillation circuit

C

2

Rd

EXTAL

XTAL

C

1

(i) Main clock

TEX

TX

C

1

C

2

Rd

(iii) Sub clock

Rd

EXTAL

XTAL

C

1

C

2

(ii) Main clock

Manufacture

RIVER

ELETEC CO.,

LTD.

MURATA MFG

CO., LTD.

CSA10.0MTZ

CSA12.0MTZ

CSA16.00MXZ040

CST10.0MTW

CST12.0MTW

CST16.00MXW0C1

KINSEKI LTD.

Model

HC-49/U03

HC-49/U (-S)

P3

fc (MHz)

10.0

12.0

16.0

10.0

12.0

16.0

8.0

12.0

16.0

8.0

12.0

16.0

30

5

30

5

18

12

10

10

5

Open

30

30

5

30

5

18

12

10

10

5

Open

33

0

1

330

1

0

1

120k

32.768kHz

(iii)

C

1

(pF)

C

2

(pF)

Rd (

)

Circuit example

(i)

Models with an astarisk have the built-in ground capacitance (C

1

, C

2

).

1

The series resistor for XTAL (Rd = 500

or less) can reduce the effect of the noise caused by the

electrostatic discharge.

(i)

(ii)

≠ 20 ≠

CXP86541/86549/86561

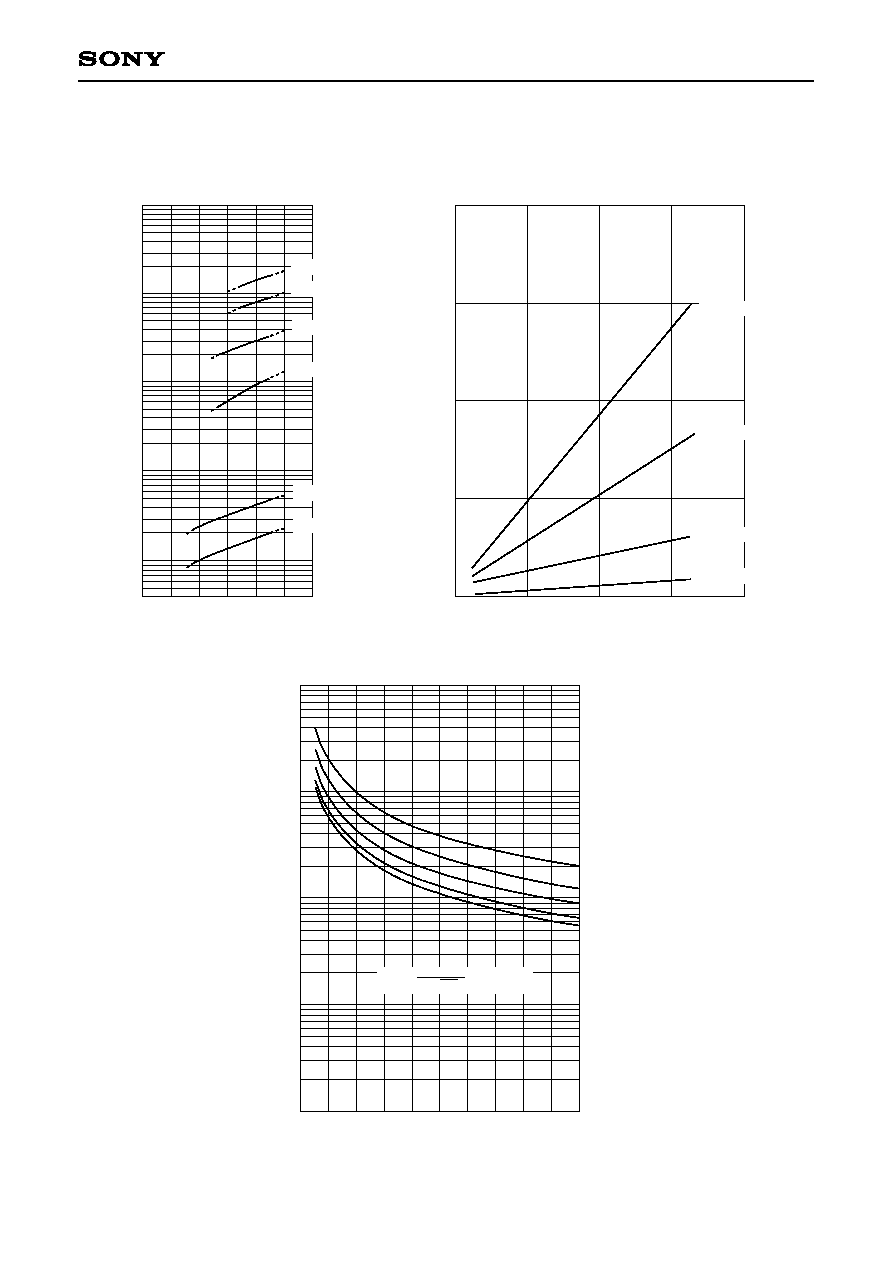

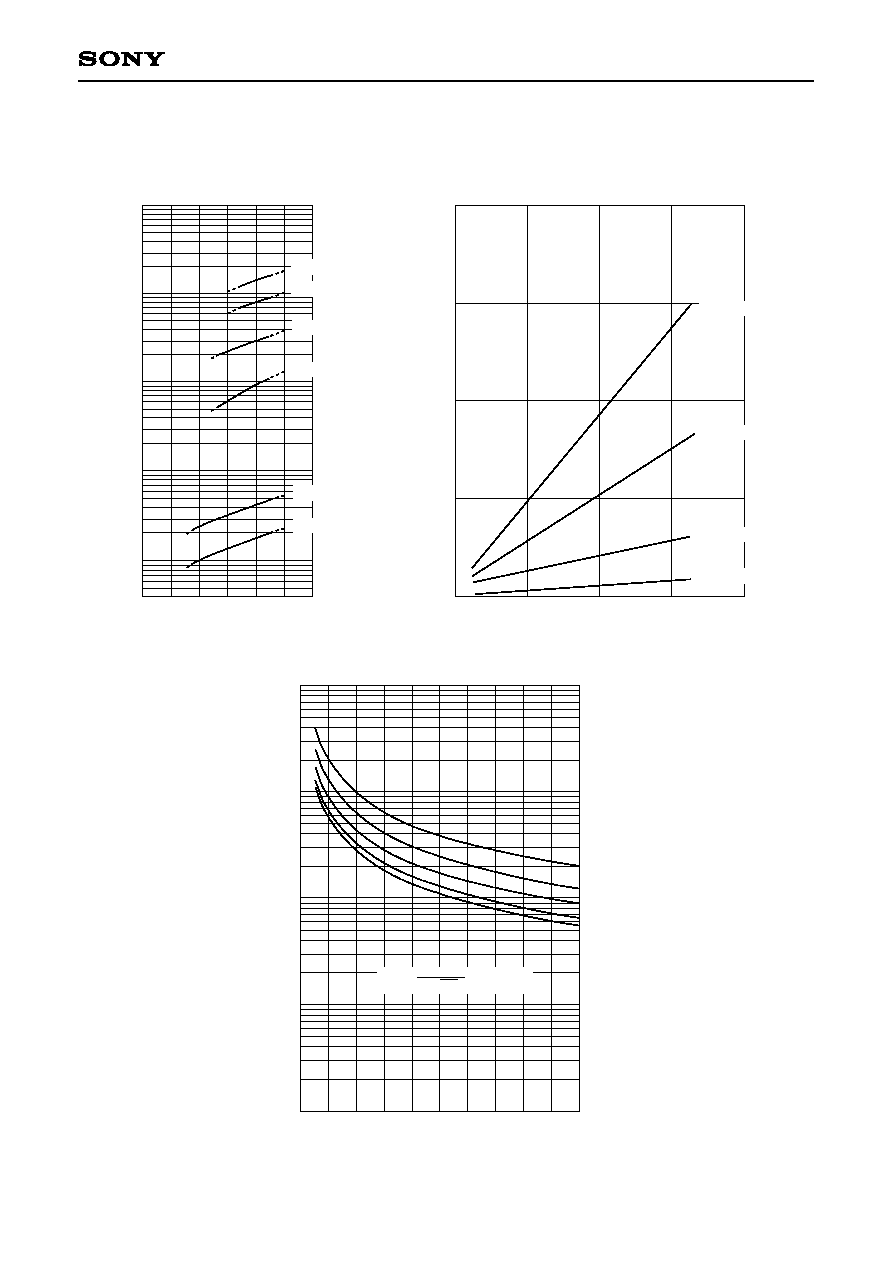

Fig. 13. Characteristic curve

15

10

5

3

4

5

6

0.1

1

7

2

0.01

10

100

10

0

5

15

100

10

20MHz

24MHz

30MHz

50

100

90

80

70

60

40

30

20

10

0

1

0.1

0.01

28MHz

16MHz

0

1

I

DD

vs. V

DD

(fc = 16MHz, Ta = 25∞C, Typical)

Frequency [MHz]

I

D

D

≠

S

u

p

p

l

y

c

u

r

r

e

n

t

[

m

A

]

I

DD

vs. fc

(V

DD

= 5V, Ta = 25∞C, Typical)

V

DD

≠ Supply voltage [mA]

I

D

D

≠

S

u

p

p

l

y

c

u

r

r

e

n

t

[

m

A

]

1/16 dividing mode

1/4 dividing mode

Sleep mode

32kHz sleep mode

32kHz operation mode

1/2 dividing mode

1/2 dividing mode

1/4 dividing mode

1/16 dividing mode

Sleep mode

L

≠

I

n

d

u

c

t

a

n

c

e

[

µ

H

]

Parameter curve for OSD oscillator L vs. C

(Analytically calculated value)

C

1

, C

2

≠ Capacitance [pF]

f

OSC

=

2

LC

1

C = C

1

//C

2

≠ 21 ≠

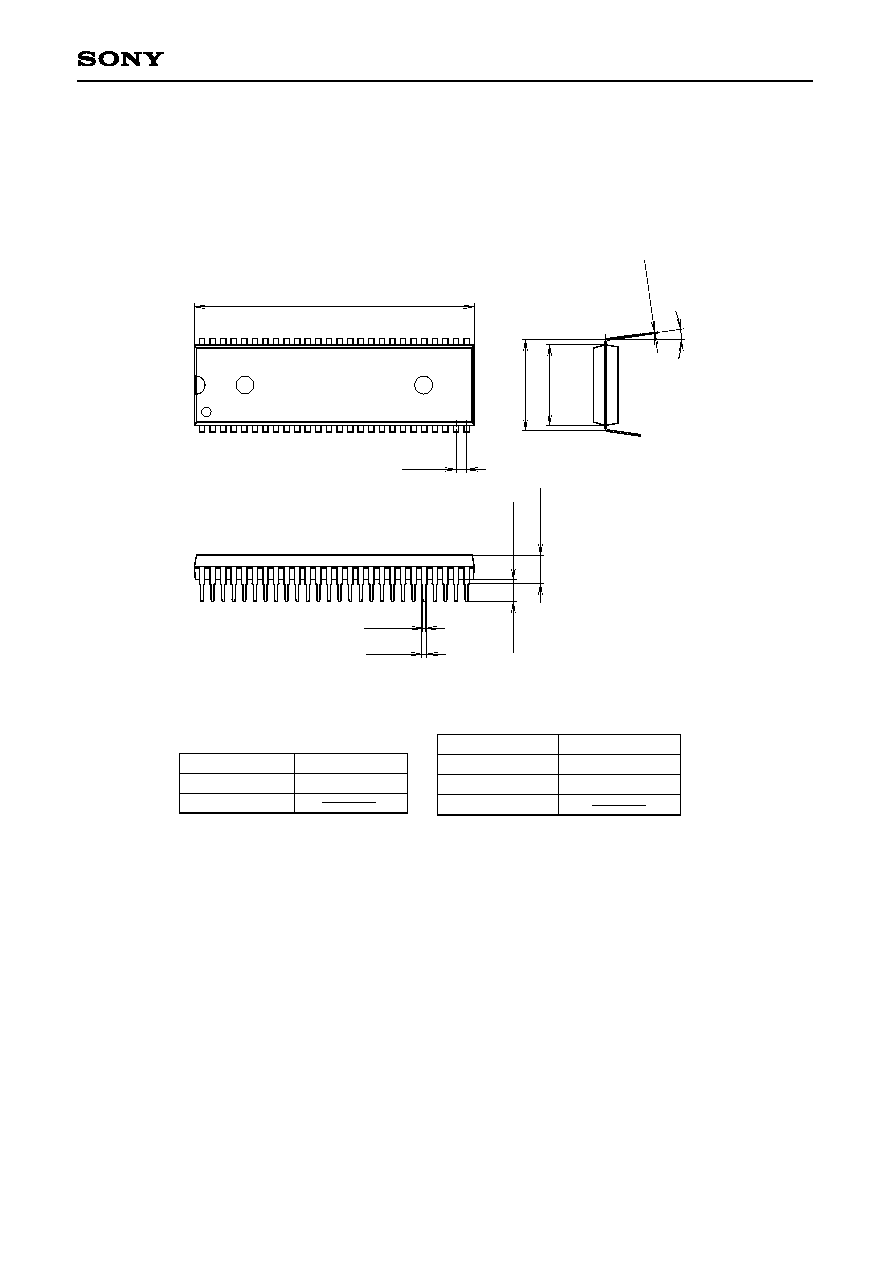

CXP86541/86549/86561

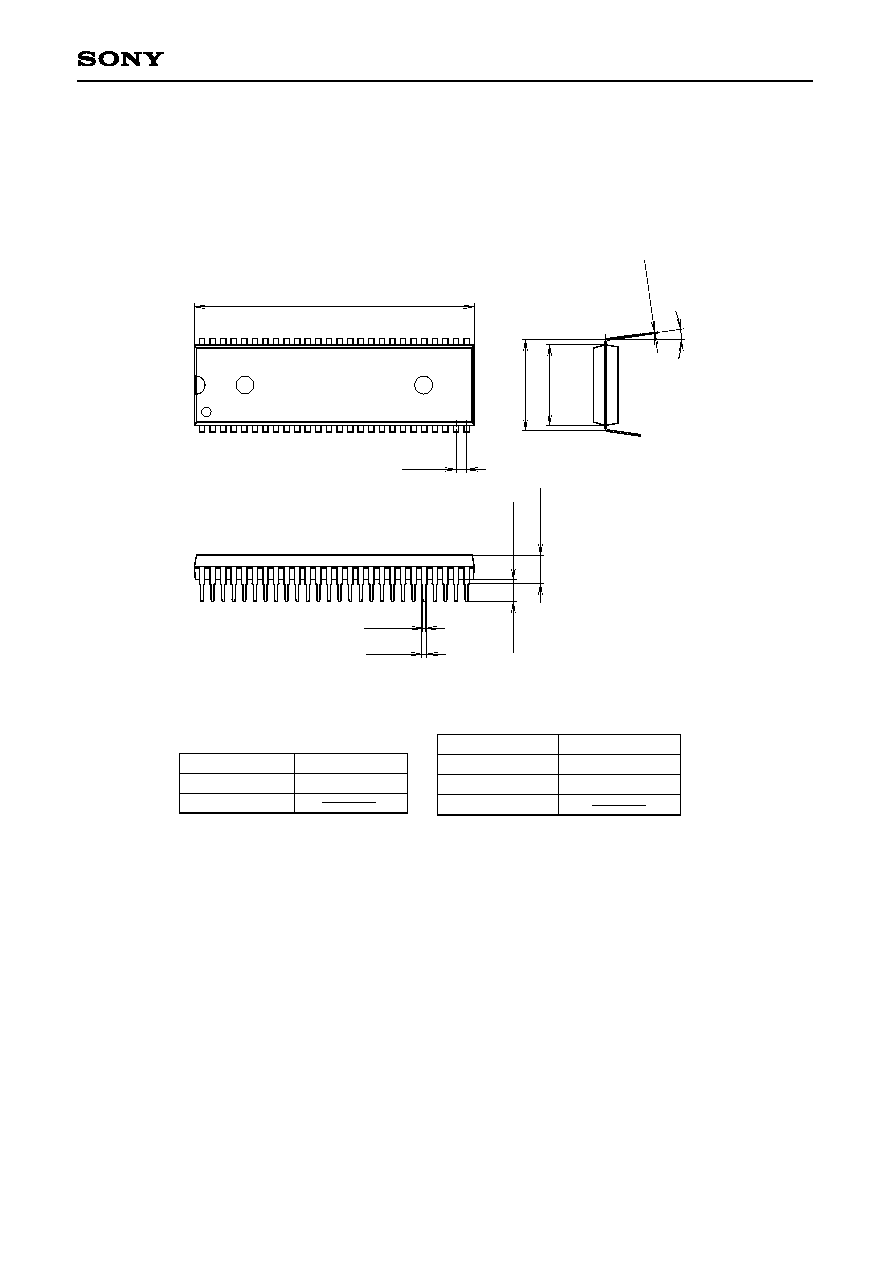

Package Outline

Unit: mm

PACKAGE STRUCTURE

PACKAGE MATERIAL

LEAD TREATMENT

LEAD MATERIAL

PACKAGE WEIGHT

EPOXY RESIN

SOLDER PLATING

COPPER

47.0 ≠ 0.1

+ 0.4

1.778

1

5

.

2

4

1

3

.

5

≠

0

.

1

+

0

.

3

0∞ to 15∞

0

.2

5

≠

0

.0

5

+

0

.1

0.5 ± 0.1

0.9 ≠ 0.05

+ 0.1

2

.

8

M

I

N

0

.

5

1

M

I

N

5

.

0

M

I

N

SDIP-52P-01

SDIP052-P-0600-A

52PIN SDIP (PLASTIC) 600mil

52

1

26

27

SONY CODE

EIAJ CODE

JEDEC CODE