September 2003

This document specifies SPANSION

memory products that are now offered by both Advanced Micro Devices and

Fujitsu. Although the document is marked with the name of the company that originally developed the specification,

these products will be offered to customers of both AMD and Fujitsu.

Continuity of Specifications

There is no change to this datasheet as a result of offering the device as a SPANSION

product. Future routine

revisions will occur when appropriate, and changes will be noted in a revision summary.

Continuity of Ordering Part Numbers

AMD and Fujitsu continue to support existing part numbers beginning with "Am" and "MBM". To order these

products, please use only the Ordering Part Numbers listed in this document.

For More Information

Please contact your local AMD or Fujitsu sales office for additional information about SPANSION

memory

solutions.

TM

TM

TM

SPANSION MCP

Data Sheet

TM

DS05-50230-2E

FUJITSU SEMICONDUCTOR

DATA SHEET

Stacked MCP (Multi-Chip Package) FLASH MEMORY & SRAM

CMOS

32M (

◊

16) FLASH MEMORY &

4M (

◊

16) STATIC RAM

MB84VD22184FM

-70

/MB84VD22194FM

-70

s

FEATURES

∑ Power Supply Voltage of 2.7 V to 3.1 V

∑ High Performance

70 ns maximum access time (Flash)

70 ns maximum access time (SRAM)

∑ Operating Temperature

≠30

∞

C to +85

∞

C

∑ Package 56-ball FBGA

(Continued)

s

PRODUCT LINE UP

Note: Both V

CC

f and V

CC

s must be in recommended operation range when either part is being accessed.

s

PACKAGE

Part No.

VD22184FM / VD22194FM

Supply Voltage(V)

V

CC

f= 3.0V

V

CC

s= 3.0V

Max Address Access Time (ns)

70

70

Max CE Access Time (ns)

70

70

Max OE Access Time (ns)

30

35

56-ball plastic FBGA

(BGA-56P-M03)

+0.1 V

≠0.3 V

+0.1 V

≠0.3 V

MB84VD22184FM/VD22194FM

-70

2

(Continued)

-- FLASH MEMORY

∑ Simultaneous Read/Write Operations (Dual Bank)

Bank 1 : 8 Mbit (8 KB

◊

8 and 64 KB

◊

15)

Bank 2 : 24 Mbit (64 KB

◊

48)

Host system can program or erase in one bank, and then read immediately and simultaneously from the other

bank with zero latency between read and write operations.

Read-while-erase

Read-while-program

∑ Minimum 100,000 Write/Erase Cycles

∑ Sector Erase Architecture

Eight 4K word and sixty-three 32K word sectors in word mode

Any combination of sectors can be concurrently erased. Also supports full chip erase.

∑ Boot Code Sector Architecture

MB84VD22184: Top sector

MB84VD22194: Bottom sector

∑ Embedded Erase

TM

* Algorithms

Automatically pre-programs and erases the chip or any sector

∑ Embedded Program

TM

* Algorithms

Automatically writes and verifies data at specified address

∑ Data Polling and Toggle Bit Feature for Detection of Program or Erase Cycle Completion

∑ Ready-Busy Output (RY/BY)

Hardware method for detection of program or erase cycle completion

∑ Automatic Sleep Mode

When addresses remain stable, automatically switch themselves to low power mode.

∑ Low V

CC

f Write Inhibit

2.5 V

∑ HiddenROM Region

256 byte of HiddenROM, accessible through a new "HiddenROM Enable" command sequence

Factory serialized and protected to provide a secure electronic serial number (ESN)

∑ WP/ACC Input Pin

At V

IL

, allows protection of "outermost" 2

◊

8 bytes on boot sectors, regardless of sector protection/unprotection

status.

At V

IH

, allows removal of boot sector protection

At V

ACC

, increases program performance

∑ Erase Suspend/Resume

Suspends the erase operation to allow a read in another sector within the same device

∑ Please refer to "MBM29DL34TF/BF" Datasheet in Detailed Function

-- SRAM

∑ Power Dissipation

Operating : 40 mA Max

Standby : 10

µ

A Max

∑ Power Down Features using CE1s and CE2s

∑ Data Retention Supply Voltage: 1.5 V to 3.1 V

∑ CE1s and CE2s Chip Select

∑ Byte Data Control: LB (DQ

7

to DQ

0

), UB (DQ

15

to DQ

8

)

*: Embedded Erase

TM

and Embedded Program

TM

are trademarks of Advanced Micro Devices, Inc.

MB84VD22184FM/VD22194FM

-70

3

s

PIN ASSIGNMENT

(BGA-56P-M03)

(Top View)

Marking side

C7

A

13

C6

A

9

C5

A20

C4

RY/BY

C3

A

18

C2

A

5

C1

A

2

C8

N.C.

E7

N.C.

E6

DQ

6

E3

DQ

1

E2

V

SS

E1

A

0

E8

A

16

F7

DQ

15

F6

DQ

13

F5

DQ

4

F4

DQ

3

F3

DQ

9

F2

OE

F1

CEf

F8

N.C.

D7

A

14

D6

A

10

D3

A

17

D2

A

4

D1

A

1

D8

N.C.

G7

DQ

7

G6

DQ

12

G5

Vccs

G4

Vccf

G3

DQ

10

G2

DQ

0

G1

CE1s

G8

Vss

H7

DQ

14

H6

DQ

5

H5

N.C.

H4

DQ

11

H3

DQ

2

H2

DQ

8

B7

A

12

B6

A

19

B5

CE2s

B4

RESET

B3

UB

B2

A

6

B1

A

3

B8

A

15

A7

A

11

A6

A

8

A5

WE

A4

WP/ACC

A3

LB

A2

A

7

MB84VD22184FM/VD22194FM

-70

4

s

PIN DESCRIPTION

Pin Name

Function

Input/Output

A

17

to A

0

Address Inputs (Common)

I

A

20

to A

18

Address Inputs (Flash)

I

DQ

15

to DQ

0

Data Inputs / Outputs (Common)

I/O

CEf

Chip Enable (Flash)

I

CE1s

Chip Enable (SRAM)

I

CE2s

Chip Enable (SRAM)

I

OE

Output Enable (Common)

I

WE

Write Enable (Common)

I

RY/BY

Ready/Busy Outputs (Flash) Open Drain

Output

O

UB

Upper Byte Control (SRAM)

I

LB

Lower Byte

Control (SRAM)

I

RESET

Hardware Reset Pin / Sector Protection

Unlock (Flash)

I

WP/ACC

Write Protect / Acceleration (Flash)

I

N.C.

No Internal Connection

--

V

SS

Device Ground (Common)

Power

V

CC

f

Device Power Supply (Flash)

Power

V

CC

s

Device Power Supply (SRAM)

Power

MB84VD22184FM/VD22194FM

-70

5

s

BLOCK DIAGRAM

V

SS

V

CC

s

32 M bit

RESET

Flash Memory

WE

4 M bit

Static RAM

CEf

A

20

to A

0

OE

CE1s

V

SS

V

CC

f

A

20

to A

0

A

17

to A

0

DQ

15

to DQ

0

RY/BY

LB

UB

WP/ACC

CE2s

DQ

15

to DQ

0

DQ

15

to DQ

0

MB84VD22184FM/VD22194FM

-70

6

s

DEVICE BUS OPERATIONS

∑ User Bus Operations

Legend: L = V

IL

, H = V

IH

, X = V

IL

or V

IH

. See DC Characteristics for voltage levels.

*1 : Other operations except for indicated this column are inhibited.

*2 : WE can be V

IL

if OE is V

IL

, OE at V

IH

initiates the write operations.

*3 : Do not apply CEf = V

IL

, CE1s = V

IL

and CE2s = V

IH

at a time.

*4 : It is also used for the extended sector group protections.

*5 : WP/ACC = V

IL

; protection of boot sectors.

WP/ACC = V

IH

; removal of boot sectors protection.

WP/ACC = V

ACC

(9V)

; Program time will reduce by 40%.

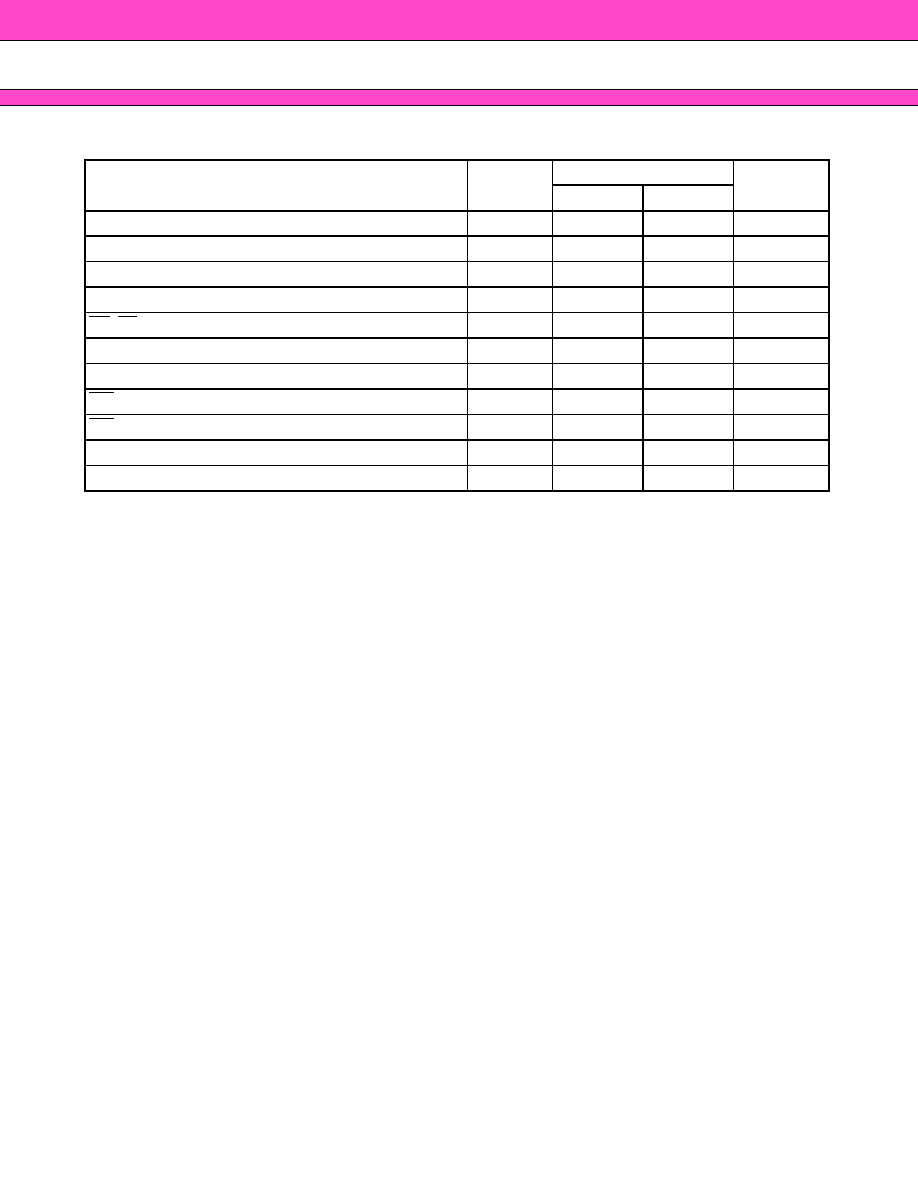

Operation *

1,

*

3

CEf CE1s CE2s OE

WE

LB

UB

DQ

7

to DQ

0

DQ

15

to DQ

8

RESET

WP/

ACC

*

5

Full Standby

H

H

X

X

X

X

X

High-Z

High-Z

H

X

X

L

Output Disable

H

L

H

H

H

X

X

High-Z

High-Z

H

X

X

X

H

H

High-Z

High-Z

L

H

X

H

H

X

X

High-Z

High-Z

X

L

Read from Flash *

2

L

H

X

L

H

X

X

D

OUT

D

OUT

H

X

X

L

Write to Flash

L

H

X

H

L

X

X

D

IN

D

IN

H

X

X

L

Read from SRAM

H

L

H

L

H

L

L

D

OUT

D

OUT

H

X

H

L

High-Z

D

OUT

L

H

D

OUT

High-Z

Write to SRAM

H

L

H

X

L

L

L

D

IN

D

IN

H

X

H

L

High-Z

D

IN

L

H

D

IN

High-Z

Temporary Sector

Group Unprotection*

4

X

X

X

X

X

X

X

X

X

V

ID

X

Flash Hardware Reset

X

H

X

X

X

X

X

High-Z

High-Z

L

X

X

L

Boot Block Sector Write

Protection

X

X

X

X

X

X

X

X

X

X

L

MB84VD22184FM/VD22194FM

-70

7

s

ABSOLUTE MAXIMUM RATINGS

*1 : Minimum DC voltage on input or I/O pins is ≠0.3 V. During voltage transitions, input or I/O pins may undershoot

V

SS

to ≠1.0 V for periods of up to 20 ns. Maximum DC voltage on input or I/O pins is V

CC

f+0.3 V or

V

CC

s+0.4 V. During voltage transitions, input or I/O pins may overshoot to V

CC

f+1.0 V or V

CC

s + 1.0 V for periods

of up to 20 ns.

*2 : Minimum DC input voltage on RESET pin is ≠0.5 V. During voltage transitions, RESET pins may undershoot

V

SS

to ≠2.0 V for periods of up to 20 ns. Voltage difference between input and supply voltage (V

IN

-V

CC

f or V

CC

s)

does not exceed

+

9.0 V. Maximum DC input voltage on RESET pins is +13.0 V which may overshoot to

+14.0 V for periods of up to 20 ns.

*3 : Minimum DC input voltage on WP/ACC pin is ≠0.5 V. During voltage transitions, WP/ACC pin may undershoot

Vss to ≠2.0 V for periods of up to 20 ns. Maximum DC input voltage on WP/ACC pin is +10.5 V which may

overshoot to +12.0 V for periods of up to 20 ns, when V

CC

f is applied.

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current,

temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

s

RECOMMENDED OPERATING CONDITIONS

Note: Operating ranges define those limits between which the functionality of the device is guaranteed.

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the

semiconductor device. All of the device's electrical characteristics are warranted when the device is

operated within these ranges.

Always use semiconductor devices within the recommended operating conditions. Operation outside

these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on

the data sheet. Users considering application outside the listed conditions are advised to contact their

FUJITSU representative beforehand.

Parameter

Symbol

Rating

Unit

Min

Max

Storage Temperature

Tstg

≠55

+125

∞C

Ambient Temperature with Power Applied

T

A

≠30

+85

∞C

Voltage with Respect to Ground All pins

except RESET, WP/ACC *

1

V

IN

, V

OUT

≠0.3

V

CC

f + 0.3

V

V

CC

s + 0.4

V

V

CC

f/V

CC

s Supply *

1

V

CC

f, V

CC

s

≠0.3 +3.3

V

RESET *

2

V

IN

≠0.5

+13.0 V

WP/ACC *

3

V

IN

≠0.5

+10.5

V

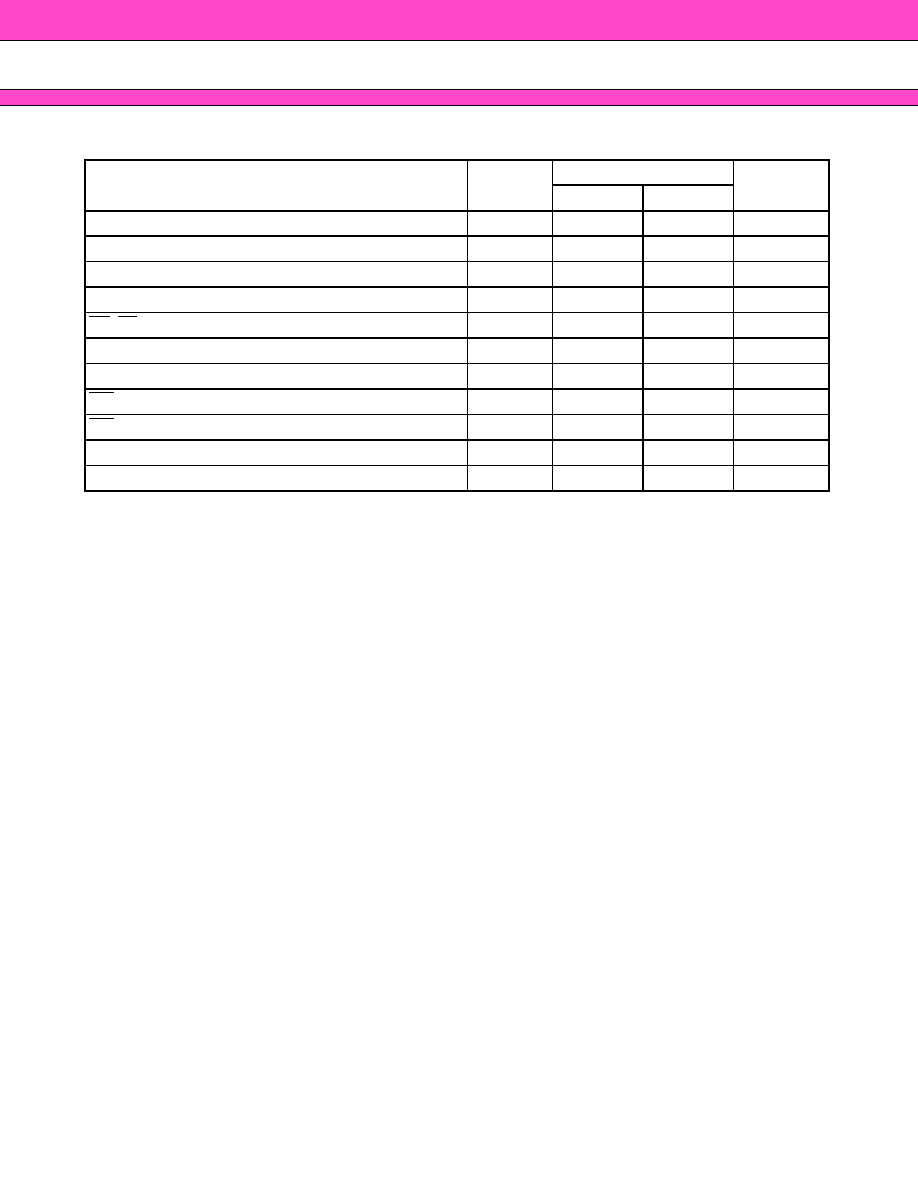

Parameter

Symbol

Value

Unit

Min

Max

Ambient Temperature

T

A

≠30

+85

∞C

V

CC

f/V

CC

s Supply Voltages

Vccf, Vccs

+2.7

+3.1

V

MB84VD22184FM/VD22194FM

-70

8

s

ELECTRICAL CHARACTERISTICS

1.

DC CHARACTERISTICS

(Continued)

Parameter

Symbol

Test Conditions

Value

Unit

Min

Typ

Max

Input Leakage Current

I

LI

V

IN

= V

SS

to V

CC

f, V

CC

s

≠1.0

--

+1.0

µ

A

Output Leakage Current

I

LO

V

OUT

= V

SS

to V

CC

f, V

CC

s

≠1.0

--

+1.0

µ

A

RESET Inputs Leakage

Current

I

LIT

V

CC

f

= V

CC

f Max, V

CC

s

= V

CC

s Max,

RESET = 12.5V

--

--

35

µA

Flash V

CC

Active Current

(Read) *

1

I

CC1

f

CEf = V

IL

,

OE = V

IH

t

CYCLE

= 5 MHz

--

--

18

mA

t

CYCLE

= 1 MHz

--

--

4

mA

Flash V

CC

Active Current

(Program/Erase) *

2

I

CC2

f

CEf = V

IL

, OE = V

IH

--

--

30

mA

Flash V

CC

Active Current

(Read-While-Program) *

5

I

CC3

f

CEf = V

IL

, OE = V

IH

--

--

48

mA

Flash V

CC

Active Current

(Read-While-Erase) *

5

I

CC4

f

CEf = V

IL

, OE = V

IH

--

--

48

mA

Flash V

CC

Active Current

(Erase-Suspend-Program)

I

CC5

f

CEf = V

IL

, OE = V

IH

--

--

35

mA

ACC Input Leakage

Current

I

LIA

V

CC

f

= V

CC

f Max, V

CC

s

= V

CC

s Max,

WP/ACC = V

ACC

Max

--

--

20

mA

SRAM V

CC

Active Current

I

CC1

s

V

CC

s = V

CC

s Max,

CE1s = V

IL

,

CE2s = V

IH

t

CYCLE

=10 MHz

--

--

40

mA

SRAM V

CC

Active Current

I

CC2

s

CE1s = 0.2 V,

CE2s = V

CC

s ≠ 0.2 V

t

CYCLE

= 10 MHz

--

--

40

mA

t

CYCLE

= 1 MHz

--

--

8

mA

Flash V

CC

Standby Current

I

SB1

f

V

CC

f = V

CC

f Max, CEf = V

CC

f ± 0.3 V

RESET = V

CC

f ± 0.3 V,

WP/ACC = V

CC

f± 0.3 V

--

--

5

µ

A

Flash V

CC

Standby Current

(RESET)

I

SB2

f

V

CC

f = V

CC

f Max, RESET = V

SS

± 0.3 V,

WP/ACC = V

CC

f± 0.3 V

--

--

5

µ

A

Flash V

CC

Current

(Automatic Sleep Mode) *

3

I

SB3

f

V

CC

f = V

CC

f Max, CEf = V

SS

± 0.3 V

RESET = V

CC

f ± 0.3 V,

WP/ACC = V

CC

f± 0.3 V

V

IN

= V

CC

f± 0.3 V or V

SS

± 0.3 V

--

--

5

µ

A

SRAM V

CC

Standby Current

I

SB1

s

CE1s > V

CC

s ≠ 0.2 V, CE2s > V

CC

s ≠ 0.2 V

LB = UB > V

CC

s≠0.2 V or < 0.2V

--

--

10

µ

A

SRAM V

CC

Standby Current

I

SB2

s

CE1s > V

CC

s ≠ 0.2 V or < 0.2V,

CE2s < 0.2 V

LB = UB > V

CC

s≠0.2 V or < 0.2V

--

--

10

µ

A

MB84VD22184FM/VD22194FM

-70

9

(Continued)

*1 : The I

CC

current listed includes both the DC operating current and the frequency dependent component.

*2 : I

CC

active while Embedded Algorithm (program or erase) is in progress.

*3 : Automatic sleep mode enables the low power mode when address remain stable for 150 ns.

*4 : Applicable for only V

CC

f applying.

*5 : Embedded Algorithm (program or erase) is in progress. (@5 MHz)

*6 : V

CC

indicates lower of V

CC

f or V

CC

s.

Parameter

Symbol

Test Conditions

Value

Unit

Min

Typ

Max

Input Low Level

V

IL

--

≠0.3

--

0.5

V

Input High Level

V

IH

--

2.2

--

V

CC

+0.3*

6

V

Voltage for Sector

Protection, and Temporary

Sector Unprotection

(RESET) *

4

V

ID

--

11.5

--

12.5

V

Voltage for Program

Acceleration (WP/ACC) *

4

V

ACC

--

8.5

9.0

9.5

V

SRAM Output Low Level

V

OL

V

CC

s = V

CC

s

Min, I

OL

= 0.1 mA

--

--

0.4

V

SRAM Output High Level

V

OH

V

CC

s = V

CC

s

Min, I

OH

= ≠0.1 mA

2.0

--

--

V

Flash Output Low Level

V

OL

V

CC

f = V

CC

f

Min, I

OL

= 4.0 mA

--

--

0.45

V

Flash Output High Level

V

OH

V

CC

f = V

CC

f

Min, I

OH

= ≠0.1 mA

V

CC

s≠0.4

--

--

V

Flash Low V

CC

f Lock-Out

Voltage

V

LKO

--

2.3

--

2.5

V

MB84VD22184FM/VD22194FM

-70

10

2.

AC CHARACTERISTICS

∑ CE Timing

∑ Timing Diagram for alternating SRAM to Flash

∑ Flash Characteristics

Please refer to "

s

32M Flash Memory for MCP".

∑ SRAM Characteristics,

Please refer to "

s

4M SRAM for MCP".

Parameter

Symbol

Test Setup

Value

Unit

JEDEC

Standard

CE Recover Time

--

t

CCR

--

Min

0

ns

CEf

t

CCR

t

CCR

CE1s

CE2s

t

CCR

t

CCR

MB84VD22184FM/VD22194FM

-70

11

s

32 M FLASH MEMORY for MCP

1.

Flexible Sector-erase Architecture on Flash Memory

∑ Eight 4 K words, and sixty three 32 K words.

∑ Individual-sector, multiple-sector, or bulk-erase capability.

100000h

(Top Boot Block)

SA39 : 64KB (32KW)

SA40 : 64KB (32KW)

SA41 : 64KB (32KW)

SA42 : 64KB (32KW)

SA43 : 64KB (32KW)

SA44 : 64KB (32KW)

SA45 : 64KB (32KW)

SA46 : 64KB (32KW)

SA47 : 64KB (32KW)

SA48 : 64KB (32KW)

SA49 : 64KB (32KW)

SA50 : 64KB (32KW)

SA51 : 64KB (32KW)

SA52 : 64KB (32KW)

SA53 : 64KB (32KW)

SA54 : 64KB (32KW)

SA55 : 64KB (32KW)

SA56 : 64KB (32KW)

SA57 : 64KB (32KW)

SA58 : 64KB (32KW)

SA59 : 64KB (32KW)

SA60 : 64KB (32KW)

SA61 : 64KB (32KW)

SA62 : 64KB (32KW)

SA63 : 8KB (4KW)

SA64 : 8KB (4KW)

SA65 : 8KB (4KW)

SA66 : 8KB (4KW)

SA67 : 8KB (4KW)

SA68 : 8KB (4KW)

008000h

000000h

018000h

010000h

028000h

020000h

038000h

030000h

048000h

040000h

058000h

050000h

068000h

060000h

078000h

070000h

088000h

080000h

098000h

090000h

0A8000h

0A0000h

0B8000h

0B0000h

0C8000h

0C0000h

0D8000h

0D0000h

0E8000h

0E0000h

0F8000h

0F0000h

SA0 : 64KB (32KW)

SA1 : 64KB (32KW)

SA2 : 64KB (32KW)

SA3 : 64KB (32KW)

SA4 : 64KB (32KW)

SA5 : 64KB (32KW)

SA6 : 64KB (32KW)

SA7 : 64KB (32KW)

SA8 : 64KB (32KW)

SA9 : 64KB (32KW)

SA10 : 64KB (32KW)

SA11 : 64KB (32KW)

SA12 : 64KB (32KW)

SA13 : 64KB (32KW)

SA14 : 64KB (32KW)

SA15 : 64KB (32KW)

SA16 : 64KB (32KW)

SA17 : 64KB (32KW)

SA18 : 64KB (32KW)

SA19 : 64KB (32KW)

SA20 : 64KB (32KW)

SA21 : 64KB (32KW)

SA22 : 64KB (32KW)

SA23 : 64KB (32KW)

SA24 : 64KB (32KW)

SA25 : 64KB (32KW)

SA26 : 64KB (32KW)

SA27 : 64KB (32KW)

SA28 : 64KB (32KW)

SA29 : 64KB (32KW)

SA30 : 64KB (32KW)

SA31 : 64KB (32KW)

SA32 : 64KB (32KW)

SA33 : 64KB (32KW)

SA34 : 64KB (32KW)

SA35 : 64KB (32KW)

SA36 : 64KB (32KW)

SA37 : 64KB (32KW)

SA38 : 64KB (32KW)

SA69 : 8KB (4KW)

SA70 : 8KB (4KW)

Bank A

108000h

118000h

110000h

128000h

120000h

138000h

130000h

148000h

140000h

158000h

150000h

168000h

160000h

178000h

188000h

180000h

198000h

190000h

1A8000h

1A0000h

1B8000h

1B0000h

1C8000h

1C0000h

1D8000h

1D0000h

1E8000h

1E0000h

1F8000h

1F0000h

1F9000h

1FFFFFh

1FA000h

1FB000h

1FC000h

1FD000h

1FE000h

1FF000h

Bank B

170000h

(Bottom Boot Block)

100000h

SA39 : 64KB (32KW)

SA40 : 64KB (32KW)

SA41 : 64KB (32KW)

SA42 : 64KB (32KW)

SA43 : 64KB (32KW)

SA44 : 64KB (32KW)

SA45 : 64KB (32KW)

SA46 : 64KB (32KW)

SA47 : 64KB (32KW)

SA48 : 64KB (32KW)

SA49 : 64KB (32KW)

SA50 : 64KB (32KW)

SA51 : 64KB (32KW)

SA52 : 64KB (32KW)

SA53 : 64KB (32KW)

SA54 : 64KB (32KW)

SA55 : 64KB (32KW)

SA56 : 64KB (32KW)

SA57 : 64KB (32KW)

SA58 : 64KB (32KW)

SA59 : 64KB (32KW)

SA60 : 64KB (32KW)

SA61 : 64KB (32KW)

SA62 : 64KB (32KW)

SA63 : 64KB (32KW)

SA64 : 64KB (32KW)

SA65 : 64KB (32KW)

SA66 : 64KB (32KW)

SA67 : 64KB (32KW)

SA68 : 64KB (32KW)

008000h

000000h

018000h

010000h

028000h

020000h

038000h

030000h

048000h

040000h

058000h

050000h

068000h

060000h

078000h

070000h

088000h

080000h

098000h

090000h

0A8000h

0A0000h

0B8000h

0B0000h

0C8000h

0C0000h

0D8000h

0D0000h

0E8000h

0E0000h

0F8000h

0F0000h

SA0 : 8KB (4KW)

SA1 : 8KB (4KW)

SA2 : 8KB (4KW)

SA3 : 8KB (4KW)

SA4 : 8KB (4KW)

SA5 : 8KB (4KW)

SA6 : 8KB (4KW)

SA7 : 8KB (4KW)

SA8 : 64KB (32KW)

SA9 : 64KB (32KW)

SA10 : 64KB (32KW)

SA11 : 64KB (32KW)

SA12 : 64KB (32KW)

SA13 : 64KB (32KW)

SA14 : 64KB (32KW)

SA15 : 64KB (32KW)

SA16 : 64KB (32KW)

SA17 : 64KB (32KW)

SA18 : 64KB (32KW)

SA19 : 64KB (32KW)

SA20 : 64KB (32KW)

SA21 : 64KB (32KW)

SA22 : 64KB (32KW)

SA23 : 64KB (32KW)

SA24 : 64KB (32KW)

SA25 : 64KB (32KW)

SA26 : 64KB (32KW)

SA27 : 64KB (32KW)

SA28 : 64KB (32KW)

SA29 : 64KB (32KW)

SA30 : 64KB (32KW)

SA31 : 64KB (32KW)

SA32 : 64KB (32KW)

SA33 : 64KB (32KW)

SA34 : 64KB (32KW)

SA35 : 64KB (32KW)

SA36 : 64KB (32KW)

SA37 : 64KB (32KW)

SA38 : 64KB (32KW)

SA69 : 64KB (32KW)

SA70 : 64KB (32KW)

108000h

118000h

110000h

128000h

120000h

138000h

130000h

148000h

140000h

158000h

150000h

168000h

160000h

178000h

170000h

188000h

180000h

198000h

190000h

1A8000h

1A0000h

1B8000h

1B0000h

1C8000h

1C0000h

1D8000h

1D0000h

1E8000h

1E0000h

1F8000h

1F0000h

001000h

1FFFFFh

002000h

003000h

004000h

005000h

006000h

007000h

Bank A

Bank B

MB84VD22184FM/VD22194FM

-70

12

Sector Address Table (Top Boot Type)

(Continued)

B

a

n

k

Sector

Sector address

Sector size

(Kwords)

Address range

Bank

address

A

20

A

19

A

18

A

17

A

16

A

15

A

14

A

13

A

12

A

11

B

a

n

k

B

SA0

0

0

0

0

0

0

X

X

X

X

32

000000h to 007FFFh

SA1

0

0

0

0

0

1

X

X

X

X

32

008000h to 00FFFFh

SA2

0

0

0

0

1

0

X

X

X

X

32

010000h to 017FFFh

SA3

0

0

0

0

1

1

X

X

X

X

32

018000h to 01FFFFh

SA4

0

0

0

1

0

0

X

X

X

X

32

020000h to 027FFFh

SA5

0

0

0

1

0

1

X

X

X

X

32

028000h to 02FFFFh

SA6

0

0

0

1

1

0

X

X

X

X

32

030000h to 037FFFh

SA7

0

0

0

1

1

1

X

X

X

X

32

038000h to 03FFFFh

SA8

0

0

1

0

0

0

X

X

X

X

32

040000h to 047FFFh

SA9

0

0

1

0

0

1

X

X

X

X

32

048000h to 04FFFFh

SA10

0

0

1

0

1

0

X

X

X

X

32

050000h to 057FFFh

SA11

0

0

1

0

1

1

X

X

X

X

32

058000h to 05FFFFh

SA12

0

0

1

1

0

0

X

X

X

X

32

060000h to 067FFFh

SA13

0

0

1

1

0

1

X

X

X

X

32

068000h to 06FFFFh

SA14

0

0

1

1

1

0

X

X

X

X

32

070000h to 077FFFh

SA15

0

0

1

1

1

1

X

X

X

X

32

078000h to 07FFFFh

SA16

0

1

0

0

0

0

X

X

X

X

32

080000h to 087FFFh

SA17

0

1

0

0

0

1

X

X

X

X

32

088000h to 08FFFFh

SA18

0

1

0

0

1

0

X

X

X

X

32

090000h to 097FFFh

SA19

0

1

0

0

1

1

X

X

X

X

32

098000h to 09FFFFh

SA20

0

1

0

1

0

0

X

X

X

X

32

0A0000h to 0A7FFFh

SA21

0

1

0

1

0

1

X

X

X

X

32

0A8000h to 0AFFFFh

SA22

0

1

0

1

1

0

X

X

X

X

32

0B0000h to 0B7FFFh

SA23

0

1

0

1

1

1

X

X

X

X

32

0B8000h to 0BFFFFh

SA24

0

1

1

0

0

0

X

X

X

X

32

0C0000h to 0C7FFFh

SA25

0

1

1

0

0

1

X

X

X

X

32

0C8000h to 0CFFFFh

SA26

0

1

1

0

1

0

X

X

X

X

32

0D0000h to 0D7FFFh

SA27

0

1

1

0

1

1

X

X

X

X

32

0D8000h to 0DFFFFh

SA28

0

1

1

1

0

0

X

X

X

X

32

0E0000h to 0E7FFFh

SA29

0

1

1

1

0

1

X

X

X

X

32

0E8000h to 0EFFFFh

SA30

0

1

1

1

1

0

X

X

X

X

32

0F0000h to 0F7FFFh

SA31

0

1

1

1

1

1

X

X

X

X

32

0F8000h to 0FFFFFh

MB84VD22184FM/VD22194FM

-70

13

(Continued)

B

a

n

k

Sector

Sector address

Sector size

(Kwords)

Address range

Bank

address

A

20

A

19

A

18

A

17

A

16

A

15

A

14

A

13

A

12

A

11

B

a

n

k

B

SA32

1

0

0

0

0

0

X

X

X

X

32

100000h to 107FFFh

SA33

1

0

0

0

0

1

X

X

X

X

32

108000h to 10FFFFh

SA34

1

0

0

0

1

0

X

X

X

X

32

110000h to 117FFFh

SA35

1

0

0

0

1

1

X

X

X

X

32

118000h to 11FFFFh

SA36

1

0

0

1

0

0

X

X

X

X

32

120000h to 127FFFh

SA37

1

0

0

1

0

1

X

X

X

X

32

128000h to 12FFFFh

SA38

1

0

0

1

1

0

X

X

X

X

32

130000h to 137FFFh

SA39

1

0

0

1

1

1

X

X

X

X

32

138000h to 13FFFFh

SA40

1

0

1

0

0

0

X

X

X

X

32

140000h to 147FFFh

SA41

1

0

1

0

0

1

X

X

X

X

32

148000h to 14FFFFh

SA42

1

0

1

0

1

0

X

X

X

X

32

150000h to 157FFFh

SA43

1

0

1

0

1

1

X

X

X

X

32

158000h to 15FFFFh

SA44

1

0

1

1

0

0

X

X

X

X

32

160000h to 167FFFh

SA45

1

0

1

1

0

1

X

X

X

X

32

168000h to 16FFFFh

SA46

1

0

1

1

1

0

X

X

X

X

32

170000h to 177FFFh

SA47

1

0

1

1

1

1

X

X

X

X

32

178000h to 17FFFFh

B

a

n

k

A

SA48

1

1

0

0

0

0

X

X

X

X

32

180000h to 187FFFh

SA49

1

1

0

0

0

1

X

X

X

X

32

188000h to 18FFFFh

SA50

1

1

0

0

1

0

X

X

X

X

32

190000h to 197FFFh

SA51

1

1

0

0

1

1

X

X

X

X

32

198000h to 19FFFFh

SA52

1

1

0

1

0

0

X

X

X

X

32

1A0000h to 1A7FFFh

SA53

1

1

0

1

0

1

X

X

X

X

32

1A8000h to 1AFFFFh

SA54

1

1

0

1

1

0

X

X

X

X

32

1B0000h to 1B7FFFh

SA55

1

1

0

1

1

1

X

X

X

X

32

1B8000h to 1BFFFFh

SA56

1

1

1

0

0

0

X

X

X

X

32

1C0000h to 1C7FFFh

SA57

1

1

1

0

0

1

X

X

X

X

32

1C8000h to 1CFFFFh

SA58

1

1

1

0

1

0

X

X

X

X

32

1D0000h to 1D7FFFh

SA59

1

1

1

0

1

1

X

X

X

X

32

1D8000h to 1DFFFFh

SA60

1

1

1

1

0

0

X

X

X

X

32

1E0000h to 1E7FFFh

SA61

1

1

1

1

0

1

X

X

X

X

32

1E8000h to 1EFFFFh

SA62

1

1

1

1

1

0

X

X

X

X

32

1F0000h to 1F7FFFh

SA63

1

1

1

1

1

1

0

0

0

X

4

1F8000h to 1F8FFFh

SA64

1

1

1

1

1

1

0

0

1

X

4

1F9000h to 1F9FFFh

SA65

1

1

1

1

1

1

0

1

0

X

4

1FA000h to 1FAFFFh

SA66

1

1

1

1

1

1

0

1

1

X

4

1FB000h to 1FBFFFh

SA67

1

1

1

1

1

1

1

0

0

X

4

1FC000h to 1FCFFFh

SA68

1

1

1

1

1

1

1

0

1

X

4

1FD000h to 1FDFFFh

SA69

1

1

1

1

1

1

1

1

0

X

4

1FE000h to 1FEFFFh

SA70

1

1

1

1

1

1

1

1

1

X

4

1FF000h to 1FFFFFh

MB84VD22184FM/VD22194FM

-70

14

Sector Address Table (Bottom Boot Type)

(Continued)

B

a

n

k

Sector

Sector address

Sector size

(Kwords)

Address range

Bank

address

A

20

A

19

A

18

A

17

A

16

A

15

A

14

A

13

A

12

A

11

B

a

n

k

B

SA70

1

1

1

1

1

1

X

X

X

X

32

1F8000h to 1FFFFFh

SA69

1

1

1

1

1

0

X

X

X

X

32

1F0000h to 1F7FFFh

SA68

1

1

1

1

0

1

X

X

X

X

32

1E8000h to 1EFFFFh

SA67

1

1

1

1

0

0

X

X

X

X

32

1E0000h to 1E7FFFh

SA66

1

1

1

0

1

1

X

X

X

X

32

1D8000h to 1DFFFFh

SA65

1

1

1

0

1

0

X

X

X

X

32

1D0000h to 1D7FFFh

SA64

1

1

1

0

0

1

X

X

X

X

32

1C8000h to 1CFFFFh

SA63

1

1

1

0

0

0

X

X

X

X

32

1C0000h to 1C7FFFh

SA62

1

1

0

1

1

1

X

X

X

X

32

1B8000h to 1BFFFFh

SA61

1

1

0

1

1

0

X

X

X

X

32

1B0000h to 1B7FFFh

SA60

1

1

0

1

0

1

X

X

X

X

32

1A8000h to 1AFFFFh

SA59

1

1

0

1

0

0

X

X

X

X

32

1A0000h to 1A7FFFh

SA58

1

1

0

0

1

1

X

X

X

X

32

198000h to 19FFFFh

SA57

1

1

0

0

1

0

X

X

X

X

32

190000h to 197FFFh

SA56

1

1

0

0

0

1

X

X

X

X

32

188000h to 18FFFFh

SA55

1

1

0

0

0

0

X

X

X

X

32

180000h to 187FFFh

SA54

1

0

1

1

1

1

X

X

X

X

32

178000h to 17FFFFh

SA53

1

0

1

1

1

0

X

X

X

X

32

170000h to 177FFFh

SA52

1

0

1

1

0

1

X

X

X

X

32

168000h to 16FFFFh

SA51

1

0

1

1

0

0

X

X

X

X

32

160000h to 167FFFh

SA50

1

0

1

0

1

1

X

X

X

X

32

158000h to 15FFFFh

SA49

1

0

1

0

1

0

X

X

X

X

32

150000h to 157FFFh

SA48

1

0

1

0

0

1

X

X

X

X

32

148000h to 14FFFFh

SA47

1

0

1

0

0

0

X

X

X

X

32

140000h to 147FFFh

SA46

1

0

0

1

1

1

X

X

X

X

32

138000h to 13FFFFh

SA45

1

0

0

1

1

0

X

X

X

X

32

130000h to 137FFFh

SA44

1

0

0

1

0

1

X

X

X

X

32

128000h to 12FFFFh

SA43

1

0

0

1

0

0

X

X

X

X

32

120000h to 127FFFh

SA42

1

0

0

0

1

1

X

X

X

X

32

118000h to 11FFFFh

SA41

1

0

0

0

1

0

X

X

X

X

32

110000h to 117FFFh

SA40

1

0

0

0

0

1

X

X

X

X

32

108000h to 10FFFFh

SA39

1

0

0

0

0

0

X

X

X

X

32

100000h to 107FFFh

MB84VD22184FM/VD22194FM

-70

15

B

a

n

k

Sector

Sector address

Sector size

(Kwords)

Address range

Bank

address

A

20

A

19

A

18

A

17

A

16

A

15

A

14

A

13

A

12

A

11

B

a

n

k

B

SA38

0

1

1

1

1

1

X

X

X

X

32

0F8000h to 0FFFFFh

SA37

0

1

1

1

1

0

X

X

X

X

32

0F0000h to 0F7FFFh

SA36

0

1

1

1

0

1

X

X

X

X

32

0E8000h to 0EFFFFh

SA35

0

1

1

1

0

0

X

X

X

X

32

0E0000h to 0E7FFFh

SA34

0

1

1

0

1

1

X

X

X

X

32

0D8000h to 0DFFFFh

SA33

0

1

1

0

1

0

X

X

X

X

32

0D0000h to 0D7FFFh

SA32

0

1

1

0

0

1

X

X

X

X

32

0C8000h to 0CFFFFh

SA31

0

1

1

0

0

0

X

X

X

X

32

0C0000h to 0C7FFFh

SA30

0

1

0

1

1

1

X

X

X

X

32

0B8000h to 0BFFFFh

SA29

0

1

0

1

1

0

X

X

X

X

32

0B0000h to 0B7FFFh

SA28

0

1

0

1

0

1

X

X

X

X

32

0A8000h to 0AFFFFh

SA27

0

1

0

1

0

0

X

X

X

X

32

0A0000h to 0A7FFFh

SA26

0

1

0

0

1

1

X

X

X

X

32

098000h to 09FFFFh

SA25

0

1

0

0

1

0

X

X

X

X

32

090000h to 097FFFh

SA24

0

1

0

0

0

1

X

X

X

X

32

088000h to 08FFFFh

SA23

0

1

0

0

0

0

X

X

X

X

32

080000h to 087FFFh

B

a

n

k

A

SA22

0

0

1

1

1

1

X

X

X

X

32

078000h to 07FFFFh

SA21

0

0

1

1

1

0

X

X

X

X

32

070000h to 077FFFh

SA20

0

0

1

1

0

1

X

X

X

X

32

068000h to 06FFFFh

SA19

0

0

1

1

0

0

X

X

X

X

32

060000h to 067FFFh

SA18

0

0

1

0

1

1

X

X

X

X

32

058000h to 05FFFFh

SA17

0

0

1

0

1

0

X

X

X

X

32

050000h to 057FFFh

SA16

0

0

1

0

0

1

X

X

X

X

32

048000h to 04FFFFh

SA15

0

0

1

0

0

0

X

X

X

X

32

040000h to 047FFFh

SA14

0

0

0

1

1

1

X

X

X

X

32

038000h to 03FFFFh

SA13

0

0

0

1

1

0

X

X

X

X

32

030000h to 037FFFh

SA12

0

0

0

1

0

1

X

X

X

X

32

028000h to 02FFFFh

SA11

0

0

0

1

0

0

X

X

X

X

32

020000h to 027FFFh

SA10

0

0

0

0

1

1

X

X

X

X

32

018000h to 01FFFFh

SA9

0

0

0

0

1

0

X

X

X

X

32

010000h to 017FFFh

SA8

0

0

0

0

0

1

X

X

X

X

32

008000h to 00FFFFh

SA7

0

0

0

0

0

0

1

1

1

X

4

007000h to 007FFFh

SA6

0

0

0

0

0

0

1

1

0

X

4

006000h to 006FFFh

SA5

0

0

0

0

0

0

1

0

1

X

4

005000h to 005FFFh

SA4

0

0

0

0

0

0

1

0

0

X

4

004000h to 004FFFh

SA3

0

0

0

0

0

0

0

1

1

X

4

003000h to 003FFFh

SA2

0

0

0

0

0

0

0

1

0

X

4

002000h to 002FFFh

SA1

0

0

0

0

0

0

0

0

1

X

4

001000h to 001FFFh

SA0

0

0

0

0

0

0

0

0

0

X

4

000000h to 000FFFh

MB84VD22184FM/VD22194FM

-70

16

Sector Group Addresses Table (Top Boot Type)

Sector group

A

20

A

19

A

18

A

17

A

16

A

15

A

14

A

13

A

12

Sectors

SGA0

0

0

0

0

0

0

X

X

X

SA0

SGA1

0

0

0

0

0

1

X

X

X

SA1 to SA3

1

0

1

1

SGA2

0

0

0

1

X

X

X

X

X

SA4 to SA7

SGA3

0

0

1

0

X

X

X

X

X

SA8 to SA11

SGA4

0

0

1

1

X

X

X

X

X

SA12 to SA15

SGA5

0

1

0

0

X

X

X

X

X

SA16 to SA19

SGA6

0

1

0

1

X

X

X

X

X

SA20 to SA23

SGA7

0

1

1

0

X

X

X

X

X

SA24 to SA27

SGA8

0

1

1

1

X

X

X

X

X

SA28 to SA31

SGA9

1

0

0

0

X

X

X

X

X

SA32 to SA35

SGA10

1

0

0

1

X

X

X

X

X

SA36 to SA39

SGA11

1

0

1

0

X

X

X

X

X

SA40 to SA43

SGA12

1

0

1

1

X

X

X

X

X

SA44 to SA47

SGA13

1

1

0

0

X

X

X

X

X

SA48 to SA51

SGA14

1

1

0

1

X

X

X

X

X

SA52 to SA55

SGA15

1

1

1

0

X

X

X

X

X

SA56 to SA59

SGA16

1

1

1

1

0

0

X

X

X

SA60 to SA62

0

1

1

0

SGA17

1

1

1

1

1

1

0

0

0

SA63

SGA18

1

1

1

1

1

1

0

0

1

SA64

SGA19

1

1

1

1

1

1

0

1

0

SA65

SGA20

1

1

1

1

1

1

0

1

1

SA66

SGA21

1

1

1

1

1

1

1

0

0

SA67

SGA22

1

1

1

1

1

1

1

0

1

SA68

SGA23

1

1

1

1

1

1

1

1

0

SA69

SGA24

1

1

1

1

1

1

1

1

1

SA70

MB84VD22184FM/VD22194FM

-70

17

Sector Group Addresses Table (Bottom Boot Type)

Sector group

A

20

A

19

A

18

A

17

A

16

A

15

A

14

A

13

A

12

Sectors

SGA0

0

0

0

0

0

0

0

0

0

SA0

SGA1

0

0

0

0

0

0

0

0

1

SA1

SGA2

0

0

0

0

0

0

0

1

0

SA2

SGA3

0

0

0

0

0

0

0

1

1

SA3

SGA4

0

0

0

0

0

0

1

0

0

SA4

SGA5

0

0

0

0

0

0

1

0

1

SA5

SGA6

0

0

0

0

0

0

1

1

0

SA6

SGA7

0

0

0

0

0

0

1

1

1

SA7

SGA8

0

0

0

0

0

1

X

X

X

SA8 to SA10

1

0

1

1

SGA9

0

0

0

1

X

X

X

X

X

SA11 to SA14

SGA10

0

0

1

0

X

X

X

X

X

SA15 to SA18

SGA11

0

0

1

1

X

X

X

X

X

SA19 to SA22

SGA12

0

1

0

0

X

X

X

X

X

SA23 to SA26

SGA13

0

1

0

1

X

X

X

X

X

SA27 to SA30

SGA14

0

1

1

0

X

X

X

X

X

SA31 to SA34

SGA15

0

1

1

1

X

X

X

X

X

SA35 to SA38

SGA16

1

0

0

0

X

X

X

X

X

SA39 to SA42

SGA17

1

0

0

1

X

X

X

X

X

SA43 to SA46

SGA18

1

0

1

0

X

X

X

X

X

SA47 to SA50

SGA19

1

0

1

1

X

X

X

X

X

SA51 to SA54

SGA20

1

1

0

0

X

X

X

X

X

SA55 to SA58

SGA21

1

1

0

1

X

X

X

X

X

SA59 to SA62

SGA22

1

1

1

0

X

X

X

X

X

SA63 to SA66

SGA23

1

1

1

1

0

0

X

X

X

SA67 to SA69

0

1

1

0

SGA24

1

1

1

1

1

1

X

X

X

SA70

MB84VD22184FM/VD22194FM

-70

18

Sector Group Protection Verify Autoselect Codes Table (Top Boot Type)

Legend: L = V

IL

, H = V

IH

. See DC Characteristics for voltage levels.

* : Outputs 01h at protected sector group addresses and outputs 00h at unprotected sector group addresses.

Expanded Autoselect Code Table (Top Boot Type)

Sector Group Protection Verify Autoselect Codes Table (Bottom Boot Type)

Legend: L = V

IL

, H = V

IH

. See DC Characteristics for voltage levels.

* : Outputs 01h at protected sector group addresses and outputs 00h at unprotected sector group addresses.

Expanded Autoselect Code Table (Bottom Boot Type)

Type

A

20

to A

12

A

6

A

3

A

2

A

1

A

0

Code (HEX)

Manufacture's Code

BA

L

L

L

L

L

04h

Device Code

BA

L

L

L

L

H

2250h

Sector Group Protection

SA

L

L

L

H

L

01h*

Type

Code

DQ

15

DQ

14

DQ

13

DQ

12

DQ

11

DQ

10

DQ

9

DQ

8

DQ

7

DQ

6

DQ

5

DQ

4

DQ

3

DQ

2

DQ

1

DQ

0

Manufacture's

Code

04h

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

Device Code

2250h

0

0

1

0

0

0

1

0

0

1

0

1

0

0

0

0

Sector Group

Protection

01h

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

Type

A

20

to A

12

A

6

A

3

A

2

A

1

A

0

Code (HEX)

Manufacture's Code

BA

L

L

L

L

L

04h

Device Code

BA

L

L

L

L

H

2253h

Sector Group Protection

SA

L

L

L

H

L

01h*

Type

Code

DQ

15

DQ

14

DQ

13

DQ

12

DQ

11

DQ

10

DQ

9

DQ

8

DQ

7

DQ

6

DQ

5

DQ

4

DQ

3

DQ

2

DQ

1

DQ

0

Manufacture's

Code

04h

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

Device Code

2253h

0

0

1

0

0

0

1

0

0

1

0

1

0

0

1

1

Sector Group

Protection

01h

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

MB84VD22184FM/VD22194FM

-70

19

Command Definitions Table

(Continued)

Command

sequence

Bus

write

cycles

req'd

First bus

write cycle

Second bus

write cycle

Third bus

write cycle

Fourth bus

read/write cy-

cle

Fifth bus

write cycle

Sixth bus

write cycle

Addr.

Data

Addr.

Data

Addr.

Data

Addr.

Data

Addr.

Data

Addr.

Data

Read/Reset*

1

1

XXXh

F0h

Read/Reset*

1

3

555h

AAh

2AAh

55h

555h

F0h

RA

RD

Autoselect

3

555h

AAh

2AAh

55h

(BA)

555h

90h

Program

4

555h

AAh

2AAh

55h

555h

A0h

PA

PD

Program

Suspend

1

BA

B0h

Program

Resume

1

BA

30h

Chip Erase

6

555h

AAh

2AAh

55h

555h

80h

555h

AAh

2AAh

55h

555h

10h

Sector Erase

6

555h

AAh

2AAh

55h

555h

80h

555h

AAh

2AAh

55h

SA

30h

Erase Suspend

1

BA

B0h

Erase Resume

1

BA

30h

Set to

Fast Mode

3

555h

AAh

2AAh

55h

555h

20h

Fast

Program *

2

2

XXXh

A0h

PA

PD

Reset from Fast

Mode *

2

2

BA

90h

XXXh

F0h*

6

Extended

Sector Group

Protection *

3

4

XXXh

60h

SPA

60h

SPA

40h

SPA

SD

Query *

4

1

(BA)

55h

98h

HiddenROM

Entry

3

555h

AAh

2AAh

55h

555h

88h

HiddenROM

Program *

5

4

555h

AAh

2AAh

55h

555h

A0h

(HRA)

PA

PD

HiddenROM

Exit *

5

4

555h

AAh

2AAh

55h

(HRBA)

555h

90h

XXXh

00h

MB84VD22184FM/VD22194FM

-70

20

(Continued)

*1 : Both of these reset commands are equivalent.

*2 : This command is valid during Fast Mode.

*3 : This command is valid while RESET

=

V

ID

.

*4 : The valid address are A

6

to A

0

.

*5 : This command is valid during HiddenROM mode.

*6 : The date "00h" is also acceptable.

Notes:

∑

Address bits A

20

to A

11

=

X

=

"H" or "L" for all address commands except or Program Address (PA) , Sector

Address (SA) , Bank Address (BA) .

∑

Bus operations are defined in

"User Bus Operations Tables" (

s

DEVICE BUS OPERATION).

∑

RA

=

Address of the memory location to be read

PA

=

Address of the memory location to be programmed

Addresses are latched on the falling edge of the write pulse.

SA

=

Address of the sector to be erased. The combination of A

20

, A

19

, A

18

, A

17

, A

16

, A

15

, A

14

, A

13

, and

A

12

will uniquely select any sector.

BA

=

Bank Address (A

20

to A

18

)

∑

RD

=

Data read from location RA during read operation.

PD

=

Data to be programmed at location PA. Data is latched on the rising edge of write pulse.

∑

SPA

=

Sector group address to be protected. Set sector group address and (A

6

, A

3

, A

2

, A

1

, A

0

)

=

(0, 0, 0,

1, 0) .

SD

=

Sector group protection verify data. Output 01h at protected sector group addresses and output

00h at unprotected sector group addresses.

∑

HRA

=

Address of the HiddenROM area

Top Boot Type :

1FF000h to 1FF07Fh

Bottom Boot Type :

000000h to 00007Fh

∑

HRBA

=

Bank Address of the HiddenROM area

Top Boot Type

: A

20

=

A

19

=

A

18

=

1

Bottom Boot Type

: A

20

=

A

19

=

A

18

=

0

∑

The system should generate the following address patterns :

Word Mode : 555h or 2AAh to addresses A

10

to A

0

∑

Both Read/Reset commands are functionally equivalent, resetting the device to the read mode.

∑

The command combinations not described in "Command Definitions Table" are illegal.

MB84VD22184FM/VD22194FM

-70

21

2.

AC Characteristics

∑ Read Only Operations Characteristics

* : Test Conditions:

Output Load:1 TTL gate and 30 pF

Input rise and fall times: 5 ns

Input pulse levels: 0.0 V to 3.0 V

Timing measurement reference level

Input: 0.5 ◊ Vccf

Output: 0.5 ◊ Vccf

Parameter

Symbol

Test setup

Value*

Unit

JEDEC

Standard

Min

Max

Read Cycle Time

t

AVAV

t

RC

--

70

ns

Address to Output Delay

t

AVQV

t

ACC

CEf = V

IL

OE = V

IL

70

ns

Chip Enable to Output Delay

t

ELQV

t

CE

OE = V

IL

70

ns

Output Enable to Output Delay

t

GLQV

t

OE

--

30

ns

Chip Enable to Output High-Z

t

EHQZ

t

DF

--

25

ns

Output Enable to Output High-Z

t

GHQZ

t

DF

--

25

ns

Output Hold Time from Addresses,

CEf or OE, Whichever Occurs First

t

AXQX

t

OH

--

0

ns

RESET Pin Low to Read Mode

--

t

READY

--

20

µ

s

MB84VD22184FM/VD22194FM

-70

22

∑ Write/Erase/Program Operations

*1 : This does not include the preprogramming time.

*2 : This timing is for Sector Group Protection operation.

Parameter

Symbol

Value

Unit

JEDEC

Standard

Min

Typ

Max

Write Cycle Time

t

AVAV

t

WC

70

ns

Address Setup Time

t

AVWL

t

AS

0

ns

Address Setup Time to OE Low During Toggle Bit

Polling

--

t

ASO

12

ns

Address Hold Time

t

WLAX

t

AH

45

ns

Address Hold Time from CEf or OE High During

Toggle Bit Polling

--

t

AHT

0

ns

Data Setup Time

t

DVWH

t

DS

30

ns

Data Hold Time

t

WHDX

t

DH

0

ns

Output Enable

Hold Time

Read

--

t

OEH

0

ns

Toggle and Data Polling

10

ns

CEf High During Toggle Bit Polling

--

t

CEPH

20

ns

OE High During Toggle Bit Polling

--

t

OEPH

20

ns

Read Recover Time Before Write

t

GHWL

t

GHWL

0

ns

Read Recover Time Before Write

t

GHEL

t

GHEL

0

ns

CEf Setup Time

t

ELWL

t

CS

0

ns

WE Setup Time

t

WLEL

t

WS

0

ns

CEf Hold Time

t

WHEH

t

CH

0

ns

WE Hold Time

t

EHWH

t

WH

0

ns

Write Pulse Width

t

WLWH

t

WP

35

ns

CEf Pulse Width

t

ELEH

t

CP

35

ns

Write Pulse Width High

t

WHWL

t

WPH

25

ns

CEf Pulse Width High

t

EHEL

t

CPH

25

ns

Sector Erase Operation *

1

t

WHWH2

t

WHWH2

0.5

s

V

CC

f Setup Time

--

t

VCS

50

µs

Rise Time to V

ID

*

2

--

t

VIDR

500

ns

Rise Time to V

ID

*

2

--

t

VACCR

500

ns

Voltage Transition Time *

2

--

t

VLHT

4

µs

Write Pulse Width *

2

--

t

WPP

100

µs

OE Setup Time to WE Active *

2

--

t

OESP

4

µs

CEf Setup Time to WE Active *

2

--

t

CSP

4

µs

Recover Time from RY/BY

--

t

RB

ns

RESET Pulse Width

--

t

RP

500

ns

RESET High Level Period before Read

--

t

RH

200

ns

Program/Erase Valid to RY/BY Delay

--

t

BUSY

90

ns

Delay Time from Embedded Output Enable

--

t

EOE

70

ns

Erase Time-Out Time

--

t

TOW

50

µs

Erase Suspend Transition Time

--

t

SPD

µs

MB84VD22184FM/VD22194FM

-70

23

∑ Read Cycle (Flash)

WE

OE

CEf

t

CEf

t

OE

DQ

Address Stable

High-Z

Output Valid

High-Z

t

OEH

t

ACC

t

RC

RESET

t

ACC

t

OH

DQ

t

RC

Address Stable

High-Z

Output Valid

t

RH

t

DF

Address

Address

t

RH

t

CEf

t

RP

CEf

MB84VD22184FM/VD22194FM

-70

24

∑ Write Cycle (WE control) (Flash)

t

CH

t

WP

t

WHWH1

t

WC

t

AH

CEf

OE

t

RC

DQ

t

AS

t

OE

t

WPH

t

GHWL

t

DH

DQ

7

PD

A0h

D

OUT

WE

555h

PA

PA

t

OH

Data Polling

3rd Bus Cycle

t

CS

t

CEf

t

DS

D

OUT

Address

Notes :

∑

PA is address of the memory location to be programmed.

∑

DQ

7

is the output of the complement of the data written to the device.

∑

D

OUT

is the output of the data written to the device.

∑

Figure indicates last two bus cycles out of four bus cycle sequence.

∑

These waveforms are for the ◊16 mode.

MB84VD22184FM/VD22194FM

-70

25

∑ Write Cycle (CEf control) (Flash)

Notes :

∑

PA is address of the memory location to be programmed.

∑

DQ

7

is the output of the complement of the data written to the device.

∑

D

OUT

is the output of the data written to the device.

∑

Figure indicates last two bus cycles out of four bus cycle sequence.

∑

These waveforms are for the ◊16 mode.

t

CP

t

DS

t

WHWH1

t

WC

t

AH

WE

OE

DQ

t

AS

t

CPH

t

DH

DQ

7

A0h

D

OUT

CEf

555h

PA

PA

Data Polling

3rd Bus Cycle

t

WS

t

WH

t

GHEL

PD

Address

MB84VD22184FM/VD22194FM

-70

26

∑ AC Waveforms Chip/Sector Erase Operations (Flash)

Address

V

CC

f

CEf

OE

DQ

WE

555h

2AAh

555h

555h

2AAh

SA*

t

DS

t

CH

t

AS

t

AH

t

CS

t

WPH

t

DH

t

GHWL

t

VCS

t

WC

t

WP

AAh

55h

80h

AAh

55h

10h/

30h for Sector Erase

30h

* : SA is the sector address for Sector Erase. Addresses = 555h for Chip Erase.

Note : These waveform are for the ◊16 mode.

MB84VD22184FM/VD22194FM

-70

27

∑ AC Waveforms for Data Polling during Embedded Algorithm Operations (Flash)

* : DQ

7

= Valid Data (The device has completed the Embedded operation.)

t

OEH

t

OE

t

WHWH1 or 2

CEf

OE

WE

DQ

7

t

DF

t

CH

t

CEf

DQ

7

=

Valid Data

DQ

7

*

DQ

DQ

6

to DQ

0

= Output Flag

t

EOE

DQ

8

to DQ

0

Valid Data

High-Z

High-Z

(DQ

6

to DQ

0

)

Data Input

Data Input

t

BUSY

RY/BY

MB84VD22184FM/VD22194FM

-70

28

∑ AC Waveforms for Toggle Bit during Embedded Algorithm Operations (Flash)

* : DQ

6

stops toggling (The device has completed the Embedded operation).

Address

RY/BY

CEf

WE

DQ

6

/DQ

2

OE

t

AS

t

BUSY

Toggle

t

AHT

t

AHT

t

ASO

t

OEH

t

OEH

t

OE

Data

Toggle

Data

Toggle

Data

Stop

Toggling

Data

t

CEf

*

Output

Valid

t

DH

t

CEPH

t

OEPH

MB84VD22184FM/VD22194FM

-70

29

∑ Back-to-back Read/Write Timing Diagram (Flash)

Note : This is example of Read for Bank 1 and Embedded Algorithm (program) for Bank 2.

BA1: Address of Bank 1.

BA2: Address of Bank 2.

CEf

DQ

WE

Address

BA1

BA1

BA1

BA2

(555h)

BA2

(PA)

BA2

(PA)

OE

Valid

Output

Valid

Output

Valid

Output

Status

Valid

Intput

Valid

Intput

t

RC

t

RC

t

RC

t

RC

t

WC

t

WC

t

AHT

t

AS

t

AS

t

AH

t

ACC

t

CE

t

OE

t

OEH

t

WP

t

GHWL

t

DS

t

DF

t

DH

t

DF

t

CEPH

Read

Command

Command

Read

Read

Read

(A0h)

(PD)

MB84VD22184FM/VD22194FM

-70

30

∑ RY/BY Timing Diagram during Write/Erase Operations (Flash)

∑ RESET, RY/BY Timing Diagram (Flash)

Rising edge of the last write pulse

CEf

RY/BY

WE

t

BUSY

Entire programming

or erase operations

t

RP

RESET

t

READY

RY/BY

WE

t

RB

MB84VD22184FM/VD22194FM

-70

31

∑ Temporary Sector Unprotection (Flash)

V

CC

f

V

ID

RESET

3V

CEf

WE

RY/BY

Program or Erase Command Sequence

t

VIDR

t

VLHT

t

VCS

t

VLHT

t

VLHT

Unprotection Period

3V

MB84VD22184FM/VD22194FM

-70

32

∑ Extended Sector Group Protection (Flash)

SGAx : Sector Group Address to be protected

SGAy : Next Group Sector Address to be protected

TIME-OUT : Time-Out window = 250

µ

s (Min)

SGAy

RESET

A

6

OE

WE

CEf

Data

A

1

V

CC

f

A

0

Address

SGAx

SGAx

60h

01h

40h

60h

60h

TIME-OUT

t

VCS

t

VLHT

t

VIDR

t

OE

t

WP

t

WC

t

WC

MB84VD22184FM/VD22194FM

-70

33

∑ Accelerated Program (Flash)

3 V

WP/ACC

V

CC

f

CEf

WE

RY/BY

t

VLHT

Program Command Sequence

3 V

t

VLHT

t

VCS

t

VACCR

V

ACC

t

VLHT

Acceleration period

MB84VD22184FM/VD22194FM

-70

34

3.

Erase and Programming Performance

Parameter

Limits

Unit

Comments

Min

Typ

Max

Sector Erase Time

0.5

2.0

s

Excludes programming time

prior to erasure

Word Programming Time

6.0

100

µ

s

Excludes system-level

overhead

Chip Programming Time

12.6

50

s

Excludes system-level

overhead

Program/Erase Cycle

100,000

cycle

MB84VD22184FM/VD22194FM

-70

35

s

4 M SRAM for MCP

1.

AC Characteristics

∑ Read Cycle (SRAM)

Note: Test Conditions≠ Output Load:1 TTL gate and 30 pF

Input rise and fall times: 5 ns

Input pulse levels: 0.0 V to V

CC

s

Timing measurement reference level

Input: 0.5◊V

CC

s

Output: 0.5◊V

CC

s

Parameter

Symbol

Value

Unit

Min

Max

Read Cycle Time

t

RC

70

--

ns

Address Access Time

t

AA

--

70

ns

Chip Enable (CE1s) Access Time

t

CO1

--

70

ns

Chip Enable (CE2s) Access Time

t

CO2

--

70

ns

Output Enable Access Time

t

OE

--

35

ns

LB, UB to Output Valid

t

BA

--

70

ns

Chip Enable (CE1s Low and CE2s High) to Output Active

t

COE

5

--

ns

Output Enable Low to Output Active

t

OEE

0

--

ns

UB, LB Enable Low to Output Active

t

BE

0

--

ns

Chip Enable (CE1s High or CE2s Low) to Output High-Z

t

OD

--

25

ns

Output Enable High to Output High-Z

t

ODO

--

25

ns

UB, LB Output Enable to Output High-Z

t

BD

--

25

ns

Output Data Hold Time

t

OH

10

--

ns

MB84VD22184FM/VD22194FM

-70

36

∑ Read Cycle (SRAM)

Note: WE remains HIGH for the read cycle.

t

RC

t

AA

t

OH

t

CO1

t

OD

t

ODO

t

OEE

t

COE

Valid Data Output

Address

CE1s

OE

DQ

CE2s

t

COE

t

OE

t

CO2

t

OD

LB, UB

t

BA

t

BD

t

BE

MB84VD22184FM/VD22194FM

-70

37

∑ Write Cycle (SRAM)

Parameter

Symbol

Value

Unit

Min

Max

Write Cycle Time

t

WC

70

--

ns

Write Pulse Width

t

WP

50

--

ns

Chip Enable to End of Write

t

CW

55

--

ns

Address valid to End of Write

t

AW

55

--

ns

UB, LB to End of Write

t

BW

55

--

ns

Address Setup Time

t

AS

0

--

ns

Write Recovery Time

t

WR

0

--

ns

WE Low to Output High-Z

t

ODW

--

25

ns

WE High to Output Active

t

OEW

0

--

ns

Data Setup Time

t

DS

30

--

ns

Data Hold Time

t

DH

0

--

ns