©2001 Silicon Storage Technology, Inc.

S71077-04-000

6/01

310

1

The SST logo and SuperFlash are registered trademarks of Silicon Storage Technology, Inc.

SSF is a trademark of Silicon Storage Technology, Inc.

These specifications are subject to change without notice.

Data Sheet

4 Mbit (512K x8) SuperFlash EEPROM

SST28SF040A / SST28VF040A

FEATURES:

∑

Single Voltage Read and Write Operations

≠ 5.0V-only for SST28SF040A

≠ 2.7-3.6V for SST28VF040A

∑

Superior Reliability

≠ Endurance: 100,000 Cycles (typical)

≠ Greater than 100 years Data Retention

∑

Memory Organization: 512K x8

∑

Sector-Erase Capability: 256 Bytes per Sector

∑

Low Power Consumption

≠ Active Current: 15 mA (typical) for 5.0V and

10 mA (typical) for 2.7-3.6V

≠ Standby Current: 5 µA (typical)

∑

Fast Sector-Erase/Byte-Program Operation

≠ Byte-Program Time: 35 µs (typical)

≠ Sector-Erase Time: 2 ms (typical)

≠ Complete Memory Rewrite: 20 sec (typical)

∑

Fast Read Access Time

≠ 5.0V-only operation: 90 and 120 ns

≠ 2.7-3.6V operation: 150 and 200 ns

∑

Latched Address and Data

∑

Hardware and Software Data Protection

≠ 7-Read-Cycle-Sequence Software Data

Protection

∑

End-of-Write Detection

≠ Toggle Bit

≠ Data# Polling

∑

TTL I/O Compatibility

∑

JEDEC Standard

≠ Flash EEPROM Pinouts

∑

Packages Available

≠ 32-lead PLCC

≠ 32-lead TSOP (8mm x 14mm and 8mm x 20mm)

≠ 32-pin PDIP

PRODUCT DESCRIPTION

The SST28SF/VF040A are 512K x8 bit CMOS Sector-

Erase, Byte-Program EEPROMs. The SST28SF/VF040A

are manufactured using SST's proprietary, high perfor-

mance CMOS SuperFlash EEPROM Technology. The

split-gate cell design and thick oxide tunneling injector

attain better reliability and manufacturability compared with

alternative approaches. The SST28SF/VF040A erase and

program with a single power supply. The SST28SF/

VF040A conform to JEDEC standard pinouts for byte wide

memories and are compatible with existing industry stan-

dard flash EEPROM pinouts.

Featuring high performance programming, the SST28SF/

VF040A typically Byte-Program in 35 µs. The SST28SF/

VF040A typically Sector-Erase in 2 ms. Both Program and

Erase times can be optimized using interface features such

as Toggle bit or Data# Polling to indicate the completion of

the Write cycle. To protect against an inadvertent write, the

SST28SF/VF040A have on chip hardware and Software

Data Protection schemes. Designed, manufactured, and

tested for a wide spectrum of applications, the SST28SF/

VF040A are offered with a guaranteed sector endurance of

10,000 cycles. Data retention is rated greater than 100

years.

The SST28SF/VF040A are best suited for applications that

require reprogrammable nonvolatile mass storage of pro-

gram, configuration, or data memory. For all system appli-

cations, the SST28SF/VF040A significantly improve

performance and reliability, while lowering power consump-

tion when compared with floppy diskettes or EPROM

approaches. Flash EEPROM technology makes possible

convenient and economical updating of codes and control

programs on-line. The SST28SF/VF040A improve flexibil-

ity, while lowering the cost of program and configuration

storage application.

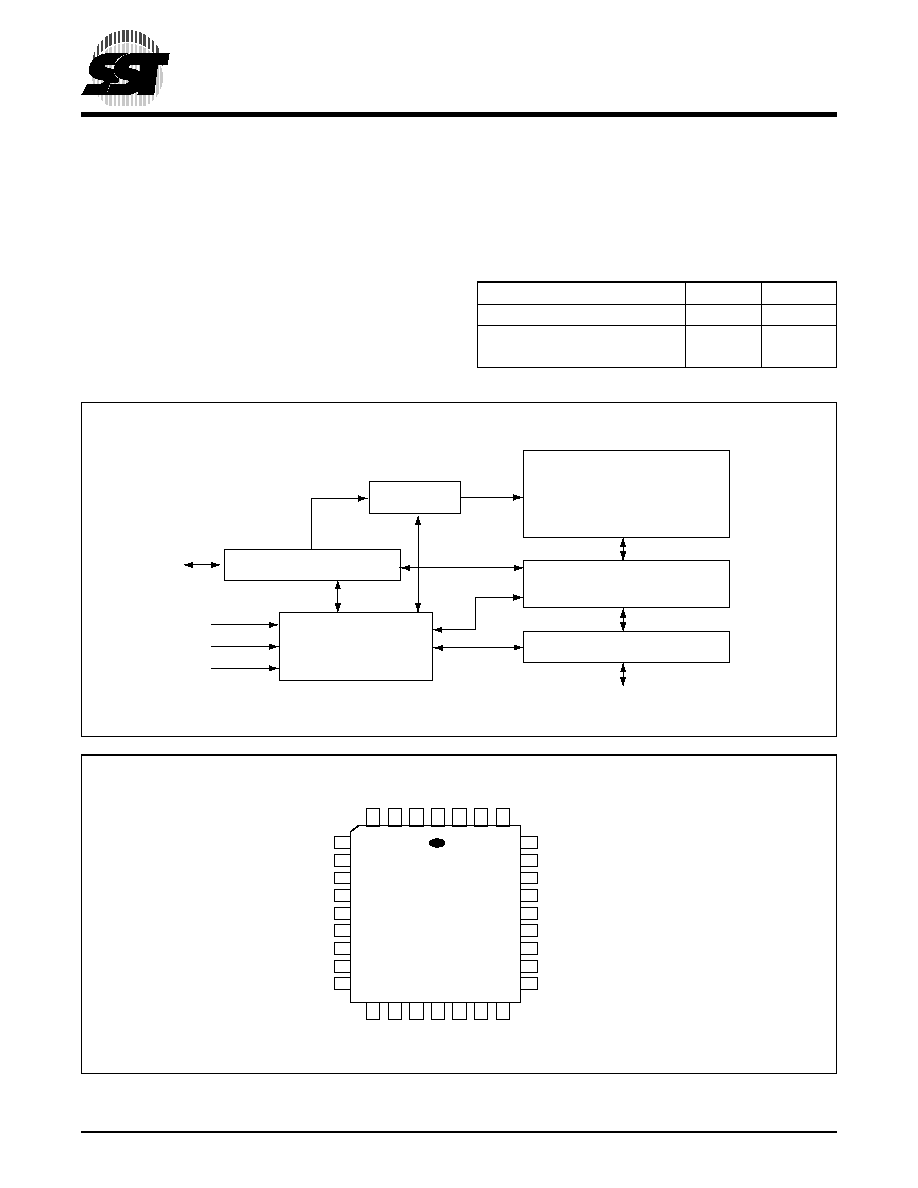

The functional block diagram shows the functional blocks of

the SST28SF/VF040A. Figures 1, 2, and 3 show the pin

assignments for the 32-lead PLCC, 32-lead TSOP, and 32-

pin PDIP packages. Pin descriptions and operation modes

are described in Tables 2 through 5.

Device Operation

Commands are used to initiate the memory operation func-

tions of the device. Commands are written to the device

using standard microprocessor write sequences. A com-

mand is written by asserting WE# low while keeping CE#

low. The address bus is latched on the falling edge of WE#

or CE#, whichever occurs last. The data bus is latched on

the rising edge of WE# or CE#, whichever occurs first.

Note, during the Software Data Protection sequence the

addresses are latched on the rising edge of OE# or CE#,

whichever occurs first.

SST28SF040A / SST28VF040A5.0 & 2.7 4Mb (x8) Byte-Program, Small Erase Sector flash memories

2

Data Sheet

4 Mbit SuperFlash EEPROM

SST28SF040A / SST28VF040A

©2001 Silicon Storage Technology, Inc.

S71077-04-000

6/01

310

Command Definitions

Table 4 contains a command list and a brief summary of

the commands. The following is a detailed description of

the operations initiated by each command.

Sector-Erase Operation

The Sector-Erase operation erases all bytes within a sector

and is initiated by a setup command and an execute com-

mand. A sector contains 256 Bytes. This sector erasability

enhances the flexibility and usefulness of the SST28SF/

VF040A, since most applications only need to change a

small number of bytes or sectors, not the entire chip.

The setup command is performed by writing 20H to the

device. The execute command is performed by writing D0H

to the device. The Erase operation begins with the rising

edge of the WE# or CE#, whichever occurs first and termi-

nates automatically by using an internal timer. The End-of-

Erase can be determined using either Data# Polling, Tog-

gle Bit, or Successive Reads detection methods. See Fig-

ure 9 for timing waveforms.

The two-step sequence of a setup command followed by

an execute command ensures that only memory contents

within the addressed sector are erased and other sectors

are not inadvertently erased.

Sector-Erase Flowchart Description

Fast and reliable erasing of the memory contents within a

sector is accomplished by following the Sector-Erase flow-

chart as shown in Figure 18. The entire procedure consists

of the execution of two commands. The Sector-Erase oper-

ation will terminate after a maximum of 4 ms. A Reset com-

mand can be executed to terminate the Sector-Erase

operation; however, if the Erase operation is terminated

prior to the 4 ms time-out, the sector may not be fully

erased. A Sector-Erase command can be reissued as

many times as necessary to complete the Erase operation.

The SST28SF/VF040A cannot be over-erased.

Chip-Erase Operation

The Chip-Erase operation is initiated by a setup command

(30H) and an execute command (30H). The Chip-Erase

operation allows the entire array of the SST28SF/VF040A

to be erased in one operation, as opposed to 2048 Sector-

Erase operations. Using the Chip-Erase operation will mini-

mize the time to rewrite the entire memory array. The Chip-

Erase operation will terminate after a maximum of 20 ms. A

Reset command can be executed to terminate the Erase

operation; however, if the Chip-Erase operation is termi-

nated prior to the 20 ms time-out, the chip may not be com-

pletely erased. If an erase error occurs a Chip-Erase

command can be reissued as many times as necessary to

complete the Chip-Erase operation. The SST28SF/

VF040A cannot be over-erased. (See Figure 8)

Byte-Program Operation

The Byte-Program operation is initiated by writing the setup

command (10H). Once the program setup is performed,

programming is executed by the next WE# pulse. See Fig-

ures 5 and 6 for timing waveforms. The address bus is

latched on the falling edge of WE# or CE#, whichever

occurs last. The data bus is latched on the rising edge of

WE# or CE#, whichever occurs first, and begins the Pro-

gram operation. The Program operation is terminated auto-

matically by an internal timer. See Figure 16 for the

programming flowchart.

The two-step sequence of a setup command followed by

an execute command ensures that only the addressed

byte is programmed and other bytes are not inadvertently

programmed.

The Byte-Program Flowchart Description

Programming data into the SST28SF/VF040A is accom-

plished by following the Byte-Program flowchart shown in

Figure 16. The Byte-Program command sets up the byte

for programming. The address bus is latched on the falling

edge of WE# or CE#, whichever occurs last. The data bus

is latched on the rising edge of WE# or CE#, whichever

occurs first and begins the Program operation. The end of

program can be detected using either the Data# Polling,

Toggle bit, or Successive reads.

Reset Operation

The Reset command is provided as a means to safely

abort the Erase or Program command sequences. Follow-

ing either setup commands (Erase or Program) with a write

of FFH will safely abort the operation. Memory contents will

not be altered. After the Reset command, the device

returns to the Read mode. The Reset command does not

enable Software Data Protection. See Figure 7 for timing

waveforms.

Read

The Read operation is initiated by setting CE#, and OE# to

logic low and setting WE# to logic high (See Table 3). See

Figure 4 for Read cycle timing waveform. The Read opera-

tion from the host retrieves data from the array. The device

remains enabled for Read until another operation mode is

accessed. During initial power-up, the device is in the Read

mode and is Software Data protected. The device must be

unprotected to execute a Write command.

Data Sheet

4 Mbit SuperFlash EEPROM

SST28SF040A / SST28VF040A

3

©2001 Silicon Storage Technology, Inc.

S71077-04-000

6/01

310

The Read operation of the SST28SF/VF040A are con-

trolled by OE# and CE# at logic low. When CE # is high,

the chip is deselected and only standby power will be con-

sumed. OE# is the output control and is used to gate data

from the output pins. The data bus is in high impedance

state when CE# or OE# are high.

Read-ID operation

The Read-ID operation is initiated by writing a single com-

mand (90H). A read of address 0000H will output the man-

ufacturer's ID (BFH). A read of address 0001H will output

the device ID (04H). Any other valid command will termi-

nate this operation.

Data Protection

In order to protect the integrity of nonvolatile data storage,

the SST28SF/VF040A provide both

hardware and software features to prevent inadvertent

writes to the device, for example, during system power-up

or power-down. Such provisions are described below.

Hardware Data Protection

The SST28SF/VF040A are designed with hardware fea-

tures to prevent inadvertent writes. This is done in the fol-

lowing ways:

1. Write Cycle Inhibit Mode: OE# low, CE#, or WE#

high will inhibit the Write operation.

2. Noise/Glitch Protection: A WE# pulse width of less

than 5 ns will not initiate a Write cycle.

3. V

DD

Power Up/Down Detection: The Write opera-

tion is inhibited when V

DD

is less than 2.0V.

4. After power-up, the device is in the Read mode

and the device is in the Software Data Protect

state.

Software Data Protection (SDP)

The SST28SF/VF040A have software methods to further

prevent inadvertent writes. In order to perform an Erase or

Program operation, a two-step command sequence con-

sisting of a set-up command followed by an execute com-

mand avoids inadvertent erasing and programming of the

device.

The SST28SF/VF040A will default to Software Data Pro-

tection after power up. A sequence of seven consecutive

reads at specific addresses will unprotect the device The

address sequence is 1823H, 1820H, 1822H, 0418H,

041BH, 0419H, 041AH. The address bus is latched on the

rising edge of OE# or CE#, whichever occurs first. A similar

seven read sequence of 1823H, 1820H, 1822H, 0418H,

041BH, 0419H, 040AH will protect the device. Also refer to

Figures 10 and 11 for the 7 read cycle sequence Software

Data Protection. The I/O pins can be in any state (i.e., high,

low, or tri-state).

Write Operation Status Detection

The SST28SF/VF040A provide three means to detect the

completion of a Write operation, in order to optimize the

system Write operation. The end of a Write operation

(Erase or Program) can be detected by three means: 1)

monitoring the Data# Polling bit, 2) monitoring the Toggle

bit, or 3) by two successive reads of the same data. These

three detection mechanisms are described below.

The actual completion of the nonvolatile Write is asynchro-

nous with the system; therefore, either a Data# Polling or

Toggle Bit read may be simultaneous with the completion

of the Write cycle. If this occurs, the system may possibly

get an erroneous result, i.e., valid data may appear to con-

flict with the DQ used. In order to prevent spurious rejec-

tion, if an erroneous result occurs, the software routine

should include a loop to read the accessed location an

additional two (2) times. If both reads are valid, then the

device has completed the Write cycle, otherwise the rejec-

tion is valid.

Data# Polling (DQ

7

)

The SST28SF/VF040A feature Data# Polling to indicate

the Write operation status. During a Write operation, any

attempt to read the last byte loaded during the byte-load

cycle will receive the complement of the true data on DQ

7

.

Once the Write cycle is completed, DQ

7

will show true

data. The device is then ready for the next operation. See

Figure 12 for Data# Polling timing waveforms. In order for

Data# Polling to function correctly, the byte being polled

must be erased prior to programming.

Toggle Bit (DQ

6

)

An alternative means for determining the Write operation

status is by monitoring the Toggle Bit, DQ

6

. During a Write

operation, consecutive attempts to read data from the

device will result in DQ

6

toggling between logic 0 (low) and

logic 1 (high). When the Write cycle is completed, the tog-

gling will stop. The device is then ready for the next opera-

tion. See Figure 13 for Toggle Bit timing waveforms.

4

Data Sheet

4 Mbit SuperFlash EEPROM

SST28SF040A / SST28VF040A

©2001 Silicon Storage Technology, Inc.

S71077-04-000

6/01

310

Successive Reads

An Alternative means for determining an end of a write

operation is by reading the same address for two consecu-

tive data matches.

Product Identification

The Product Identification mode identifies the device as

SST28SF/VF040A and the manufacturer as SST. This

mode may be accessed by hardware and software opera-

tions. The hardware operation is typically used by an exter-

nal programmer to identify the correct algorithm for the

SST28SF/VF040A. Users may wish to use the software

operation to identify the device (i.e., using the device ID).

For details see Table 3 for the hardware operation and Fig-

ure 19 for the software operation. The manufacturer and

device IDs are the same for both operations.

FIGURE 1: P

IN

A

SSIGNMENTS

FOR

32-

LEAD

PLCC

TABLE

1: P

RODUCT

I

DENTIFICATION

Address

Data

Manufacturer's ID

0000H

BFH

Device ID

SST28SF/VF040A

0001H

04H

T1.1 310

Y-Decoder

I/O Buffers and Data Latches

310 ILL B1.1

Address Buffer & Latches

X-Decoder

DQ7 - DQ0

A18 - A0

WE#

OE#

CE#

SuperFlash

Memory

Control Logic

F

UNCTIONAL

B

LOCK

D

IAGRAM

5

6

7

8

9

10

11

12

13

29

28

27

26

25

24

23

22

21

A7

A6

A5

A4

A3

A2

A1

A0

DQ0

A14

A13

A8

A9

A11

OE#

A10

CE#

DQ7

4 3 2 1 32 31 30

A12

A15

A16

A18

V

DD

WE#

A17

32-lead PLCC

Top View

310 ILL F02.3

14 15 16 17 18 19 20

DQ1

DQ2

V

SS

DQ3

DQ4

DQ5

DQ6

Data Sheet

4 Mbit SuperFlash EEPROM

SST28SF040A / SST28VF040A

5

©2001 Silicon Storage Technology, Inc.

S71077-04-000

6/01

310

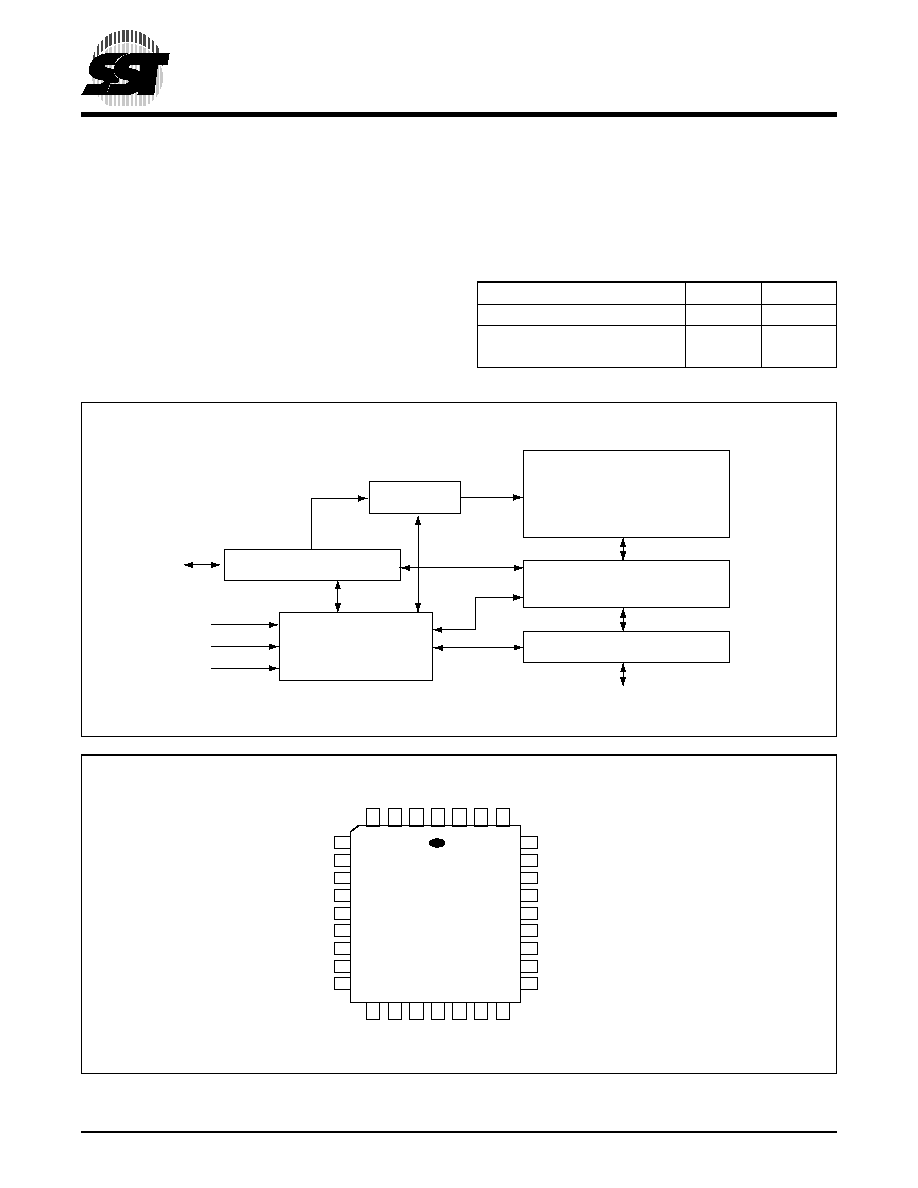

FIGURE 2: P

IN

A

SSIGNMENTS

FOR

32-

LEAD

TSOP

FIGURE 3: P

IN

A

SSIGNMENTS

FOR

32-

PIN

PDIP

A11

A9

A8

A13

A14

A17

WE#

VDD

A18

A16

A15

A12

A7

A6

A5

A4

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

OE#

A10

CE#

DQ7

DQ6

DQ5

DQ4

DQ3

VSS

DQ2

DQ1

DQ0

A0

A1

A2

A3

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

310 ILL F01.2

Standard Pinout

Top View

Die Up

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32-pin

PDIP

Top View

310 ILL F19.0

A18

A16

A15

A12

A7

A6

A5

A4

A3

A2

A1

A0

DQ0

DQ1

DQ2

VSS

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

VDD

WE#

A17

A14

A13

A8

A9

A11

OE#

A10

CE#

DQ7

DQ6

DQ5

DQ4

DQ3

TABLE

2: P

IN

D

ESCRIPTION

Symbol

Pin Name

Functions

A

18

-A

8

Row Address Inputs

To provide memory addresses. Row addresses define a sector.

A

7

-A

0

Column Address Inputs

Selects the byte within the sector

DQ

7

-DQ

0

Data Input/output

To output data during Read cycles and receive input data during Write cycles.

Data is internally latched during a Write cycle.

The outputs are in tri-state when OE# or CE# is high.

CE#

Chip Enable

To activate the device when CE# is low.

1

OE#

Output Enable

To gate the data output buffers.

WE#

Write Enable

To control the Write operations.

1

V

DD

Power Supply

To provide:

5.0V supply (±10%) for SST28SF040A

2.7V supply (2.7-3.6V) for SST28VF040A

V

SS

Ground

T2.2 310

1. This pin is internally pull-up with a resistor.