| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: TDA7490 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

TDA7490

25W + 25W STEREO CLASS-D AMPLIFIER

50W MONO IN BTL

PRODUCT PREVIEW

25W + 25W OUTPUT POWER:

R

L

= 8

/4

;

THD = 10%

HIGH EFFICIENCY

WIDE SUPPLY VOLTAGE RANGE (FROM

±

10 TO

±

25V)

SPLIT SUPPLY

TURN OFF/ON POP FREE

ST-BY AND MUTE FEATURES

SHORT CIRCUIT PROTECTION ACROSS

THE LOAD

THERMAL OVERLOAD PROTECTION

EXTERNALLY SINCHRONIZABLE

BRIDGE CONFIGURATION

DESCRIPTION

The TDA7490 is a dual audio class D amplifier

assembled in Flexiwatt 25 package; it is specially

designed for high efficiency application mainly for

TV and Home Stereo sets.

This is preliminary information on a new product now in development. Details are subject to change without notice.

December 1999

Æ

PWM-stage1

G=2.5

PREAMPLIFIER1

INTEGRATOR1

R21 4.7K

C26 470pF C25 470pF

R20

68K

R17 52.3K

C23

2200

µ

F

C22

100nF

C21

2200

µ

F

R4

130K

L1 30

µ

INPUT1

OSC

C19

560pF

C20

33nF

C18 330pF

C17

24pF

C16 330pF

R15

100

-V

CC

R14 22K

R12 22K

C10

220nF

OUT1

PWM-stage2

L2 30

µ

OUT2

C29

220nF

R13

10K

C15

560pF

R11

100

-V

CC

EXT_CK

G=2.5

PREAMPLIFIER2

C8 470pF

C9 470pF

R6

68K

R5 4.7K

C14

33nF

R9 52.3K

+V

CC

-V

CC

+V

CC

+V

CC

-V

CC

C28

2200

µ

F

C12

2200

µ

F

C11

100nF

C1 330nF

C2

1nF

STBY

MUTE

R2

30K

C27

2.2

µ

F

R1 10K

C3

100nF

C4

100nF

INPUT2

C5 330nF

C6

1nF

-V

CC

-V

CC

D98AU978A

7

9

14

2

4

6

10

12

13

16

1

25

18

19

17

20

24

22

21

23

15

8

11

3

5

INTEGRATOR2

R3

10K

C7 100nF

R1 10K

R 6.8

Figure 1. Test and application circuit. (Stereo Configuration)

Flexiwatt 25

ORDERING NUMBER: TDA7490

1/9

PWM-stage

PRE

+

-

-

+

470pF

470pF

R4

68K

R5 52.3K

L9 30

µ

INPUT

C23

235nF

PWM-stage

L10 30

µ

C26

470nF

dumping

(common

mode)

The LC filter is optimized for 8

(<->LC filter for 4

in single-ended)

It hos to be changed for other loads

C24

235nF

C29

470nF

R28

10

R27

10

R25

Rload

PRE

470pF

470pF

R61

68K

R62 52.3K

D99AU1081

7

9

10

18

19

17

23

3

R63

4.7K

Int.

Int.

C40

C60

C59

C41

Figure 2. Test and application circuit. (Bridge Configuration)

ABSOLUTE MAXIMUM RATINGS

Symbol

Parameter

Value

Unit

V

CC

DC Supply Voltage (no signal)

±

30

V

P

tot

Power Dissipation T

case

= 70∞C

35

W

T

stg

, T

j

Storage and Junction Temperature

≠40 to 150

∞C

T

op

Operating Temperature Range

0 to 70

∞C

V

6,8,10,18

Maximum Voltage on pins # 6,8,10,18 referred to GND

±

5

V

THERMAL DATA

Symbol

Parameter

Typ.

Max.

Unit

R

th j-case

Thermal Resistance Junction-case

1

∞C/W

TDA7490

2/9

D97AU816B

-V

CC

-V

CC

OUT1

+V

CC

BOOT1

STBY-MUTE

FEED1

OSC

FEED2

IN1

T1

+5V

GND

CURREF

T2

-5V

FEED3

IN2

FEED4

N.C.

BOOT2

+V

CC

OUT2

-V

CC

Vreg

1

25

PIN CONNECTION (Top view)

PIN FUNCTIONS

N.

Name

Function

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

-V

CC sign/sub

-V

CCpow1

out 1

+V

CCpow1

BOOT1

STBY-MUTE

FEED1

OSC

FEED2

IN1

T1

+5V

GND

CURREF

T2

-5V

FEED3

IN2

FEED4

NC

BOOT2

+V

CCpow2

OUT2

-V

CCpow2

V

reg

Negative signal/substrate supply

Negative power supply CH1

PWM output of CH1

Positive power supply CH1

Bootstrap CH1

Control State Pin

Feedback pin 1 CH1

Master Oscillator Setting Freequency Pin (or external sync.)

Feedback pin2 CH1

Input CH1

Triangular waveform CH1

+5V regulator (only for internal purposes)

Signal ground

Setting current resistor

Triangular waveform CH2

-5V regulator (only for internal purposes)

Feedback pin1 CH2

Input CH2

Feedback pin2 CH2

Not connected

Bootstrap CH2

Positive power supply CH2

PWM output of CH2

Negative power supply CH2

10V regulator

TDA7490

3/9

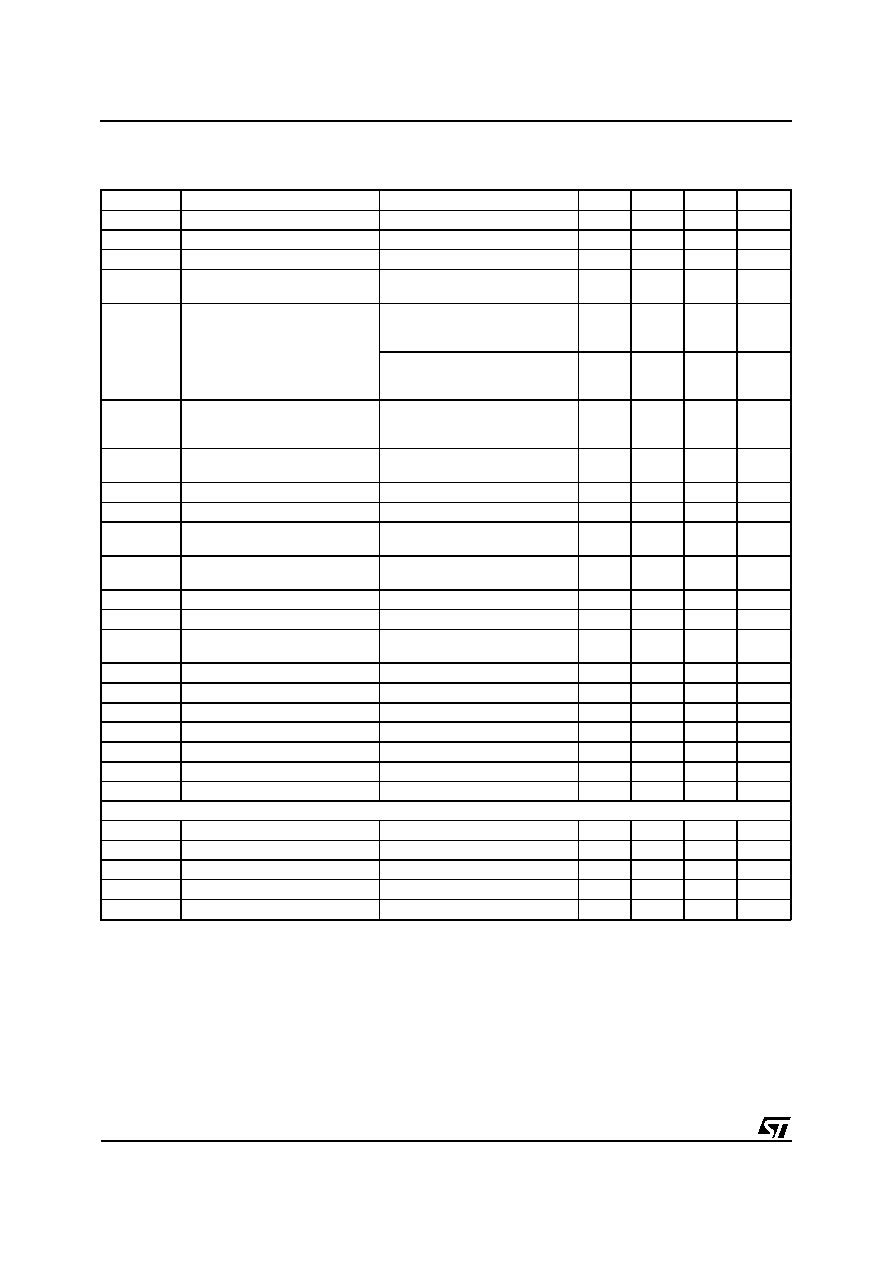

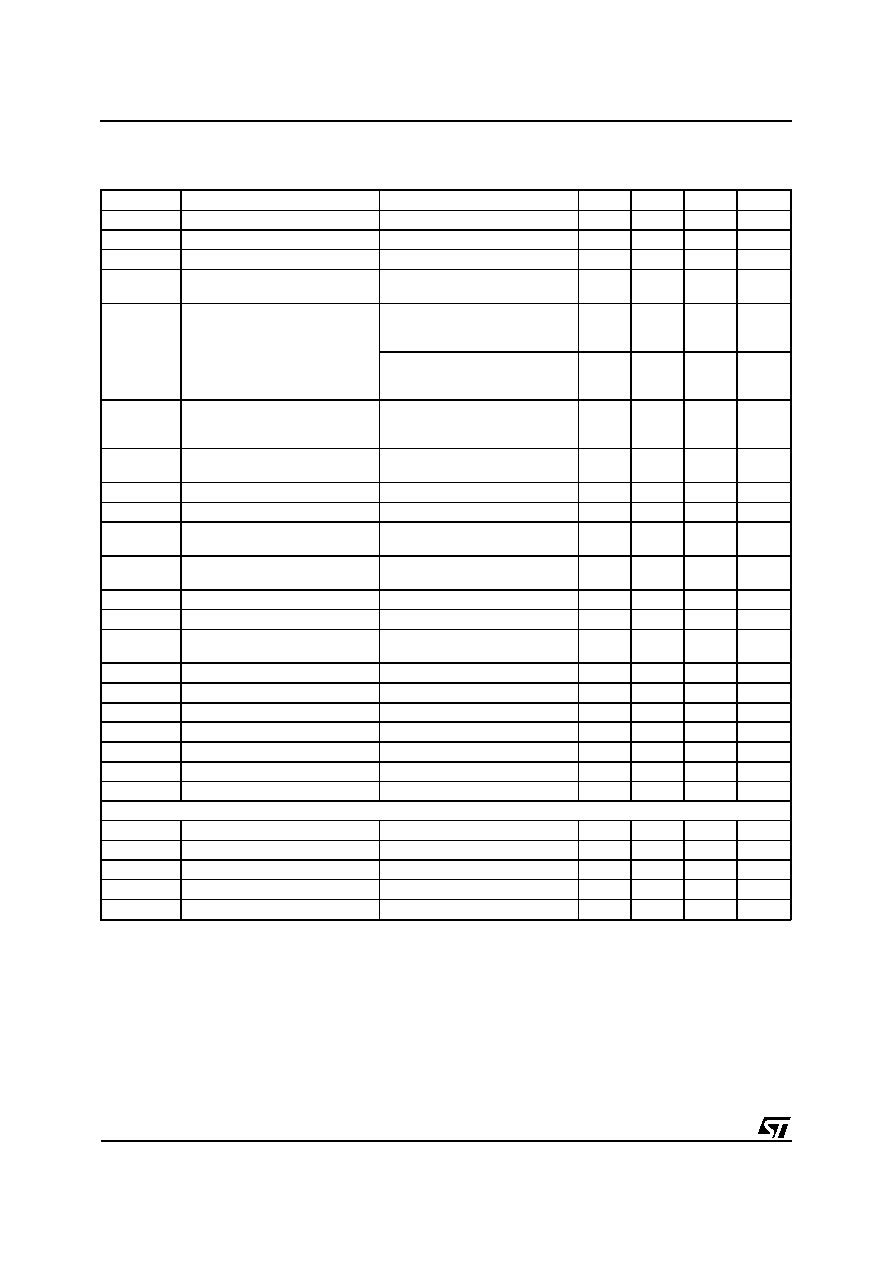

ELECTRICAL CHARACTERISTICS (Refer to the test circuit, V

CC

=

±

21V; RL = 8

; Demod. filter L =

30mH, C = 220nF; f = 1KHz; fsw = 200kHz; Tamb = 25∞`C unless otherwise specified.)

Symbol

Parameter

Test Condition

Min.

Typ.

Max.

Unit

V

S

Supply Range

±

10

±

25

V

I

q

Total Quiescent Current

R

L

=

no LC filter

70

120

mA

V

OS

Output Offset Voltage

≠150

+150

mV

P

O

Output Power

THD = 10%

THD = 1%

25

18

W

W

P

O(BTL)

Output Power in Bridge

Configuration

Vs =

±

22V; R

L

= 16

THD = 10%

THD = 1%

50

40

W

W

Vs =

±

17V; R

L

= 8

THD = 10%

THD = 1%

50

40

W

W

P

O

(1)

Output Power

R

L

= 4

V

CC

=

±

16V

THD = 10%

THD = 1%

25

18

W

W

P

D

Maximum Dissipated Power

V

CC

=

±

21V; R

L

= 8

P

O

= 25W + 25W; THD = 10%

6

W

(2)

Efficiency (*)

P

O

= 25W + 25W

89

%

THD

Total Harmonic Distortion

R

L

= 8

; P

O

= 1W

0.1

%

I

max

Overcurrent Protection

Threshold

R

L

= 0

3.5

5

A

T

j

Thermal Shut-down Junction

Temperature

150

∞C

G

V

Closed Loop Gain

30

dB

G

V

(3)

Gain Matching

-1

+1

dB

e

N

Total Input Noise

R

G

= 50

A Curve

f = 20Hz to 22KHz

7

12

µ

V

µ

V

C

T

Cross talk

f = 1KHz, P

O

= 1W

55

dB

R

i

Input Resistance

30

k

SVR

Supply Voltage Rejection

f = 100Hz; V

r

= 0.5

60

dB

V

rmax

Overvoltage Threshold

(5)

55

60

V

T

r

, T

f

Rising and Falling Time

50

ns

R

DSON

Power Transistor on Resistance

0.4

F

SW

(4)

Switching Frequency Range

100

200

230

KHz

MUTE & STAND-BY FUNCTIONS

V

ST-BY

Stand-by range

0

0.7

V

V

MUTE

Mute Range

1.7

2.5

V

V

PLAY

Play Range

4

5

V

A

MUTE

Mute Attenuation

60

dB

I

qST-BY

Quiescent Current @ Stand-by

3

mA

*: P

O

= measured across the load using the following inductor:

COIL58120 MPPA 2 (magnectics) TURNS = 20 ¯ 1mm

(1) L = 15

µ

H, C = 470nF

(2)

Top

= 90% where V

CC

=

±

25V; R

L

= 8

; P

O

= 43W + 43W; THD = 20%

(3)

Gv is intended with R2, R17, R5, R9 1% precision

(4) F

SW

= 0.25

(1/(300ns + R13

( C17 + 76pF)

0.85)

(5) V

RMAX

= (+V

CC

) - (-V

CC

) when V

R

V

RMAX

the device goes in Stand-By mode

TDA7490

4/9

Figure 3. P.C. Board and component layout of the Figs. 1, 2.

(for Stereo and Bridge compatible configuration)

C

O

M

P

O

N

E

N

T

S

I

D

E

S

O

L

D

E

R

S

I

D

E

TDA7490

5/9