| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: TC660EPA | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Document Outline

- Return to Contents

- List of Figures

- 1. TC660 Test Circuit (Inverter)

- 2. Idealized Switched Capacitor

- 3. Simple Negative Converter

- 4. Paralleling Devices Lowers Output Impedance

- 5. Increased Output Voltage by Cascading Devices

- 6. External Clocking

- 7. Lowering Oscillator Frequency

- 8. Positive Voltage Doubler

- 9. Improved Voltage Doubler

- 10. Combined Negative Converter and Positive Multiplier

- 11. Positive Voltage Multiplier

- Features

- Applications

- Pin Configuration (DIP and SOIC)

- Functional Block Diagram

- General Description

- Ordering Information

- Absolute Maximum Ratings

- Electrical Characteristics: Specifications Measured Over Operating Temperature Range With, V + = 5V, COSC = Open, C1, C2 = 150mF

- Typical Characteristics

- Pin Description

- Circuit Description

- Theoretical Power Efficiency Considerations

- Dos and Don'ts

- Simple Negative Voltage Converter

- Paralleling Devices

- Cascading Devices

- Changing the TC660 Oscillator Frequency

- Positive Voltage Doubler

- Combined Negative Voltage Conversion and Positive Supply Multiplication

- Efficient Positive Voltage Multiplication/Conversion

4-5

TELCOM SEMICONDUCTOR, INC.

7

6

5

4

3

1

2

8

TC660

100mA CHARGE PUMP DC-TO-DC VOLTAGE CONVERTER

FEATURES

s

Pin Compatible with TC7660

s

High Output Current ..................................... 100mA

s

Converts (+1.5V to 5.5V) to (≠ 1.5V to ≠ 5.5V)

s

Power Efficiency @100mA ......................... 88% typ

s

Low Power Consumption ................ 200

µ

A @ 5 V

IN

s

Low Cost and Easy to Use

-- Only Two External Capacitors Required

s

Selectable Oscillator Frequency ....... 10kHz/90kHz

s

ESD Protection ................................................... 4kV

APPLICATIONS

s

Laptop Computers

s

µ

P Based Controllers

s

Process Instrumentation

s

Automotive Instruments

GENERAL DESCRIPTION

The TC660 DC-to-DC voltage converter generates a

negative voltage supply, that can support a 100mA maxi-

mum load, from a positive voltage input of 1.5V to 5.5V. Only

two external capacitors are required.

Power supply voltage is stored on an undedicated

capacitor then inverted and transferred to an output reser-

voir capacitor. The on-board oscillator normally runs at a

frequency of 10kHz with V

+

at 5V. This frequency can be

lowered by the addition of an external capacitor from OSC

(pin 7) to ground, or raised to 90kHz by connecting the

frequency control pin (FC) to V

+

, in order to optimize capaci-

tor size, quiescent current, and output voltage ripple

frequency. Operation using input voltage between 1.5V and

3.0V is accommodated by grounding the LV input (pin 6).

Operation at higher input voltages (3.0V to 5.5V) is accom-

plished by leaving LV open.

The TC660 open circuit output voltage is within 0.1% of

the input voltage with the output open-circuited. Power

conversion efficiency is 98% when output load is between

2mA and 5mA.

1

2

3

4

8

7

6

5

TC660CPA

TC660EPA

FC

CAP +

GND

CAP ≠

VOUT

LV

OSC

+

V

1

2

3

4

8

7

6

5

TC660COA

TC660EOA

FC

CAP +

GND

CAP ≠

VOUT

LV

OSC

+

V

TC660

GND

INTERNAL

VOLTAGE

REGULATOR

RC

OSCILLATOR

VOLTAGE≠

LEVEL

TRANSLATOR

˜

2

V + CAP +

8

2

7

6

OSC

LV

3

LOGIC

NETWORK

VOUT

5

CAP ≠

4

1

FC

FUNCTIONAL BLOCK DIAGRAM

PIN CONFIGURATION (DIP and SOIC)

ORDERING INFORMATION

Part No.

Package

Temp. Range

TC660COA

8-Pin SOIC

0

∞

C to +70

∞

C

TC660CPA

8-Pin Plastic DIP

0

∞

C to +70

∞

C

TC660EOA

8-Pin SOIC

≠ 40

∞

C to +85

∞

C

TC660EPA

8-Pin Plastic DIP

≠ 40

∞

C to +85

∞

C

TC7660EV

Evaluation Kit for

Charge Pump Family

TC660-2 9/10/96

EVALUATION

KIT

AVAILABLE

4-6

TELCOM SEMICONDUCTOR, INC.

ELECTRICAL CHARACTERISTICS:

Specifications Measured Over Operating Temperature Range With,

V

+

= 5V, C

OSC

= Open, C1, C2 = 150

µ

F, FC = Open, Test Circuit

(Figure 1), unless otherwise indicated.

Symbol

Parameter

Test Conditions

Min

Typ

Max

Unit

I

+

Supply Current

R

L

=

FC pin = OPEN or GND

--

200

500

µ

A

FC pin = V

+

--

1

3

mA

V

+

Supply Voltage Range

LV = HIGH, R

L

= 1 k

3

--

5.5

V

LV = GND, R

L

= 1 k

1.5

--

5.5

LV = OUT, R

L

= 1 k

(Figure 9)

2.5

--

5.5

R

OUT

Output Source Resistance

I

OUT

= 100mA

--

6.5

10

I

OUT

Output Current

V

OUT

< ≠ 4V

100

--

--

mA

F

OSC

Oscillator Frequency

Pin 7 open; Pin 1 open or GND

--

10

--

kHz

Pin 1 = V

+

--

90

--

I

OSC

Input Current

Pin 1 open

--

+1.1

--

µ

A

Pin 1 = V

+

--

+5

--

P

EFF

Power Efficiency (Note 4)

R

L

= 1 k

connected between V

+

& V

OUT

96

98

--

%

R

L

= 500

connected between V

OUT

& GND

92

96

--

I

L

= 100mA to GND

--

88

--

V

OUT

E

FF

Voltage Conversion Efficiency

R

L

=

99

99.9

--

%

NOTES: 1. Connecting any input terminal to voltages greater than V

+

or less than GND may cause destructive latch-up. It is recommended that no

inputs from sources operating from external supplies be applied prior to "power up" of the TC660.

2. Derate linearly above 50

∞

C by 5.5 mW/

∞

C.

3. To prevent damaging the device, do not short V

OUT

to V

+

.

4. To maximize output voltage and efficiency performance, use low ESR capacitors for C

1

and C

2

.

ABSOLUTE MAXIMUM RATINGS*

Supply Voltage ........................................................... +6V

LV, FC, OSC Input

Voltage (Note 1) ....................... V

OUT

≠ 0.3V to (V

+

+0.3V)

Current Into LV (Note 1) ...................... 20

µ

A for V

+

>3.5V

Output Short Duration (V

SUPPLY

5.5V) (Note 3) .. 10 Sec

Power Dissipation (Note 2) (T

A

70

∞

C)

SOIC ............................................................... 470mW

Plastic DIP ...................................................... 730mW

Operating Temperature Range

C Suffix .................................................. 0

∞

C to +70

∞

C

E Suffix ............................................. ≠ 40

∞

C to +85

∞

C

Storage Temperature Range ................ ≠ 65

∞

C to +150

∞

C

Lead Temperature (Soldering, 10 sec) ................. +300

∞

C

*Static-sensitive device. Unused devices must be stored in conductive

material. Protect devices from static discharge and static fields. Stresses

above those listed under "Absolute Maximum Ratings" may cause perma-

nent damage to the device. These are stress ratings only and functional

operation of the device at these or any other conditions above those

indicated in the operation sections of the specifications is not implied.

Exposure to absolute maximum rating conditions for extended periods may

affect device reliability.

TC660

100mA CHARGE PUMP DC-TO-DC

VOLTAGE CONVERTER

4-7

TELCOM SEMICONDUCTOR, INC.

7

6

5

4

3

1

2

8

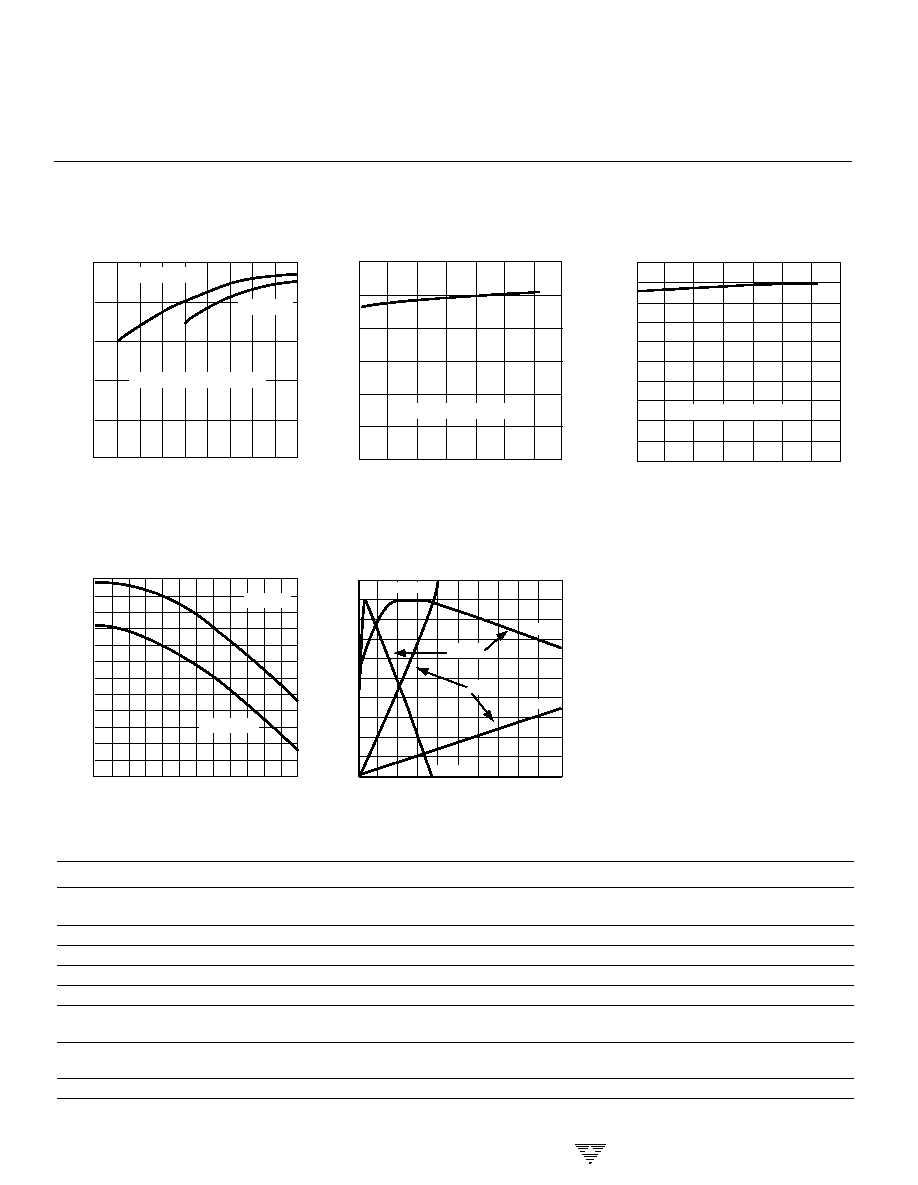

TYPICAL CHARACTERISTICS

All curves are generated using the test circuit of Figure 1 with V

+

= 5V, LV = GND, FC = open, and T

A

= +25

∞

C, unless

otherwise noted.

Supply Current vs.

Supply Voltage

1)

Output Voltage Drop

vs. Load Current

4)

Output Source Resistance

vs. Supply Voltage

7)

Output Source Resistance

vs. Temperature

8)

Oscillator Frequency

vs. Supply Voltage

9)

Output Voltage vs.

Oscillator Frequency

5)

Efficiency vs.

Oscillator Frequency

6)

2)

3)

Supply Current vs.

Oscillator Frequency

Efficiency vs.

Load Current

SUPPLY CURRENT (

µ

A)

SUPPLY CURRENT (

µ

A)

SUPPLY VOLTAGE (V)

LOAD CURRENT (mA)

OSCILLATOR FREQUENCY (kHz)

EFFICIENCY (%)

OUTPUT VOLTAGE DROP

FROM SUPPLY VOLTAGE (V)

OUTPUT SOURCE RESISTANCE (

)

SUPPLY VOLTAGE (V)

100

92

84

76

68

60

0

40

20

100

80

60

600

300

400

500

100

200

0

1.5

2.5

2.0

3.5

5.0

4.5

4.0

3.0

5.5

10,000

1000

100

10

1

0.01

0.1

1

10

100

LV = GND

LV = OPEN

DOUBLER MODE

LV = OUT

INVERTING MODE

DOUBLER MODE

16

14

12

10

8

6

4

TEMPERATURE (

∞

C)

OUTPUT SOURCE RESISTANCE (

)

0

20

40

-20

-40

80

60

100

SUPPLY VOLTAGE (V)

OSCILLATOR FREQUENCY (kHz)

12

10

8

6

4

2

0

1.0

2.0

1.5

2.5 3.0 3.5 4.0 4.5 5.0 5.5

OUTPUT VOLTAGE (V)

OSCILLATOR FREQUENCY (kHz)

OSCILLATOR FREQUENCY (kHz)

POWER EFFICIENCY (%)

V+ = 5.5V

V+ = 3.5V

V+ = 4.5V

V+ = 2.5V

V+ = 1.5V

LOAD CURRENT (mA)

2.0

1.6

1.2

0.8

0.4

0

0

40

20

100

80

60

15

12

9

6

3

0

0.5

1.5

1.0

2.0

3.0 3.5 4.0

2.5

5.5

5.0

4.5

V+ = 5.5V

V+ = 3.5V

V+ = 4.5V

V+ = 2.5V

V+ = 1.5V

-5.0

-4.0

-4.5

-3.5

-3.0

0.1 0.2 0.4

1

4

10 20 40

2

100

100

96

92

88

84

80

76

72

68

64

60

0.1 0.2 0.4

1

4

10 20 40

2

100

ILOAD = 10mA

ILOAD = 10mA

ILOAD = 1mA

LV GROUNDED

FC = OPEN, OSC = OPEN

LV OPEN

ILOAD = 1mA

ILOAD = 80mA

ILOAD =

80mA

V+ = 1.5VDC

V+ = 3VDC

V+ = 5VDC

TC660

100mA CHARGE PUMP DC-TO-DC

VOLTAGE CONVERTER

4-8

TELCOM SEMICONDUCTOR, INC.

TC660

100mA CHARGE PUMP DC-TO-DC

VOLTAGE CONVERTER

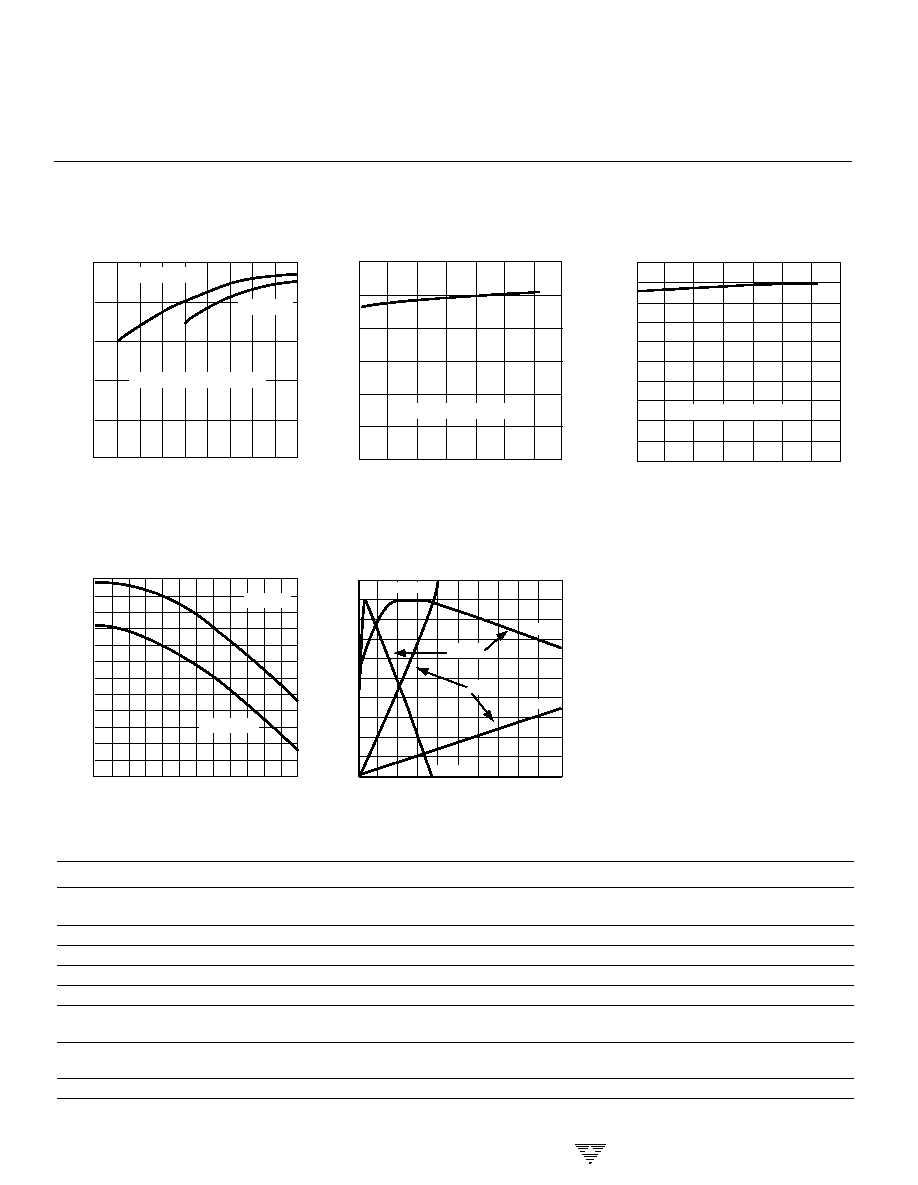

TYPICAL CHARACTERISTICS (Cont.)

Oscillator Frequency

vs. External Capacitance

13)

11)

12)

Oscillator Frequency

vs. Temperature

Oscillator Frequency

vs. Temperature

OSCILATOR FREQUENCY (kHz)

TEMPERATURE (

∞

C)

TEMPERATURE (

∞

C)

OSCILLATOR FREQENCY (kHz)

OSCILLATOR FREQUENCY (kHz)

100

80

60

40

20

0

-40

20

40

-20

0

100

60

80

CAPACITANCE (pF)

100

10

1

0.1

0.01

1

2

5

20

10

10000

2000

100

500

FC = V+

FC = OPEN

Oscillator Frequency

vs. Supply Voltage

10)

SUPPLY VOLTAGE (V)

OSCILLATOR FREQUENCY (kHz)

100

80

60

40

20

0

1.0

2.0

1.5

2.5 3.0 3.5 4.0 4.5 5.0 5.5

LV GROUNDED

FC = V+, OSC = OPEN

LV OPEN

FC = V+, OSC = OPEN

TC7660 and TC660 Output

Voltage and Power Efficiency

vs. Load Current, V

+ =

5V

14)

OUTPUT VOLTAGE (V)

LOAD CURRENT (mA)

-3.0

-3.4

-3.8

-4.2

-4.6

-5.0

0

2.0

60

40

100

80

100

92

84

76

68

60

TC660

TC7660

EFF

VOUT

TC7660

TC660

POWER EFFICIENCY (%)

12

10

8

6

4

2

0

0

20

40

-20

-40

80

60

100

FC= OPEN, OSC = OPEN

PIN DESCRIPTION

Pin No.

Symbol

Description

1

FC

Internal Oscillator frequency control. f

10 kHz when FC

OPEN;

90 kHz when

FC = V

+

. FC has no effect if OSC is overdriven.

2

CAP

+

External capacitor, + terminal

3

GND

Power-Supply Ground (Inverter) or Positive Input (Doubler)

4

CAP

≠

External capacitor, ≠ terminal

5

V

OUT

Negative Voltage output (Inverter) or Ground (Doubler)

6

LV

"Low-Voltage" pin. Connect to GND Pin for inverter operation when V

IN

< 3V; leave

open or GND above 3V. When overdriving OSC, connect to GND.

7

OSC

For external control of internal OSC. Connect ext. C from OSC to GND (close to pkg.)

to reduce frequency of oscillator

8

V

+

Positive Voltage Input (Inverter) or Output (Doubler)

4-9

TELCOM SEMICONDUCTOR, INC.

7

6

5

4

3

1

2

8

TC660

100mA CHARGE PUMP DC-TO-DC

VOLTAGE CONVERTER

Figure 1. TC660 Test Circuit (Inverter)

Figure 2. Idealized Switched Capacitor

V+

GND

S3

S1

S2

S4

C2

VOUT = ≠ VIN

C1

Theoretical Power Efficiency

Considerations

In theory, a voltage multiplier can approach 100%

efficiency if certain conditions are met:

(1) The drive circuitry consumes minimal power.

(2) The output switches have extremely low ON

resistance and virtually no offset.

(3) The impedances of the pump and reservoir

capacitors are negligible at the pump frequency.

The TC660 approaches these conditions for negative

voltage multiplication if large values of C

1

and C

2

are used.

Energy is lost only in the transfer of charge between

capacitors if a change in voltage occurs. The energy lost

is defined by:

E = 1/2 C

1

(V

1

2

≠ V

2

2

)

V

1

and V

2

are the voltages on C

1

during the pump and

transfer cycles. If the impedances of C

1

and C

2

are relatively

high at the pump frequency (refer to Figure 2) compared to

the value of R

L

, there will be a substantial difference in

voltages V

1

and V

2

. Therefore, it is desirable not only to

make C

2

as large as possible to eliminate output voltage

ripple, but also to employ a correspondingly large value for

C

1

in order to achieve maximum efficiency of operation.

1

2

3

4

8

7

6

5

TC660

+

V+

(+5V)

VOUT

C1

150 µF

+

C2

150 µF

IL

RL

IS

V+

Circuit Description

The TC660 contains all the necessary circuitry to com-

plete a voltage inverter (Figure 1), with the exception of two

external capacitors, which may be inexpensive 150

µ

F polar-

ized electrolytic capacitors. Operation is best understood by

considering Figure 2, which shows an idealized voltage

inverter. Capacitor C

1

is charged to a voltage V

+

for the half

cycle when switches S

1

and S

3

are closed. (Note: Switches

S

2

and S

4

are open during this half cycle.) During the second

half cycle of operation, switches S

2

and S

4

are closed, with

S

1

and S

3

open, thereby shifting capacitor C

1

negatively by

V

+

volts. Charge is then transferred from C

1

to C

2

, such that

the voltage on C

2

is exactly V

+

, assuming ideal switches and

no load on C

2

.

The four switches in Figure 2 are MOS power switches;

S

1

is a P-channel device, and S

2

, S

3

and S

4

are N-channel

devices. The main difficulty with this approach is that in

integrating the switches, the substrates of S

3

and S

4

must

always remain reverse-biased with respect to their sources,

but not so much as to degrade their ON resistances. In

addition, at circuit start-up, and under output short circuit

conditions (V

OUT

= V

+

), the output voltage must be sensed

and the substrate bias adjusted accordingly. Failure to

accomplish this would result in high power losses and

possible device latch-up. This problem is eliminated in the

TC660 by a logic network which senses the output voltage

(V

OUT

) together with the level translators, and switches the

substrates of S

3

and S

4

to the correct level to maintain

necessary reverse bias.

To improve low-voltage operation, the "LV" pin should

be connected to GND, disabling the internal regulator. For

supply voltages greater than 3.0V, the LV terminal should

be left open to ensure latch-up-proof operation and prevent

device damage.

4-10

TELCOM SEMICONDUCTOR, INC.

TC660

100mA CHARGE PUMP DC-TO-DC

VOLTAGE CONVERTER

The output characteristics of the circuit in Figure 3 are

those of a nearly ideal voltage source in series with 6.5

.

Thus, for a load current of ≠100mA and a supply voltage of

+5V, the output voltage would be ≠ 4.35V.

The dynamic output impedance of the TC660 is due,

primarily, to capacitive reactance of the charge transfer

capacitor (C

1

). Since this capacitor is connected to the

output for only 1/2 of the cycle, the equation is:

Paralleling Devices

Any number of TC660 voltage converters may be paral-

leled to reduce output resistance (Figure 4). The reservoir

capacitor, C

2

, serves all devices, while each device requires

its own pump capacitor, C

1

. The resultant output resistance

would be approximately:

2

2

f

C

1

X

C

= = 0.21

,

where f = 10 kHz and C

1

= 150

µ

F.

Figure 4. Paralleling Devices Lowers Output Impedance

Dos and Don'ts

∑ Do not exceed maximum supply voltages.

∑ Do not connect the LV terminal to GND for supply

voltages greater than 3.0V.

∑ Do not short circuit the output to V

+

in inverting mode

and for more than 10 sec (a very slow startup!) in

doubler mode.

∑ When using polarized capacitors in the inverting mode,

the + terminal of C

1

must be connected to pin 2 of the

TC660 and the + terminal of C

2

must be connected to

GND.

Simple Negative Voltage Converter

Figure 3 shows typical connections to provide a nega-

tive supply where a positive supply is available. A similar

scheme may be employed for supply voltages anywhere in

the operating range of +1.5V to +5.5V, keeping in mind that

pin 6 (LV) is tied to the supply negative (GND) only for supply

voltages below 3.0V.

R

OUT

(of TC660)

n (number of devices)

R

OUT

=

Figure 3. Simple Negative Converter

1

2

3

4

8

7

6

5

TC660

150 µF

+

V

+

150 µF

+

VOUT

*

1. VOUT = ≠V

+

for 1.5V

V

+

5.5V

NOTES:

*

C1

C2

1

2

3

4

8

7

6

5

TC660

V

+

1

2

3

4

8

7

6

5

TC660

C1

RL

C2

C1

"n"

"1"

+

4-11

TELCOM SEMICONDUCTOR, INC.

7

6

5

4

3

1

2

8

TC660

100mA CHARGE PUMP DC-TO-DC

VOLTAGE CONVERTER

clock frequency using TTL logic, the addition of a 10k

pull-

up resistor to V

+

supply is required. Note that the pump

frequency with external clocking, as with internal clocking,

will be 1/2 of the clock frequency. Output transitions occur on

the positive-going edge of the clock.

It is also possible to increase the conversion efficiency

of the TC660 at low load levels by lowering the oscillator

frequency. This reduces the switching losses, and is achieved

by connecting an additional capacitor, C

OSC

, as shown in

Figure 7. Lowering the oscillator frequency will cause an

undesirable increase in the impedance of the pump (C

1

) and

the reservoir (C

2

) capacitors. To overcome this, increase the

values of C

1

and C

2

by the same factor that the frequency

has been reduced. For example, the addition of a 100pF

capacitor between pin 7 (OSC) and GND will lower the

oscillator frequency to 1kHz from its nominal frequency of

10kHz (a multiple of 10), and necessitate a corresponding

increase in the values of C

1

and C

2

.

Positive Voltage Doubler

Figure 5. Increased Output Voltage by Cascading Devices

1

2

3

4

8

7

6

5

V

+

1

2

3

4

8

7

6

5

150

µ

F

150

µ

F

150

µ

F

"n"

"1"

150

µ

F

VOUT

. VOUT = ≠n(V+) for 1.5V

V+

5.5V

NOTE:

*

*

+

+

+

+

TC660

TC660

Figure 6. External Clocking

1

2

3

4

8

7

6

5

TC660

+

V +

+

CMOS

GATE

150

µ

F

VOUT

150

µ

F

OSC

V +

Cascading Devices

The TC660 may be cascaded as shown (Figure 5) to

produce larger negative multiplication of the initial supply

voltage. However, due to the finite efficiency of each device,

the practical limit is 10 devices for light loads. The output

voltage is defined by:

V

OUT

= ≠n (V

IN

)

where n is an integer representing the number of devices

cascaded. The resulting output resistance would be ap-

proximately the weighted sum of the individual TC660 R

OUT

values.

Changing the TC660 Oscillator Frequency

It may be desirable in some applications (due to noise or

other considerations) to increase the oscillator frequency.

Pin 1, the FC pin, may be connected to V

+

to increase

oscillator frequency to 90kHz from a nominal of 10 kHz for

an input supply voltage of 5.0 volts. The oscillator may also

be synchronized to an external clock as shown in Figure 6

and LV must be grounded when overdriving OSC. In a

situation where the designer has generated the external

Figure 7. Lowering Oscillator Frequency

1

2

3

4

8

7

6

5

+

V

+

VOUT

C1

COSC

+

C2

TC660

4-12

TELCOM SEMICONDUCTOR, INC.

TC660

100mA CHARGE PUMP DC-TO-DC

VOLTAGE CONVERTER

Figure 8. Positive Voltage Doubler

Figure 9. Improved Voltage Doubler

1

2

3

4

8

7

6

5

R = 0.1 ≠ 1M

C1

200

R

D

VOUT

= 2 VIN

VIN

C2

TC660

Figure 10. Combined Negative Converter and Positive Multiplier

Figure 9 shows an improved way of using the TC660 as

a voltage doubler.

In this circuit, C1 is first charged to V

IN

and C2 is quickly

brought to within a diode drop of V

IN

(to prevent substrate

reversal) through D. The optional 200

resistor is only to

limit the brief latchup current.

On the next half-cycle, V

IN

is in series with C1; C2 is then

charged to 2 V

IN

. D is now reverse-biased and plays no

further part. For V

IN

< 3V, R may be necessary to ensure

startup.

Combined Negative Voltage Conversion

and Positive Supply Multiplication

Figure 10 combines the functions shown in Figures 3

and 8 to provide negative voltage conversion and positive

voltage multiplication simultaneously. In this instance, ca-

pacitors C

1

and C

3

perform the pump and reservoir func-

tions, respectively, for the generation of the negative volt-

age, while capacitors C

2

and C

4

are pump and reservoir,

respectively, for the multiplied positive voltage. There is a

penalty in this configuration in that the source impedances

of the generated supplies will be somewhat higher due to

the finite impedance of the common charge pump driver at

pin 2 of the device.

Figure 11. Positive Voltage Multiplier

1

2

3

4

8

7

6

5

+

V +

VOUT =

(2 V +) ≠ (2 VF)

C1

D1

+

+

C3

C4

VOUT = ≠V

+

C2

TC660

D2

+

1

2

3

4

8

7

6

5

V+

VOUT =

(2 V+) ≠ (2 VF)

+

C2

D1

D2

+

C1

TC660

Efficient Positive Voltage

Multiplication/Conversion

Since the switches that allow the charge pumping op-

eration are bidirectional, the charge transfer can be per-

formed backward as easily as forward. Figure 11 shows a

TC660 transforming ≠5V to +5V. The only problem here is

that the internal clock and switch-drive section will not

operate until some positive voltage has been generated. A

diode and resistor shown dotted in Figure 11 can be used to

"force" the internal regulator on.

1

2

3

4

8

7

6

5

+

VOUT = ≠V

≠

150

µ

F

+

1 M

V≠ INPUT

C1

150

µ

F

TC660