Document Outline

- features

- description

- logic symbol

- logic diagram (positive logic)

- schematic diagrams of inputs and outputs

- absolute maximum ratings over operating free-air temperature (unless ot\

herwise noted)

- recommended operating conditions

- electrical characteristics over recommended ranges of supply voltage and\

operating free-air temperature (unless otherwise noted)

- switching characteristics, V switching characteristics, V CC = 5 V

- PARAMETER MEASUREMENT INFORMATION

- TYPICAL CHARACTERISTICS

- TYPICAL CHARACTERISTICS

- MECHANICAL DATA

- FK (S-CQCC-N**) LEADLESS CERAMIC CHIP CARRIER

- J (R-GDIP-T**) CERAMIC DUAL-IN-LINE PACKAGE

- W (R-GDFP-F16) CERAMIC DUAL FLATPACK

- IMPORTANT NOTICE

SN55LBC172

QUADRUPLE LOW-POWER DIFFERENTIAL LINE DRIVER

SGLS084C ≠ MARCH 1995 ≠ REVISED JANUARY 2003

1

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

D

Meets Standard EIA-485

D

Designed for High-Speed Multipoint

Transmission on Long Bus Lines in Noisy

Environments

D

Supports Data Rates up to and Exceeding

Ten Million Transfers Per Second

D

Common-Mode Output Voltage Range of

≠ 7 V to 12 V

D

Positive- and Negative-Current Limiting

D

Low Power Consumption . . . 1.5 mA Max

(Output Disabled)

description

The SN55LBC172 is a monolithic quadruple

differential line driver with 3-state outputs. This

device is designed to meet the requirements of the

Electronics Industry Association (EIA) standard

RS-485. The SN55LBC172 is optimized for

balanced multipoint bus transmission at data

rates up to and exceeding 10 million bits per

second. The driver features wide positive and

negative common-mode output voltage ranges,

current limiting, and thermal-shutdown circuitry,

making it suitable for party-line applications in

noisy environments. The device is designed using

the LinBiCMOS

process, facilitating ultralow

power consumption and inherent robustness.

The SN55LBC172 provides positive- and negative-current limiting and thermal shutdown for protection from

line fault conditions on the transmission bus line. This device offers optimum performance when used with the

SN55LBC173M quadruple line receiver.

ORDERING INFORMATION

TA

PACKAGEß

ORDERABLE

PART NUMBER

TOP-SIDE

MARKING

LCCC ≠ FK

Tube

SNJ55LBC172FK

SNJ55LBC172FK

≠55

∞

C to 125

∞

C

CDIP ≠ J

Tube

SNJ55LBC172J

SNJ55LBC172J

CFP ≠ W

Tube

SNJ55LBC172W

SNJ55LBC172W

Package drawings, standard packing quantities, thermal data, symbolization, and PCB design

guidelines are available at www.ti.com/sc/package.

Copyright

1995≠2003, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

1A

1Y

1Z

G

2Z

2Y

2A

GND

V

CC

4A

4Y

4Z

G

3Z

3Y

3A

J OR W PACKAGE

(TOP VIEW)

NC ≠ No internal connection

FK PACKAGE

(TOP VIEW)

19

20

1

3

2

17

18

16

15

14

13

12

11

9

10

5

4

6

7

8

4Y

4Z

NC

G

3Z

1Z

G

NC

2Z

2Y

1Y

1A

NC

4A

GND

NC

3A

3Y

2A

V

CC

LinBiCMOS is a trademark of Texas Instruments Incorporated.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SN55LBC172

QUADRUPLE LOW-POWER DIFFERENTIAL LINE DRIVER

SGLS084C ≠ MARCH 1995 ≠ REVISED JANUARY 2003

2

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

FUNCTION TABLE

(each driver)

INPUT

ENABLES

OUTPUTS

A

G

G

Y

Z

H

H

X

H

L

L

H

X

L

H

H

X

L

H

L

L

X

L

L

H

X

L

H

Z

Z

H = high level, L = low level, X = irrelevant,

Z = high impedance (off)

logic symbol

4A

3A

2A

1A

G

G

4Z

4Y

3Z

3Y

2Z

2Y

1Z

1Y

13

14

11

10

5

6

3

2

15

9

7

1

12

4

1

EN

This symbol is in accordance with ANSI/IEEE Std 91-1984

and IEC Publication 617-12.

Pin numbers shown are for the J or W package.

logic diagram (positive logic)

4A

3A

2A

1A

G

G

15

9

7

1

12

4

4Z

4Y

3Z

3Y

2Z

2Y

1Z

1Y

13

14

11

10

5

6

3

2

4A

3A

2A

1A

G

G

15

9

7

1

12

4

4Z

4Y

3Z

3Y

2Z

2Y

1Z

1Y

13

14

11

10

5

6

3

2

SN55LBC172

QUADRUPLE LOW-POWER DIFFERENTIAL LINE DRIVER

SGLS084C ≠ MARCH 1995 ≠ REVISED JANUARY 2003

3

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

schematic diagrams of inputs and outputs

Input

50

µ

A

VCC

Driver

Output

VCC

200

ALL INPUTS

Y OR Z OUTPUT

≠

+

SN55LBC172

QUADRUPLE LOW-POWER DIFFERENTIAL LINE DRIVER

SGLS084C ≠ MARCH 1995 ≠ REVISED JANUARY 2003

4

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

absolute maximum ratings over operating free-air temperature (unless otherwise noted)

Supply voltage range, V

CC

(see Note 1)

≠0.3 V to 7 V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output voltage range, V

O

≠10 V to 15 V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input voltage range, V

I

≠0.3 V to 7 V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Continuous power dissipation

Internally limited

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating free-air temperature range, T

A

≠55

∞

C to 125

∞

C

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range, T

stg

≠65

∞

C to 150

∞

C

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds

≠65

∞

C to 150

∞

C

. . . . . . . . . . . . . . . . . . . . . . .

Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

The maximum operating junction temperature is internally limited. Use the dissipation rating table to operate below this temperature.

NOTE 1: All voltage values are with respect to GND.

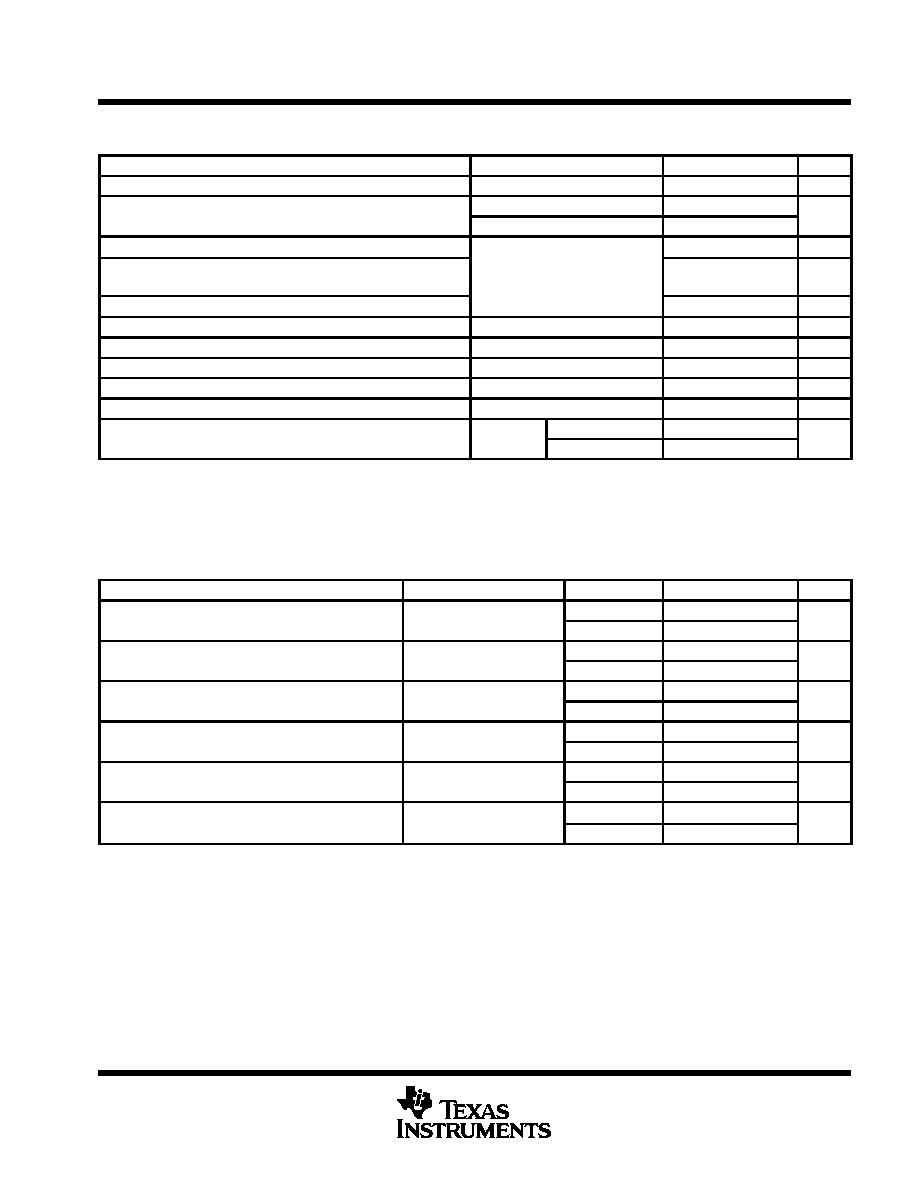

DISSIPATION RATING TABLE

PACKAGE

TA

25

∞

C

POWER RATING

DERATING FACTOR

ABOVE TA=125

∞

C

TA = 125

∞

C

POWER RATING

FK

1375 mW

11.0 mW/

∞

C

275 mW

J

1375 mW

11.0 mW/

∞

C

275 mW

W

1000 mW

8.0 mW/

∞

C

200 mW

recommended operating conditions

MIN

NOM

MAX

UNIT

Supply voltage, VCC

4.75

5

5.25

V

High-level input voltage, VIH

2

V

Low-level input voltage, VIL

0.8

V

Output voltage at any bus terminal (separately or common mode) VO

Y or Z

12

V

Output voltage at any bus terminal (separately or common mode), VO

Y or Z

≠7

V

High-level output current, IOH

Y or Z

≠60

mA

Low-level output current, IOL

Y or Z

60

mA

Continuous total power dissipation

See Dissipation Rating Table

Operating free-air temperature, TA

≠55

125

∞

C

SN55LBC172

QUADRUPLE LOW-POWER DIFFERENTIAL LINE DRIVER

SGLS084C ≠ MARCH 1995 ≠ REVISED JANUARY 2003

5

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

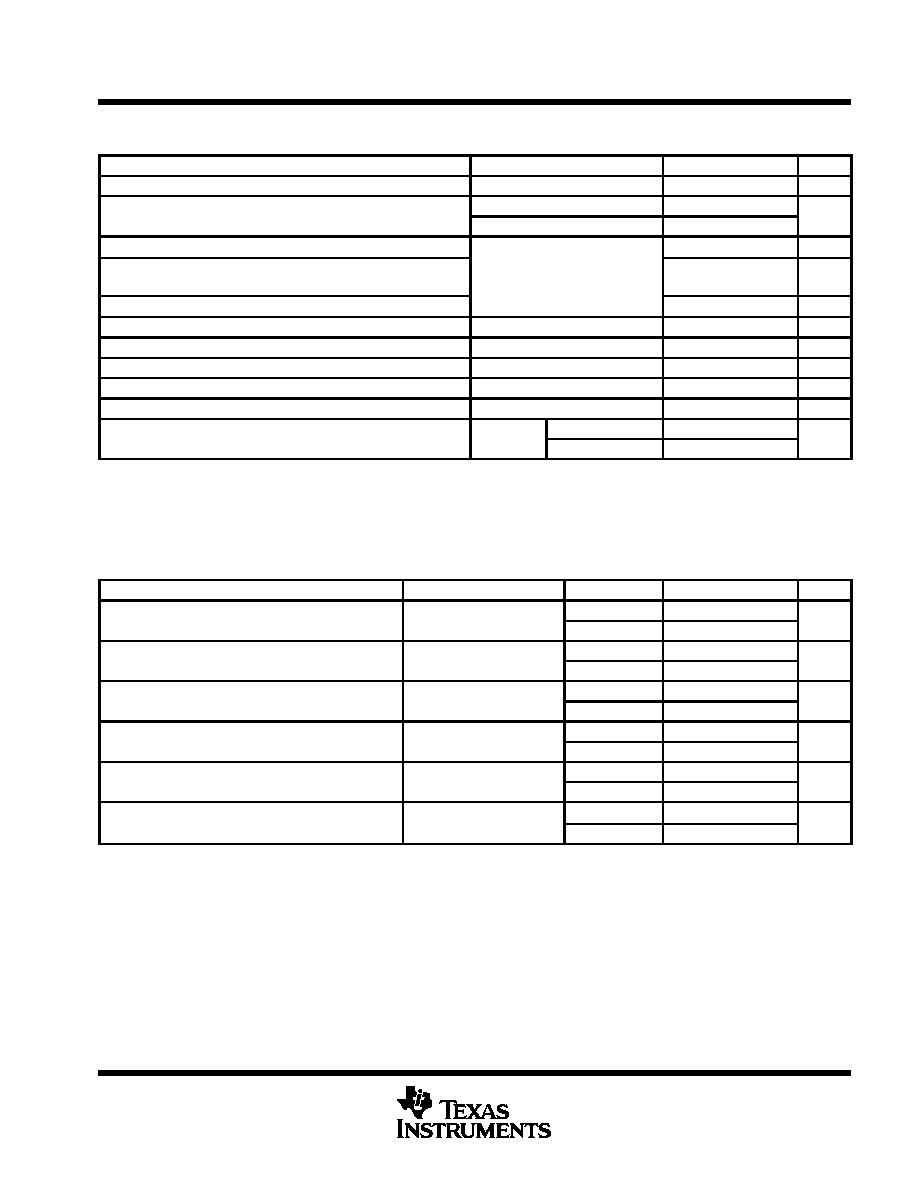

electrical characteristics over recommended ranges of supply voltage and operating free-air

temperature (unless otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

VIK

Input clamp voltage

II = ≠ 18 mA

≠ 1.5

V

|VOD|

Differential output voltage

RL = 54

,

See Figure 1

1.1

1.8

5

V

|VOD|

Differential output voltage

RL = 60

,

See Figure 2

1.1

1.7

5

V

|VOD|

Change in magnitude of differential output voltageß

±

0.2

V

VOC

Common mode output voltage

RL = 54

See Figure 1

3

V

VOC

Common-mode output voltage

RL = 54

,

See Figure 1

≠ 1

V

|VOC|

Change in magnitude of common-mode output voltageß

±

0.2

V

IO

Output current with power off

VCC = 0,

VO = ≠ 7 V to 12 V

±

100

µ

A

IOZ

High-impedance-state output current

VO = ≠ 7 V to 12 V

±

100

µ

A

IIH

High-level input current

VI = 2.4 V

≠ 100

µ

A

IIL

Low-level input current

VI = 0.4 V

≠ 100

µ

A

IOS

Short-circuit output current

VO

=

≠ 7 V to 12 V

±

250

mA

ICC

Supply current (all drivers)

No load

Outputs enabled

7

mA

ICC

Supply current (all drivers)

No load

Outputs disabled

1.5

mA

All typical values are at VCC = 5 V and TA = 25

∞

C.

The minimum VOD specification does not fully comply with EIA-485 at operating temperatures below 0

∞

C. The lower output signal should be used

to determine the maximum signal transmission distance.

ß

|VOD| and

|VOC| are the changes in magnitude of VOD and VOC, respectively, that occur when the input is changed from a high level to a low

level.

switching characteristics, V

CC

= 5 V

PARAMETER

TEST CONDITIONS

TA

MIN

TYP

MAX

UNIT

td(OD) Differential output delay time

RL = 54

See Figure 3

25

∞

C

2

11

20

ns

td(OD) Differential output delay time

RL = 54

,

See Figure 3

≠ 55

∞

C to 125

∞

C

2

40

ns

tt(OD)

Differential output transition time

RL = 54

See Figure 3

25

∞

C

10

15

25

ns

tt(OD)

Differential output transition time

RL = 54

,

See Figure 3

≠ 55

∞

C to 125

∞

C

4

60

ns

tPZH

Output enable time to high level

RL = 110

See Figure 4

25

∞

C

30

ns

tPZH

Output enable time to high level

RL = 110

,

See Figure 4

≠ 55

∞

C to 125

∞

C

40

ns

tPZL

Output enable time to low level

RL = 110

See Figure 5

25

∞

C

30

ns

tPZL

Output enable time to low level

RL = 110

,

See Figure 5

≠ 55

∞

C to 125

∞

C

40

ns

tPHZ

Output disable time from high level

RL = 110

See Figure 4

25

∞

C

60

ns

tPHZ

Output disable time from high level

RL = 110

,

See Figure 4

≠ 55

∞

C to 125

∞

C

115

ns

tPLZ

Output disable time from low level

RL = 110

See Figure 5

25

∞

C

30

ns

tPLZ

Out ut disable time from low level

RL = 110

,

See Figure 5

≠ 55

∞

C to 125

∞

C

55

ns