SN54LVTH240, SN74LVTH240 (Rev. K)

SN54LVTH240, SN74LVTH240

3.3 V ABT OCTAL BUFFERS/DRIVERS

WITH 3 STATE OUTPUTS

SCBS679K - DECEMBER 1996 - REVISED SEPTEMBER 2003

1

POST OFFICE BOX 655303

·

DALLAS, TEXAS 75265

D

Support Mixed-Mode Signal Operation (5-V

Input and Output Voltages With 3.3-V V

CC

)

D

Support Unregulated Battery Operation

Down to 2.7 V

D

Typical V

OLP

(Output Ground Bounce)

<0.8 V at V

CC

= 3.3 V, T

A

= 25

°

C

D

I

off

and Power-Up 3-State Support Hot

Insertion

D

Bus Hold on Data Inputs Eliminates the

Need for External Pullup/Pulldown

Resistors

D

Latch-Up Performance Exceeds 500 mA Per

JESD 17

D

ESD Protection Exceeds JESD 22

- 2000-V Human-Body Model (A114-A)

- 200-V Machine Model (A115-A)

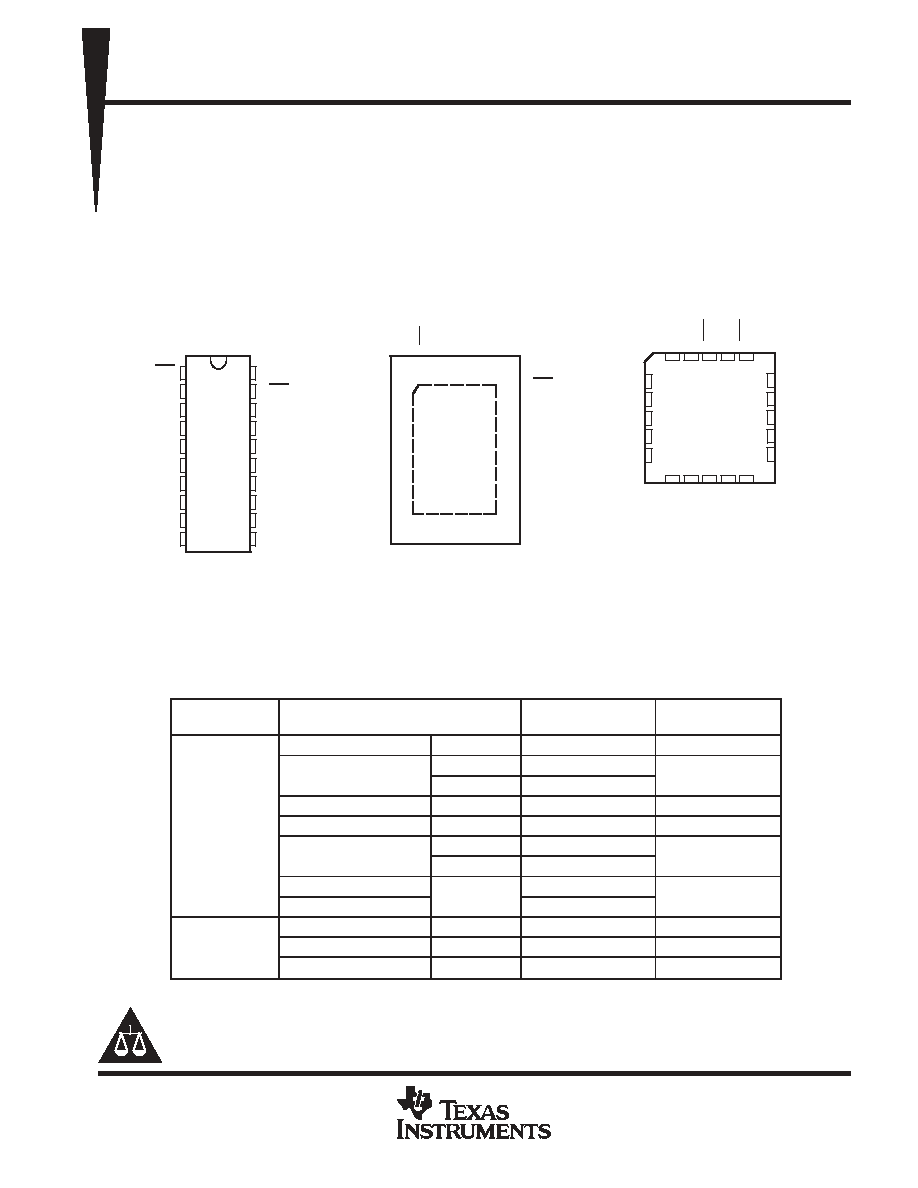

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

1OE

1A1

2Y4

1A2

2Y3

1A3

2Y2

1A4

2Y1

GND

V

CC

2OE

1Y1

2A4

1Y2

2A3

1Y3

2A2

1Y4

2A1

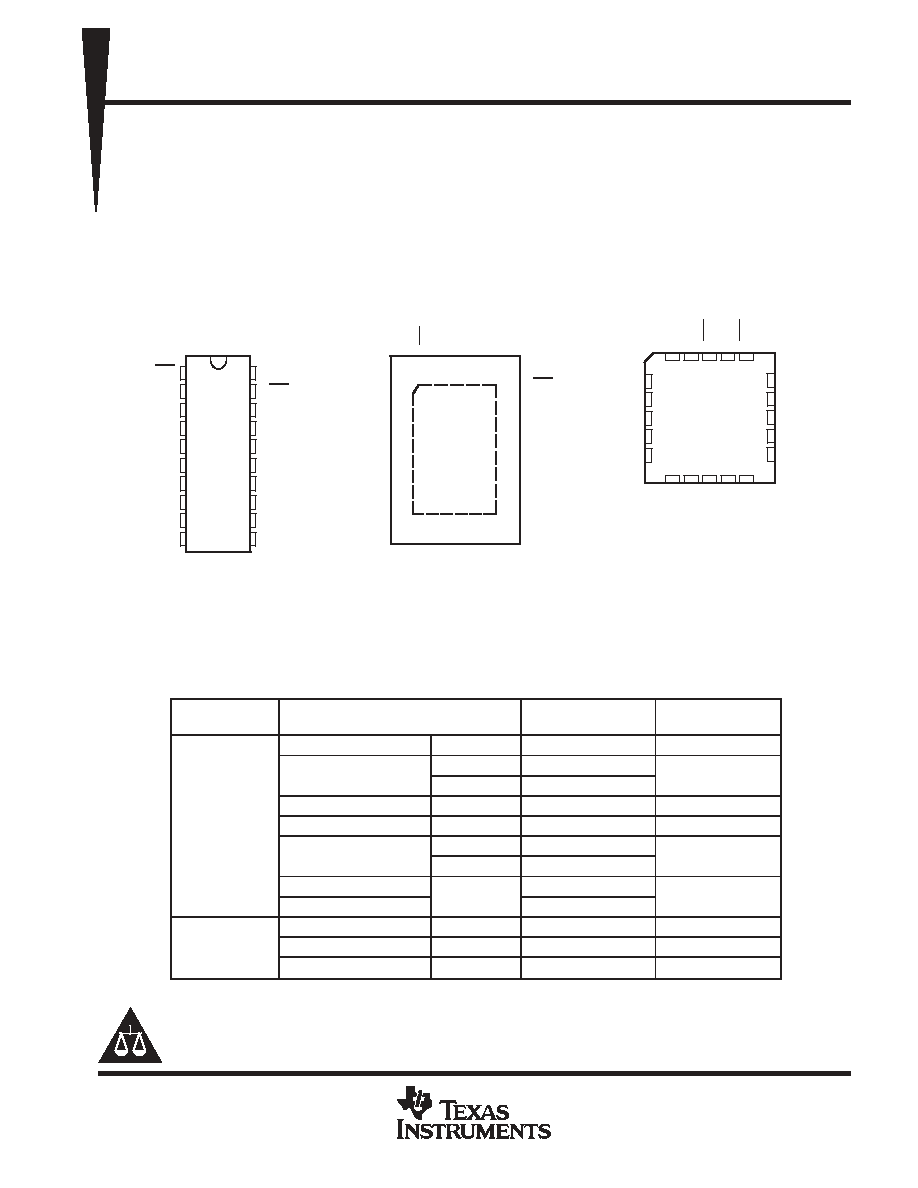

SN54LVTH240 . . . J OR W PACKAGE

SN74LVTH240 . . . DB, DW, NS,

OR PW PACKAGE

(TOP VIEW)

3

2

1 20 19

9 10 11 12 13

4

5

6

7

8

18

17

16

15

14

1Y1

2A4

1Y2

2A3

1Y3

1A2

2Y3

1A3

2Y2

1A4

SN54LVTH240 . . . FK PACKAGE

(TOP VIEW)

2Y4

1A1

1OE

1Y4

2A2

2OE

2Y1

GND

2A1

V

CC

SN74LVTH240 . . . RGY PACKAGE

(TOP VIEW)

1

20

10

11

2

3

4

5

6

7

8

9

19

18

17

16

15

14

13

12

2OE

1Y1

2A4

1Y2

2A3

1Y3

2A2

1Y4

1A1

2Y4

1A2

2Y3

1A3

2Y2

1A4

2Y1

2A1

V

GND

CC

1OE

description/ordering information

These octal buffers and line drivers are designed specifically for low-voltage (3.3-V) V

CC

operation, but with the

capability to provide a TTL interface to a 5-V system environment.

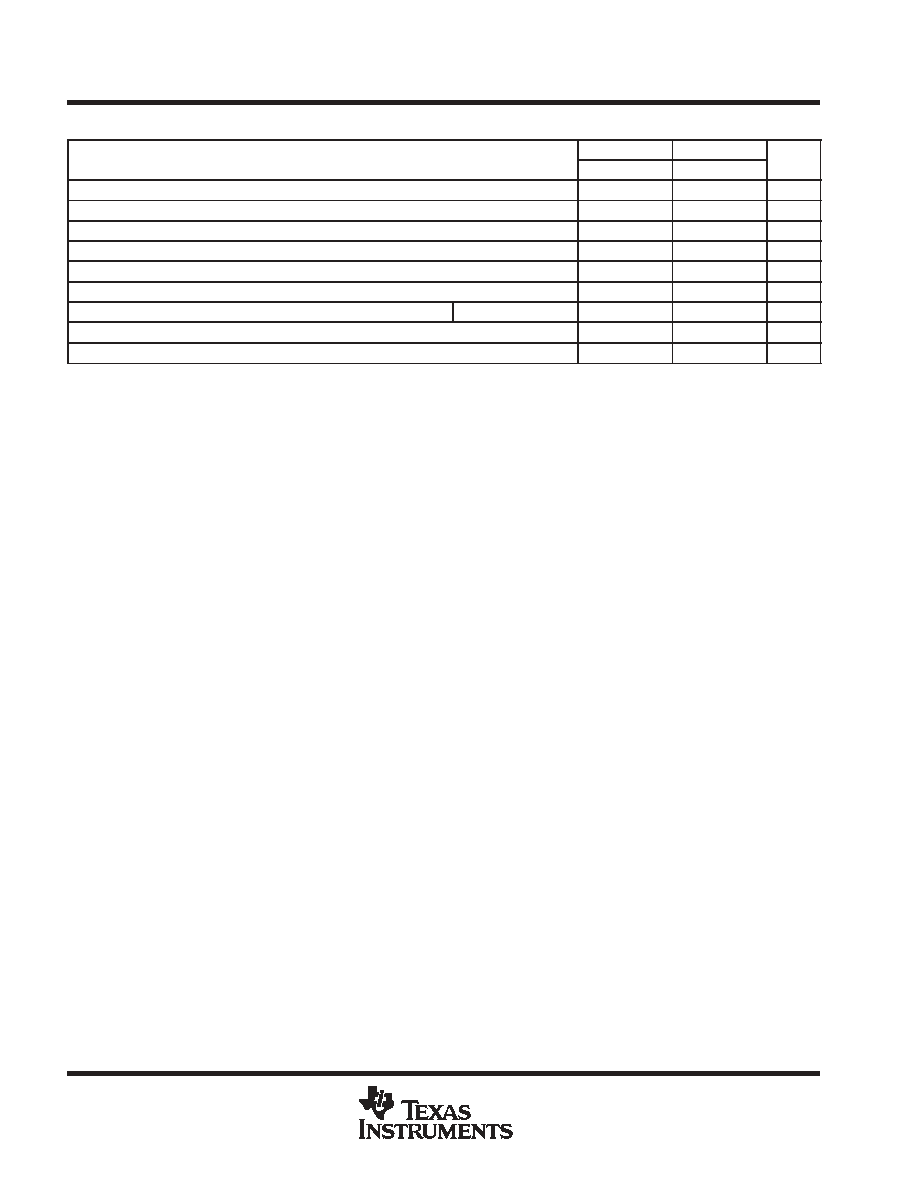

ORDERING INFORMATION

TA

PACKAGE

ORDERABLE

PART NUMBER

TOP-SIDE

MARKING

QFN - RGY

Tape and reel

SN74LVTH240RGYR

LXH240

SOIC - DW

Tube

SN74LVTH240DW

LVTH240

SOIC - DW

Tape and reel

SN74LVTH240DWR

LVTH240

SOP - NS

Tape and reel

SN74LVTH240NSR

LVTH240

-40

°

C to 85

°

C

SSOP - DB

Tape and reel

SN74LVTH240DBR

LXH240

-40 C to 85 C

TSSOP - PW

Tube

SN74LVTH240PW

LXH240

TSSOP - PW

Tape and reel

SN74LVTH240PWR

LXH240

VFBGA - GQN

Tape and reel

SN74LVTH240GQNR

LXH240

VFBGA - ZQN (Pb-free)

Tape and reel

SN74LVTH240ZQNR

LXH240

CDIP - J

Tube

SNJ54LVTH240J

SNJ54LVTH240J

-55

°

C to 125

°

C

CFP - W

Tube

SNJ54LVTH240W

SNJ54LVTH240W

-55 C to 125 C

LCCC - FK

Tube

SNJ54LVTH240FK

SNJ54LVTH240FK

Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are

available at www.ti.com/sc/package.

Copyright

2003, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

On products compliant to MIL PRF 38535, all parameters are tested

unless otherwise noted. On all other products, production

processing does not necessarily include testing of all parameters.

SN54LVTH240, SN74LVTH240

3.3 V ABT OCTAL BUFFERS/DRIVERS

WITH 3 STATE OUTPUTS

SCBS679K - DECEMBER 1996 - REVISED SEPTEMBER 2003

2

POST OFFICE BOX 655303

·

DALLAS, TEXAS 75265

description/ordering information (continued)

These devices are organized as two 4-bit buffer/line drivers with separate output-enable (OE) inputs. When OE

is low, the devices pass data from the A inputs to the Y outputs. When OE is high, the outputs are in the

high-impedance state.

To ensure the high-impedance state during power up or power down, OE should be tied to V

CC

through a pullup

resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver.

Active bus-hold circuitry holds unused or undriven inputs at a valid logic state. Use of pullup or pulldown resistors

with the bus-hold circuitry is not recommended.

These devices are fully specified for hot-insertion applications using I

off

and power-up 3-state. The I

off

circuitry

disables the outputs, preventing damaging current backflow through the devices when they are powered down.

The power-up 3-state circuitry places the outputs in the high-impedance state during power up and power down,

which prevents driver conflict.

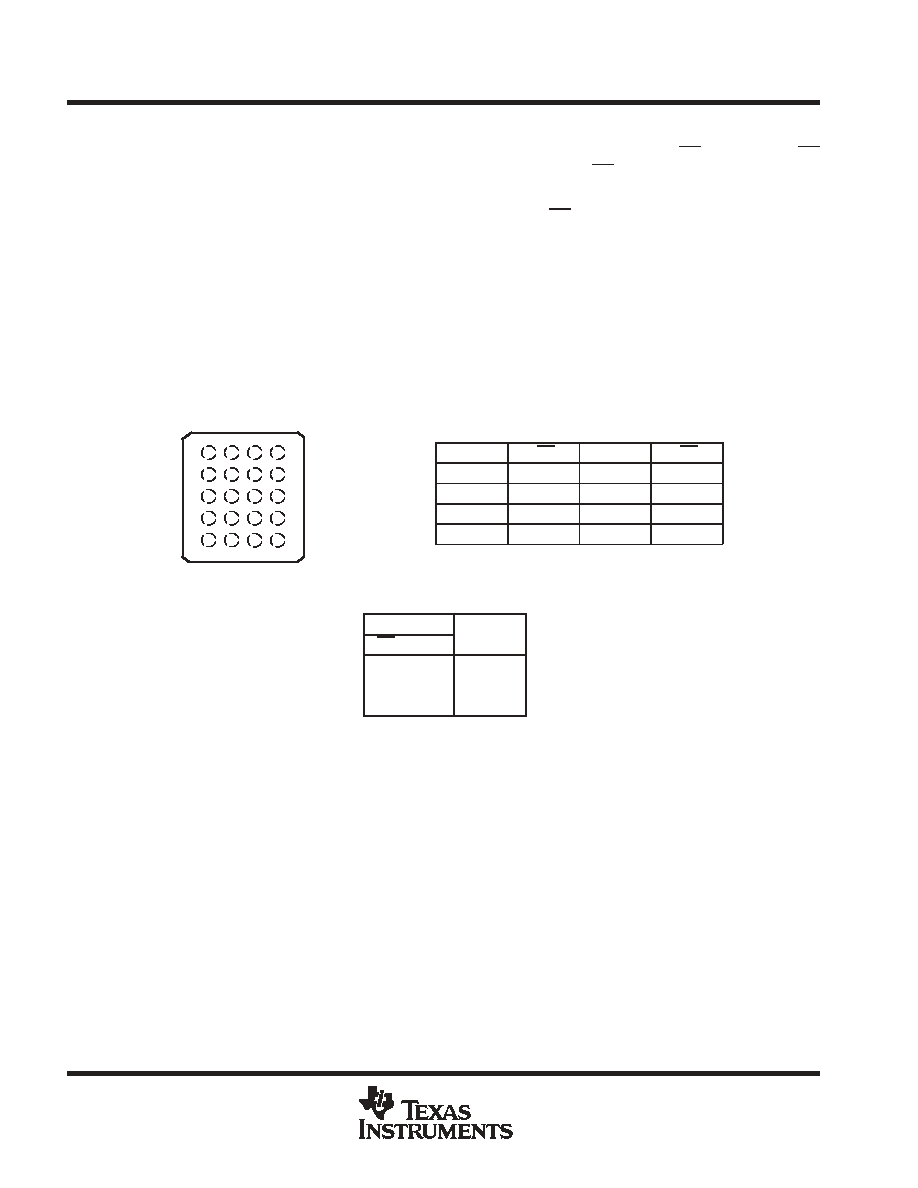

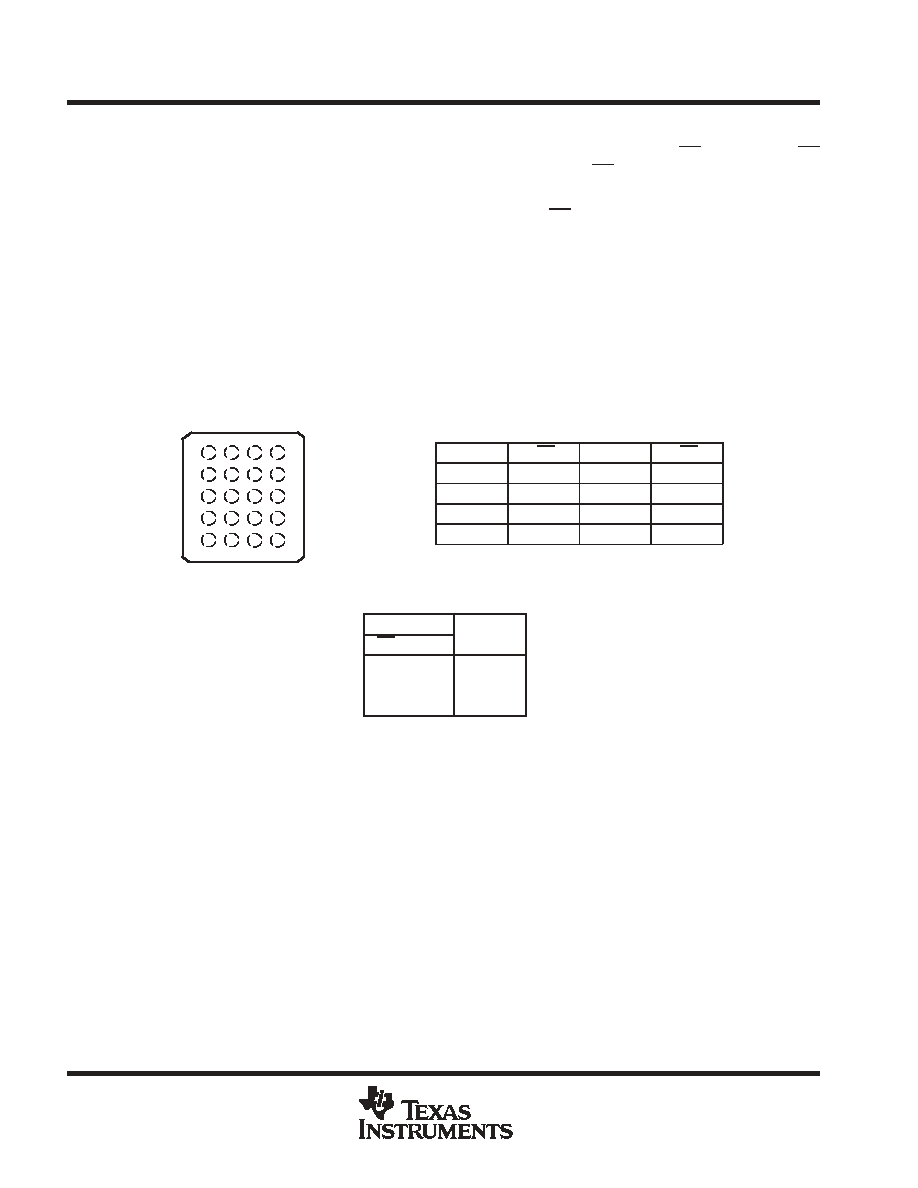

terminal assignments

1

2

3

4

A

1A1

1OE

VCC

2OE

B

1A2

2A4

2Y4

1Y1

C

1A3

2Y3

2A3

1Y2

D

1A4

2A2

2Y2

1Y3

E

GND

2Y1

2A1

1Y4

FUNCTION TABLE

(each 4-bit buffer)

INPUTS

OUTPUT

OE

A

OUTPUT

Y

L

H

L

L

L

H

H

X

Z

SN74LVTH240 . . . GQN OR ZQN PACKAGE

(TOP VIEW)

1

2

3

4

A

B

C

D

E

SN54LVTH240, SN74LVTH240

3.3 V ABT OCTAL BUFFERS/DRIVERS

WITH 3 STATE OUTPUTS

SCBS679K - DECEMBER 1996 - REVISED SEPTEMBER 2003

3

POST OFFICE BOX 655303

·

DALLAS, TEXAS 75265

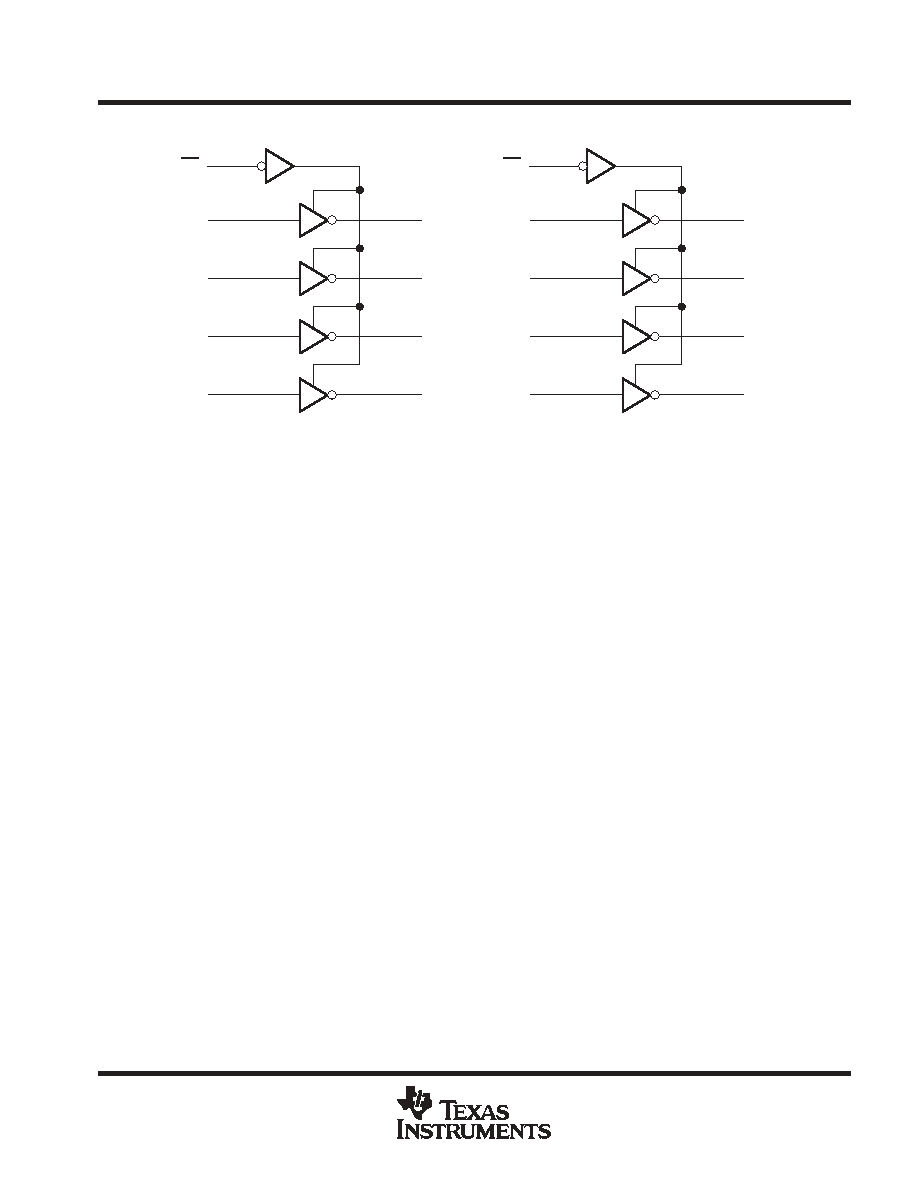

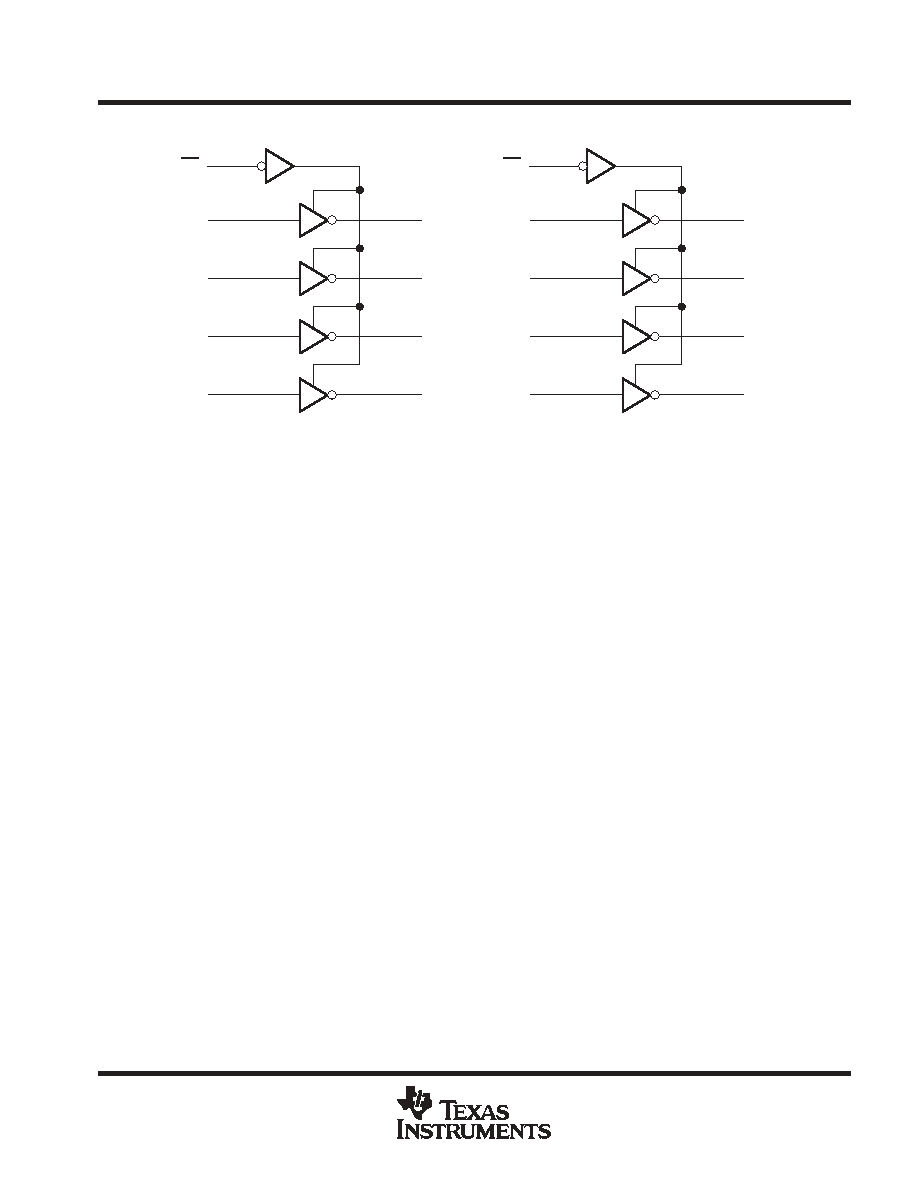

logic diagram (positive logic)

1

2

18

1Y1

1OE

1A1

4

16

1Y2

1A2

6

14

1Y3

1A3

8

12

1Y4

1A4

19

11

9

2Y1

2OE

2A1

13

7

2Y2

2A2

15

5

2Y3

2A3

17

3

2Y4

2A4

Pin numbers shown are for the DB, DW, FK, J, NS, PW, RGY, and W packages.

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

Supply voltage range, V

CC

-0.5 V to 4.6 V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input voltage range, V

I

(see Note 1)

-0.5 V to 7 V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Voltage range applied to any output in the high-impedance

or power-off state, V

O

(see Note 1)

-0.5 V to 7 V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Voltage range applied to any output in the high state, V

O

(see Note 1)

-0.5 V to V

CC

+ 0.5 V

. . . . . . . . . . . . .

Current into any output in the low state, I

O

: SN54LVTH240 96

mA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SN74LVTH240 128

mA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Current into any output in the high state, I

O

(see Note 2): SN54LVTH240

48 mA

. . . . . . . . . . . . . . . . . . . . . . .

SN74LVTH240 64

mA

. . . . . . . . . . . . . . . . . . . . . . .

Input clamp current, I

IK

(V

I

< 0)

-50 mA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output clamp current, I

OK

(V

O

< 0)

-50 mA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Package thermal impedance,

JA

(see Note 3): DB package

70

°

C/W

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

(see Note 3): DW package

58

°

C/W

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

(see Note 3): GQN/ZQN package

78

°

C/W

. . . . . . . . . . . . . . . . . . . . . . . . . . .

(see Note 3): NS package

60

°

C/W

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

(see Note 3): PW package

83

°

C/W

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

(see Note 4): RGY package

37

°

C/W

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range, T

stg

-65

°

C to 150

°

C

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES:

1. The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

2. This current flows only when the output is in the high state and VO > VCC.

3. The package thermal impedance is calculated in accordance with JESD 51-7.

4. The package thermal impedance is calculated in accordance with JESD 51-5.

SN54LVTH240, SN74LVTH240

3.3 V ABT OCTAL BUFFERS/DRIVERS

WITH 3 STATE OUTPUTS

SCBS679K - DECEMBER 1996 - REVISED SEPTEMBER 2003

4

POST OFFICE BOX 655303

·

DALLAS, TEXAS 75265

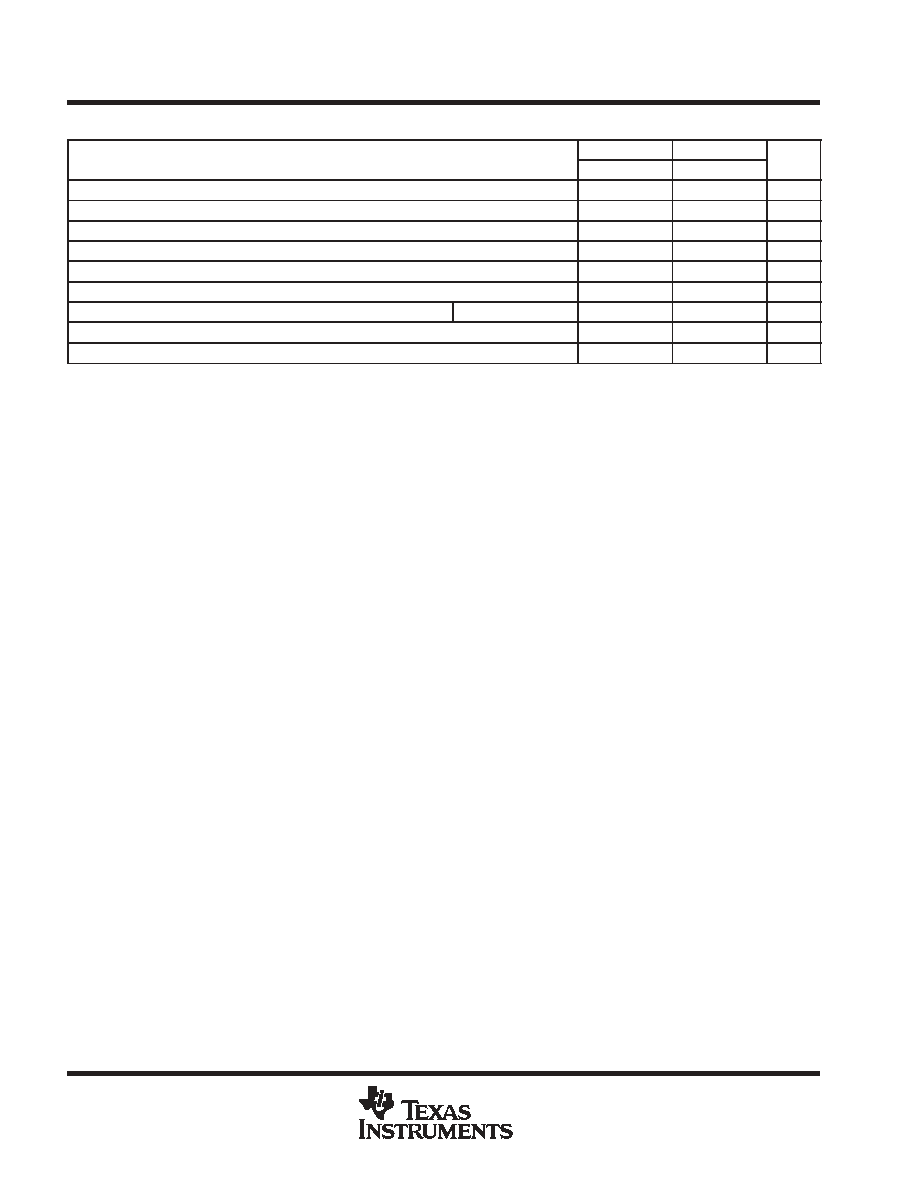

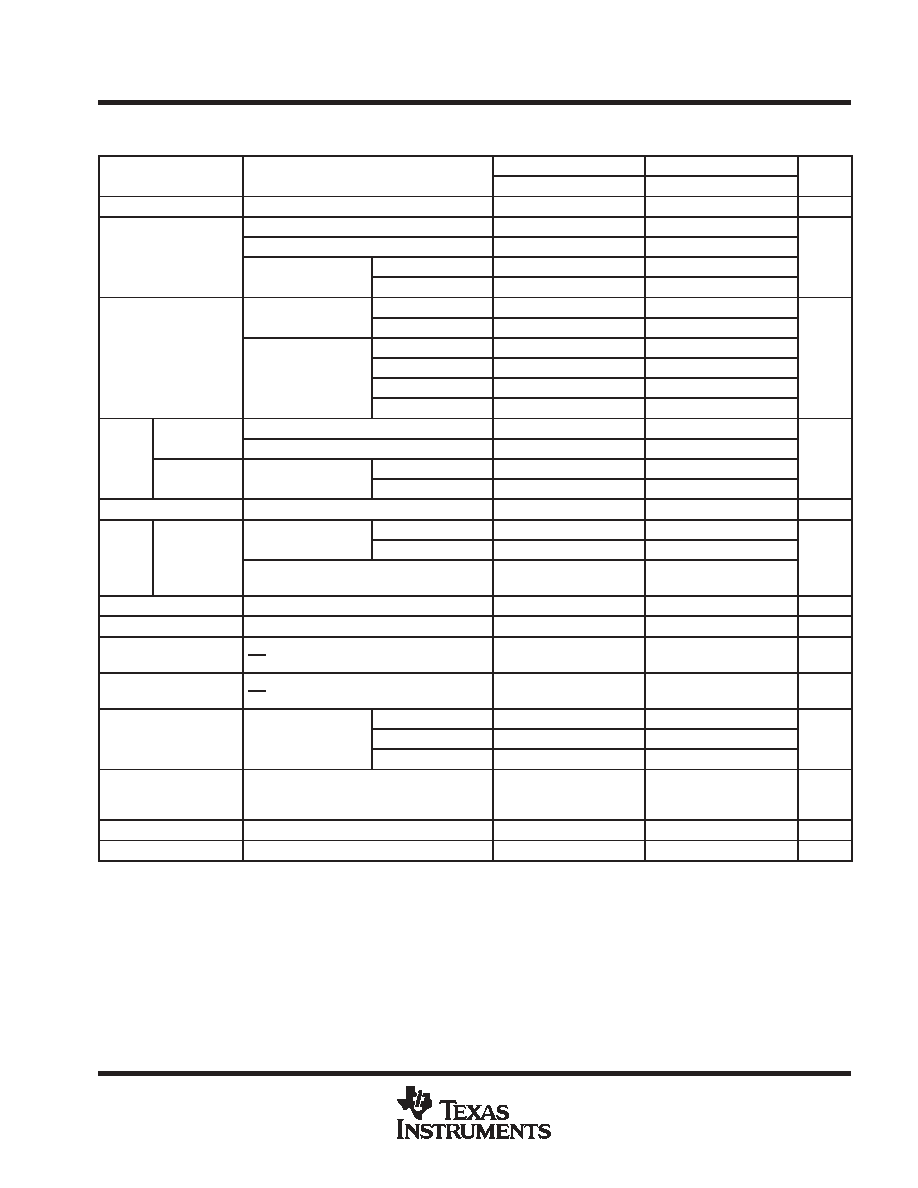

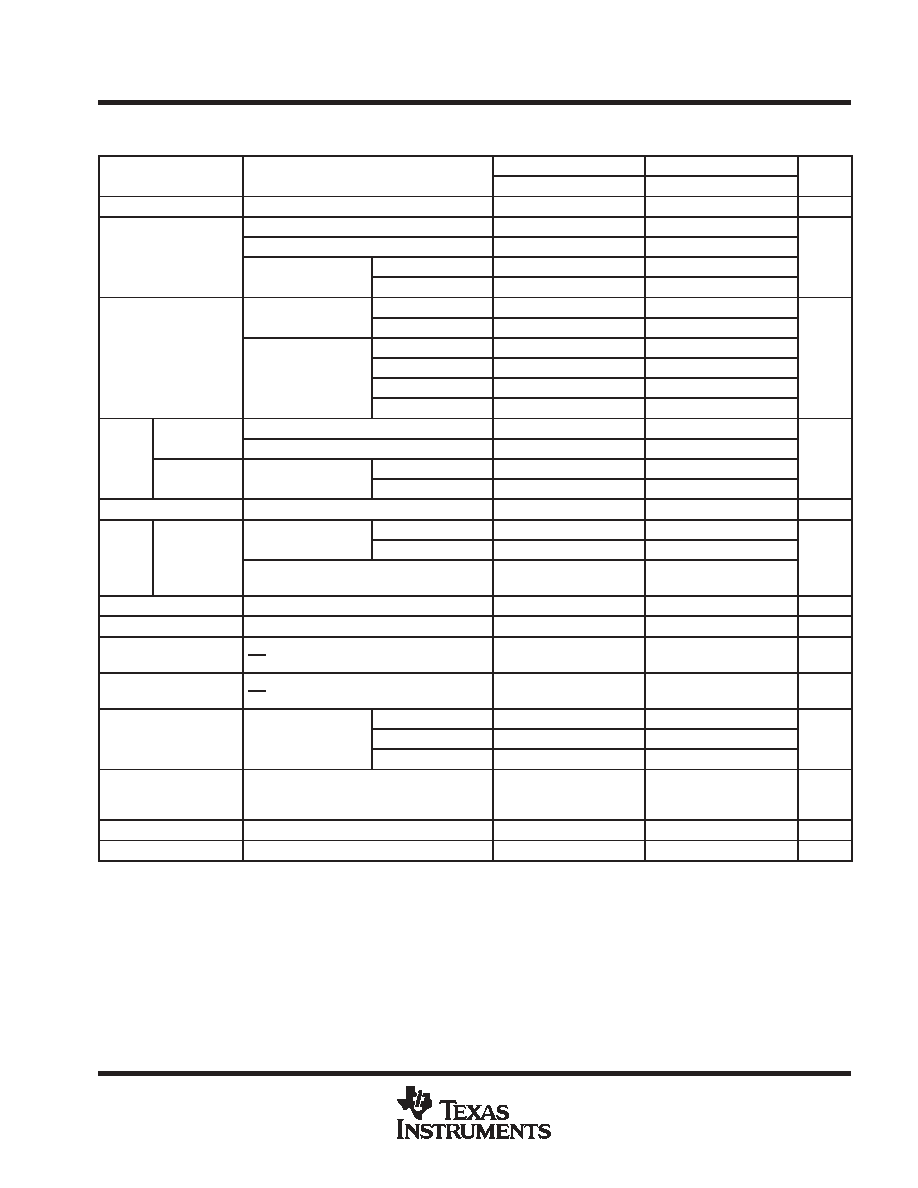

recommended operating conditions (see Note 5)

SN54LVTH240

SN74LVTH240

UNIT

MIN

MAX

MIN

MAX

UNIT

VCC

Supply voltage

2.7

3.6

2.7

3.6

V

VIH

High-level input voltage

2

2

V

VIL

Low-level input voltage

0.8

0.8

V

VI

Input voltage

5.5

5.5

V

IOH

High-level output current

-24

-32

mA

IOL

Low-level output current

48

64

mA

t/

v

Input transition rise or fall rate

Outputs enabled

10

10

ns/V

t/

VCC

Power-up ramp rate

200

200

µ

s/V

TA

Operating free-air temperature

-55

125

-40

85

°

C

NOTE 5: All unused control inputs of the device must be held at VCC or GND to ensure proper device operation. Refer to the TI application report,

Implications of Slow or Floating CMOS Inputs, literature number SCBA004.

SN54LVTH240, SN74LVTH240

3.3 V ABT OCTAL BUFFERS/DRIVERS

WITH 3 STATE OUTPUTS

SCBS679K - DECEMBER 1996 - REVISED SEPTEMBER 2003

5

POST OFFICE BOX 655303

·

DALLAS, TEXAS 75265

electrical characteristics over recommended operating free-air temperature range (unless

otherwise noted)

PARAMETER

TEST CONDITIONS

SN54LVTH240

SN74LVTH240

UNIT

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

MIN

TYP

MAX

UNIT

VIK

VCC = 2.7 V,

II = -18 mA

-1.2

-1.2

V

VCC = 2.7 V to 3.6 V,

IOH = -100

µ

A

VCC-0.2

VCC-0.2

VOH

VCC = 2.7 V,

IOH = -8 mA

2.4

2.4

V

VOH

VCC = 3 V

IOH = -24 mA

2

V

VCC = 3 V

IOH = -32 mA

2

VCC = 2.7 V

IOL = 100

µ

A

0.2

0.2

VCC = 2.7 V

IOL = 24 mA

0.5

0.5

VOL

IOL = 16 mA

0.4

0.4

V

VOL

VCC = 3 V

IOL = 32 mA

0.5

0.5

V

VCC = 3 V

IOL = 48 mA

0.55

IOL = 64 mA

0.55

Control inputs

VCC = 0 or 3.6 V,

VI = 5.5 V

10

10

II

Control inputs

VCC = 3.6 V,

VI = VCC or GND

±

1

±

1

A

II

Data inputs

VCC = 3.6 V

VI = VCC

1

1

µ

A

Data inputs

VCC = 3.6 V

VI = 0

-5

-5

Ioff

VCC = 0, VI or VO = 0 to 4.5 V

±

100

µ

A

VCC = 3 V

VI = 0.8 V

75

75

II(hold) Data inputs

VCC = 3 V

VI = 2 V

-75

-75

µ

A

II(hold) Data inputs

VCC = 3.6 V,

VI = 0 to 3.6 V

500

-750

µ

A

IOZH

VCC = 3.6 V,

VO = 3 V

5

5

µ

A

IOZL

VCC = 3.6 V,

VO = 0.5 V

-5

-5

µ

A

IOZPU

VCC = 0 to 1.5 V, VO = 0.5 V to 3 V,

OE = don't care

±

100

±

100

µ

A

IOZPD

VCC = 1.5 V to 0, VO = 0.5 V to 3 V,

OE = don't care

±

100

±

100

µ

A

VCC = 3.6 V,

Outputs high

0.19

0.19

ICC

VCC = 3.6 V,

IO = 0,

V = V

or GND

Outputs low

5

5

mA

ICC

IO = 0,

VI = VCC or GND

Outputs disabled

0.19

0.19

mA

ICC§

VCC = 3 V to 3.6 V,

One input at VCC - 0.6 V,

Other inputs at VCC or GND

0.2

0.2

mA

Ci

VI = 3 V or 0

3

3

pF

Co

VO = 3 V or 0

7

7

pF

On products compliant to MIL-PRF-38535, this parameter is not production tested.

All typical values are at VCC = 3.3 V, TA = 25

°

C.

This is the bus-hold maximum dynamic current. It is the minimum overdrive current required to switch the input from one state to another.

§ This is the increase in supply current for each input that is at the specified TTL voltage level, rather than VCC or GND.