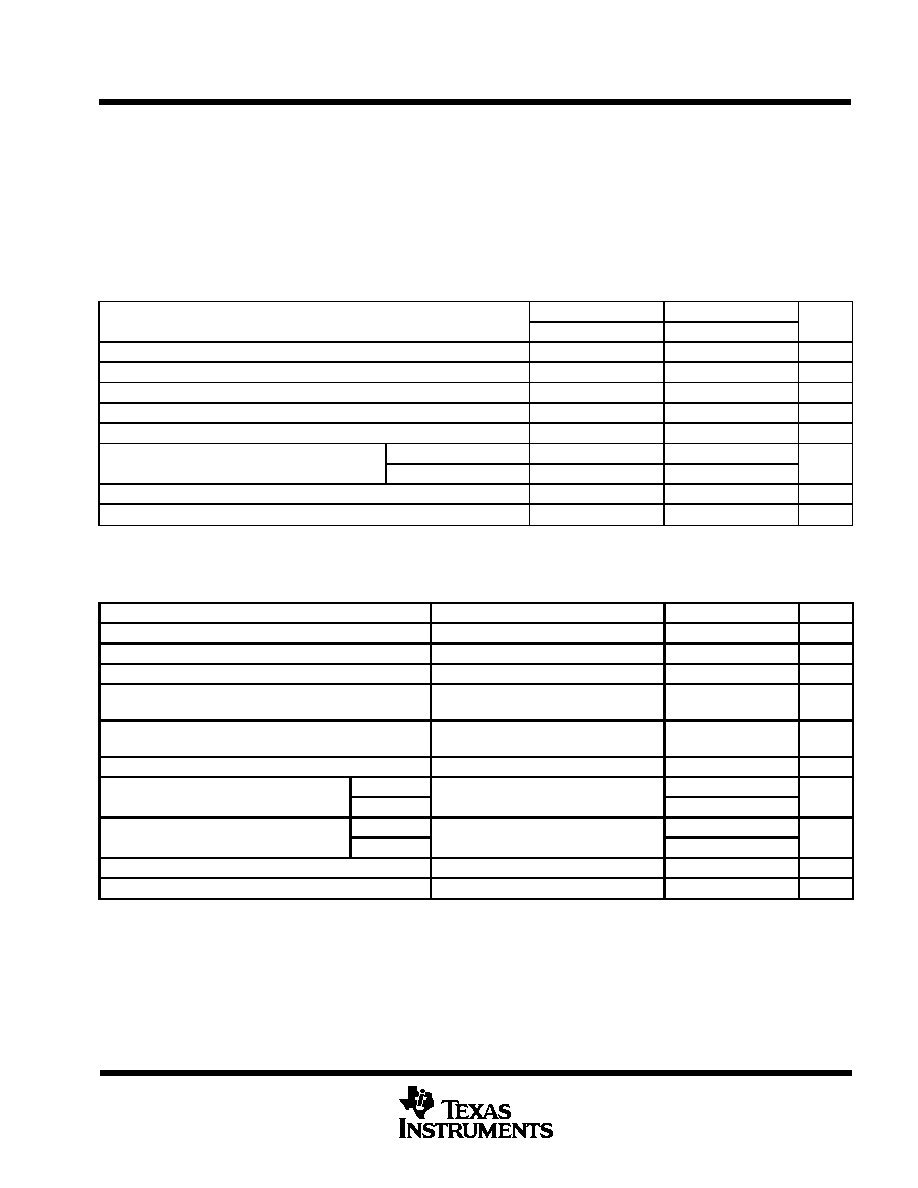

8D

7D

6D

5D

4D

3D

2D

1D

CLK

CLR

18

17

14

13

8

7

4

3

11

1

1D

C1

EN

8Q

7Q

6Q

5Q

4Q

3Q

2Q

1Q

19

16

15

12

6

5

2

9

logic symbol

This symbol is in accordance with ANSI/IEEE Std.

91-1984 and IEC Publication 617-12.

Pin numbers shown are for the DW, J, N, and W packages.

SN54273, SN54LS273, SN74273, SN74LS273

OCTAL D-TYPE FLIP-FLOP WITH CLEAR

SDLS090 ≠ OCTOBER 1976 ≠ REVISED MARCH 1988

Copyright

©

1988, Texas Instruments Incorporated

1

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

∑

Contains Eight Flip-Flops With Single-Rail

Outputs

∑

Buffered Clock and Direct Clear Inputs

∑

Individual Data Input to Each Flip-Flop

∑

Applications Include:

Buffer/Storage Registers

Shift Registers

Pattern Generators

description

These monolithic, positive-edge-triggered flip-

flops utilize TTL circuitry to implement D-type

flip-flop logic with a direct clear input.

Information at the D inputs meeting the setup time

requirements is transferred to the Q outputs on the

positive-going edge of the clock pulse. Clock

triggering occurs at a particular voltage level and

is not directly related to the transition time of the

positive-going pulse. When the clock input is at

either the high or low level, the D input signal has

no effect ar the output.

These flip-flops are guaranteed to respond to

clock frequencies ranging form 0 to 30 megahertz

while maximum clock frequency is typically 40

megahertz. Typical power dissipation is 39

milliwatts per flip-flop for the

273 and 10 milliwatts

for the

LS273.

FUNCTION TABLE

(each flip-flop)

INPUTS

OUTPUT

CLEAR

CLOCK

D

Q

L

X

X

L

H

H

H

H

L

L

H

L

X

Q0

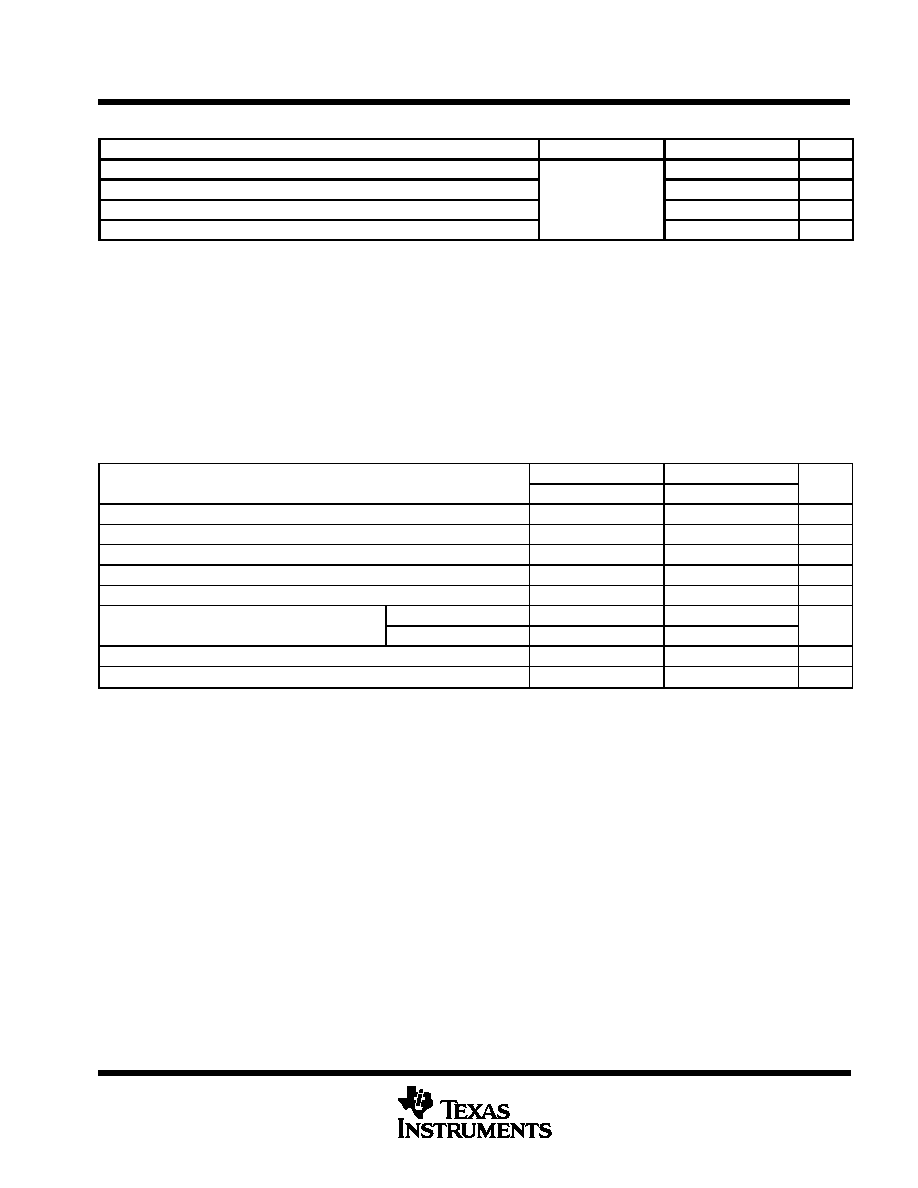

SN54LS273 . . . FK PACKAGE

(TOP VIEW)

SN54273, SN74LS273 . . . J OR W PACKAGE

SN74273 . . . N PACKAGE

SN74LS273 . . . DW OR N PACKAGE

(TOP VIEW)

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

CLR

1Q

1D

2D

2Q

3Q

3D

4D

4Q

GND

V

CC

8Q

8D

7D

7Q

6Q

6D

5D

5Q

CLK

3

2

1 20 19

9 10 11 12 13

4

5

6

7

8

18

17

16

15

14

8D

7D

7Q

6Q

6D

2D

2Q

3Q

3D

4D

1D

1Q

CLR

5D

8Q

4Q

GND

CLK

CC

V

5Q

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

SN54273, SN54LS273, SN74273, SN74LS273

OCTAL D-TYPE FLIP-FLOP WITH CLEAR

SDLS090 ≠ OCTOBER 1976 ≠ REVISED MARCH 1988

2

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

schematics of inputs and outputs

VCC

EQUIVALENT OF EACH INPUT

INPUT

Req

273

Clear: Req = 3 k

NOM

Clock: Req = 6 k

NOM

All other inputs: Req = 8 k

NOM

VCC

TYPICAL OF ALL OUTPUTS

100

NOM

OUTPUT

VCC

EQUIVALENT OF EACH INPUT

INPUT

20 k

NOM

LS273

VCC

TYPICAL OF ALL OUTPUTS

120

NOM

OUTPUT

logic diagram (positive logic)

11

CLOCK

1

CLEAR

1D

1Q

R

C1

1D

1D

C1

R

2Q

2D

1D

C1

R

3Q

3D

1D

C1

R

4Q

4D

1D

C1

R

5Q

5D

1D

C1

R

6Q

6D

1D

C1

R

7Q

7D

1D

C1

R

8Q

8D

2

3

4

5

7

6

8

9

13

12

14

15

17

16

18

19

Pin numbers shown are for the DW, J, N, and W packages.

SN54273, SN54LS273, SN74273, SN74LS273

OCTAL D-TYPE FLIP-FLOP WITH CLEAR

SDLS090 ≠ OCTOBER 1976 ≠ REVISED MARCH 1988

3

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

Supply voltage, V

CC

(see Note 1)

7 V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input voltage

5.5 V

. . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating free-air temperature range, T

A

: SN54273

≠ 55

∞

C to 125

∞

C

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SN74273

0

∞

C to 70

∞

C

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range

≠ 65

∞

C to 150

∞

C

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

NOTE 1: Voltage values are with respect to network ground terminal.

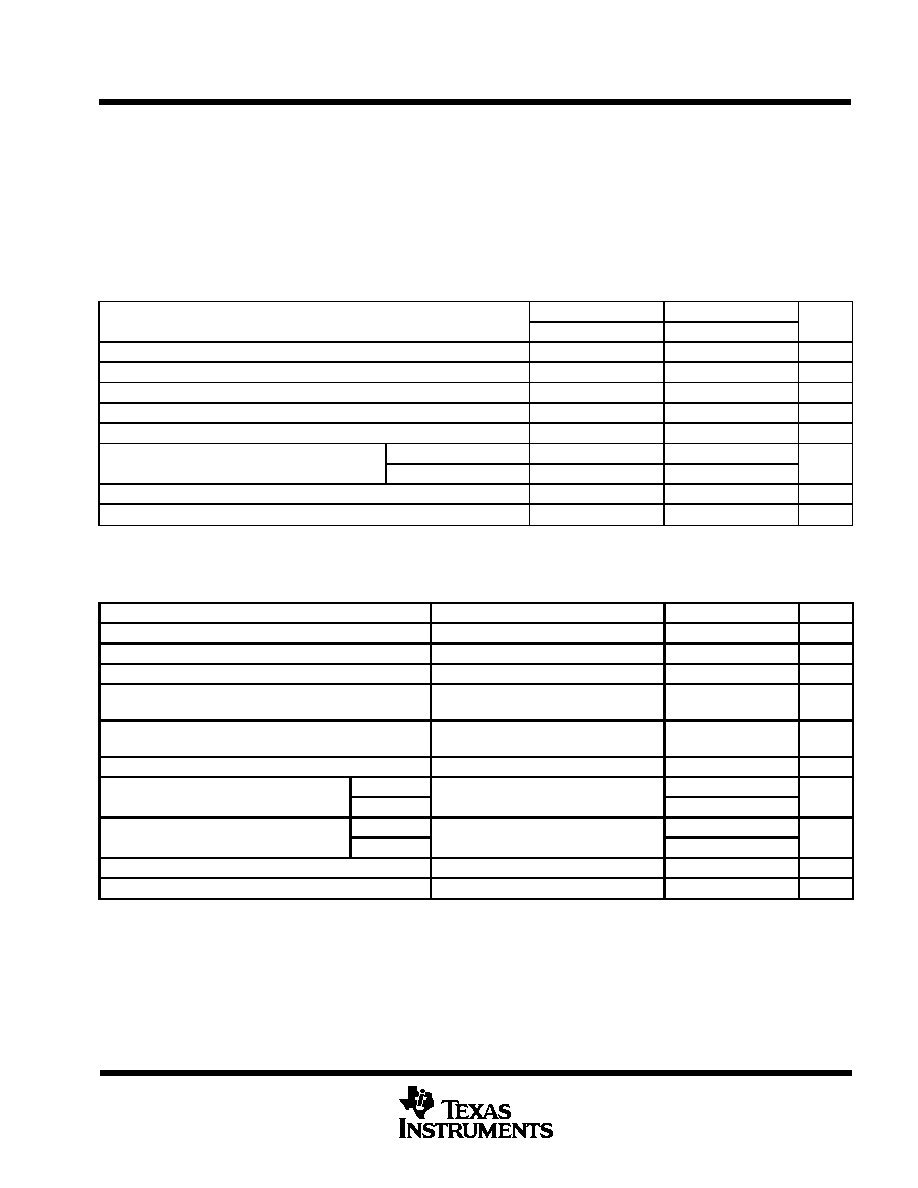

recommended operating conditions

SN54273

SN74273

UNIT

MIN

NOM

MAX

MIN

NOM

MAX

UNIT

Supply voltage, VCC

4.5

5

5.5

4.75

5

5.25

V

High-level output current, IOH

≠ 800

≠ 800

µ

A

Low-level output current, IOL

16

16

mA

Clock frequency, fclock

0

30

0

30

MHz

Width of clock or clear pulse, tw

16.5

16.5

ns

Setup time t

Data input

20

20

ns

Setup time, tsu

Clear inactive state

25

25

ns

Data hold time, th

5

5

ns

Operating free-air temperature, TA

≠ 55

125

0

70

∞

C

The arrow indicates that the rising edge of the clock pulse is used for reference.

electrical characteristics over recommended operating free-air temperature range (unless

otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

VIH

High-level input voltage

2

V

VIL

Low-level input voltage

0.8

V

VIK

Input clamp voltage

VCC = MIN,

II = ≠ 12 mA

≠1.5

V

VOH

High-level output voltage

VCC = MIN,

VIL = 0.8 V,

VIH = 2 V,

IOH = ≠ 800

µ

A

2.4

3.4

V

VOL

Low-level output voltage

VCC = MIN,

VIL = 0.8 V,

VIH = 2 V,

IOH = 16 mA

0.4

V

II

Input current at maximum input voltage

VCC = MAX,

VI = 5.5 V

1

mA

IIH

High level input current

Clear

VCC = MAX

VI = 2 4 V

80

µ

A

IIH

High-level input current

Clock or D

VCC = MAX,

VI = 2.4 V

40

µ

A

IIL

Low level input current

Clear

VCC = MAX

VI = 0 4 V

≠ 3.2

mA

IIL

Low-level input current

Clock or D

VCC = MAX,

VI = 0.4 V

≠ 1.6

mA

IOS

Short-circuit output currentß

VCC = MAX

≠ 18

≠ 57

mA

ICC

Supply current

VCC = MAX,

See Note 2

62

94

mA

For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

All typical values are at VCC = 5 V, TA = 25

∞

C.

ß Not more than one output should be shorted at a time.

NOTE 2: With all outputs open and 4.5 V applied to all data and clear inputs, ICC is measured after a momentary ground, then 4.5 V, is applied

to clock.

SN54273, SN54LS273, SN74273, SN74LS273

OCTAL D-TYPE FLIP-FLOP WITH CLEAR

SDLS090 ≠ OCTOBER 1976 ≠ REVISED MARCH 1988

4

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

switching characteristics, V

CC

= 5 V, T

A

= 25

∞

C

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

fmax

Maximum clock frequency

C

30

40

MHz

tPHL

Propagation delay time, high-to-low-level output from clear

CL = 15 pF,

RL = 400

18

27

ns

tPLH

Propagation delay time, low-to-high-level output from clock

RL = 400

,

See Note 3

17

27

ns

tPHL

Propagation delay time, high-to-low-level output from clock

See Note 3

18

27

ns

NOTE 3: Load circuits and voltage waveforms are shown in Section 1.

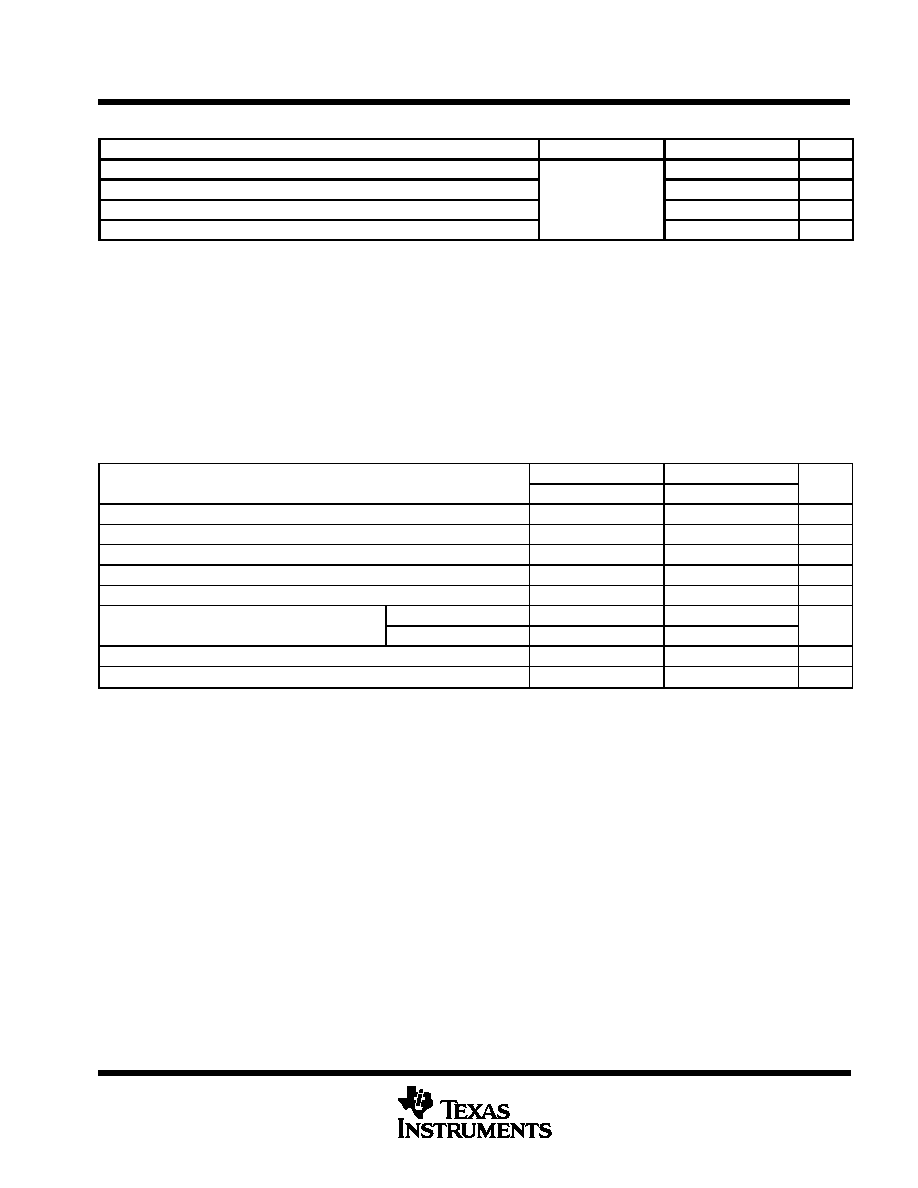

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

Supply voltage, V

CC

(see Note 1)

7 V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input voltage

7 V

. . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating free-air temperature range, T

A

: SN54LS273

≠ 55

∞

C to 125

∞

C

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SN74LS273

0

∞

C to 70

∞

C

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range

≠ 65

∞

C to 150

∞

C

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

NOTE 1: Voltage values are with respect to network ground terminal.

recommended operating conditions

SN54LS273

SN74LS273

UNIT

MIN

NOM

MAX

MIN

NOM

MAX

UNIT

Supply voltage, VCC

4.5

5

5.5

4.75

5

5.25

V

High-level output current, IOH

≠ 400

≠ 400

µ

A

Low-level output current, IOL

4

8

mA

Clock frequency, fclock

0

30

0

30

MHz

Width of clock or clear pulse, tw

20

20

ns

Setup time t

Data input

20

20

ns

Setup time, tsu

Clear inactive state

25

25

ns

Data hold time, th

5

5

ns

Operating free-air temperature, TA

≠ 55

125

0

70

∞

C

The arrow indicates that the rising edge of the clock pulse is used for reference.

SN54273, SN54LS273, SN74273, SN74LS273

OCTAL D-TYPE FLIP-FLOP WITH CLEAR

SDLS090 ≠ OCTOBER 1976 ≠ REVISED MARCH 1988

5

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

electrical characteristics over recommended operating free-air temperature range (unless

otherwise noted)

PARAMETER

TEST CONDITIONS

SN54LS273

SN74LS273

UNIT

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

MIN

TYP

MAX

UNIT

VIH

High-level input voltage

2

2

V

VIL

Low-level input voltage

0.7

0.8

V

VIK

Input clamp voltage

VCC = MIN,

II = ≠ 18 mA

≠1.5

≠1.5

V

VOH

High-level output voltage

VCC = MIN,

VIL = VILmax,

VIH = 2 V,

IOH = ≠ 400

µ

A

2.5

3.4

2.7

3.4

V

VOL

Low level output voltage

VCC = MIN,

VIH = 2 V,

IOL = 4 mA

0.25

0.4

0.25

0.4

V

VOL

Low-level output voltage

CC

,

VIL = VILmax,

IH

,

IOL = 8 mA

0.35

0.5

V

II

Input current at

maximum input voltage

VCC = MAX,

VI = 7 V

0.1

0.1

mA

IIH

High-level input current

VCC = MAX,

VI = 2.7 V

20

20

µ

A

IIL

Low-level input current

VCC = MAX,

VI = 0.4 V

≠ 0.4

≠ 0.4

mA

IOS

Short-circuit output

currentß

VCC = MAX

≠ 20

≠ 100

≠ 20

≠ 100

mA

ICC

Supply current

VCC = MAX,

See Note 2

17

27

17

27

mA

For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

All typical values are at VCC = 5 V, TA = 25

∞

C.

ß Not more than one output should be shorted at a time and duration of short circuit should not exceed one second.

NOTE 2: With all outputs open and 4.5 V applied to all data and clear inputs, ICC is measured after a momentary ground, then 4.5 V, is applied

to clock.

switching characteristics, V

CC

= 5 V, T

A

= 25

∞

C

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

fmax

Maximum clock frequency

C

30

40

MHz

tPHL

Propagation delay time, high-to-low-level output from clear

CL = 15 pF,

RL = 2 k

18

27

ns

tPLH

Propagation delay time, low-to-high-level output from clock

RL = 2 k

,

See Note 3

17

27

ns

tPHL

Propagation delay time, high-to-low-level output from clock

See Note 3

18

27

ns

NOTE 3: Load circuits and voltage waveforms are shown in Section 1.