| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: VSC7129R | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Data Sheet

VSC7127/VSC7129

Family of Repeater/Retimer and Port

Bypass Circuits for Fibre Channel

G52298-0, Rev 4.3

Page 1

05/01/01

© VITESSE

SEMICONDUCTOR CORPORATION ∑ 741 Calle Plano ∑ Camarillo, CA 93012

Tel: (800) VITESSE ∑ FAX: (805) 987-5896 ∑ Email: prodinfo@vitesse.com

Internet: www.vitesse.com

VITESSE

SEMICONDUCTOR CORPORATION

Features

General Description

The VSC7127 and VSC7129 contain six cascaded Port Bypass Circuits (PBCs), the FibreTimer

TM

config-

urable Repeater/Retimer (CRU) and a Signal Detect Unit (SDU). These parts are typically used in distributing

Fibre Channel signals to an array of disk drives in an FC-AL loop as illustrated in Figure 1. The first

VSC7127's CRU is configured as a Repeater to attenuate jitter, the second VSC7127's CRU is bypassed to

reduce power and the third VSC7127's CRU is configured as a retimer so that the output of the device is a jitter-

compliance point.

Each PBC is a multiplexer that is controlled by the corresponding SELx line which, if HIGH, selects the

external input or, if LOW, selects the output of the previous PBC. For the VSC712xR, when MODE is LOW

and SEL5 is HIGH, the CRU is a sophisticated repeater which has low latency, no peaking and attenuates jitter

even at low frequencies. When MODE is HIGH and SEL5 is HIGH, the CRU is a retimer which eliminates jit-

ter transfer but has increased latency due to an elasticity buffer which adds/drops Fibre Channel fill words in

order to accomodate the difference between the baud rate of the incoming data and the local REFCLK. When

SEL5 is LOW, the CRU is bypassed and powered down. The SDU monitors the analog levels of the IO+/- input

and monitors the output of the CRU digitally to indicate whether valid data is present.

The VSC7127/VSC7129 are similar to the VSC7124 which does not contain the FibreTimer

TM

cell or CMU.

VSC7127/VSC7129 Block Diagram

∑ ANSI X3T11 Fibre Channel Compliant

∑ 1.0625Gb/s Operation

∑ Features the FibreTimer

TM

Configurable Clock

Recovery Unit (CRU): Repeater, Retimer or

Bypassed

∑ Six Port Bypass Circuits (PBC)

∑ Analog/Digital Signal Detect (SDU)

∑ On-Chip Transmit Termination

∑ 3.3V, 700mW Power Dissipation

∑ Compatible with HDMP-0451 (VSC7127) or

HDMP-0452 (VSC7129)

∑ 44-Pin, 10mm PQFP Package

I1

+

I1

-

O1-

SE

L1

1

0

PBC1

REFCLK

SDU

CRU

I2

+

I2

-

O2+

O2-

SE

L2

1

0

PBC2

I3

+

I3

-

O3+

O3-

SE

L3

1

0

PBC3

I4

+

I4

-

O4+

O4-

SE

L4

1

0

PBC4

CMU

SIGDET

0.1uF

MODE

O1+

I0

+

I0

-

O0+

O0-

SE

L0

1

0

PBC0

106.25MHz

0

1

PBC5

SEL5

Data Sheet

VSC7127/VSC7129

Family of Repeater/Retimer and Port

Bypass Circuits for Fibre Channel

VITESSE

SEMICONDUCTOR CORPORATION

Page 2

G52298-0, Rev 4.3

05/01/01

© VITESSE

SEMICONDUCTOR CORPORATION ∑ 741 Calle Plano ∑ Camarillo, CA 93012

Tel: (800) VITESSE ∑ FAX: (805) 987-5896 ∑ Email: prodinfo@vitesse.com

Internet: www.vitesse.com

Application: Fibre Channel Disk Arrays

A 12-port JBOD is shown in Figure 1. This dual loop application uses 3 VSC7127Xs on each loop in order

to configure the FC-AL disk array. Functional drives are included in the FC-AL loop while non-functional or

missing drives (numbers 2, 7, 9) are excluded.

Figure 1: 12-Drive FC-AL JBOD Application

VSC

712

7R #

1

VSC

7

1

27R #2

V

S

C

7

12

7 R

#

3

V

S

C7

127

R #4

7125

VSC7

12

1 QUAD P

O

R

T

B

Y

P

A

SS

C

I

RCUIT

Optics

or

Copper

SerDes

7125

SerDes

1

0

1

0

1

0

1

0

7125

SerDes

7125

SerDes

1

0

1

0

7125

SerDes

7125

SerDes

1

0

1

0

7125

SerDes

7125

SerDes

1

0

1

0

7125

SerDes

7125

SerDes

1

0

1

0

1

0

1

0

7125

SerDes

7125

SerDes

1

0

1

0

1

0

1

0

7125

SerDes

7125

SerDes

1

0

1

0

7125

SerDes

7125

SerDes

1

0

1

0

7125

SerDes

7125

SerDes

1

0

1

0

Repeater

Retimer

Retimer

Repeater

VSC

7

1

27T

#

5

1

2

3

4

5

6

7

8

9

10

11

12

VS

C7

127

T #

6

Optics

or

Copper

LOOP A

LOOP B

CONFIGURATION:

7127R #1 & 2: Repeater Mode

SEL0=1, SEL5=1

7127T #5 & 6: Retimer Mode

SEL1=1, SEL5=1

MODE=0

MODE=1

7127R #3 & 4: Bypass Mode

SEL5=0

MODE=x, No REFCLK

0

1

2

3

4

0

0

1

2

3

4

0

1

1

2

3

4

0

Data Sheet

VSC7127/VSC7129

Family of Repeater/Retimer and Port

Bypass Circuits for Fibre Channel

G52298-0, Rev 4.3

Page 3

05/01/01

© VITESSE

SEMICONDUCTOR CORPORATION ∑ 741 Calle Plano ∑ Camarillo, CA 93012

Tel: (800) VITESSE ∑ FAX: (805) 987-5896 ∑ Email: prodinfo@vitesse.com

Internet: www.vitesse.com

VITESSE

SEMICONDUCTOR CORPORATION

Functionality

Device Configurations

Four devices are specified in this datasheet: VSC7127R, VSC7127T, VSC7129R and VSC7129T. The

VSC7127 is pin-compatible to the HDMP-0451. The VSC7129 is pin compatible with the HDMP-0452. The

VSC712xR is configured as a Repeater when pin 12, MODE, is LOW, or a Retimer when HIGH. The

VSC712xT is configured as a Retimer when pin 12, MODE, is LOW, or a Repeater when HIGH.

Port Bypass Circuits

The VSC712x contains six Port Bypass Circuits (PBCs) which are 2-to-1 multiplexers used to steer serial

signals. Each PBC, PBCx has a single select line, SELx, which when HIGH, selects the external input, Ix, to

PBCx and when LOW, selects the output of the previous PBC. PCB5 does not have an external input but selects

between the output of the CRU (when SEL5 is HIGH) and the output of PBC0 (when SEL5 is LOW). These

controls allow FC-AL loops to include a functional device on the loop or exclude a non-functional device from

the loop.

FibreTimer

TM

Clock Recovery Unit--Repeater Mode

The Clock Recovery Unit (CRU) is a digital PLL which extracts the clock from the incoming data and sam-

ples the data with the extracted clock. In repeater mode, the output of the CRU is synchronized to the recovered

clock and has improved signal quality due to amplification of the signal and attenuation of jitter. Latency

through the device is quite low, just a few bit times. Multiple repeaters can be cascaded without accumulation

of jitter. MODE determines whether the CRU is a Repeater or a Retimer.

FibreTimer

TM

Clock Recovery Unit --Retimer Mode

MODE may configure the CRU as a retimer where the recovered data is placed into an elasticity buffer.

Data is taken out of the elasticity buffer and retransmitted synchronously to the local REFCLK. For Fibre Chan-

nel data, Fill words will be added and dropped in the elasticity buffer in order to accomodate the differences in

speed between the incoming data and the REFCLK. The retimer does not transfer jitter from the input to the

output but has longer latency, up to 4 word times, through the device.

FibreTimer

TM

Clock Recovery Unit--Bypass Mode

When SEL5 is LOW, PBC5 selects the output of PBC0 and the CRU is unused. In this mode, the CRU is

powered down to reduce power dissipation. If the part will be used only in this mode, REFCLK and MODE are

ignored and can be left open. If the CRU is bypassed, the Signal Detect Unit is disabled and the output is LOW.

Signal Detection

A signal detect unit (SDU) monitors IO+/- and the output of the CRU to determine if there is a valid Fibre

Channel signal present. The SIGDET is updated every 160 bits (an "interval") with the previous interval's status

of three different Signal Detect Units: analog signal amplitude (ASDU), run length check (RLLSDU), Ordered

Set density (OSSDU). If the input amplitude is less than 200mV (differential), ASDU will be set LOW. If the

input amplitude is greater than 400mV, ASDU will be asserted HIGH. If a run length violation occurs (more

than 5 consecutive ones or zeros), the RLLSDU will be set LOW and stay LOW until the occurrence of a valid

Data Sheet

VSC7127/VSC7129

Family of Repeater/Retimer and Port

Bypass Circuits for Fibre Channel

VITESSE

SEMICONDUCTOR CORPORATION

Page 4

G52298-0, Rev 4.3

05/01/01

© VITESSE

SEMICONDUCTOR CORPORATION ∑ 741 Calle Plano ∑ Camarillo, CA 93012

Tel: (800) VITESSE ∑ FAX: (805) 987-5896 ∑ Email: prodinfo@vitesse.com

Internet: www.vitesse.com

Fill Word or Primitive Sequence. Any Fill Word or Primitive Sequence will reset the OSSDU counter which

will increment on any 160-bit sequence which is not a Fill Word or Primitive Sequence. If the counter reaches

256, a Fill Word or Primitive Sequence has not occured often enough so OSSDU is asserted until reset again.

SIGDET is just an or'ing of these three state machines resynchronized to the 160-bit interval clock.

If SEL5 is LOW or REFCLK is absent, the signal detect unit is disabled and SIGDET is LOW.

Application Example

Figure 2 shows one loop of an 8-drive JBOD implemented with two VSC712xs per loop. The input from

the connector goes through a repeater in order to clean up the signal prior to the array of disk drives. After all

eight PBCs, the output the to connector is retimed to ensure jitter compliance at the connector.

Figure 2: 8-Drive JBOD

1

0

SEL1

RPTR

1

0

1

0

1

0

I0

O0

I1

O1

I2

O2

I3

O3

I4

O4

SEL4

SEL3

SEL2

MODE=0

SEL0=1

Dr

ive

1

Drive 2

Drive 3

Dr

i

v

e

4

Connector

Drive 8

MODE

SEL0

1

0

1

0

SEL1

RTMR

1

0

1

0

1

0

I0

O0

I1

O1

I2

O2

I3

O3

I4

O4

SEL4

SEL3

SEL2

MODE=1

SEL1=1

Drive 5

Drive 6

Dri

v

e 7

MODE

SEL0

1

0

1

1

0

1

NOT SHOWN: PBC5, SEL5

Data Sheet

VSC7127/VSC7129

Family of Repeater/Retimer and Port

Bypass Circuits for Fibre Channel

G52298-0, Rev 4.3

Page 5

05/01/01

© VITESSE

SEMICONDUCTOR CORPORATION ∑ 741 Calle Plano ∑ Camarillo, CA 93012

Tel: (800) VITESSE ∑ FAX: (805) 987-5896 ∑ Email: prodinfo@vitesse.com

Internet: www.vitesse.com

VITESSE

SEMICONDUCTOR CORPORATION

AC Characteristics

(Over Recommended Operating Conditions)

Figure 3: Timing Waveforms

Table 1: AC Characteristics

(Over recommended operating conditions)

NOTE: (1) Retimer mode is only available for Fibre Channel applications.

Parameters

Description

Min

Typ

Max

Units

Conditions

T

1

Propagation delay (Repeater mode)

7.0

ns

Delay with all circuits bypassed.

T

1

Propagation delay (Retimer mode)

180

ns

Delay with all circuits bypassed.

Typical delay is 100 bit times.

T

R

, T

F

Serial data rise and fall time

300

ps

At

V

IN

minimum levels

T

j(PBC)

Data jitter accumulation

(PBC only)

120

ps

Peak-to-peak on Ox+/- in Port

Bypass Circuit Mode.

T

J(RPTR)

Total data output jitter

(Repeater mode)

192

ps

Jitter generation at Ox+/- when

driven by the CRU in Repeater

Mode. IEEE 802.3z Clause 38.68

T

DJ(RPTR)

Serial data output deterministic jitter

(p-p) (Repeater mode)

80

ps

Jitter generation at Ox+/- when

driven by the CRU in Repeater

Mode. IEEE 802.3z Clause 38.68

T

J(RTMR)

Total data output jitter

(Retimer Mode)

(1)

192

ps

Jitter generation at Ox+/- when

driven by the CRU in Retimer

Mode.

T

DJ(RTMR)

Serial data output deterministic jitter

(p-p) (Retimer Mode)

(1)

80

ps

Jitter generation at Ox+/- when

driven by the CRU in Retimer

Mode.

T

JTOL

Jitter tolerance

0.24

UI

Minimum eye opening for proper

operation as defined in MJS 8.0.

T

1

T

1

Ox+/-

Ix+/-

Data Sheet

VSC7127/VSC7129

Family of Repeater/Retimer and Port

Bypass Circuits for Fibre Channel

VITESSE

SEMICONDUCTOR CORPORATION

Page 6

G52298-0, Rev 4.3

05/01/01

© VITESSE

SEMICONDUCTOR CORPORATION ∑ 741 Calle Plano ∑ Camarillo, CA 93012

Tel: (800) VITESSE ∑ FAX: (805) 987-5896 ∑ Email: prodinfo@vitesse.com

Internet: www.vitesse.com

Figure 4: REFCLK Timing Waveforms *

Table 2: Reference Clock Requirements

DC Characteristics

(Over recommended operating conditions)

NOTE: (1) Refer to Application Note AN-37 for details regarding differential voltage measurements.

Parameters

Description

Min

Typ

Max

Units

Conditions

FR

Frequency Range

105

107

MHz

FO

Frequency Offset

-200

200

ppm

Maximum frequency offset

between transmit and receive

reference clocks on one link

DC

Duty Cycle

35

65

%

Measured at 1.5V

T

R

, T

F

Rise and Fall Time

2.0

ns

Between V

IL(MAX)

and V

IH(MIN)

Parameters

Description

Min

Typ

Max

Units

Conditions

V

OH

Output HIGH voltage (TTL)

2.4

V

I

OH

= -1.0mA

V

OL

Output LOW voltage (TTL)

0.5

V

I

OL

= +1.0mA

V

IH

Input HIGH voltage (TTL)

2.0

5.5

V

V

IL

Input LOW voltage (TTL)

0

0.8

V

I

IH

Input HIGH current (TTL)

50

500

µA

V

IN

=2.4V

I

IL

Input LOW current (TTL)

-500

µA

V

IN

=0.5V

V

OUT75

(1)

TX output differential peak-to-

peak voltage swing

1200

2200

mVp-p

75

to V

DD

≠ 2.0 V

V

OUT50

(1)

TX output differential peak-to-

peak voltage swing

1000

2200

mVp-p

50

to V

DD

≠ 2.0 V

V

IN

(1)

Receiver differential peak-to-peak

input Sensitivity RX

400

2600

mVp-p

Internally biased to V

DD

/2

V

DD

Supply voltage

3.14

3.47

V

3.3V±5%

P

D

Power dissipation

707

902

mW

Outputs open, V

DD

= V

DD

max.

±2%

I

DD

Current (all supplies)

215

260

mA

Outputs open, V

DD

= V

DD

max

I

DDA

Current (V

DDA

)

50

70

mA

V

DDA

= V

DD

max

REFCLK

V

IL(MAX)

V

IH(MIN)

NOTE: A reference clock must be provided to the REFCLK pin in order for the chip to power up in the right state.

Data Sheet

VSC7127/VSC7129

Family of Repeater/Retimer and Port

Bypass Circuits for Fibre Channel

G52298-0, Rev 4.3

Page 7

05/01/01

© VITESSE

SEMICONDUCTOR CORPORATION ∑ 741 Calle Plano ∑ Camarillo, CA 93012

Tel: (800) VITESSE ∑ FAX: (805) 987-5896 ∑ Email: prodinfo@vitesse.com

Internet: www.vitesse.com

VITESSE

SEMICONDUCTOR CORPORATION

Absolute Maximum Ratings

(1)

TTL Power Supply Voltage (V

DD

) ...................................................................................................... 0.5V to +4V

PECL DC Input Voltage (V

INP

) ............................................................................................. -0.5V to V

DD

+0.5V

TTL DC Input Voltage (V

INT

)........................................................................................................... -0.5V to 5.5V

DC Voltage Applied to Outputs for High Output State (V

IN TTL

) ........................................ -0.5V to V

DD

+ 0.5V

TTL Output Current (I

OUT

), (DC, output high) .......................................................................................... +50mA

PECL Output Current, (I

OUT

), (DC, output high)........................................................................................ -50mA

Case Temperature Under Bias (T

C

).............................................................................................. -55

o

C to +125

o

C

Storage Temperature (T

STG

)........................................................................................................ -65

o

C to + 150

o

C

Maximum Input ESD ................................................................................................................................... 1000V

Recommended Operating Conditions

(2)

Power Supply Voltage (V

DD

) ....................................................................................................... +3.14V to 3.47V

Ambient Operating Temperature Range (T)...............................................................0

∞

C Ambient to +95

∞

C Case

NOTES: (1) CAUTION: Stresses listed under "Absolute Maximum Ratings" may be applied to devices one at a time without causing permanent

damage. Functionality at or above the values listed is not implied. Exposure to these values for extended periods may affect device reli-

ability.

(2) Vitesse guarantees the functional and parametric operation of the part under "Recommended Operating Conditions" except where

specifically noted in the AC and DC Parametric tables.

Data Sheet

VSC7127/VSC7129

Family of Repeater/Retimer and Port

Bypass Circuits for Fibre Channel

VITESSE

SEMICONDUCTOR CORPORATION

Page 8

G52298-0, Rev 4.3

05/01/01

© VITESSE

SEMICONDUCTOR CORPORATION ∑ 741 Calle Plano ∑ Camarillo, CA 93012

Tel: (800) VITESSE ∑ FAX: (805) 987-5896 ∑ Email: prodinfo@vitesse.com

Internet: www.vitesse.com

Package Pin Descriptions

Figure 5: Pin Diagram

Table 3: VSC7124/VSC7127/VSC7129 Pin Differences

NOTE: (1) The VSC7124 is a 5 PBC device similar to the VSC7127/VSC7129 without the FibreTimerTM Repeater/Retimer functionality.

Pin 12

Pin 13

Pin 32

Pin 19

Pin 20

Pin 21

Pin 22

Pin 23

Comment

VSC7124

N/C

N/C

VDD

VSS

N/C

VDD

N/C

N/C

Provided for reference only

(1)

VSC7127

MODE

REFCLK

VDDA

VSS

SIGDET

VDD

SEL5

TRST

Compatible with HDMP-0451

VSC7129

MODE

REFCLK

VDDA

SIGDET

VDD

SEL5

TRST

VSS

Compatible with HDMP-0452

P

I

N 19*

VSS

I0+

VSS

O2+

O3-

O2-

VDDP

2

I3

+

PIN23*

O0+

O4+

O0-

VDDP1

O1-

O1+

PI

N

2

1*

I4-

VDD

VSS

REF

C

L

K

SEL

4

SEL

0

I0-

PI

N

2

2*

SEL

3

SEL

1

SEL

2

PI

N

2

0*

VDDP0

I4+

VDDP4

O4-

VDDA

I2

-

I2

+

I1+

I1-

VS

S

O3+

I3

-

VDDP

3

VSC7127

VSS

1

3

5

7

9

11

33

31

29

27

25

23

13

15

17

19

21

43

41

39

37

35

M

ODE

VSC7129

* See Tables 3 and 4 for Pin Differences and Description

Data Sheet

VSC7127/VSC7129

Family of Repeater/Retimer and Port

Bypass Circuits for Fibre Channel

G52298-0, Rev 4.3

Page 9

05/01/01

© VITESSE

SEMICONDUCTOR CORPORATION ∑ 741 Calle Plano ∑ Camarillo, CA 93012

Tel: (800) VITESSE ∑ FAX: (805) 987-5896 ∑ Email: prodinfo@vitesse.com

Internet: www.vitesse.com

VITESSE

SEMICONDUCTOR CORPORATION

Table 4: Pin Identification

Pin #

Name

Description

4, 3

41, 40

35, 34

28, 27

10, 9

I1+, I1-

I2+, I2-

I3+, I3-

I4+, I4-

I0+, I 0-

INPUT - Differential, internally biased to V

DD

/2.

I1+/I1- is the serial input to PBC1.

I2+/I2- is the serial input to PBC2.

I3+/I3- is the serial input to PBC3.

I4+/I4- is the serial input to PBC4.

I0+/I0- is the serial input to PBC0.

15, 16,

17, 18

14, 22

SEL1, SEL2

SEL3, SEL4

SEL0, SEL5

INPUT - TTL.

Port Bypass MUX SELect lines. A HIGH selects Ix. A LOW selects the

output of the previous internal device.

7, 6

44, 43

38, 37

31, 30

24, 25

O1+, O1-

O2+, O2-

O3+, O3-

O4+, O4-

O0+, O0-

OUTPUT - Differential

O1+/O1- is the serial output from MUX1.

O2+/O2- is the serial output from PBC port 1.

O3+/O3- is the serial output from PBC port 2.

O4+/O4- is the serial output from PBC port 3.

O0+/O0- is the serial output from PBC port 4.

13

REFCLK

INPUT - TTL

106.25MHz REFerence CLocK for the internal Clock Multiplier PLL.

NOTE: A reference clock must be provided to the REFCLK pin in order for

the chip to power up in the right state

12

MODE

INPUT - TTL (NOTE: Different for VSC7127T or VSC7127R)

In the VSC7127T, MODE configures the part as a Retimer if LOW or a

Repeater if HIGH. In the VSC7127R, MODE configures the parts as a

Repeater if LOW or a Retimer if HIGH. If unused, tie HIGH or LOW.

20 (VSC7127)

19 (VSC7129

SIGDET

OUTPUT - TTL:

SIGnal DETect output

23 (VSC7127)

22 (VSC7129)

TRST

INPUT - TTL: (Internal Pull-up Resistor)

Test mode input. Pull HIGH or leave open for normal operation.

2

21 (VSC7127)

20 (VSC7129)

VDD

Digital Logic Power Supply

5

42

36

29

26

VDDP1

VDDP2

VDDP3

VDDP4

VDDP0

Power Supply (3.3V) for O1+/-. If unused, connect to V

SS

.

Power Supply (3.3V) for O2+/-. If unused, connect to V

SS

.

Power Supply (3.3V) for O3+/-. If unused, connect to V

SS

.

Power Supply (3.3V) for O4+/-. If unused, connect to V

SS

.

Power Supply (3.3V) for O0+/-. If unused, connect to V

SS

32

VDDA

Analog Power Supply

1, 8, 11, 33, 39

19 (VSC7127)

23 (VSC7129)

VSS

Ground

Data Sheet

VSC7127/VSC7129

Family of Repeater/Retimer and Port

Bypass Circuits for Fibre Channel

VITESSE

SEMICONDUCTOR CORPORATION

Page 10

G52298-0, Rev 4.3

05/01/01

© VITESSE

SEMICONDUCTOR CORPORATION ∑ 741 Calle Plano ∑ Camarillo, CA 93012

Tel: (800) VITESSE ∑ FAX: (805) 987-5896 ∑ Email: prodinfo@vitesse.com

Internet: www.vitesse.com

Package Information

44

34

0.102 MAX. LEAD

COPLANARITY

1

33

23

22

12

G

F

I

H

12

o

TYP

0.17 MAX.

NOTES:

12

o

TYP

K

D

A

0.25

J

0

o

- 8

o

0.25 MAX.

E

0.30 RAD. TYP.

0.20 RAD. TYP.

11

Drawing not to scale.

Cavity up

J

1

All units in mm unless otherwise noted.

Item

mm

Tol.

A

2.45

MAX

D

2.00

+0.10

E

0.35

+.05

F

13.20

+.25

G

10.00

+.10

H

13.20

+.25

I

10.00

+.10

J

0.88

+.15 / -.10

K

0.80

BASIC

44-Pin PQFP 10 x 10 mm

Data Sheet

VSC7127/VSC7129

Family of Repeater/Retimer and Port

Bypass Circuits for Fibre Channel

G52298-0, Rev 4.3

Page 11

05/01/01

© VITESSE

SEMICONDUCTOR CORPORATION ∑ 741 Calle Plano ∑ Camarillo, CA 93012

Tel: (800) VITESSE ∑ FAX: (805) 987-5896 ∑ Email: prodinfo@vitesse.com

Internet: www.vitesse.com

VITESSE

SEMICONDUCTOR CORPORATION

Package Thermal Characteristics

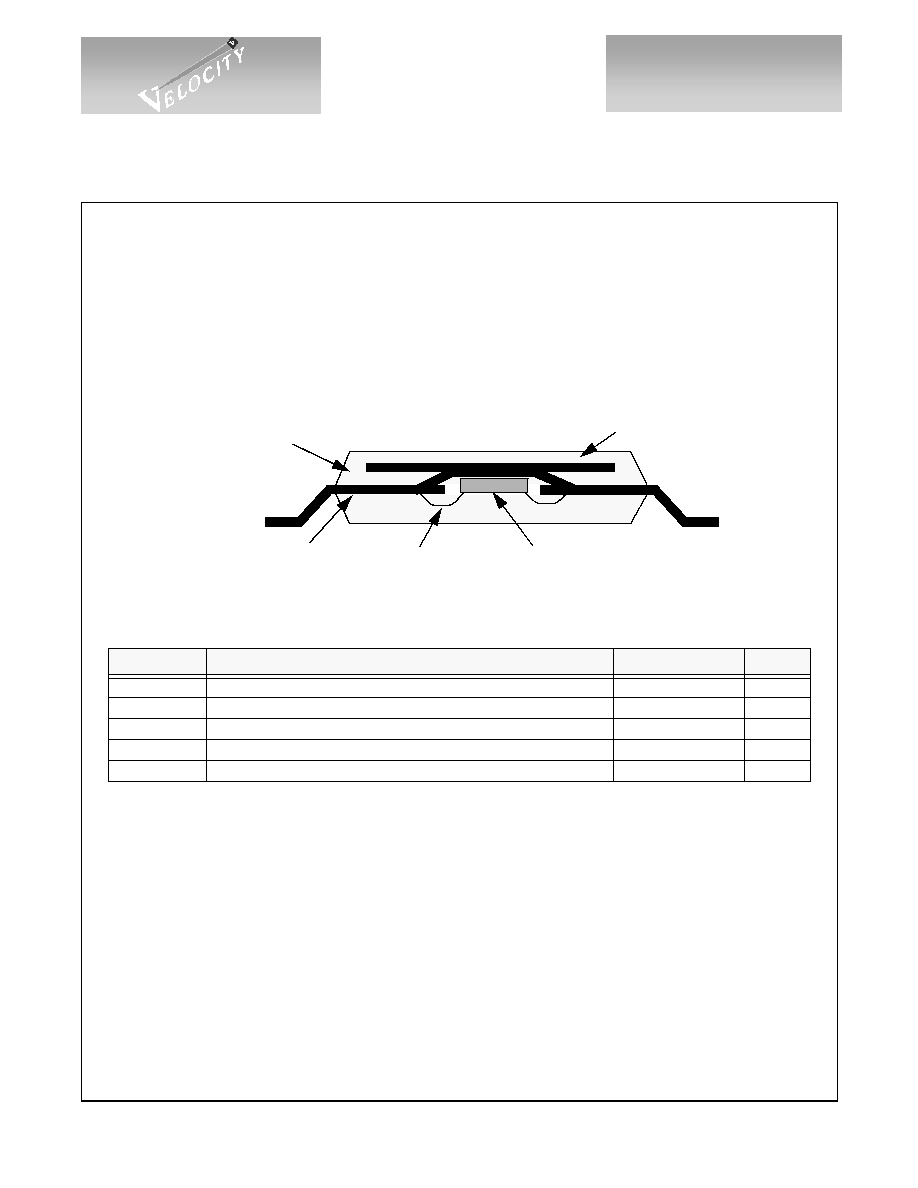

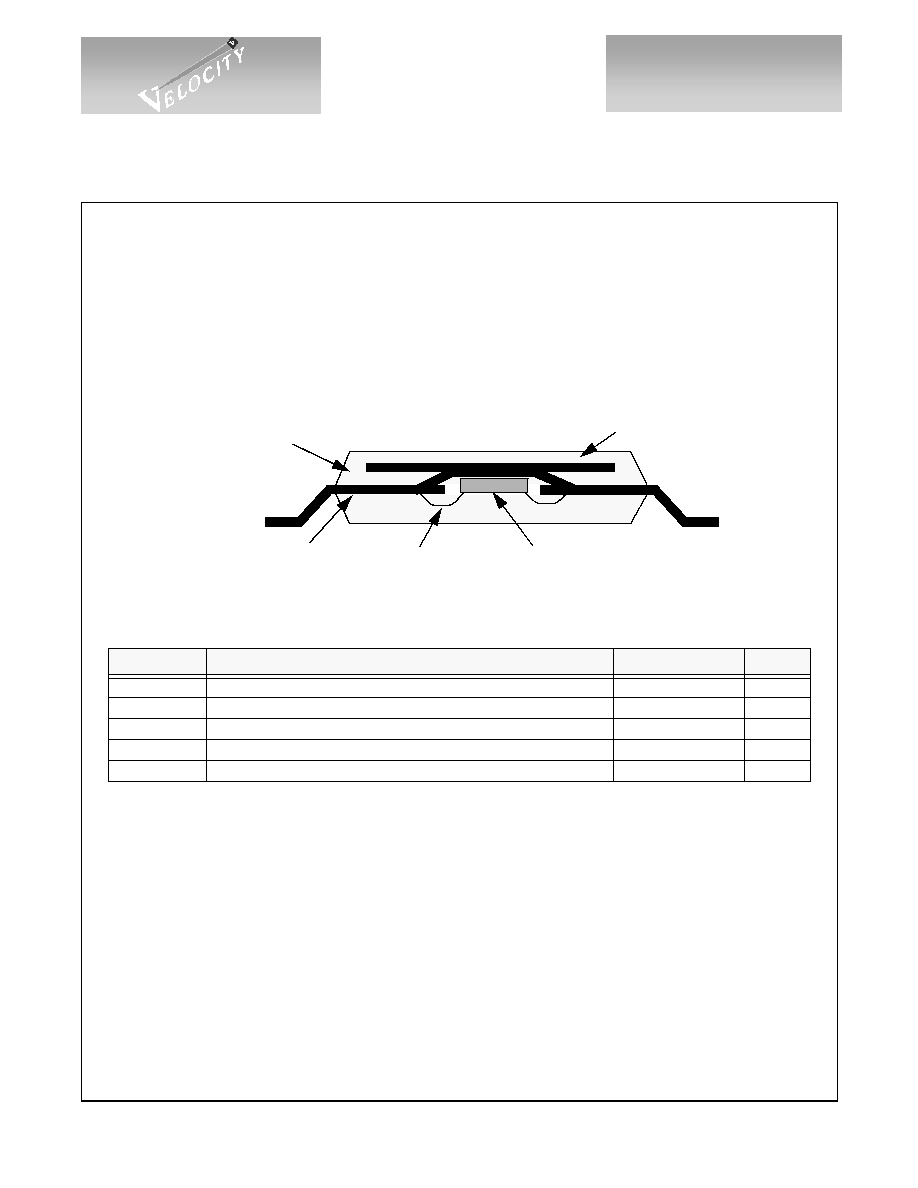

The VSC7127/VSC7129 is packaged in a standard plastic quad flatpack, PQFP, with an embedded, but

unexposed thermal heatslug. This package adheres to industry-standard EIAJ footprints for a 10 mm body, 44

lead PQFP. The package construction is as shown in Figure 6. The 44 PQFP with embedded slug has the thermal

properties shown in Figure 6.

Figure 6: Package Cross Section--10 mm package

Table 5: 44 PQFP Thermal Resistance

The VSC7127/VSC7129 is designed to operate with a case temperature up to 95

o

C. The user must guaran-

tee that the case temperature specification is not violated. With the thermal resistances shown in Table 5, the

10mm PQFP can operate in still air ambient temperatures of 50

o

C [50

o

C = 95

o

C - 0.9W * 50]. If the ambient air

temperature exceeds these limits, some form of cooling through a heatsink or an increase in airflow must be pro-

vided.

Moisture Sensitivity Level

This device is rated at a Moisture Sensitivity Level 3 rating with maximum floor life of 168 hours at 30∫C,

60% relative humidity. Please refer to Application Note AN-20 for appropriate handling procedures.

Symbol

Description

Value

Units

CA-0

Thermal resistance from case-to-ambient, still air

50

o

C/W

CA-100

Thermal resistance from case-to-ambient, 100 LFPM air

43

o

C/W

CA-200

Thermal resistance from case-to-ambient, 200 LFPM air

39

o

C/W

CA-400

Thermal resistance from case-to-ambient, 400 LFPM air

36

o

C/W

CA-600

Thermal resistance from case-to-ambient, 600 LFPM air

34

o

C/W

Copper Heat Spreader

Die

Plastic Molding Compound

Lead

Bond Wire

Data Sheet

VSC7127/VSC7129

Family of Repeater/Retimer and Port

Bypass Circuits for Fibre Channel

VITESSE

SEMICONDUCTOR CORPORATION

Page 12

G52298-0, Rev 4.3

05/01/01

© VITESSE

SEMICONDUCTOR CORPORATION ∑ 741 Calle Plano ∑ Camarillo, CA 93012

Tel: (800) VITESSE ∑ FAX: (805) 987-5896 ∑ Email: prodinfo@vitesse.com

Internet: www.vitesse.com

Ordering Information

The order number for this product is formed by a combination of the device number and package type.

Marking Information

The package is marked with three lines of text as shown in Figure 7 (VSC7127TQM shown).

Figure 7: Package Marking Information

VSC712XX XX

Device Type

Package Type

QM: 44-pin PQFP, 10mm Body

VSC7127T Configured as a Retimer when MODE is HIGH. HDMP-0451 compatible

VSC7127R Configured as a Repeater when MODE is LOW. HDMP-0451 compatible

VSC7129T Configured as a Retimer when MODE is HIGH. HDMP-0452 compatible

VSC7129R Configured as a Repeater when MODE is LOW. HDMP-0452 compatible

VITESSE

VSC7127T QM

####AAAAA

Part Number

DateCode

Package Suffix

Lot Tracking Code

Pin 1 Identifier

(4 or 5 characters)

Notice

Vitesse Semiconductor Corporation ("Vitesse") provides this document for informational purposes only. All information in this document, includ-

ing descriptions of features, functions, performance, technical specifications and availability, is subject to change without notice at any time. Noth-

ing contained in this document shall be construed as extending any warranty or promise, express or implied, that any Vitesse product will be

available as described or will be suitable for or will accomplish any particular task.

Vitesse products are not intended for use in life support appliances, devices or systems. Use of a Vitesse product in such applications without writ-

ten consent is prohibited.