www.vitesse.com

Product

Brief

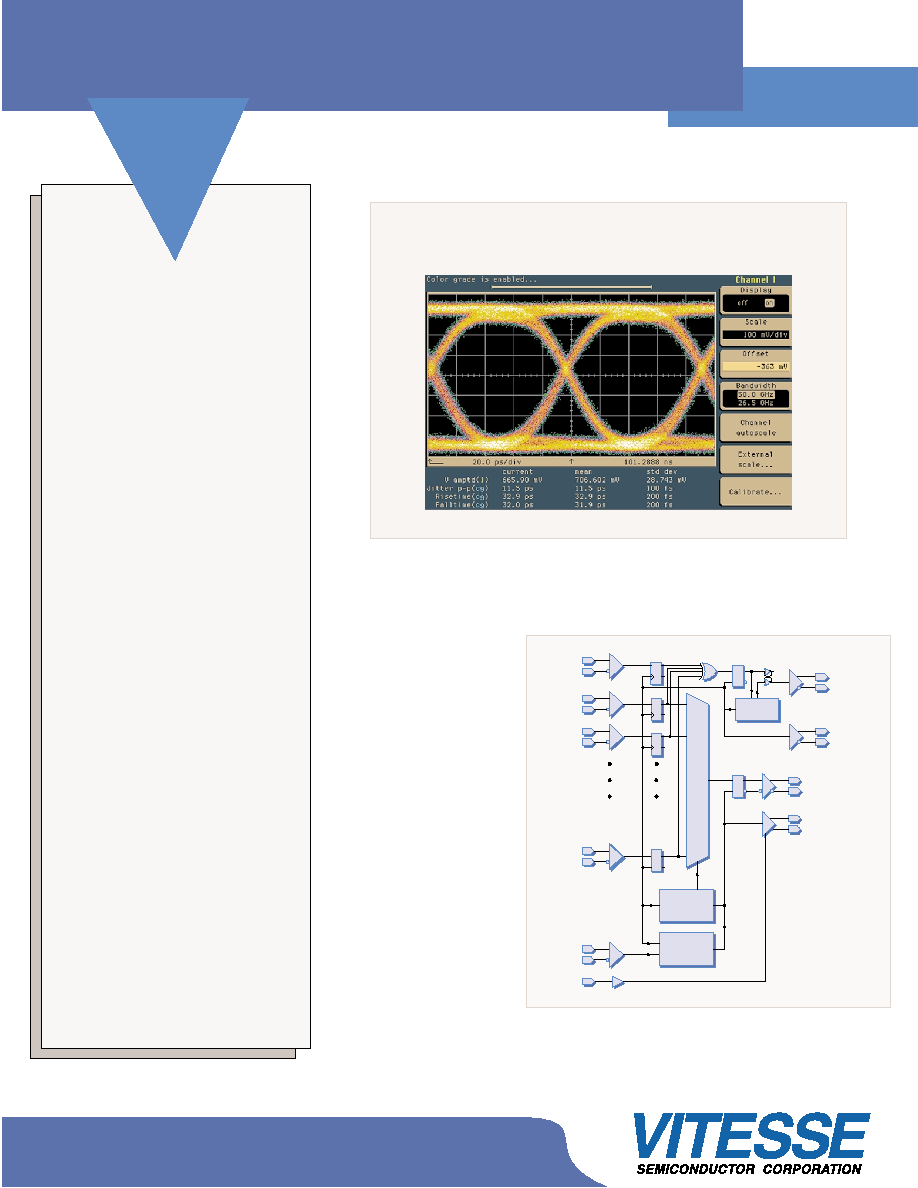

"Best Data Eyes in the Business"

10G PHY

Layer

Products

Physical Layer Products

Vitesse Semiconductor

offers a complete line of

physical layer serializer/

deserializer devices for

use in a broad range of

SONET OC-192 / SDH

STM-64 and forward er-

ror correction applica-

tions. Vitesse has lever-

aged production proven

technology to develop a

family of chip sets that

support a full range of

design requirements

from high-performance

to low-power, perfor-

mance-optimized, appli-

cations.

Features for VSC8171

SONET/SDH 16:1 Mux with CMU

∑

9.953 - 10.7 GHz Operation

∑

16:1 Multiplexer with Integrated

Clock Multiplier

∑

FIFO Companion Device

VSC8273 16 x 622/667 MHz

∑

Supports OC-192 and FEC

Rates with only a Reference

Clock Frequency Change

∑

LVDS Parallel Interface

∑

Parity Checking

∑

High Speed Clock and Serial

Data Output

∑

650 mV (typ) Serial Data Output

∑

35 ps (max) Rise/Fall Times

∑

Meets SONET OC-192 and SDH

STM-64 Jitter Generation

Requirements

∑

-5.2 V Single Power Supply

∑

2.6 W (typ) Power Dissipation

∑

Thermally Enhanced 80-Pin

PQFP and 96-Ball BGA

∑

11.5 - 12.5 GHz Version

Available - VSC8181

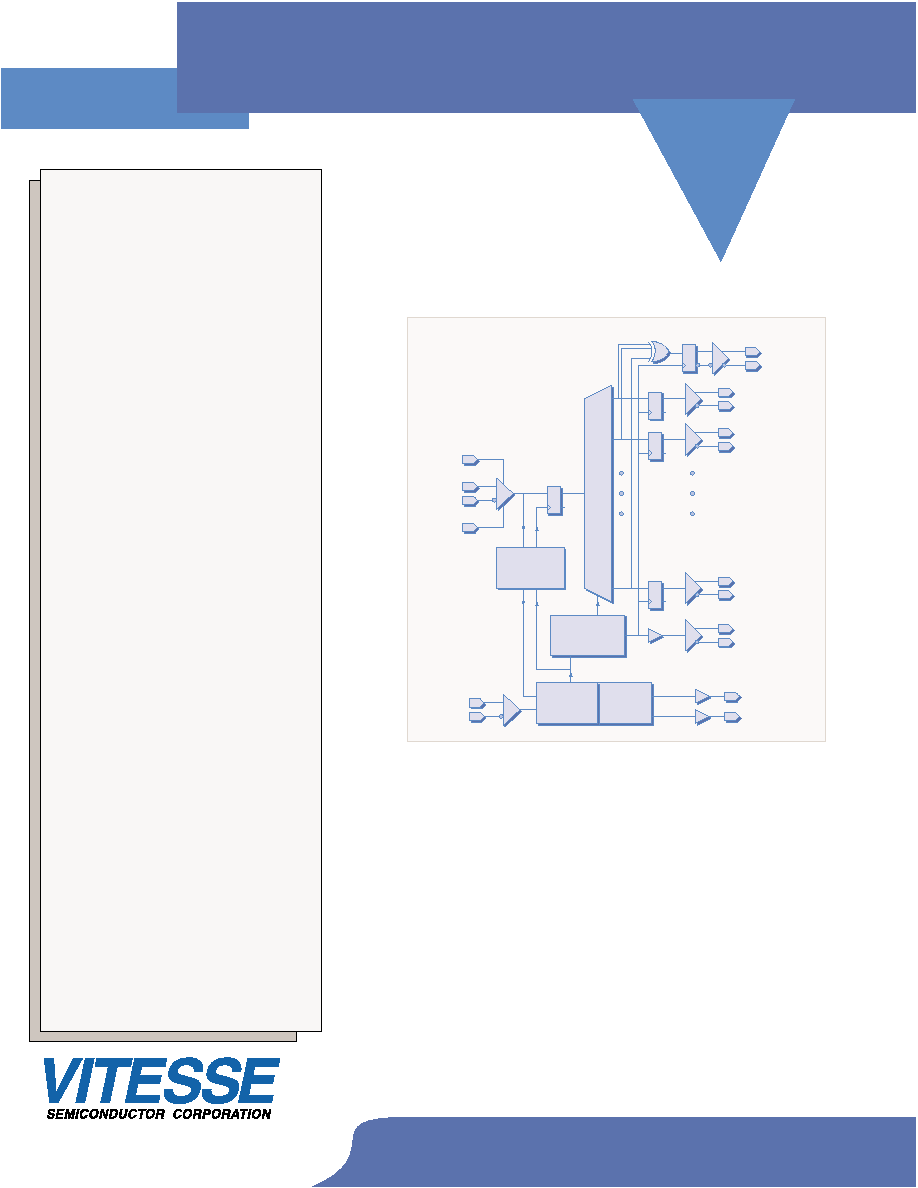

VSC8171 Block Diagram

VITESSE Has Eyes For You

VITESSE Has Eyes For You

PARITY+

PARITY -

DINV ALID+

DINV ALID-

CK16+

CK16-

DOUT+

DOUT -

COUT+

COUT -

Timing

Generator

PLL

D0+

D0-

D1+

D1-

16:1

D15+

D15-

REFCK+

REFCK-

CKOEN

Cloc k

Stretch

Introduction

For more information on Vitesse Products visit the Vitesse web site

at

www.vitesse.com

or contact Vitesse Sales at

(800) VITESSE or

sales@vitesse.com

© Copyright 2000 Vitesse Semiconductor Corporation

and the Vitesse logo are all registered trademarks

of Vitesse Semiconductor Corp;oration

www.vitesse.com

Product

Brief

10G PHY

Layer

Products

"Best Data Eyes in the Business"

Features for VSC8172

SONET/SDH 1:16 Demux with CDR

∑

9.953 - 10.7 GHz Operation

∑

1:16 Demultiplexer with Limiting

Amplifier and Integrated Clock

Recovery

∑

LVDS Parallel Interface

∑

Parity Bit Calculation

∑

Loss of Lock Detection

∑

50 mV (min) Input Sensitivity

∑

Supports OC-192 and FEC

Rates with only a Reference

Clock Frequency Change

∑

Meets SONET OC-192 and SDH

STM-64 Jitter Tolerance

Requirements

∑

-5.2 V / -2 V Power Supplies

∑

3.4 W (typ) Power Dissipation

∑

Thermally Enhanced 100-Pin

PQFP and 96-Ball BGA

∑

11.5 - 12.5 GHz Version

Available - VSC8182

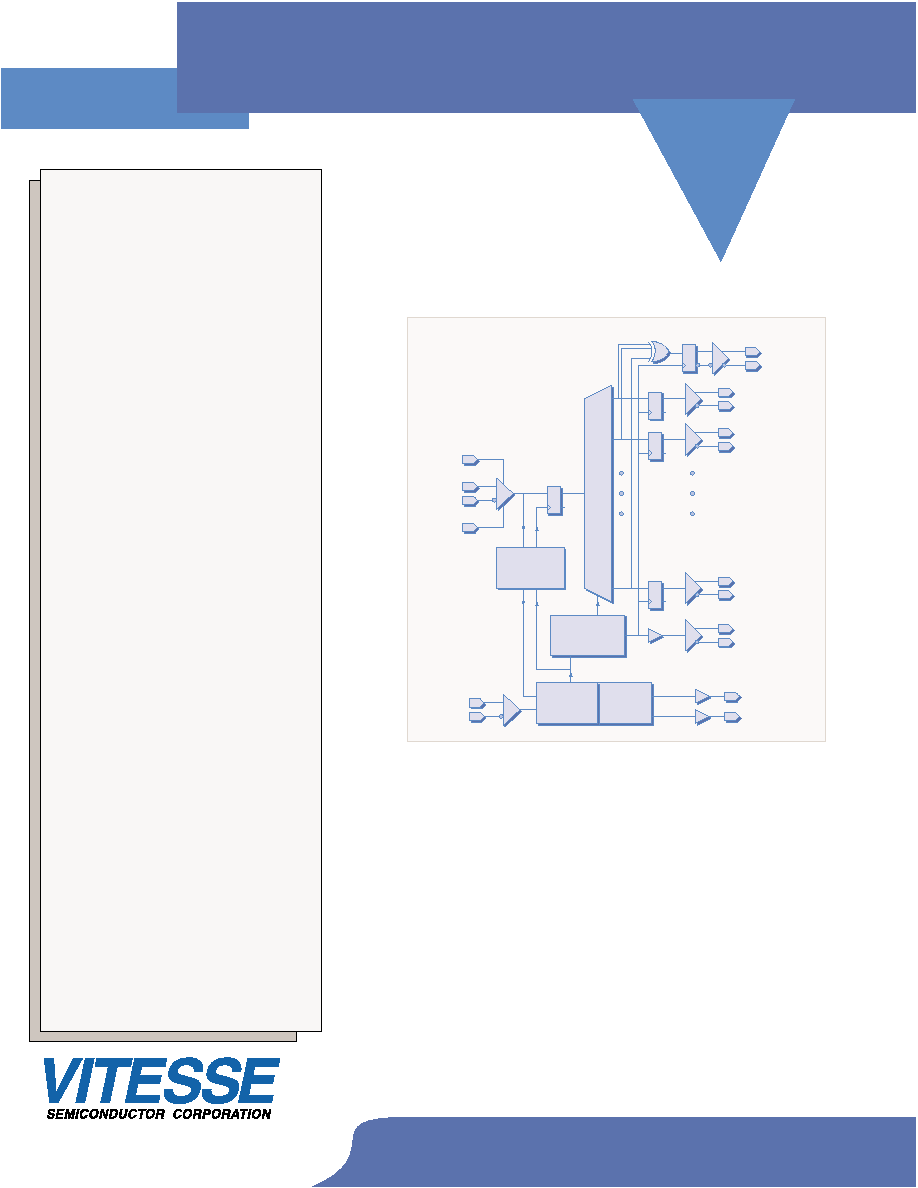

VSC8172 Block Diagram

The VSC8171 mux offers integration of a high output swing mux with a low-

jitter generation clock multiplier unit. The VSC8172 demux offers an inte-

grated limiting amplifier, demux and high jitter tolerant clock and data recov-

ery unit. Vitesse has eyes for you: "The best data eyes in the business."

NOREF

LOL

DETECT

LOCK

LOSS

OF

REFCK-

REFCK+

TIMING

PARITY+

PARITY-

RECOVERY

DATA-

1:16

CK16+

CK16-

D15-

D15+

D1-

D1+

D0+

D0-

CLOCK

GENERATOR

PLL

DATA+

OFF-

OFF+