1

White Electronic Designs Corporation (508) 366-5151 www.whiteedc.com

Oct. 2002 Rev. 4A

ECO #15655

EDI9F37512C

FEATURES

n 512Kx37 bit CMOS Static RAM

Access Times: 45 and 55ns

Individual Byte Selects

Fully Static, No Clocks

TTL Compatible I/O

n High Density Package

72 lead SIMM, No. 418

Common Data Inputs and Outputs

n Single +5V (±10%) Supply Operation

The EDI9F37512C is a high speed 20 megabit Static RAM module

organized as 512K words x 37 bits. This module is constructed from

five 512Kx8 Static RAMs in TSOP packages on an epoxy laminate

(FR4) board.

Four write selects (W0-W3) are used to independently enable the four

bytes. Reading and writing can be executed on individual bytes or any

combination of multiple bytes through proper use of selects.

The EDI9F37512C is offered in a 72 lead SIMM which allows 20

megabits of memory to be placed in less than 1.5 square inch of board

space.

All inputs and outputs are TTL compatible and operate from a single

5V supply. Fully asynchronous circuitry requires no clocks or refresh-

ing for operation and provides equal access and cycle times for ease

of use.

The SIMM module contains two Presence Detect pins which are used

to identify module memory density in applications where alternate

modules can be interchanged.

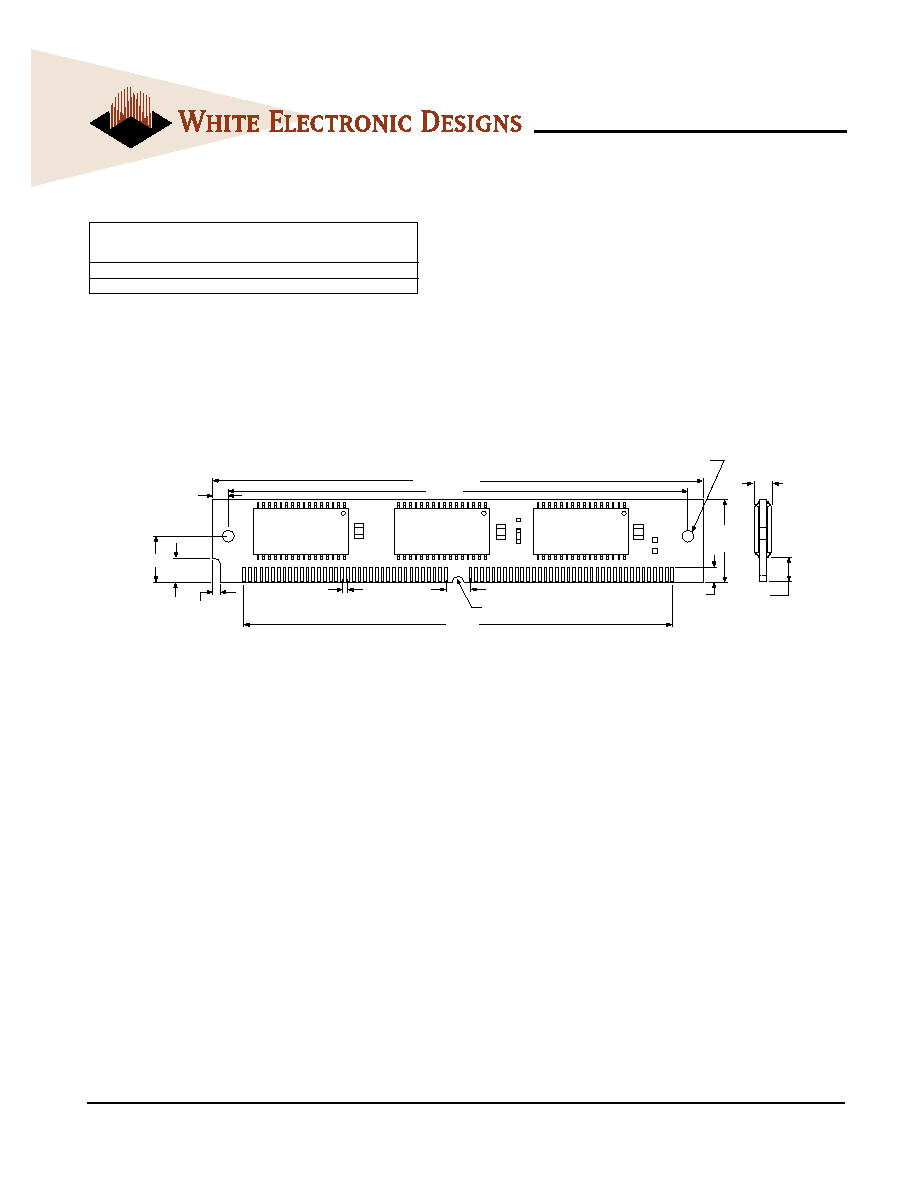

PIN CONFIGURATIONS AND BLOCK DIAGRAM

PIN NAMES

512Kx37 Static RAM CMOS, High Speed Module

DESCRIPTION

Aÿ-A18

Address Inputs

E

Chip Enables

W0-W3

Write Enable

AW

Parity Write Enable

G

Output Enable

DQÿ-DQ31

Common Data Input/Output

VCC

Power (+5V±10%)

VSS

Ground

PD0-PD1

Presence Detect

FIG. 1

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

AD3

AD4

AD1

AD2

VSS

AD0

AW

DQ0

DQ8

DQ1

DQ9

DQ2

DQ10

DQ3

DQ11

VCC

A0

A1

A2

A3

A4

A5

DQ12

DQ4

DQ13

DQ5

DQ14

DQ6

DQ15

DQ7

VSS

E

A6

A7

W1

W0

9F37512C Pin Config.

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

W3

W2

A18

A17

G

VSS

DQ24

DQ16

DQ25

DQ17

DQ26

DQ18

DQ27

DQ19

A8

A9

A10

A11

A12

A13

VCC

A14

A15

DQ20

DQ28

DQ21

DQ29

DQ22

DQ30

DQ23

DQ31

VSS

A16

PD1

NC

PD0

DQ0-DQ7

DQ8-DQ15

DQ16-DQ23

DQ24-DQ31

W0

W1

W2

W3

AW

AD0-AD4

A0-A18

G

E

9F37512C Blk Dia

512k

x 8

512k

x 8

512k

x 8

512k

x 8

512k

x 8

2

White Electronic Designs Corporation (508) 366-5151 www.whiteedc.com

Oct. 2002 Rev. 4A

ECO #15655

EDI9F37512C

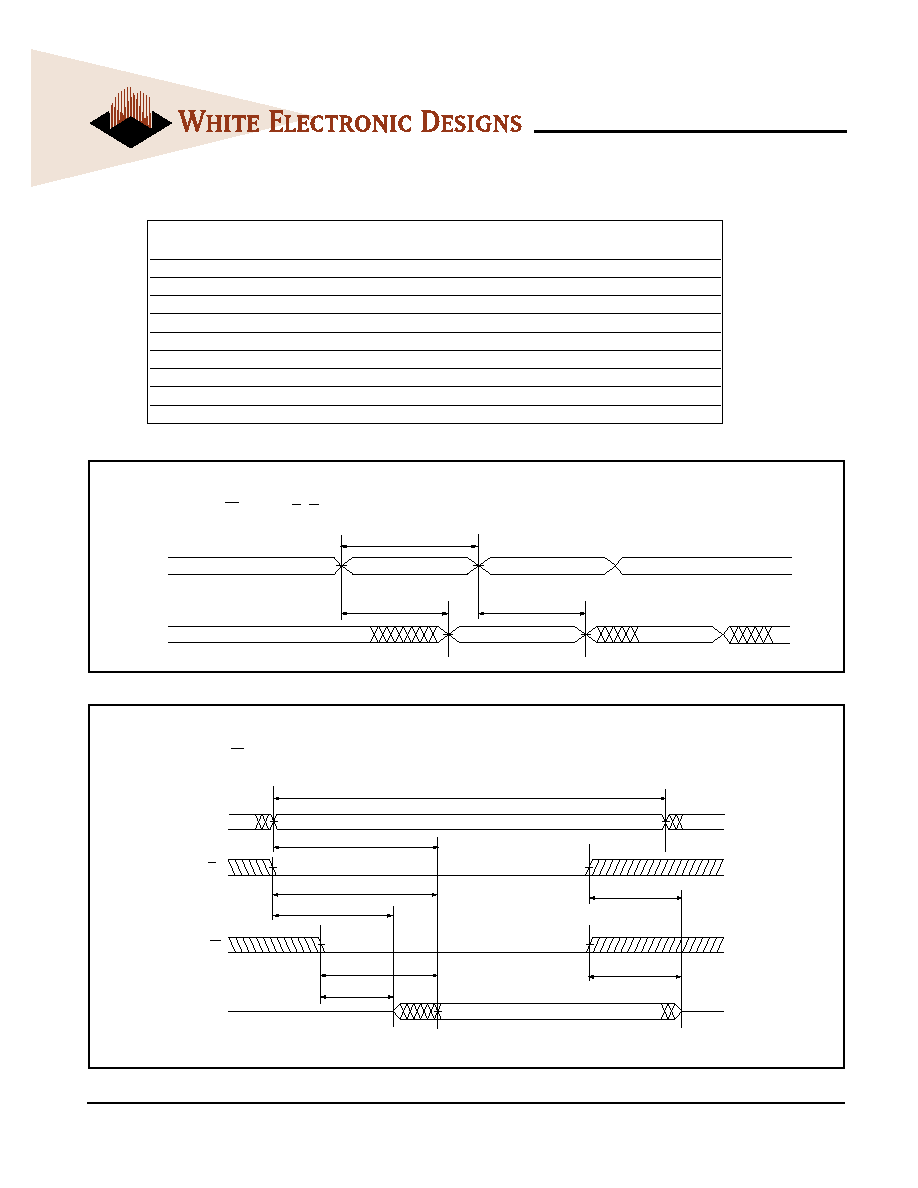

AC CHARACTERISTICS READ CYCLE

READ CYCLE 2 - W HIGH

Notes: 1. Parameter guaranteed, but not tested.

Symbo

45ns

55ns

Parameter

JEDEC

Alt.

Min

Max

Min

Max

Units

Read Cycle Time

TAVAV

TRC

45

55

ns

Address Access Time

TAVQV

TAA

45

55

ns

Chip Enable Access

TELQV

TACS

45

55

ns

Chip Enable to Output in Low Z (1)

TELQX

TCLZ

3

3

ns

Chip Disable to Output in High Z (1)

TEHQZ

TCHZ

18

25

ns

Output Hold from Address Change

TAVQX

TOH

3

3

ns

Output Enable to Output Valid

TGLQV

TOE

15

25

ns

Output Enable to Output in Low Z (1)

TGLQX

TOLZ

0

0

ns

Output Disable to Output in High Z(1)

TGHQZ

TOHZ

15

15

ns

FIG. 3

READ CYCLE 1 - W HIGH, G, E LOW

FIG. 2

ADDRESS 1

ADDRESS 2

TAVAV

DATA 1

DATA 2

TAVQV

TAVQX

9F37512C Rd Cyc1

A

Q

TGHQZ

TELQV

TELQX

E

G

Q

TEHQZ

A

TAVAV

TGLQV

TGLQX

TAVQV

9F37512C Rd Cyc2

3

White Electronic Designs Corporation (508) 366-5151 www.whiteedc.com

Oct. 2002 Rev. 4A

ECO #15655

EDI9F37512C

Notes: 1. Parameter guaranteed, but not tested.

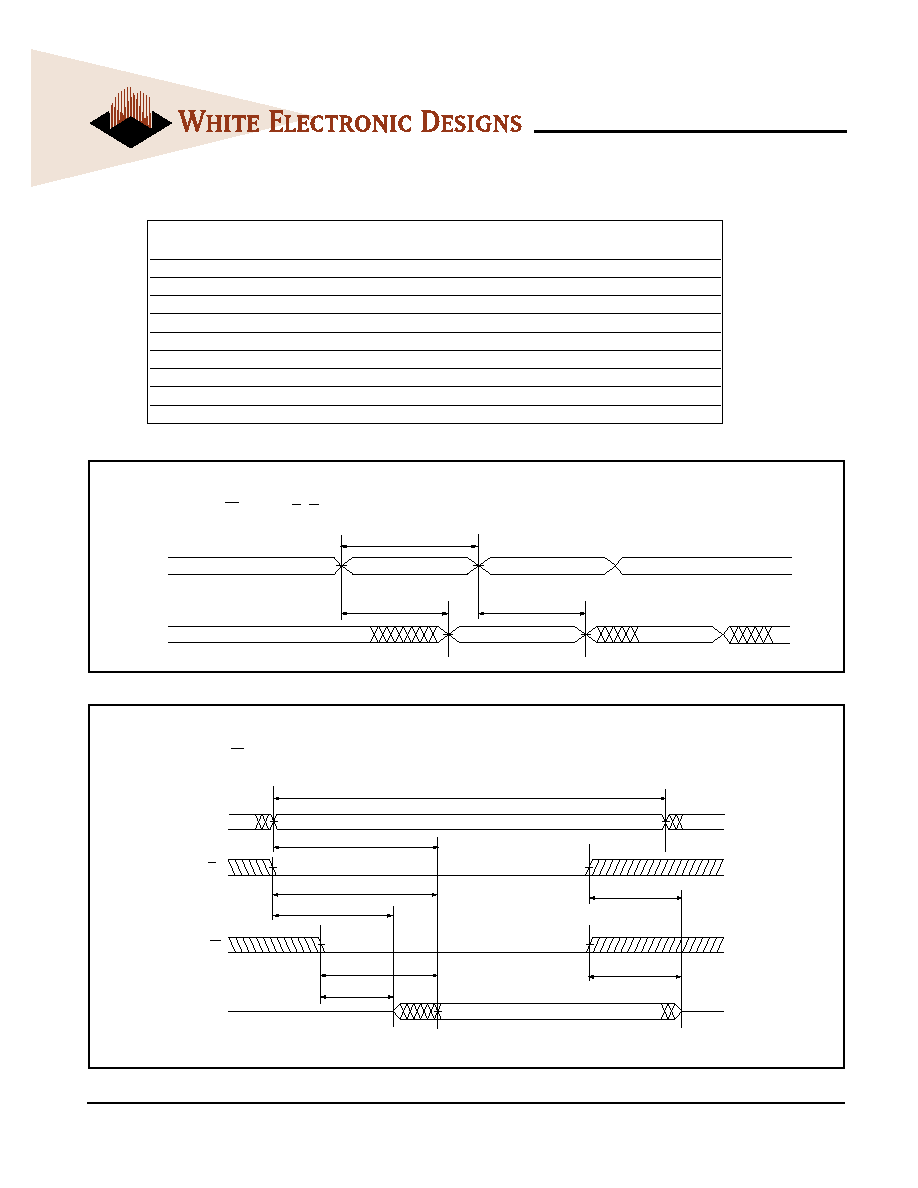

AC CHARACTERISTICS WRITE CYCLE

WRITE CYCLE 2 - E CONTROLLED

FIG. 4

Symbol

45ns

55ns

Parameter

JEDEC

Alt.

Min

Max

Min

Max

Units

Write Cycle Time

TAVAV

TWC

45

55

ns

Chip Enable to End of Write

TELWH

TCW

25

45

ns

TWLEH

TCW

25

45

ns

Address Setup Time

TAVWL

TAS

0

0

ns

TAVEL

TAS

0

0

ns

Address Valid to End of Write

TAVWH

TAW

25

45

ns

TAVEH

TAW

25

45

ns

Write Pulse Width

TWLWH

TWP

25

40

ns

TELEH

TWP

25

40

ns

Write Recovery Time

TWHAX

TWR

0

0

ns

TEHAX

TWR

0

0

ns

Data Hold Time

TWHDX

TDH

0

0

ns

TEHDX

TDH

0

0

ns

Write to Output in High Z (1)

TWLQZ

TWHZ

0

6

0

28

ns

Data to Write Time

TDVWH

TDW

20

30

ns

TDVEH

TDW

20

30

ns

Output Active from End of Write (1)

TWHQX

TWLZ3

3

ns

A

TAVEL

HIGH Z

TAVAV

9F37512C Write Cyc2

TELEH

E

TAVEH

TEHAX

W

TWLEH

TEHDX

TDVEH

Q

DATA VALID

D

DATASHEET APPROVALS

ECO#

EDI PART NO.

NEW REV

DATE

APPROVAL:

INITIAL

DATE

CORRECTION ON PAGES

JUAN GUZMAN

MUKESH TRIVEDI

PAUL MARIEN

LARRY WINROTH

DAVE KELLY

MARK DOWNEY

DAVE HARRISON

TONY LEE

BOB KHEDERIAN

LUIS ESTELLA

YES

NO

LINE

:________

WILL THIS DATASHEET GO ON THE WEB?

FAMILY:

____________

PROD.TYPE:

________

ORG:___________

IS THIS A NEW DATASHEET?

DENSITY:________

SPEED:__________

WILL THIS DATASHEET REPLACE AN EXISTING

PKG:____________

DATASHEET THAT'S ALREADY ON THE WEB?

VOLTAGE:________

IF YES, WHAT DATASHEET IS IT REPLACING?

WHAT SECTION SHOULD THIS DATASHEET BE

PLACED IN ON THE WEB?

AFTER REVIEWING OR MAKING CORRECTIONS ON THE DATASHEET (S)

PLEASE SIGN-OFF ON THIS SHEET AND ,MAKE YOUR CORRECTIONS ≠ON

THE ORIGINAL COPY(S).

AFTER REVIEWING THE DATA SHEET, TEST ENGINEERING WILL COMPLETE THE SECTION BELOW.

TEST PROGRAM CHANGE REQUIRED:

YES:_________NO____________DATE:___________

TEST ENGINEER SIGNATURE___________________

IF YES, DO NOT RELEASE DATA SHEET UNTIL TEST PROGRAM CHANGE IS COMPLETED.

TEST PROGRAM CHANGE COMPLETION DATE:__________

TEST PROGRAM NAME AND REVISION_________________

TEST ENGINEER SIGNATURE__________________________

FO-00342R1.DOC

ECO# 14942

SHEET 1 OF

1

10/8/02

10/10/02

10/10/02

ED19F37512C

4A

15655

10/8/02

L.K.

M.A.