W78E516B

8-BIT MICROCONTROLLER

Publication Release Date: February 2000

- 1 - Revision A3

GENERAL DESCRIPTION

The W78E516B is an 8-bit microcontroller which has an in-system programmable MTP-ROM for

firmware updating. The instruction set of the W78E516B is fully compatible with the standard 8052.

The W78E516B contains a 64K bytes of main MTP-ROM and a 4K bytes of auxiliary MTP-ROM

which allows the contents of the 64KB main MTP-ROM to be updated by the loader program located

at the 4KB auxiliary MTP-ROM; 512 bytes of on-chip RAM; four 8-bit bi-directional and bit-

addressable I/O ports; an additional 4-bit port P4; three 16-bit timer/counters; a serial port. These

peripherals are supported by a eight sources two-level interrupt capability. To facilitate programming

and verification, the MTP-ROM inside the W78E516B allows the program memory to be programmed

and read electronically. Once the code is confirmed, the user can protect the code for security.

The W78E516B microcontroller has two power reduction modes, idle mode and power-down mode,

both of which are software selectable. The idle mode turns off the processor clock but allows for

continued peripheral operation. The power-down mode stops the crystal oscillator for minimum power

consumption. The external clock can be stopped at any time and in any state without affecting the

processor.

FEATURES

∑

Fully static design 8-bit CMOS microcontroller up to 40 MHz.

∑

64K bytes of in-system programmable MTP-ROM for Application Program (APROM).

∑

4K bytes of auxiliary MTP-ROM for Loader Program (LDROM).

∑

512 bytes of on-chip RAM. (including 256 bytes of AUX-RAM, software selectable)

∑

64K bytes program memory address space and 64K bytes data memory address space.

∑

Four 8-bit bi-directional ports.

∑

One 4-bit multipurpose programmable port.

∑

Three 16-bit timer/counters

∑

One full duplex serial port

∑

Six-sources, two-level interrupt capability

∑

Built-in power management

∑

Code protection

∑

Packaged in

-

DIP 40: W78E516B-24/40

-

PLCC 44: W78E516BP-24/40

W78E516B

- 2 -

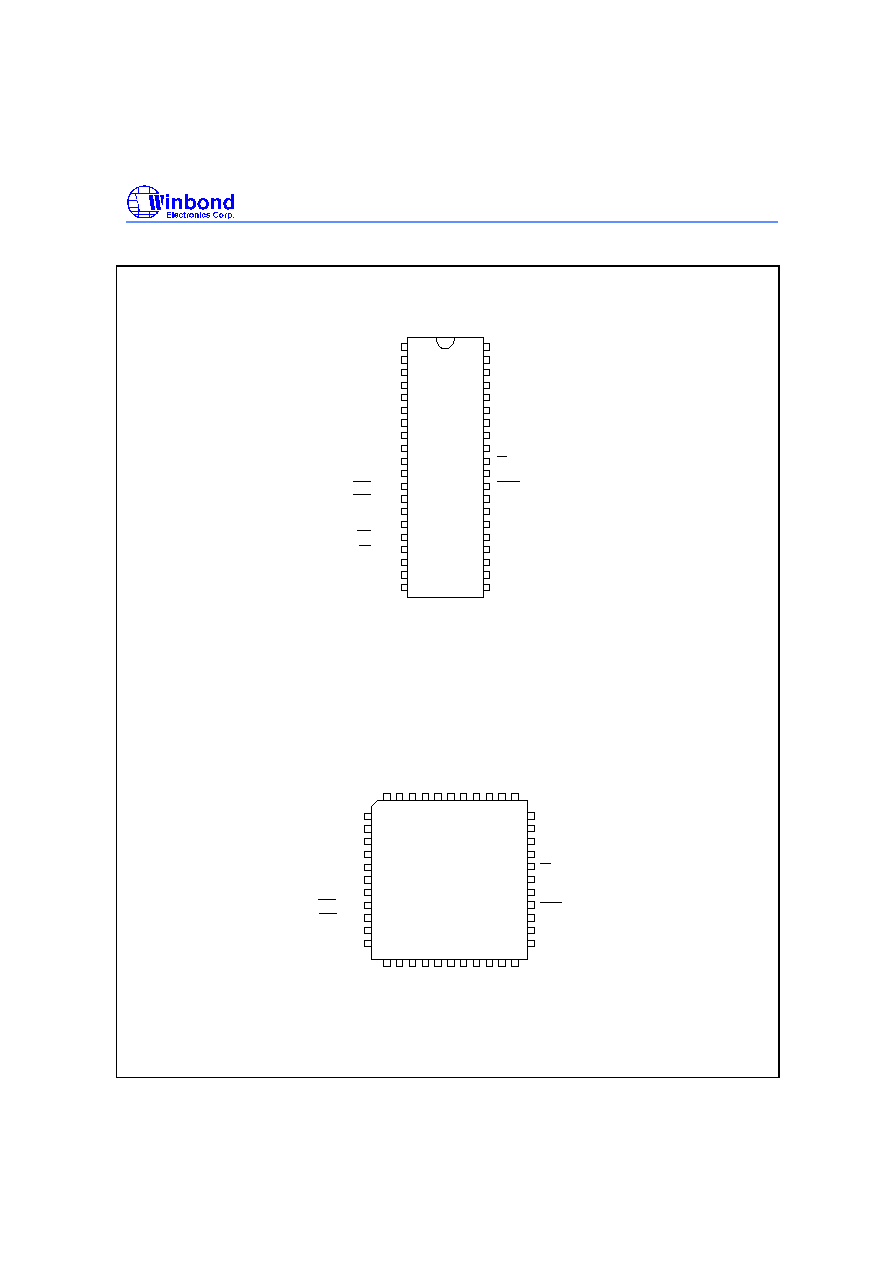

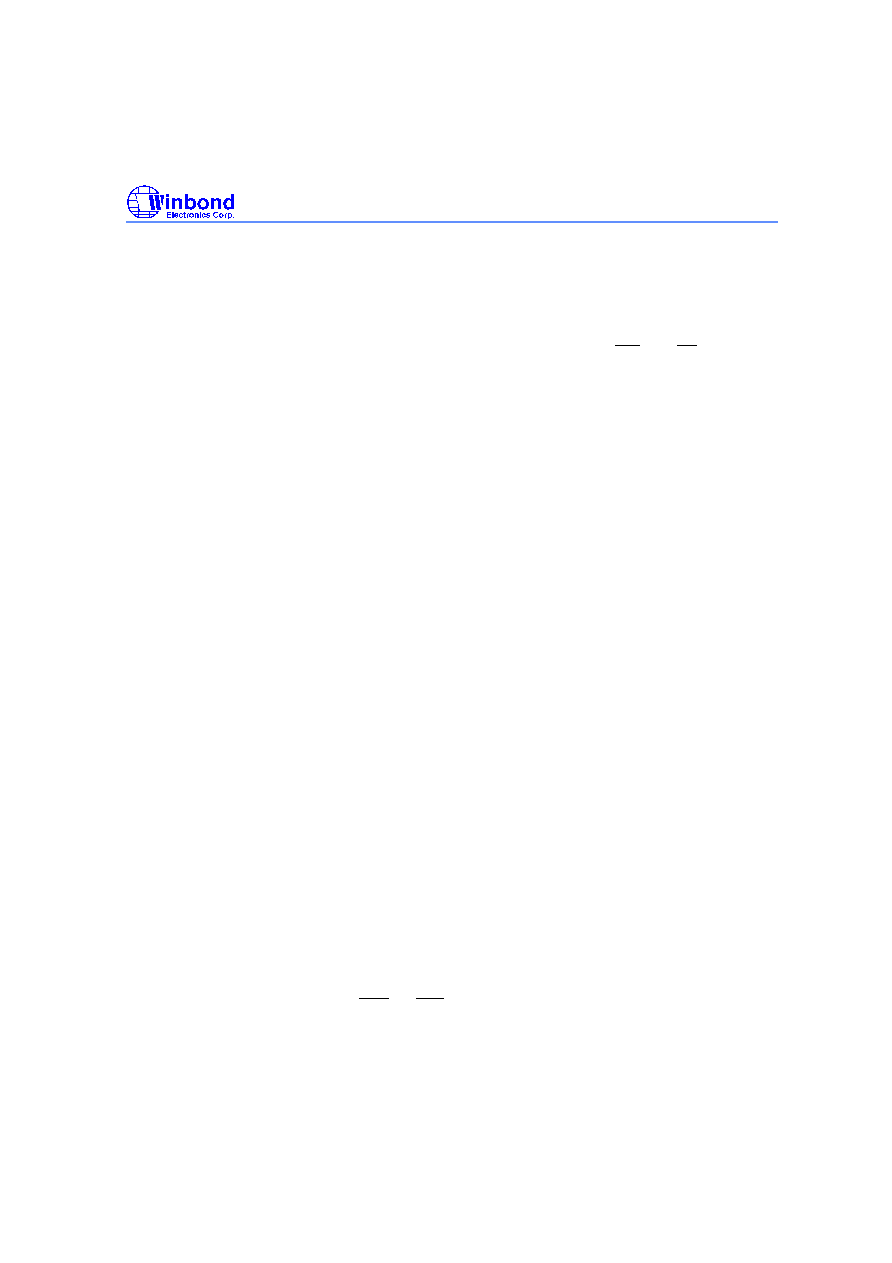

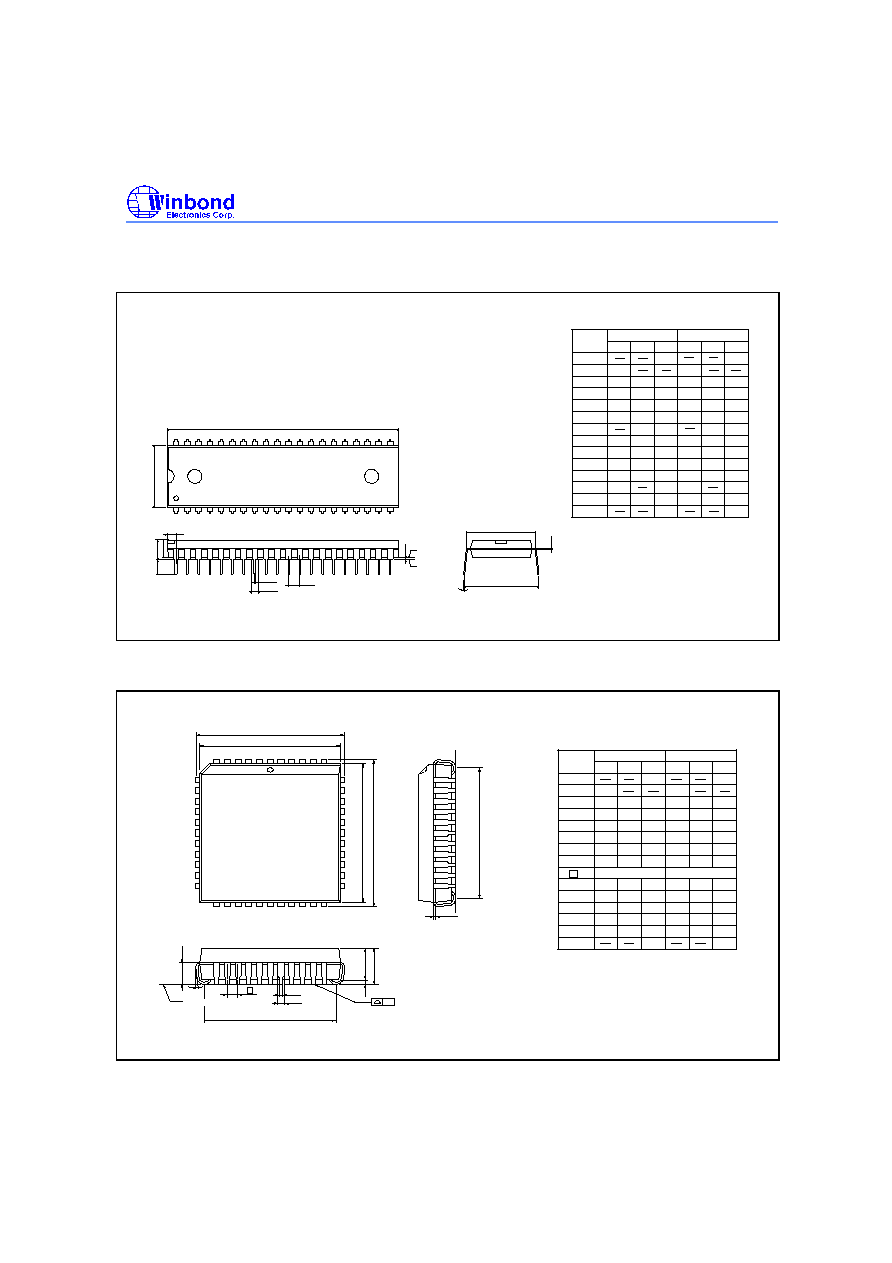

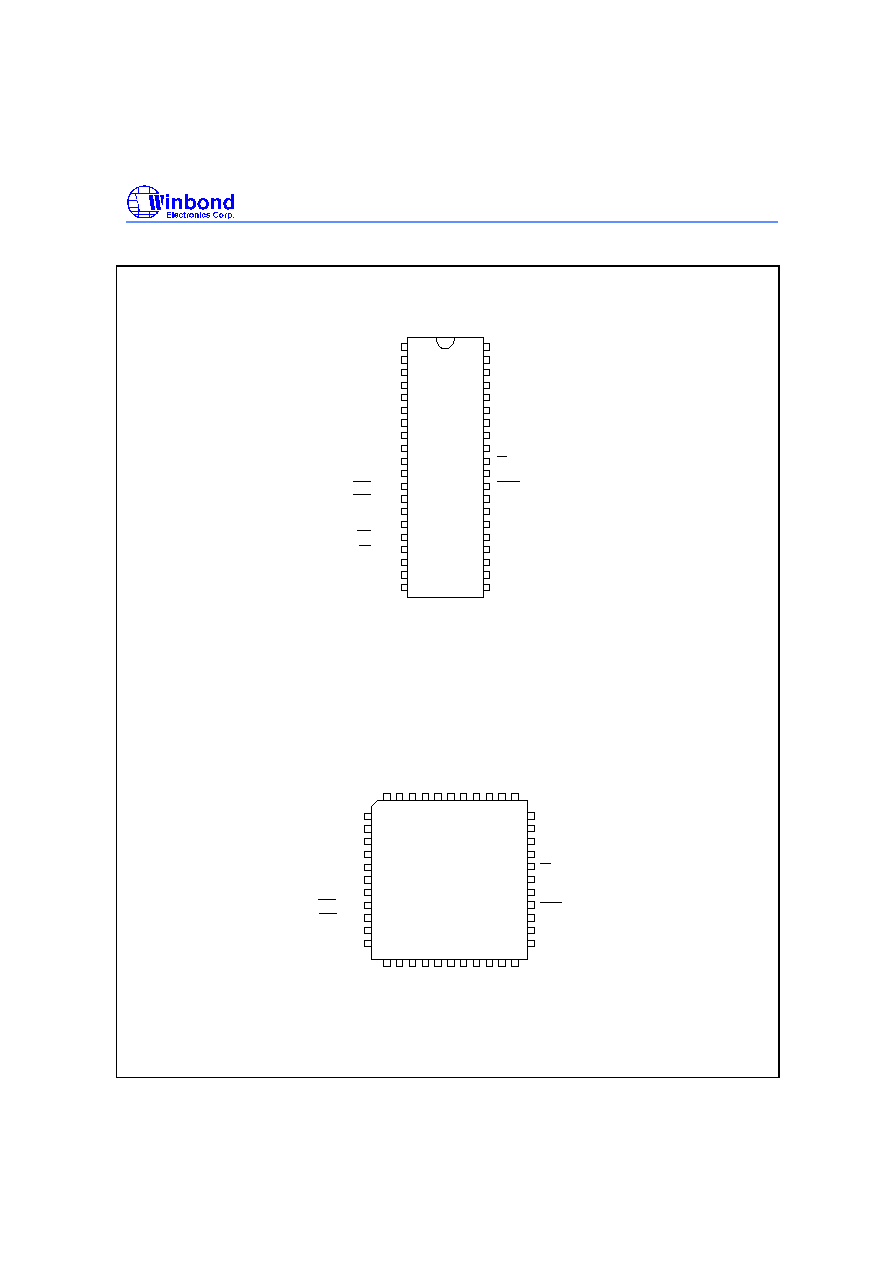

PIN CONFIGURATIONS

VDD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

39

40

34

35

36

37

38

30

31

32

33

26

27

28

29

21

22

23

24

25

P0.0, AD0

P0.1, AD1

P0.2, AD2

P0.3, AD3

P0.4, AD4

P0.5, AD5

P0.6, AD6

P0.7, AD7

EA

ALE

PSEN

P2.5, A13

P2.6, A14

P2.7, A15

P2.0, A8

P2.1, A9

P2.2, A10

P2.3, A11

P2.4, A12

T2, P1.0

40-pin DIP (W78E516B)

P1.2

P1.3

P1.4

P1.5

P1.6

RXD, P3.0

TXD, P3.1

P1.7

RST

INT0, P3.2

INT1, P3.3

T0, P3.4

T1, P3.5

WR, P3.6

RD, P3.7

XTAL1

XTAL2

VSS

T2EX, P1.1

44-pin PLCC (W78E516BP)

40

2 1 44 43 42 41

6 5

4 3

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

10

9

8

7

14

13

12

11

16

15

P1.5

P1.6

P1.7

RST

RXD, P3.0

TXD, P3.1

INT0, P3.2

INT1, P3.3

T0, P3.4

T1, P3.5

A

D

3

,

P

0

.

3

T

2

,

P

1

.

0

P

1

.

2

V

D

D

A

D

2

,

P

0

.

2

A

D

1

,

P

0

.

1

A

D

0

,

P

0

.

0

T

2

E

X

,

P

1

.

1

P

1

.

3

P

1

.

4

X

T

A

L

1

V

S

S

P

2

.

4

,

A

1

2

P

2

.

3

,

A

1

1

P

2

.

2

,

A

1

0

P

2

.

1

,

A

9

P

2

.

0

,

A

8

X

T

A

L

2

P

3

.

7

,

/

R

D

P

3

.

6

,

/

W

R

P0.4, AD4

P0.5, AD5

P0.6, AD6

P0.7, AD7

EA

ALE

PSEN

P2.7, A15

P2.6, A14

P2.5, A13

P4.1

P

4

.

0

P4.3

P

4

.

2

W78E516B

Publication Release Date: February 2000

- 3 - Revision A3

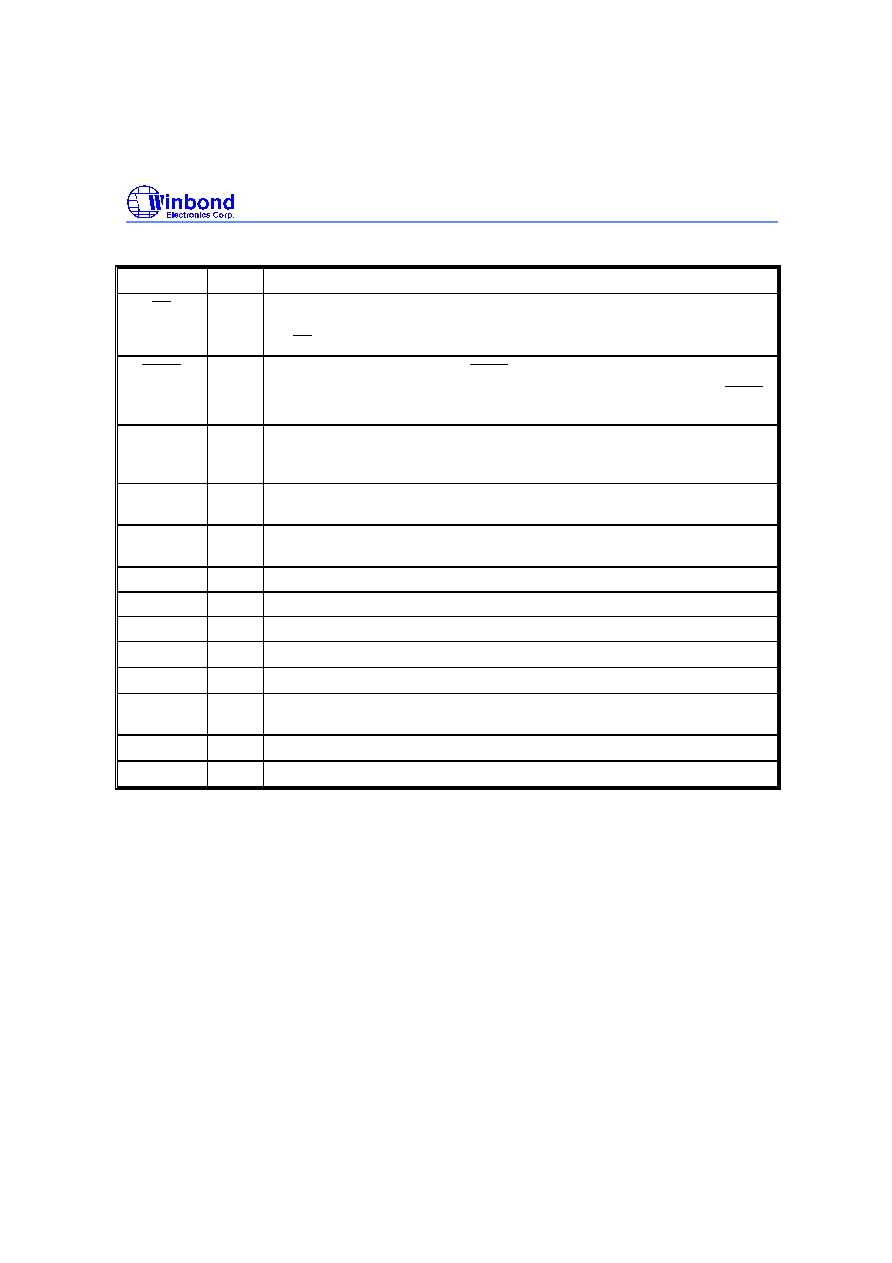

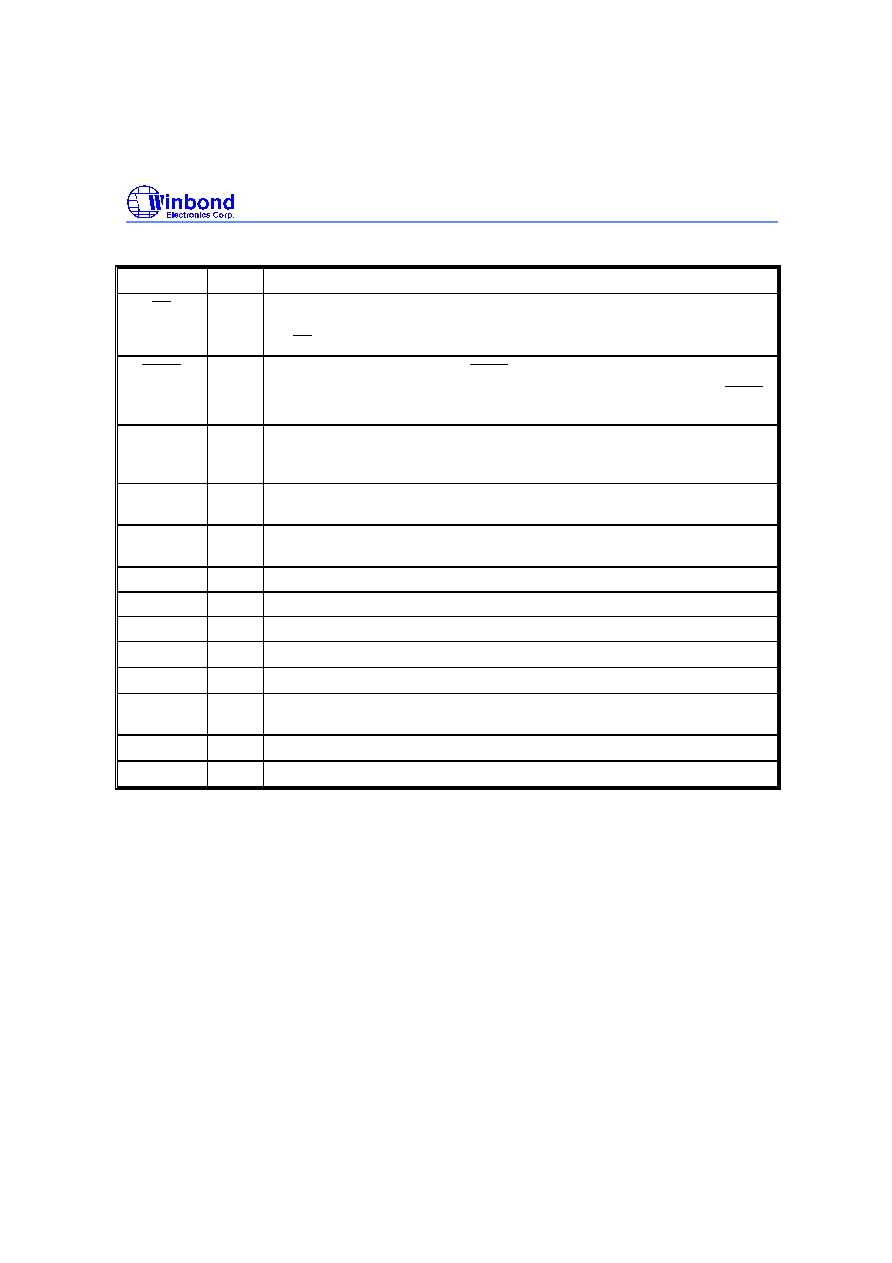

PIN DESCRIPTION

SYMBOL TYPE

DESCRIPTIONS

EA

I

EXTERNAL ACCESS ENABLE: This pin forces the processor to execute the

external ROM. The ROM address and data will not be presented on the bus if

the EA pin is high.

PSEN

O H PROGRAM STORE ENABLE: PSEN enables the external ROM data in the

Port 0 address/data bus. When internal ROM access is performed, no PSEN

strobe signal outputs originate from this pin.

ALE

O H ADDRESS LATCH ENABLE: ALE is used to enable the address latch that

separates the address from the data on Port 0. ALE runs at 1/6th of the

oscillator frequency.

RST

I L RESET: A high on this pin for two machine cycles while the oscillator is

running resets the device.

XTAL1

I

CRYSTAL 1: This is the crystal oscillator input. This pin may be driven by an

external clock.

XTAL2

O

CRYSTAL 2: This is the crystal oscillator output. It is the inversion of XTAL1.

V

SS

I

GROUND: ground potential.

V

DD

I

POWER SUPPLY: Supply voltage for operation.

P0.0

-

P0.7

I/O D PORT 0: Function is the same as that of standard 8052.

P1.0

-

P1.7

I/O H PORT 1: Function is the same as that of standard 8052.

P2.0

-

P2.7

I/O H PORT 2: Port 2 is a bi-directional I/O port with internal pull-ups. This port also

provides the upper address bits for accesses to external memory.

P3.0

-

P3.7

I/O H PORT 3: Function is the same as that of the standard 8052.

P4.0

-

P4.3

I/O H PORT 4: A bi-directional I/O. See details below.

* Note:

TYPE I: input, O: output, I/O: bi-directional, H: pull-high, L: pull-low, D: open drain

PORT4

Another bit-addressable port P4 is also available and only 4 bits (P4<3:0>) can be used. This port

address is located at 0D8H with the same function as that of port P1,

Example:

P4 REG 0D8H

MOV P4, #0AH ; Output data "A" through P4.0

-

P4.3.

MOV A, P4 ; Read P4 status to Accumulator.

SETB P4.0 ; Set bit P4.0

CLR P4.1 ; Clear bit P4.1

W78E516B

- 4 -

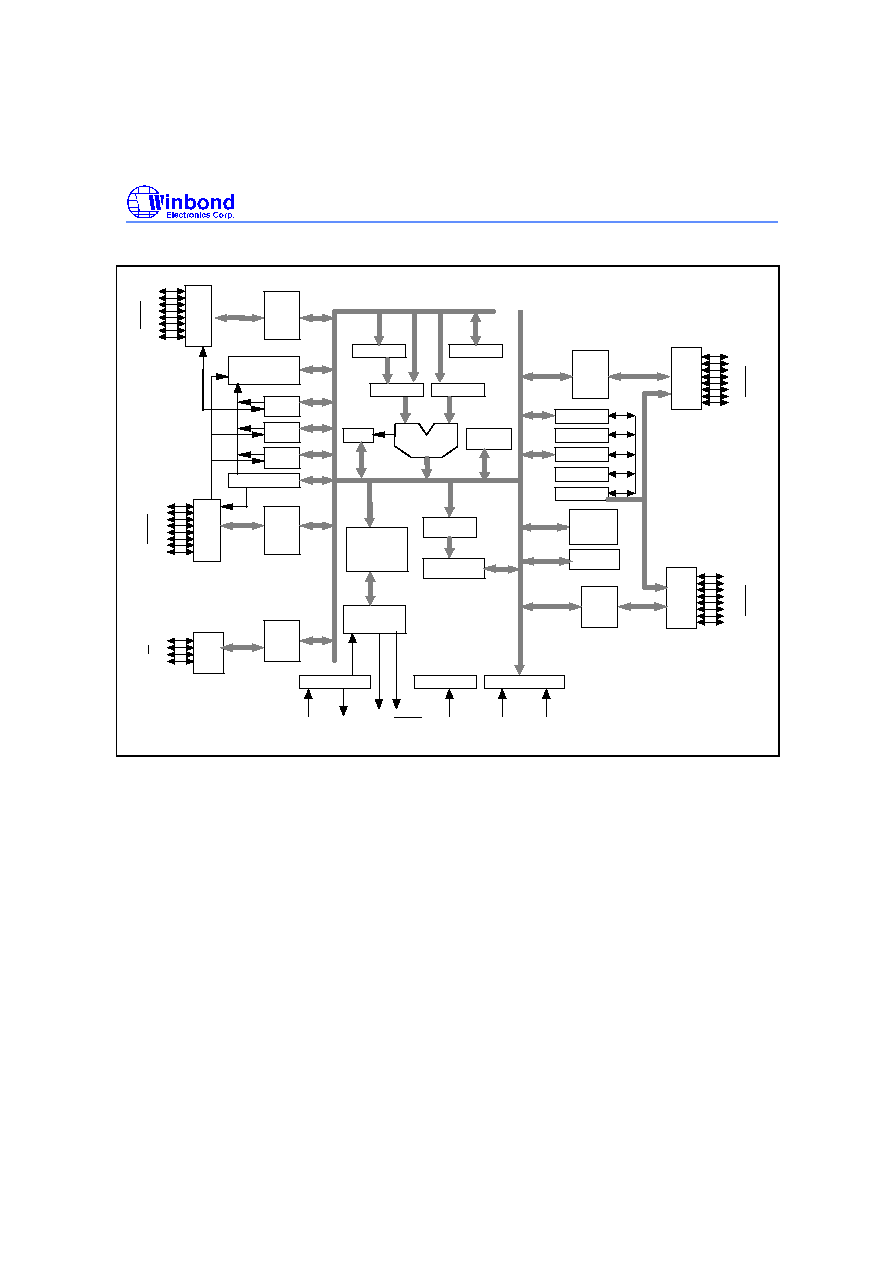

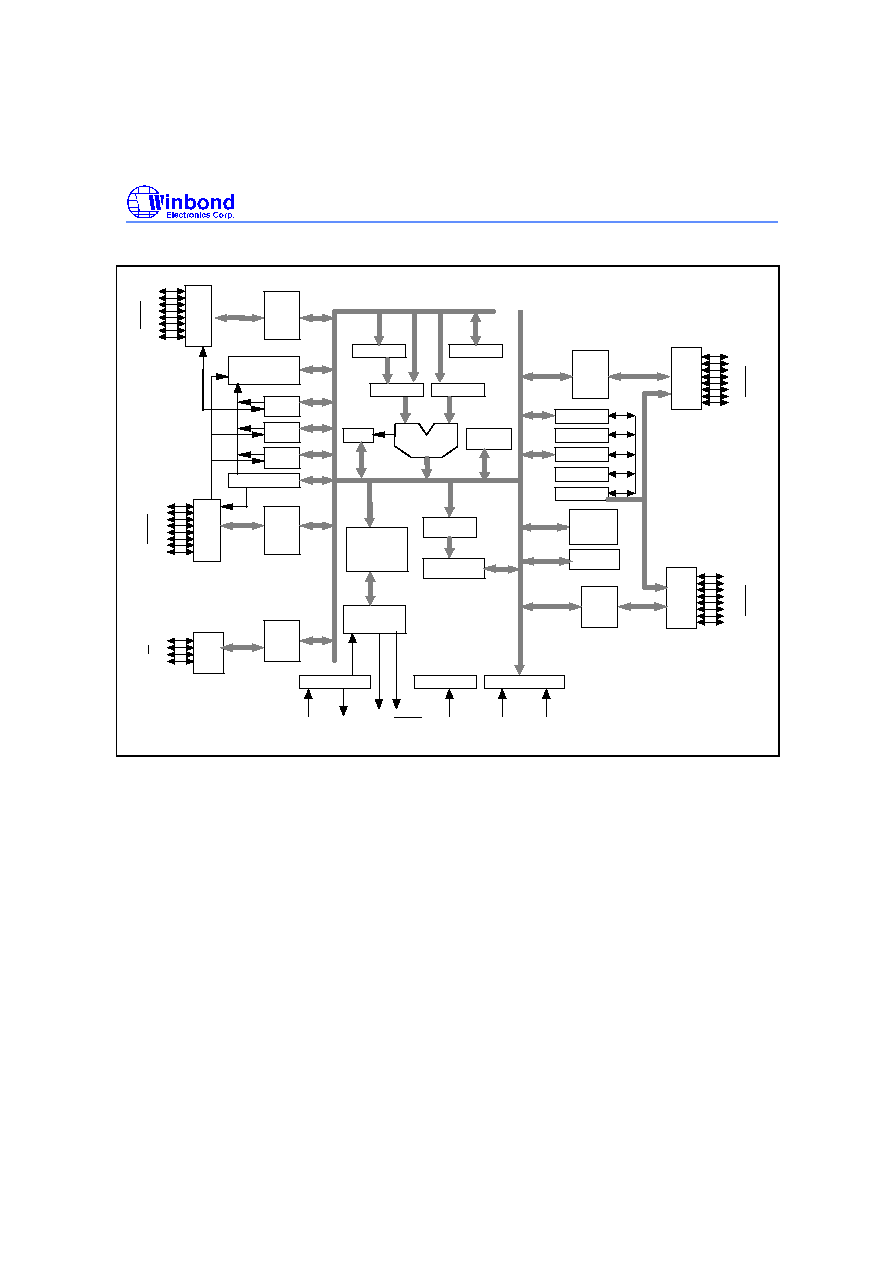

BLOCK DIAGRAM

P3.0

P3.7

P1.0

P1.7

ALU

Port 0

Latch

Port 1

Latch

Timer

1

Timer

0

Timer

2

Port

1

UART

XTAL1

PSEN

ALE

Vss

VCC

RST

XTAL2

Oscillator

Interrupt

PSW

Instruction

Decoder

&

Sequencer

Reset Block

Bus & Clock

Controller

SFR RAM

Address

Power control

512 bytes

RAM & SFR

Stack

Pointer

B

Addr. Reg.

Incrementor

PC

DPTR

Temp Reg.

T2

T1

ACC

Port 3

Latch

Port 4

Latch

Port

3

Port 2

Latch

P4.0

P4.3

Port

4

Port

0

Port

2

P2.0

P2.7

P0.0

P0.7

64KB

MTP-ROM

4KB

MTP-ROM

FUNCTIONAL DESCRIPTION

The W78E516B architecture consists of a core controller surrounded by various registers, four

general purpose I/O ports, one special purpose programmable 4-bits I/O port, 512 bytes of RAM,

three timer/counters, a serial port and an internal 74373 latch and 74244 buffer which can be

switched to port2. The processor supports 111 different opcodes and references both a 64K program

address space and a 64K data storage space.

RAM

The internal data RAM in the W78E516B is 512 bytes. It is divided into two banks: 256 bytes of

scratchpad RAM and 256 bytes of AUX-RAM. These RAMs are addressed by different ways.

∑

RAM 0H

-

127H can be addressed directly and indirectly as the same as in 8051. Address pointers

are R0 and R1 of the selected register bank.

∑

RAM 128H

-

255H can only be addressed indirectly as the same as in 8051. Address pointers are

R0, R1 of the selected registers bank.

W78E516B

Publication Release Date: February 2000

- 5 - Revision A3

∑

AUX-RAM 0H

-

255H is addressed indirectly as the same way to access external data memory with

the MOVX instruction. Address pointer are R0 and R1 of the selected register bank and DPTR

register. An access to external data memory locations higher than 255H will be performed with the

MOVX instruction in the same way as in the 8051. The AUX-RAM is disable after a reset. Setting

the bit 4 in CHPCON register will enable the access to AUX-RAM. When AUX-RAM is enabled the

instructions of "MOVX @Ri" will always access to on-chip AUX-RAM. When executing from internal

program memory, an access to AUX-RAM will not affect the Ports P0, P2, WR and RD .

Timers 0, 1, and 2

Timers 0, 1, and 2 each consist of two 8-bit data registers. These are called TL0 and TH0 for Timer

0, TL1 and TH1 for Timer 1, and TL2 and TH2 for Timer 2. The TCON and TMOD registers provide

control functions for timers 0, 1. The T2CON register provides control functions for Timer 2. RCAP2H

and RCAP2L are used as reload/capture registers for Timer 2. The operations of Timer 0 and Timer

1 are the same as in the W78C51. Timer 2 is a 16-bit timer/counter that is configured and controlled

by the T2CON register. Like Timers 0 and 1, Timer 2 can operate as either an external event counter

or as an internal timer, depending on the setting of bit C/T2 in T2CON. Timer 2 has three operating

modes: capture, auto-reload, and baud rate generator. The clock speed at capture or auto-reload

mode is the same as that of Timers 0 and 1.

Clock

The W78E516B is designed with either a crystal oscillator or an external clock. Internally, the clock is

divided by two before it is used by default. This makes the W78E516B relatively insensitive to duty

cycle variations in the clock.

Crystal Oscillator

The W78E516B incorporates a built-in crystal oscillator. To make the oscillator work, a crystal must

be connected across pins XTAL1 and XTAL2. In addition, a load capacitor must be connected from

each pin to ground, and a resistor must also be connected from XTAL1 to XTAL2 to provide a DC

bias when the crystal frequency is above 24 MHz.

External Clock

An external clock should be connected to pin XTAL1. Pin XTAL2 should be left unconnected. The

XTAL1 input is a CMOS-type input, as required by the crystal oscillator. As a result, the external clock

signal should have an input one level of greater than 3.5 volts.

Power Management

Idle Mode

Setting the IDL bit in the PCON register enters the idle mode. In the idle mode, the internal clock to

the processor is stopped. The peripherals and the interrupt logic continue to be clocked. The

processor will exit idle mode when either an interrupt or a reset occurs.

Power-down Mode

When the PD bit in the PCON register is set, the processor enters the power-down mode. In this

mode all of the clocks are stopped, including the oscillator. To exit from power-down mode is by a

hardware reset or external interrupts INT0 to INT1 when enabled and set to level triggered.

Reduce EMI Emission

The W78E516B allows user to diminish the gain of on-chip oscillator amplifier by using programmer

W78E516B

- 6 -

to clear the B7 bit of security register. Once B7 is set to 0, a half of gain will be decreased. Care must

be taken if user attempts to diminish the gain of oscillator amplifier, reducing a half of gain may affect

the external crystal operating improperly at high frequency above 24 MHz. The value of R and C1, C2

may need some adjustment while running at lower gain.

Reset

The external RESET signal is sampled at S5P2. To take effect, it must be held high for at least two

machine cycles while the oscillator is running. An internal trigger circuit in the reset line is used to

deglitch the reset line when the W78E516B is used with an external RC network. The reset logic also

has a special glitch removal circuit that ignores glitches on the reset line. During reset, the ports are

initialized to FFH, the stack pointer to 07H, PCON (with the exception of bit 4) to 00H, and all of the

other SFR registers except SBUF to 00H. SBUF is not reset.

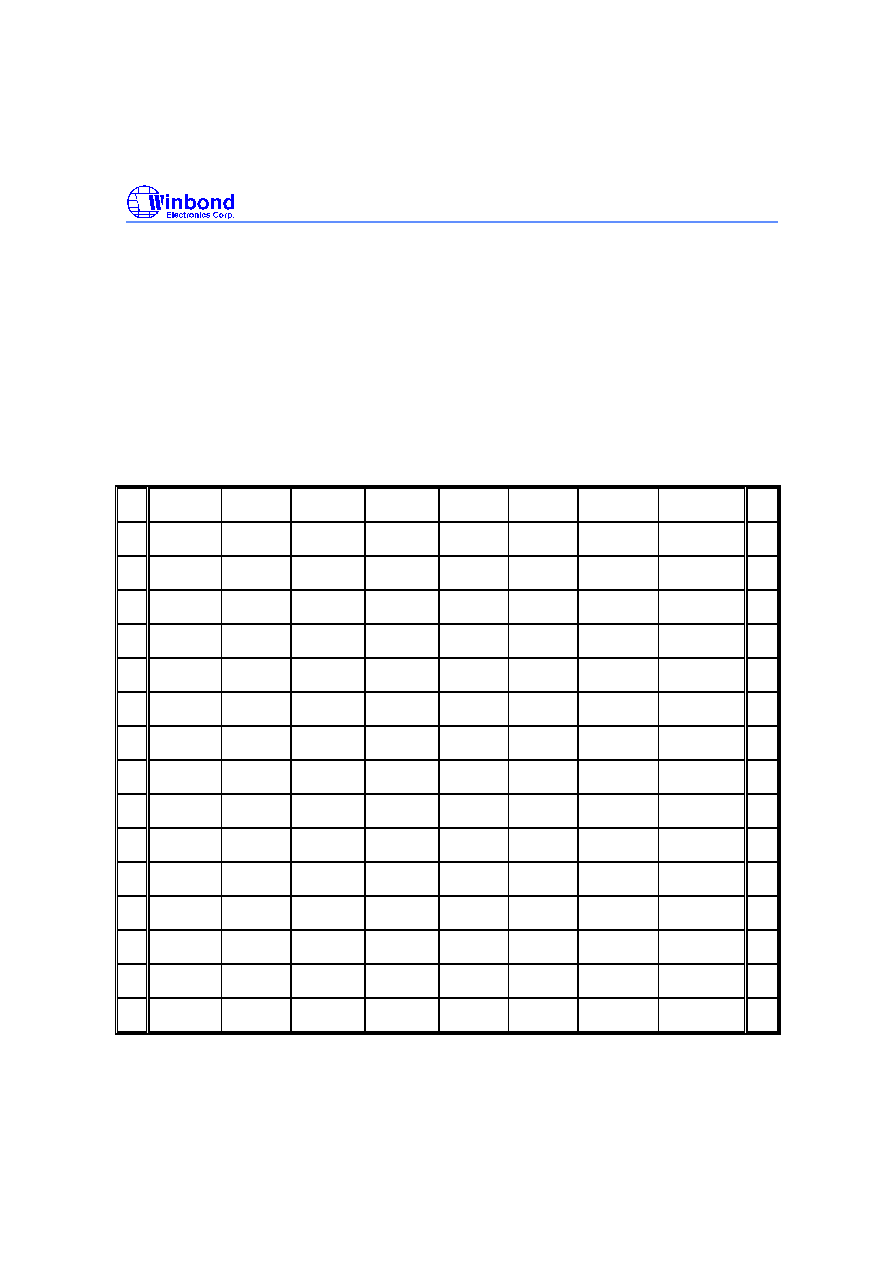

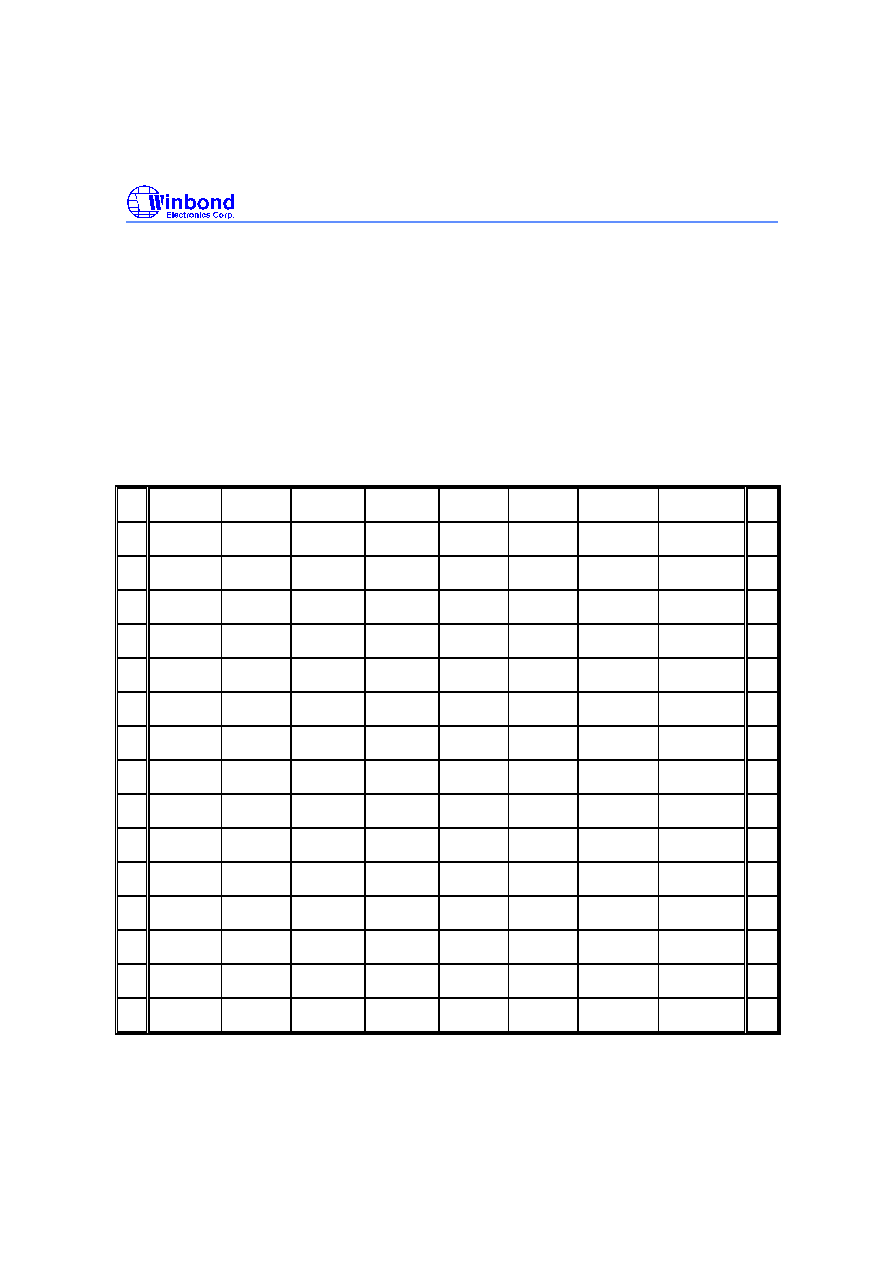

W78E516B Special Function Registers (SFRs) and Reset Values

F8

FF

F0

+B

00000000

CHPENR

00000000

F7

E8

EF

E0

+ACC

00000000

E7

D8

+P4

xxxx1111

DF

D0

+PSW

00000000

D7

C8

+T2CON

00000000

RCAP2L

00000000

RCAP2H

00000000

TL2

00000000

TH2

00000000

CF

C0

XICON

00000000

SFRAL

00000000

SFRAH

00000000

SFRFD

00000000

SFRCN

00000000

C7

B8

+IP

00000000

CHPCON

0xx00000

BF

B0

+P3

00000000

B7

A8

+IE

00000000

AF

A0

+P2

11111111

A7

98

+SCON

00000000

SBUF

xxxxxxxx

9F

90

+P1

11111111

97

88

+TCON

00000000

TMOD

00000000

TL0

00000000

TL1

00000000

TH0

00000000

TH1

00000000

8F

80

+P0

11111111

SP

00000111

DPL

00000000

DPH

00000000

PCON

00110000

87

Notes:

1.The SFRs marked with a plus sign(+) are both byte- and bit-addressable.

2. The text of SFR with bold type characters are extension function registers.

W78E516B

Publication Release Date: February 2000

- 7 - Revision A3

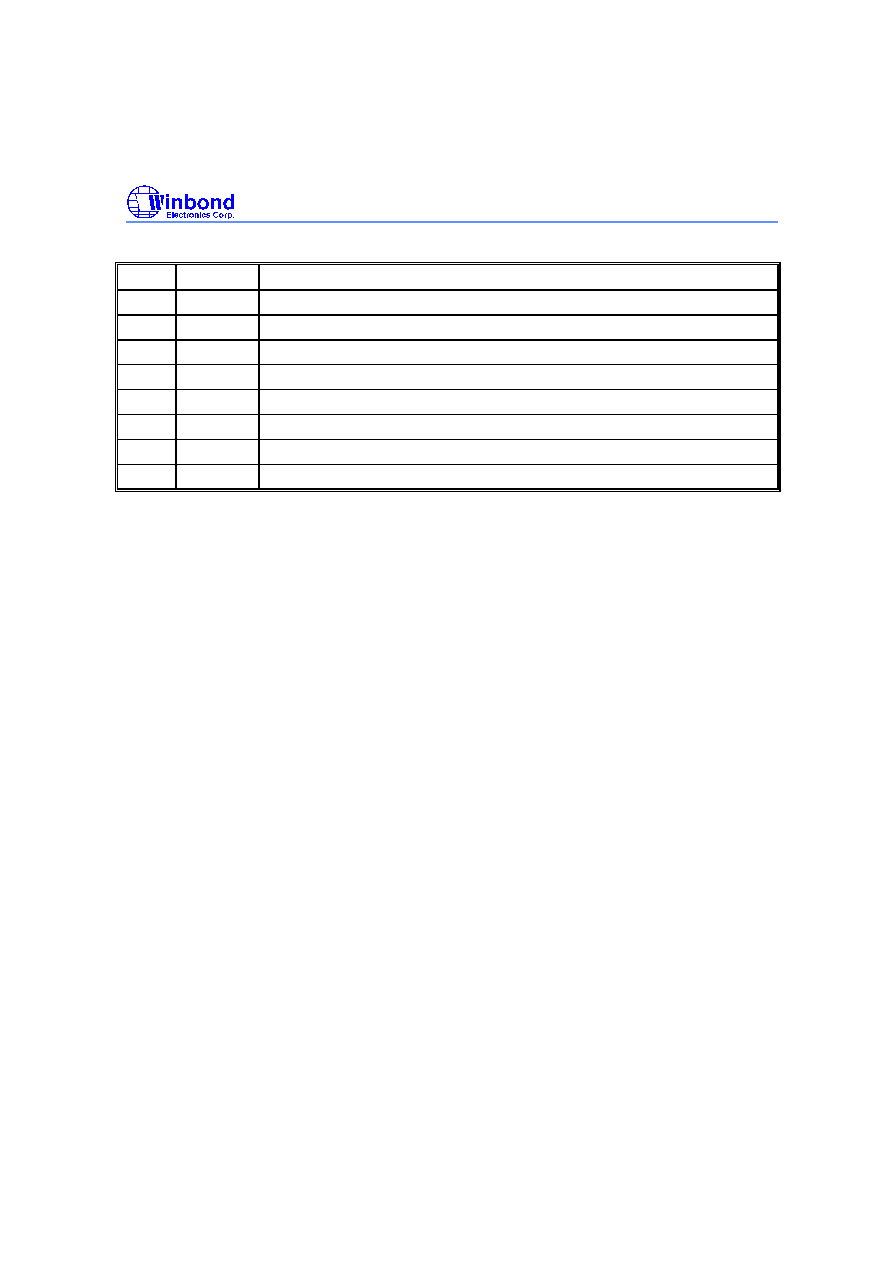

Port 4 (D8H)

BIT

NAME

FUNCTION

7

-

Reserve

6

-

Reserve

5

-

Reserve

4

-

Reserve

3

P43

Port 4 Data bit which outputs to pin P4.3.

2

P42

Port 4 Data bit. which outputs to pin P4.2.

1

P41

Port 4 Data bit. which outputs to pin P4.1.

0

P40

Port 4 Data bit which outputs to pin P4.0.

In-System Programming (ISP) Mode

The W78E516B equips one 64K byte of main MTP-ROM bank for application program (called

APROM) and one 4K byte of auxiliary MTP-ROM bank for loader program (called LDROM). In the

normal operation, the microcontroller executes the code in the APROM. If the content of APROM

needs to be modified, the W78E516B allows user to activate the In-System Programming (ISP) mode

by setting the CHPCON register. The CHPCON is read-only by default, software must write two

specific values 87H, then 59H sequentially to the CHPENR register to enable the CHPCON

write attribute. Writing CHPENR register with the values except 87H and 59H will close

CHPCON register write attribute. The W78E516B achieves all in-system programming operations

including enter/exit ISP Mode, program, erase, read ... etc, during device in the idle mode. Setting the

bit CHPCON.0 the device will enter in-system programming mode after a wake-up from idle mode.

Because device needs proper time to complete the ISP operations before awaken from idle mode,

software may use timer interrupt to control the duration for device wake-up from idle mode. To

perform ISP operation for revising contents of APROM, software located at APROM setting the

CHPCON register then enter idle mode, after awaken from idle mode the device executes the

corresponding interrupt service routine in LDROM. Because the device will clear the program counter

while switching from APROM to LDROM, the first execution of RETI instruction in interrupt service

routine will jump to 00H at LDROM area. The device offers a software reset for switching back to

APROM while the content of APROM has been updated completely. Setting CHPCON register bit 0,

1 and 7 to logic-1 will result a software reset to reset the CPU. The software reset serves as a

external reset. This in-system programming feature makes the job easy and efficient in which the

application needs to update firmware frequently. In some applications, the in-system programming

feature make it possible to easily update the system firmware without opening the chassis.

SFRAH, SFRAL:

The objective address of on-chip MTP-ROM in the in-system programming mode.

SFRFAH contains the high-order byte of address, SFRFAL contains the low-order

byte of address.

SFRFD:

The programming data for on-chip MTP-ROM in programming mode.

SFRCN:

The control byte of on-chip MTP-ROM programming mode.

W78E516B

- 8 -

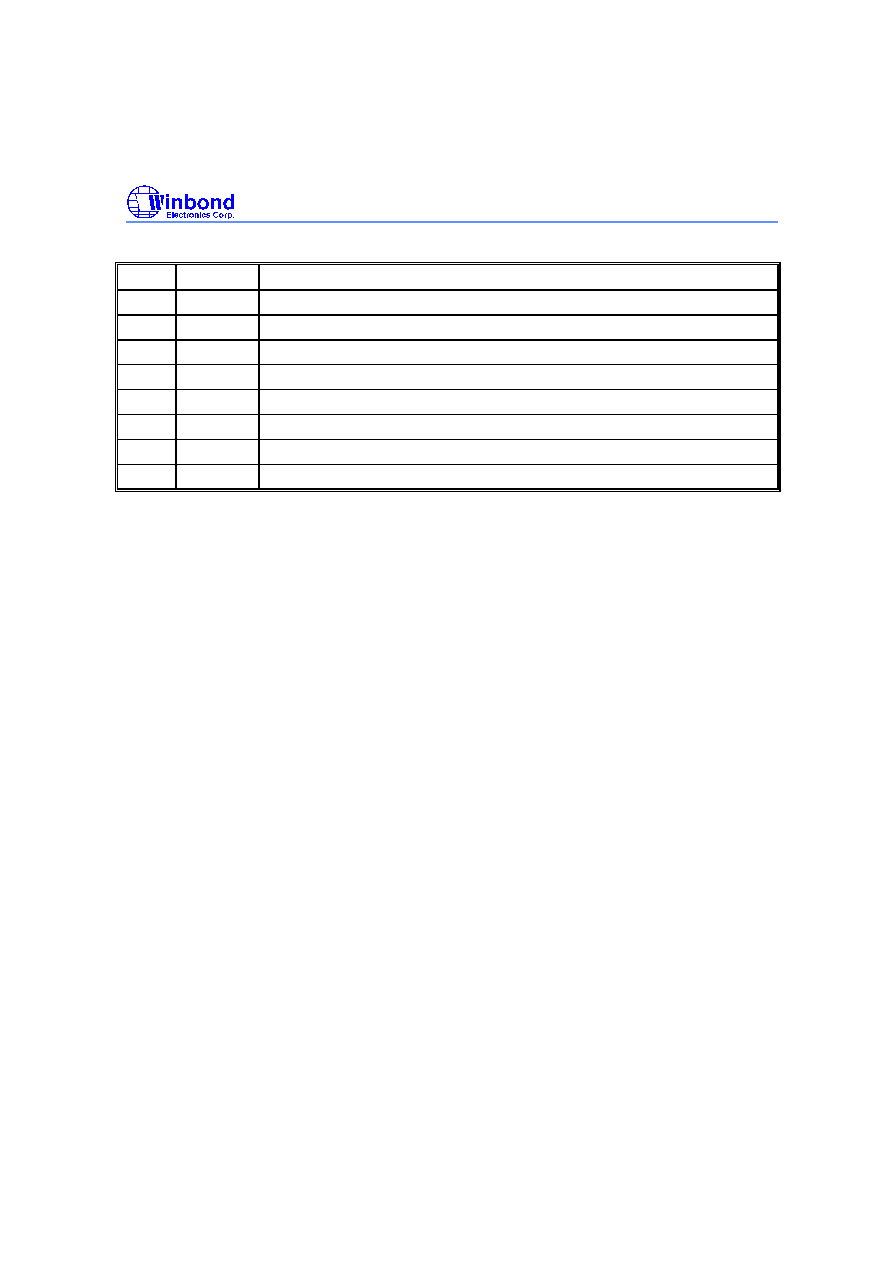

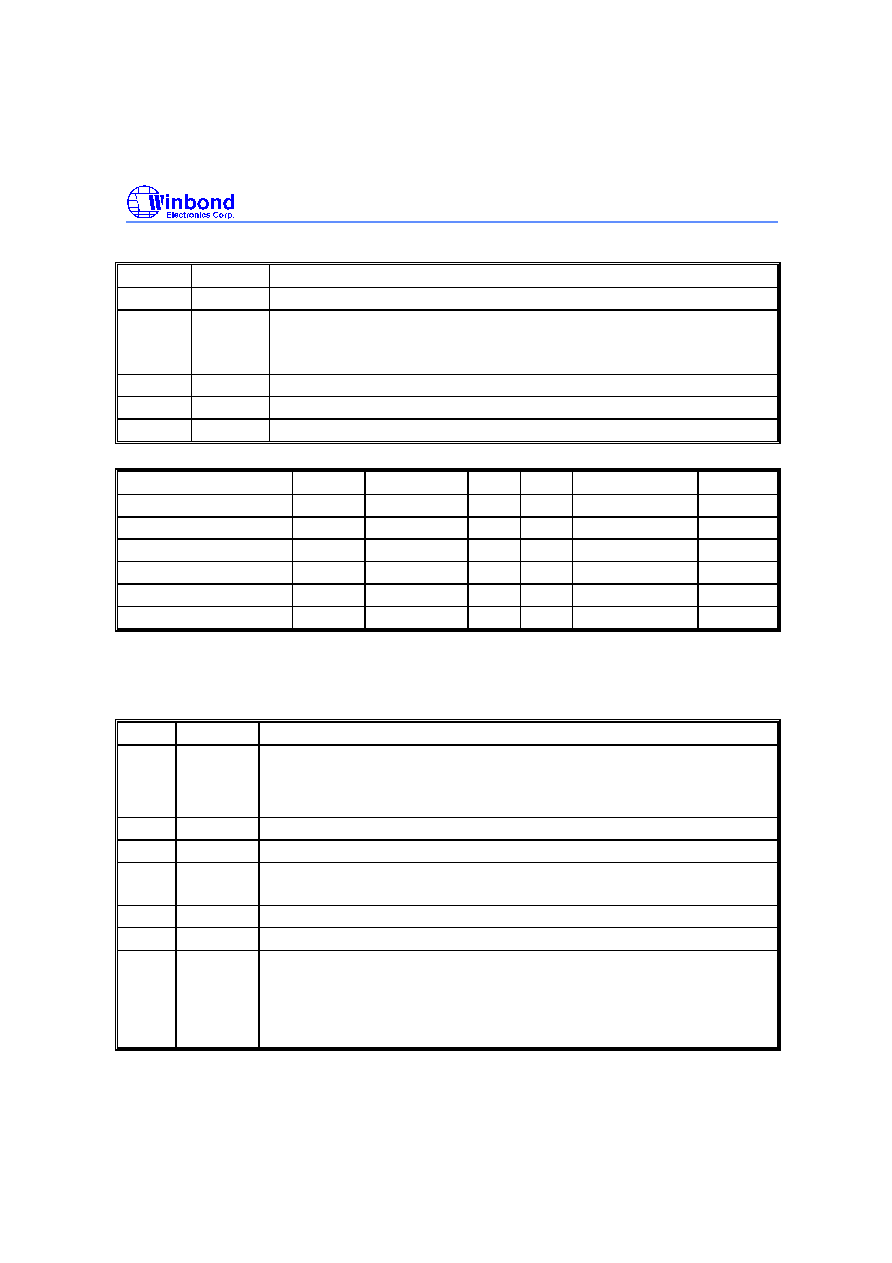

SFRCN (C7)

BIT

NAME

FUNCTION

7

-

Reserve.

6

WFWIN On-chip MTP-ROM bank select for in-system programming.

= 0: 64K bytes MTP-ROM bank is selected as destination for re-programming.

= 1: 4K bytes MTP-ROM bank is selected as destination for re-programming.

5

OEN

MTP-ROM output enable.

4

CEN

MTP-ROM chip enable.

3, 2, 1, 0 CTRL[3:0] The flash control signals

MODE

WFWIN CTRL<3:0> OEN CEN SFRAH, SFRAL SFRFD

Erase 64KB APROM

0

0010

1

0

X

X

Program 64KB APROM

0

0001

1

0

Address in

Data in

Read 64KB APROM

0

0000

0

0

Address in

Data out

Erase 4KB LDROM

1

0010

1

0

X

X

Program 4KB LDROM

1

0001

1

0

Address in

Data in

Read 4KB LDROM

1

0000

0

0

Address in

Data out

In-System Programming Control Register (CHPCON)

CHPCON (BFH)

BIT

NAME

FUNCTION

7

SWRESET

(F04KMODE)

When this bit is set to 1, and both FBOOTSL and FPROGEN are set to 1. It

will enforce microcontroller reset to initial condition just like power on reset.

This action will re-boot the microcontroller and start to normal operation. To

read this bit in logic-1 can determine that the F04KBOOT mode is running.

6

-

Reserve.

5

-

Reserve.

4

ENAUXRAM

1: Enable on-chip AUX-RAM.

0: Disable the on-chip AUX-RAM

3

0

Must set to 0.

2

0

Must set to 0.

1

FBOOTSL The Program Location Select.

0: The Loader Program locates at the 64 KB APROM. 4KB LDROM is

destination for re-programming.

1: The Loader Program locates at the 4 KB memory bank. 64KB APROM is

destination for re-programming.

W78E516B

Publication Release Date: February 2000

- 9 - Revision A3

CHPCON (BFH), continued

BIT

NAME

FUNCTION

0

FPROGEN MTP-ROM Programming Enable.

= 1: enable. The microcontroller enter the in-system programming mode after

entering the idle mode and wake-up from interrupt. During in-system

programming mode, the operation of erase, program and read are

achieve when device enters idle mode.

= 0: disable. The on-chip flash memory is read-only. In-system

programmability is disabled.

F04KBOOT Mode (Boot From LDROM)

By default, the W78E516B boots from APROM program after a power on reset. On some occasions,

user can force the W78E516B to boot from the LDROM program via following settings

.

The possible

situation that you need to enter F04KBOOT mode when the APROM program can not run properly

and device can not jump back to LDROM to execute in-system programming function. Then you can

use this F04KBOOT mode to force the W78E516B jumps to LDROM and executes in-system

programming procedure. When you design your system, you may reserve the pins P2.6, P2.7 to

switches or jumpers. For example in a CD-ROM system, you can connect the P2.6 and P2.7 to PLAY

and EJECT buttons on the panel. When the APROM program fails to execute the normal application

program. User can press both two buttons at the same time and then turn on the power of the

personal computer to force the W78E516B to enter the F04KBOOT mode. After power on of personal

computer, you can release both buttons and finish the in-system programming procedure to update

the APROM code.

In application system design, user must take care of the P2, P3, ALE, EA and

PSEN pin value at reset to prevent from accidentally activating the programming mode or

F04KBOOT mode.

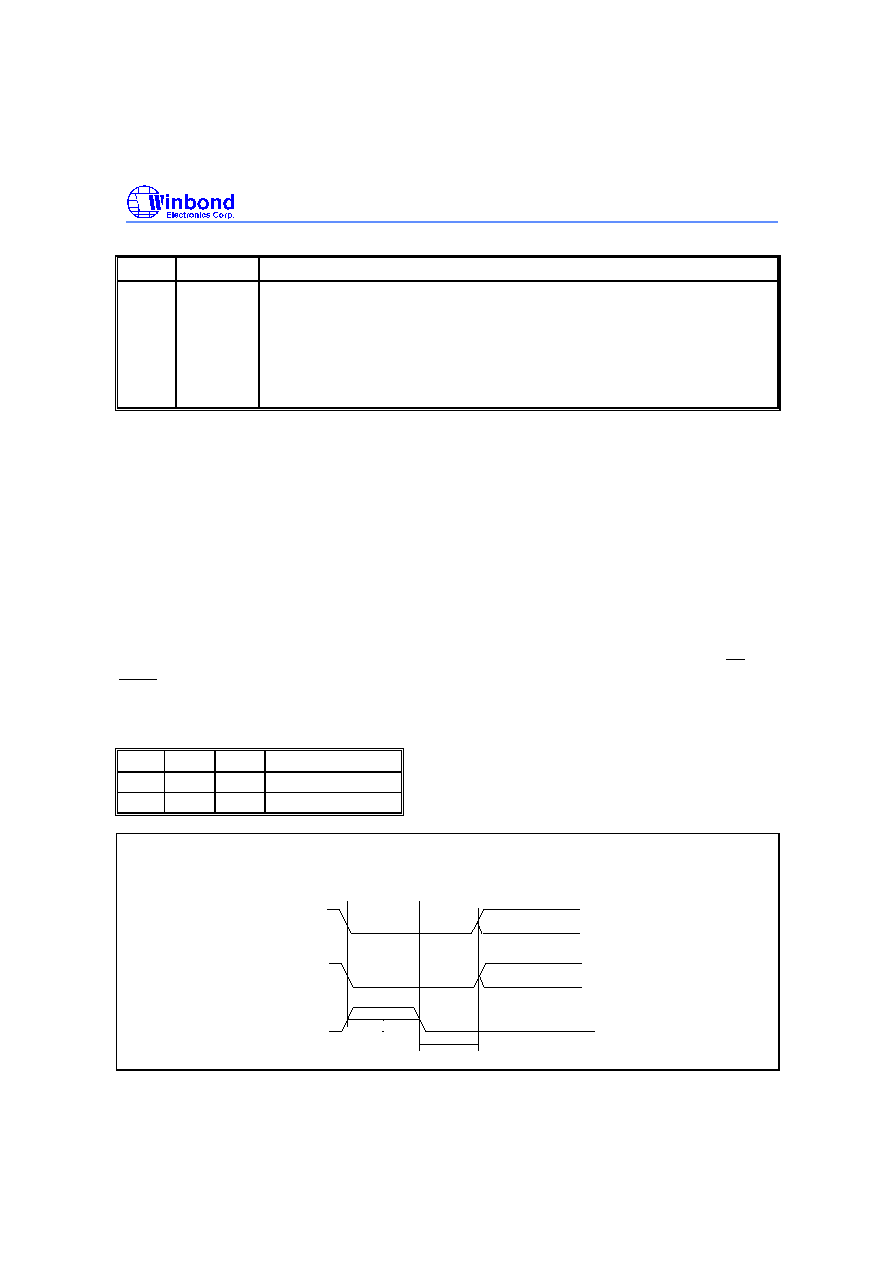

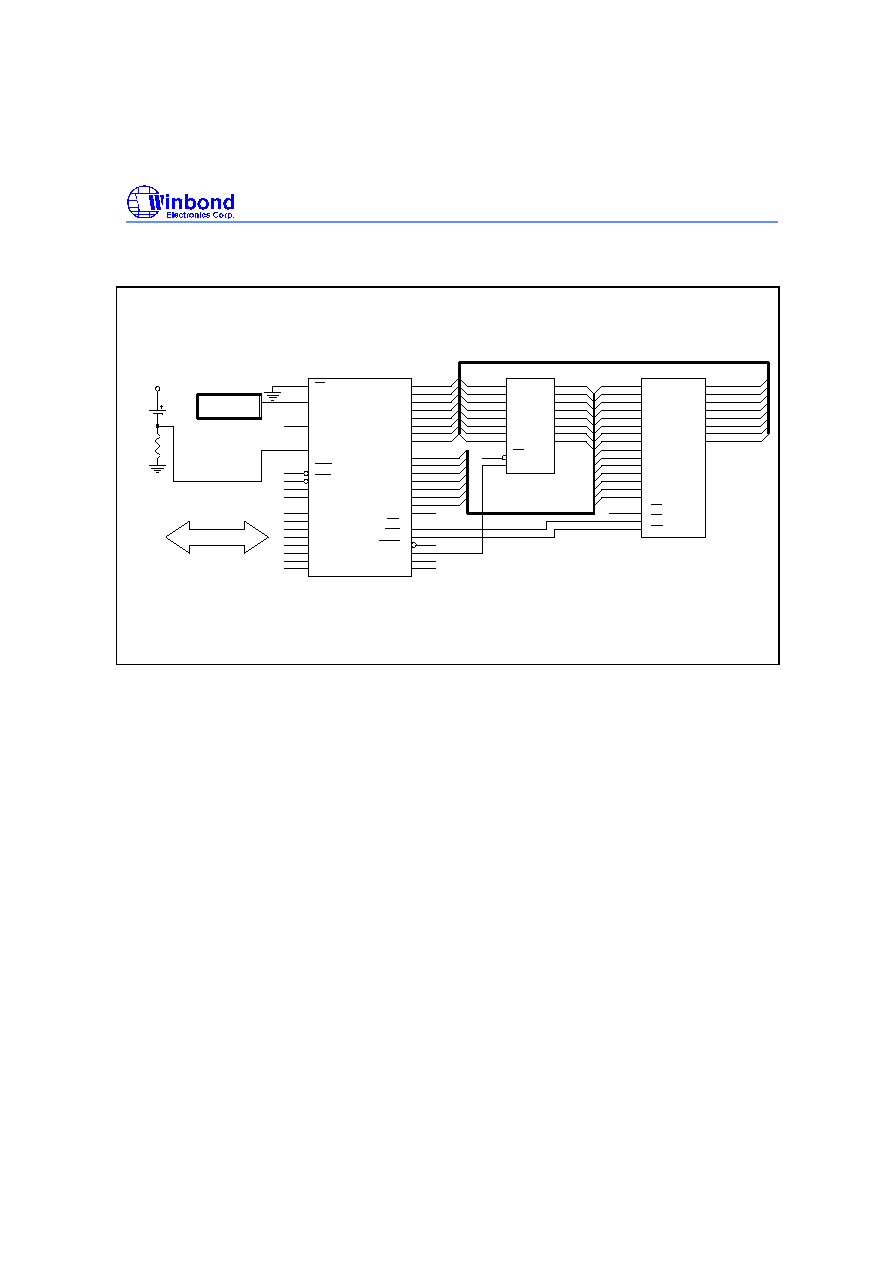

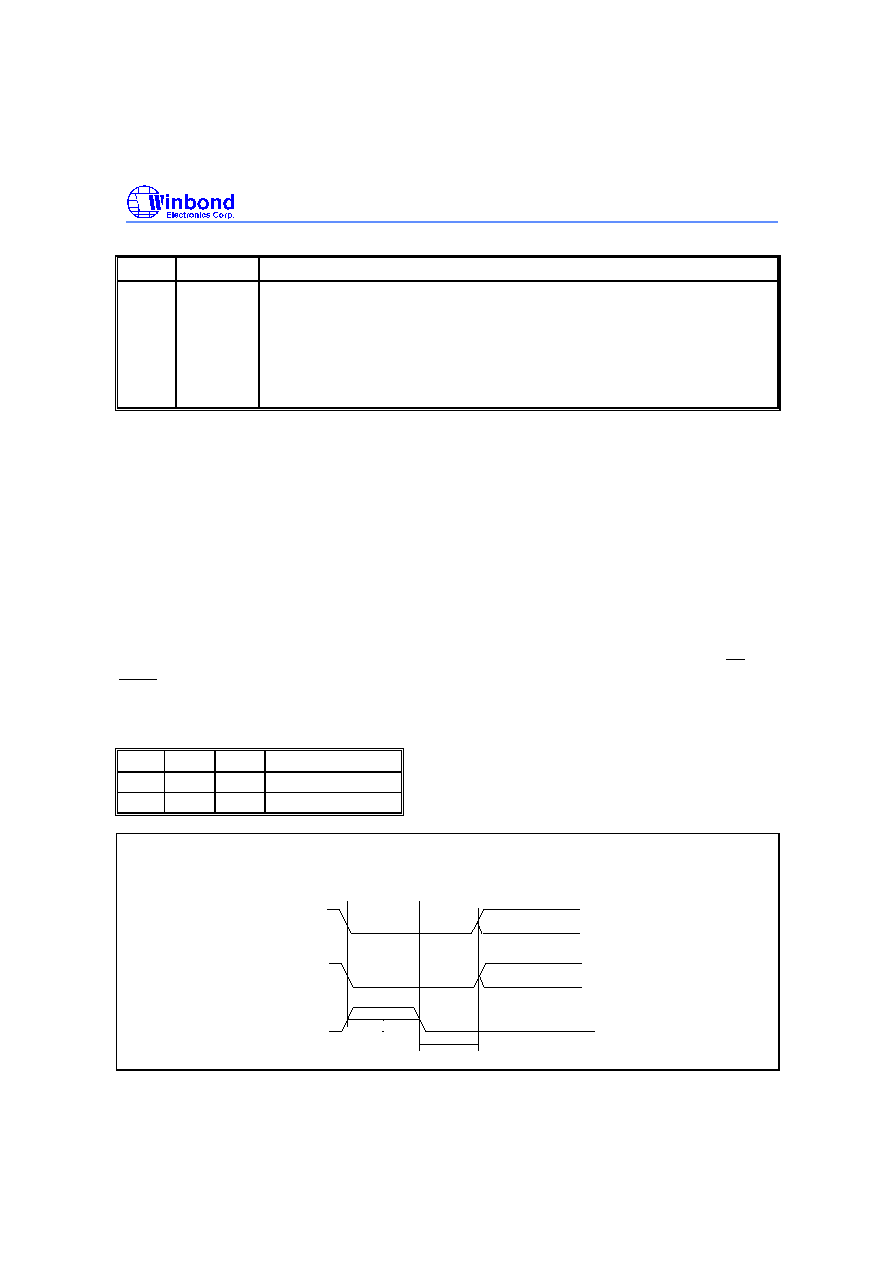

F04KBOOT MODE

P4.3 P2.7 P2.6

MODE

X

L

L

FO4KBOOT

L

X

X

FO4KBOOT

P2.7

P2.6

RST

30 mS

Hi-Z

The Reset Timing For Entering

F04KBOOT Mode

10 mS

Hi-Z

W78E516B

- 10 -

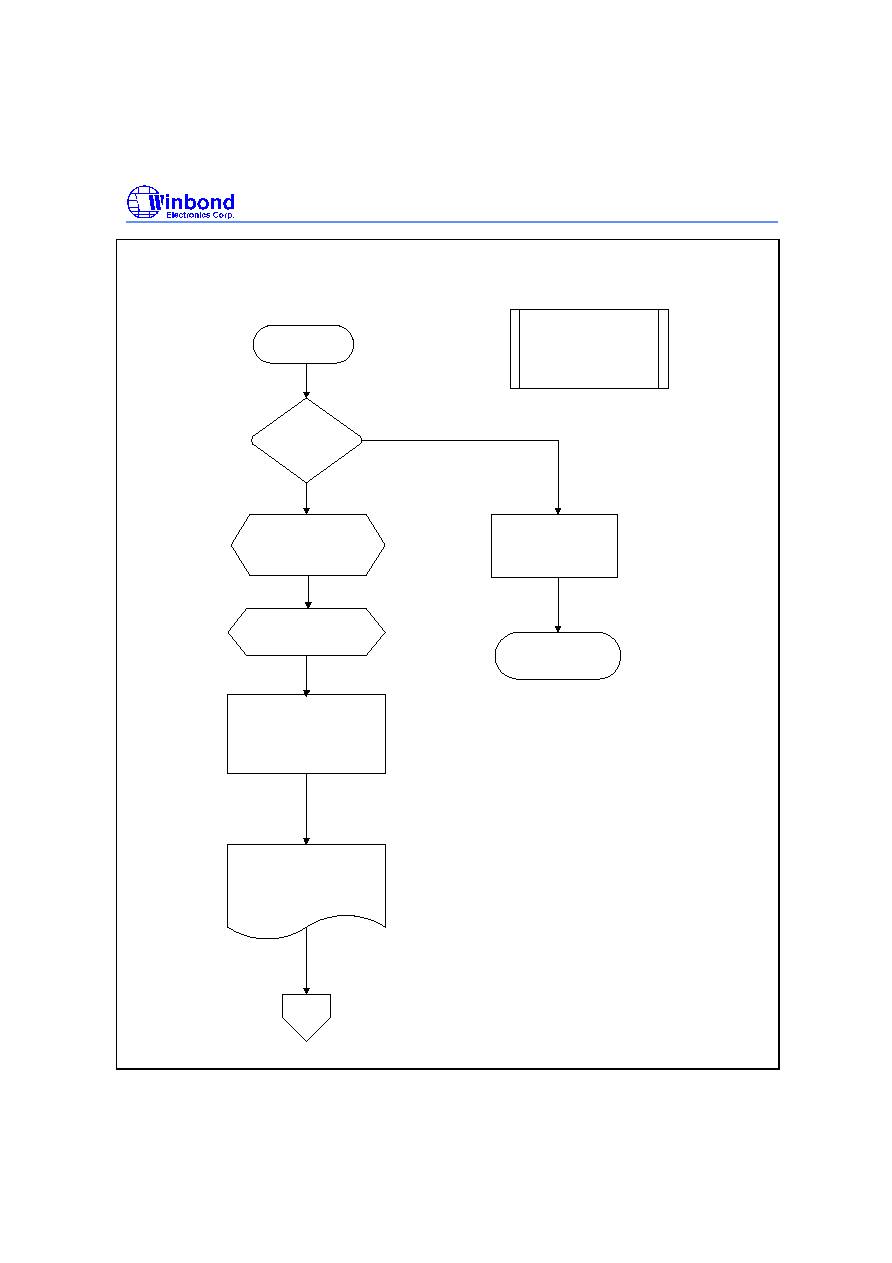

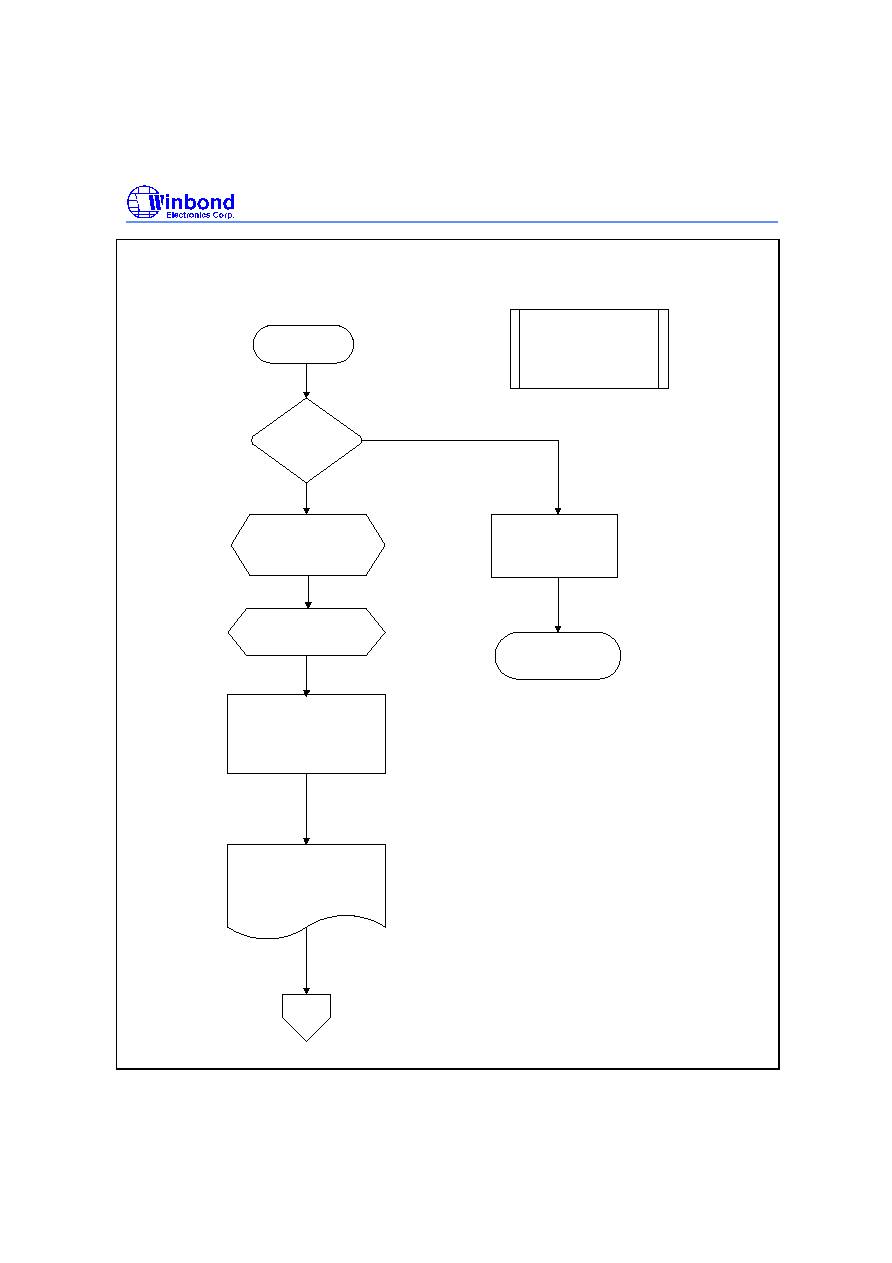

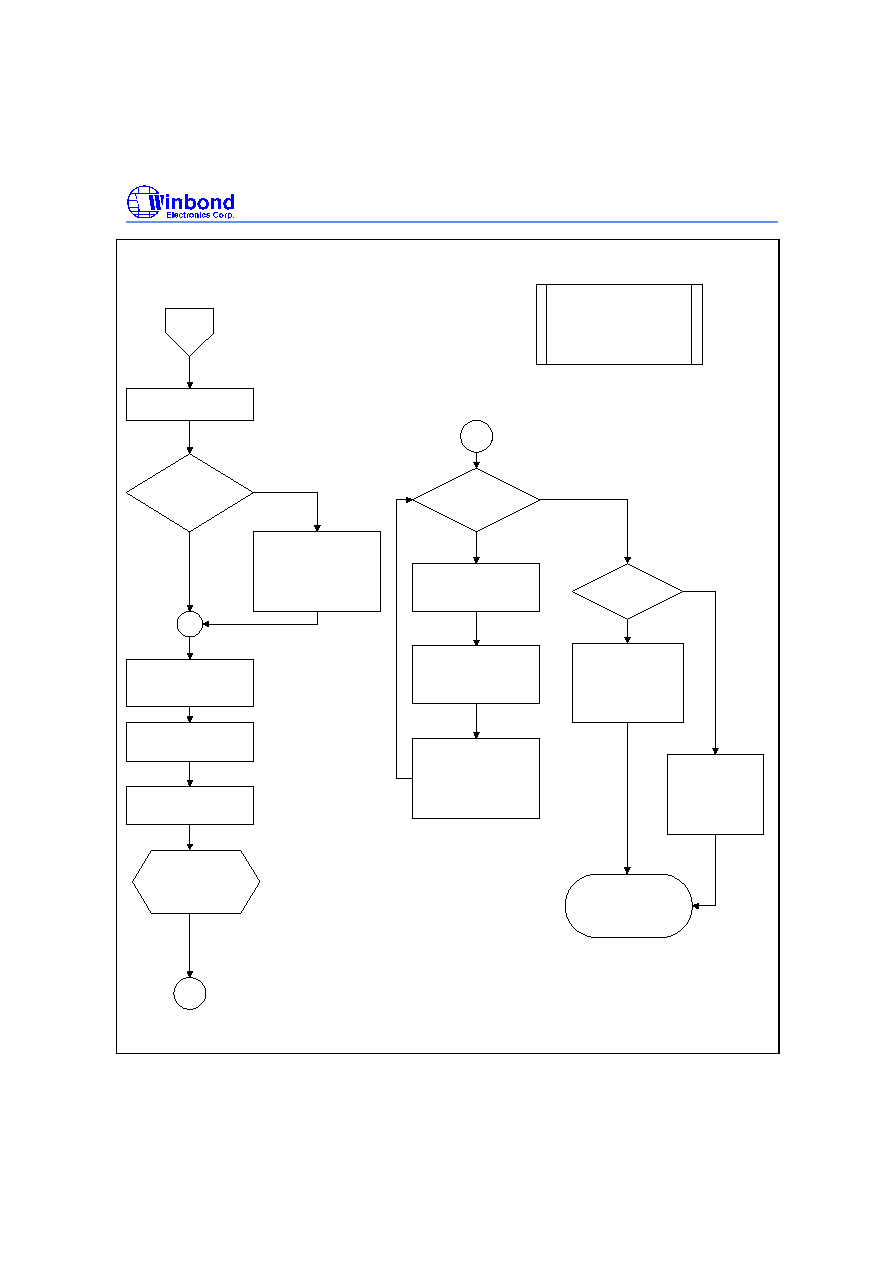

START

The Algorithm of In-System Programming

Enter In-System

Programming Mode ?

(conditions depend on

user's application)

Setting control registers

MOV CHPENR,#87H

MOV CHPENR,#59H

MOV CHPCON,#03H

Setting Timer (about 1.5 us)

and enable timer interrupt

Start Timer and enter idle Mode.

(CPU will be wakened from idle mode

by timer interrupt, then enter In-System

Programming mode)

Execute the normal application

program

No

Yes

END

CPU will be wakened by interrupt and

re-boot from 4KB LDROM to execute

the loader program.

Go

Part 1:64KB APROM

procedure of entering

In-System Programming Mode

W78E516B

Publication Release Date: February 2000

- 11 - Revision A3

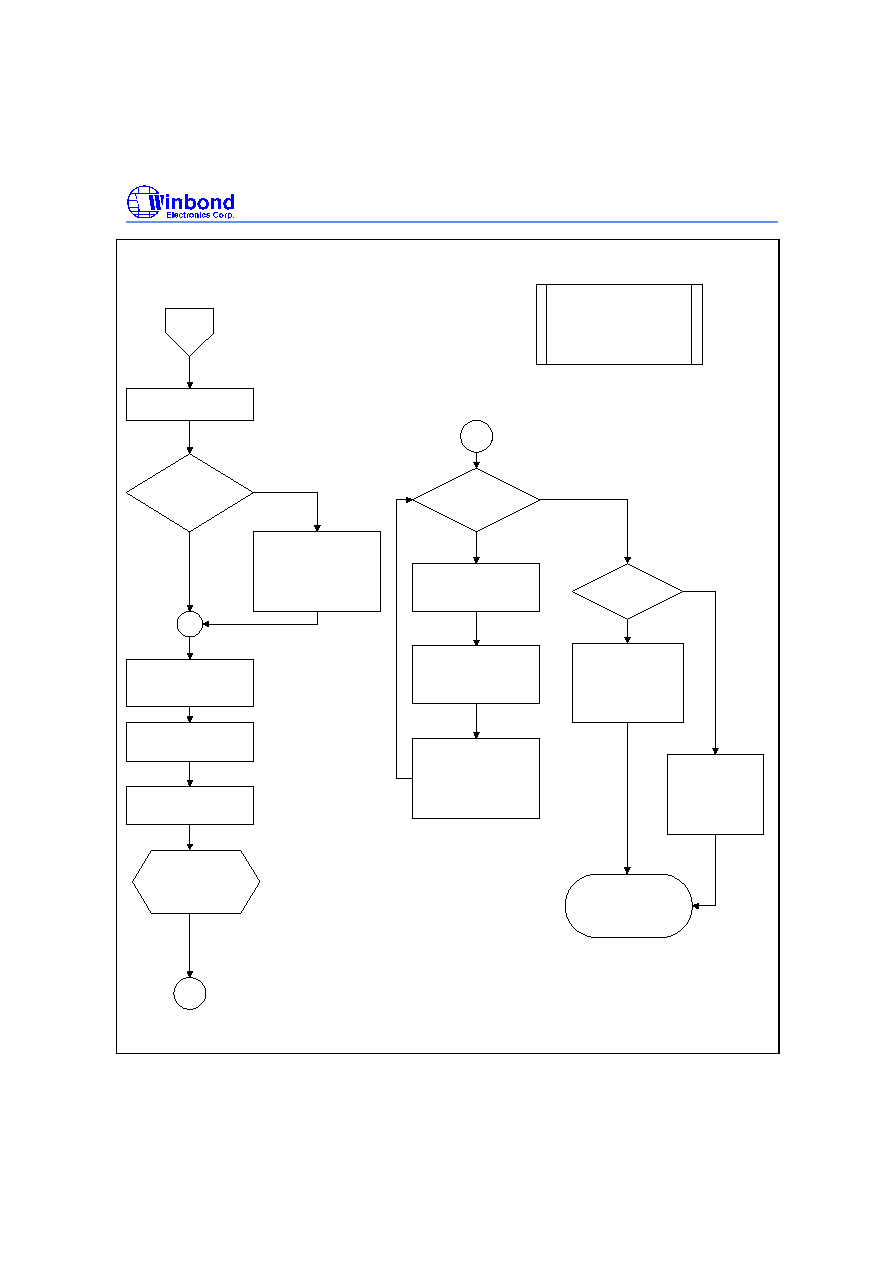

Part 2: 4KB LDROM

Procedure of Updating

the 64KB APROM

Go

Timer Interrupt Service Routine:

Stop Timer & disable interrupt

Is F04KBOOT Mode?

(CHPCON.7=1)

Reset the CHPCON Register:

MOV CHPENR,#87H

MOV CHPENR,#59H

MOV CHPCON,#03H

No

Yes

Setting Timer and enable Timer

interrupt for wake-up .

(15 ms for erasing operation)

Setting erase operation mode:

MOV SFRCN,#22H

(Erase 64KB APROM)

Start Timer and enter IDLE

Mode.

(Erasing...)

End of erase

operation. CPU will

be wakened by Timer

interrupt.

PGM

PGM

Setting Timer and enable Timer

interrupt for wake-up .

(50us for program operation)

End of Programming ?

Get the parameters of new code

(Address and data bytes)

through I/O ports, UART or

other interfaces.

Is currently in the

F04KBOOT Mode ?

Setting control registers for

programming:

MOV SFRAH,#ADDRESS_H

MOV SFRAL,#ADDRESS_L

MOV SFRFD,#DATA

MOV SFRCN,#21H

Software reset CPU and

re-boot from the 64KB

APROM.

MOV CHPENR,#87H

MOV CHPENR,#59H

MOV CHPCON,#83H

END

Executing new code

from address

00H in the 64KB APROM.

Hardware Reset

to re-boot from

new 64 KB APROM.

(S/W reset is

invalid in F04KBOOT

Mode)

Yes

No

Yes

No

W78E516B

- 12 -

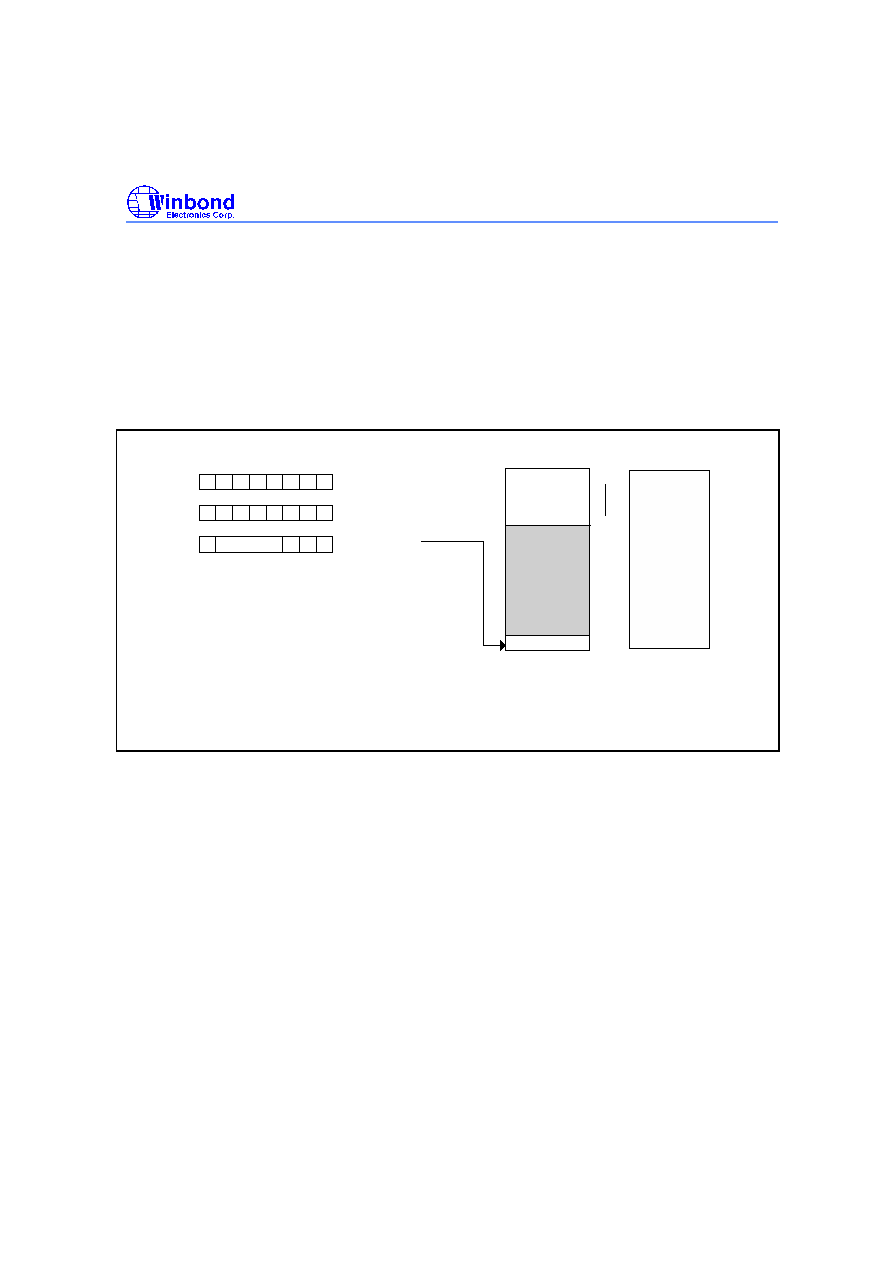

SECURITY

During the on-chip MTP-ROM programming mode, the MTP-ROM can be programmed and verified

repeatedly. Until the code inside the MTP-ROM is confirmed OK, the code can be protected. The

protection of MTP-ROM and those operations on it are described below.

The W78E516B has several Special Setting Registers, including the Security Register and

Company/Device ID Registers, which can not be accessed in programming mode. Those bits of the

Security Registers can not be changed once they have been programmed from high to low. They can

only be reset through erase-all operation. The contents of the Company ID and Device ID registers

have been set in factory. The Security Register is located at the 0FFFFH of the LDROM space.

B0

B1

B0: Lock bit, logic 0: active

B1: MOVC inhibit,

logic 0: the MOVC instruction in external memory

cannot access the code in internal memory.

logic 1: no restriction.

Default 1 for all security bits.

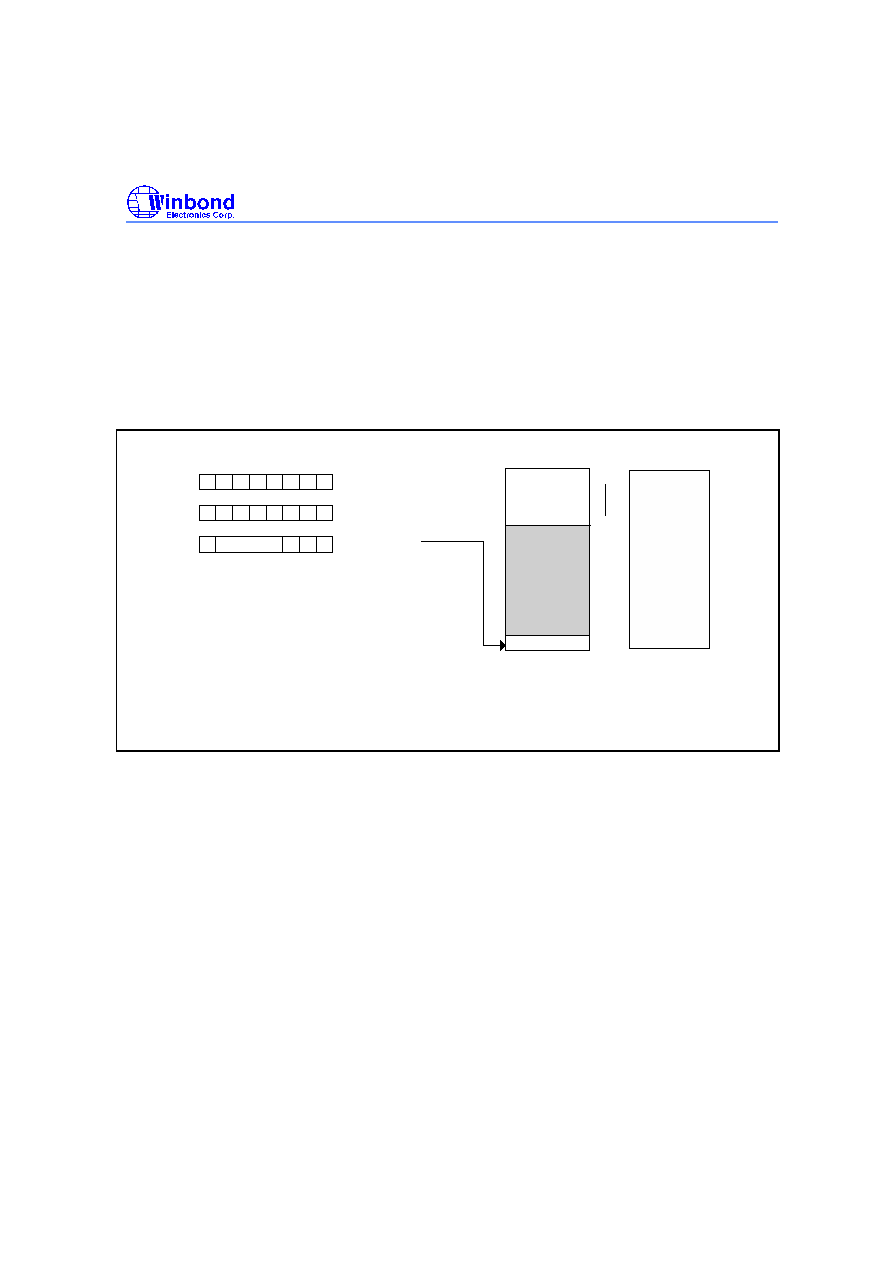

Special Setting Registers

Company ID (#DAH)

D7 D6 D5 D4 D3 D2 D1 D0

1

1

0

1

1

0

1

0

Device ID (#62H)

0

1

1

1

0

0

0

Security Bits

0

4KB MTP ROM

Program Memory

Reserved

Security Register

FFFFh

0000h

0FFFh

Reserved

B2

B2: Encryption

logic 0: the encryption logic enable

logic 1: the encryption logic disable

Reserved bits must be kept in logic 1.

B7

B07: Osillator Control

logic 0: 1/2 gain

logic 1: Full gain

LDROM

Reserved

64KB MTP ROM

Program Memory

APROM

Lock bit

This bit is used to protect the customer's program code in the W78E516B. It may be set after the

programmer finishes the programming and verifies sequence. Once this bit is set to logic 0, both the

MTP ROM data and Special Setting Registers can not be accessed again.

MOVC Inhibit

This bit is used to restrict the accessible region of the MOVC instruction. It can prevent the MOVC

instruction in external program memory from reading the internal program code. When this bit is set

to logic 0, a MOVC instruction in external program memory space will be able to access code only in

the external memory, not in the internal memory. A MOVC instruction in internal program memory

space will always be able to access the ROM data in both internal and external memory. If this bit is

logic 1, there are no restrictions on the MOVC instruction.

Encryption

This bit is used to enable/disable the encryption logic for code protection. Once encryption feature is

enabled, the data presented on port 0 will be encoded via encryption logic. Only whole chip erase will

reset this bit.

W78E516B

Publication Release Date: February 2000

- 13 - Revision A3

Oscillator Control

W78E516B/E516 allow user to diminish the gain of on-chip oscillator amplifier by using programmer

to set the bit B7 of security register. Once B7 is set to 0, a half of gain will be decreased. Care must

be taken if user attempts to diminish the gain of oscillator amplifier, reducing a half of gain may

improperly affect the external crystal operation at high frequency above 24 MHz. The value of R and

C1, C2 may need some adjustment while running at lower gain.

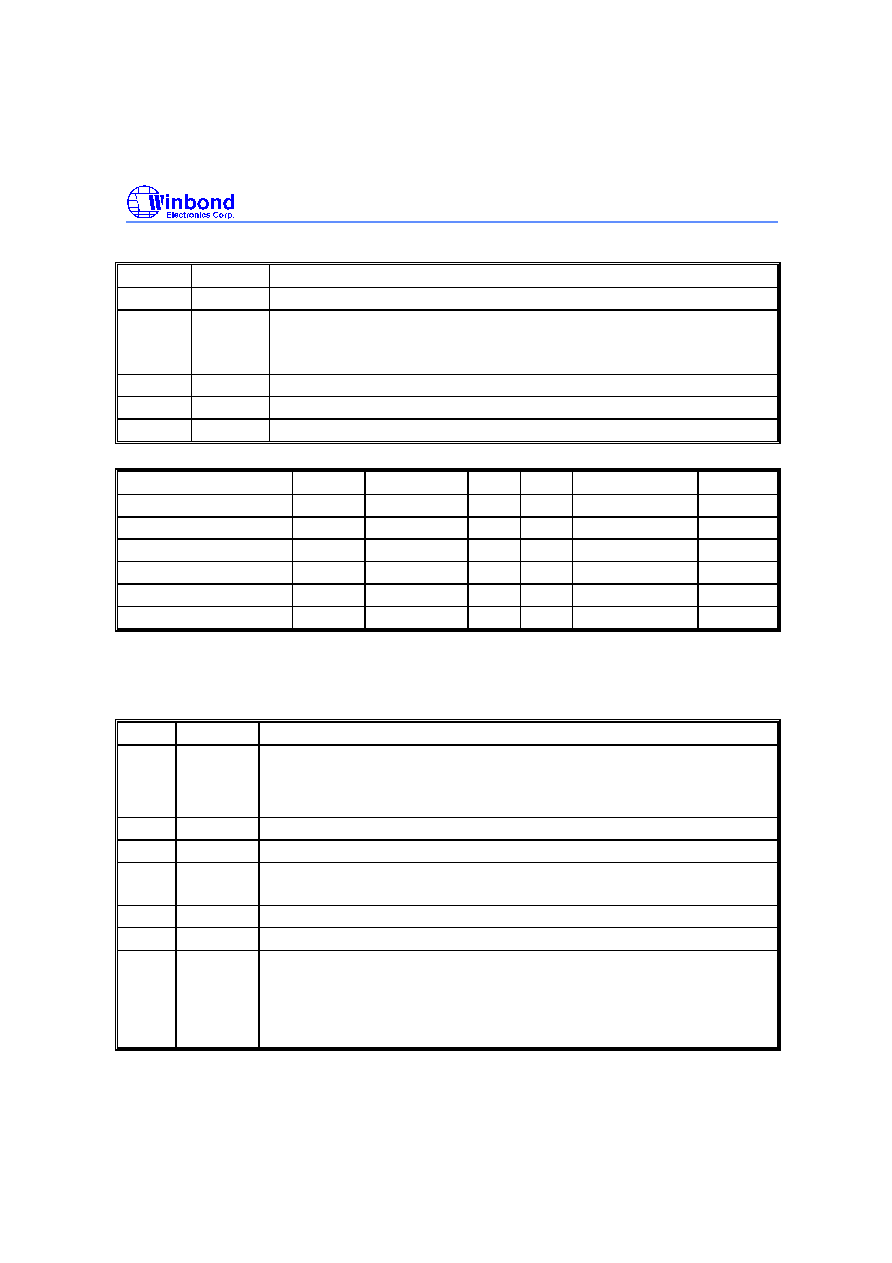

ABSOLUTE MAXIMUM RATINGS

PARAMETER

SYMBOL

MIN.

MAX.

UNIT

DC Power Supply

V

DD

-

V

SS

-0.3

+6.0

V

Input Voltage

V

IN

V

SS

-0.3

V

DD

+0.3

V

Operating Temperature

T

A

0

70

∞

C

Storage Temperature

T

ST

-55

+150

∞

C

Note: Exposure to conditions beyond those listed under Absolute Maximum Ratings may adversely affect the life and reliability of the

device.

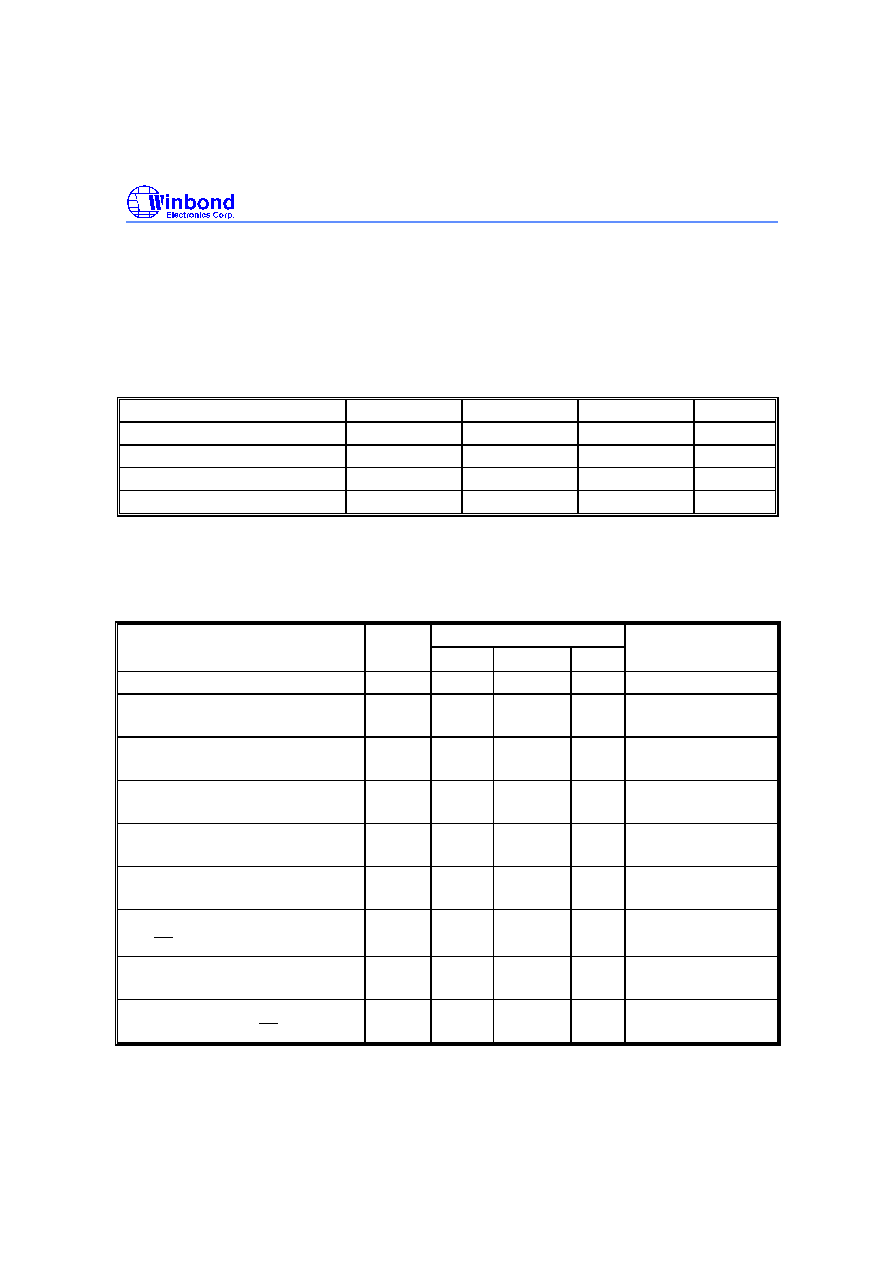

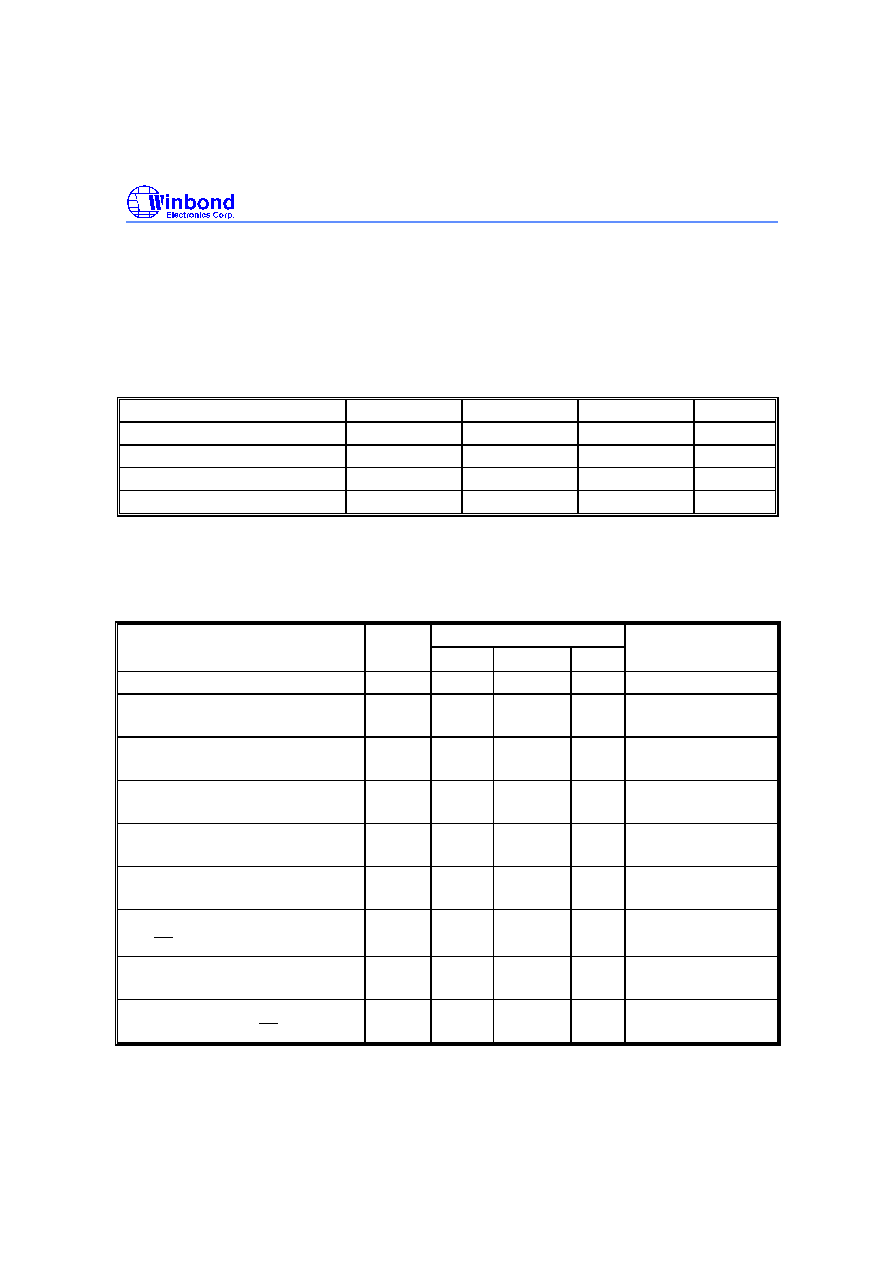

D.C. ELECTRICAL CHARACTERISTICS

(V

DD

-V

SS

= 5V

±

10%, T

A

= 25

∞

C, Fosc = 20 MHz, unless otherwise specified.)

PARAMETER

SYM.

SPECIFICATION

TEST CONDITIONS

MIN.

MAX.

UNIT

Operating Voltage

V

DD

4.5

5.5

V

RST = 1, P0 = V

DD

Operating Current

I

DD

-

20

mA

No load

V

DD

= 5.5V

Idle Current

I

IDLE

-

6

mA

Idle mode

V

DD

= 5.5V

Power Down Current

I

PWDN

-

50

µ

A

Power-down mode

V

DD

= 5.5V

Input Current

P1, P2, P3, P4

I

IN1

-50

+10

µ

A

V

DD

= 5.5V

V

IN

= 0V or V

DD

Input Current

RST

I

IN2

-10

+300

µ

A

V

DD

= 5.5V

0< V

IN

<V

DD

Input Leakage Current

P0, EA

I

LK

-10

+10

µ

A

V

DD

= 5.5V

0V< V

IN

< V

DD

Logic 1 to 0 Transition Current

P1, P2, P3, P4

I

TL

[*4]

-500

-

µ

A

V

DD

= 5.5V

V

IN

= 2.0V

Input Low Voltage

P0, P1, P2, P3, P4, EA

V

IL1

0

0.8

V

V

DD

= 4.5V

W78E516B

- 14 -

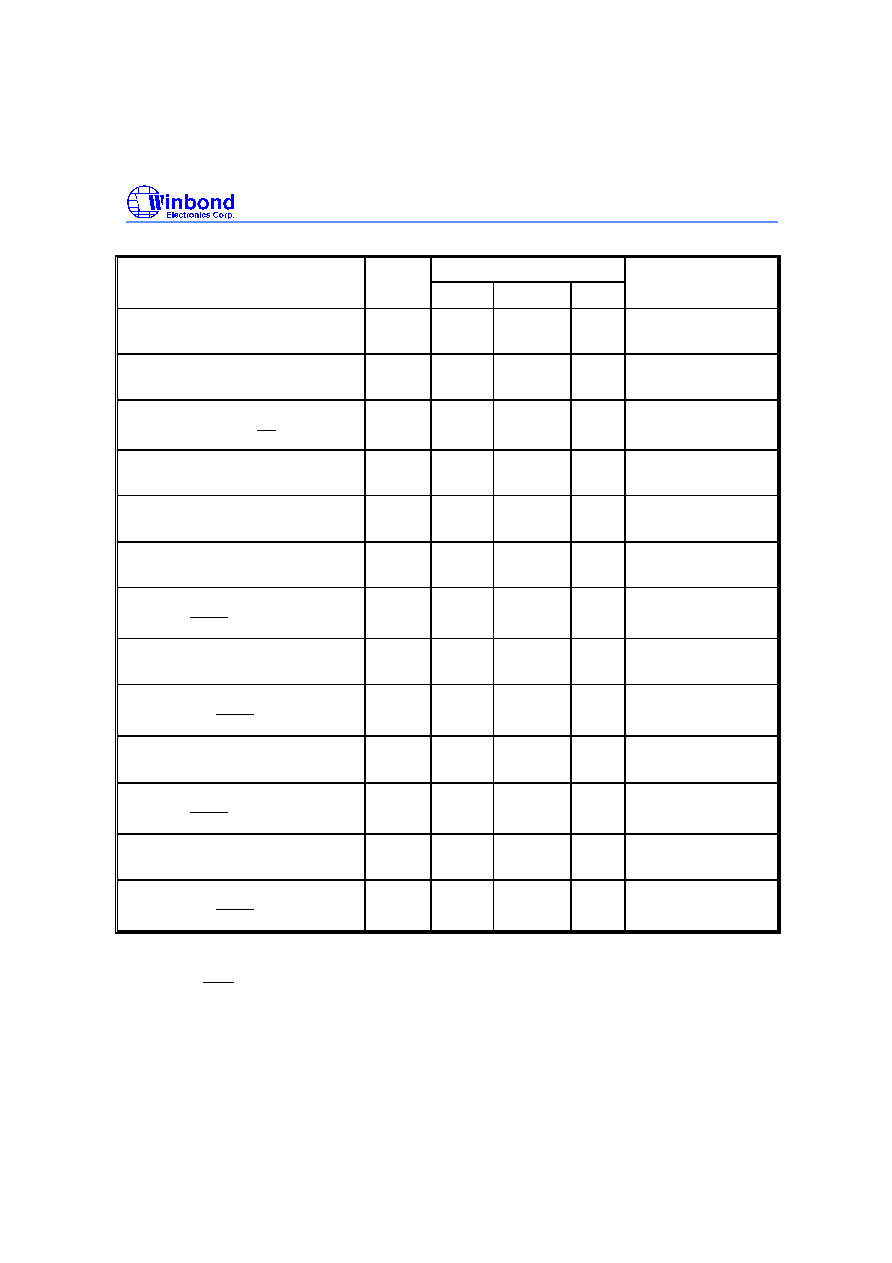

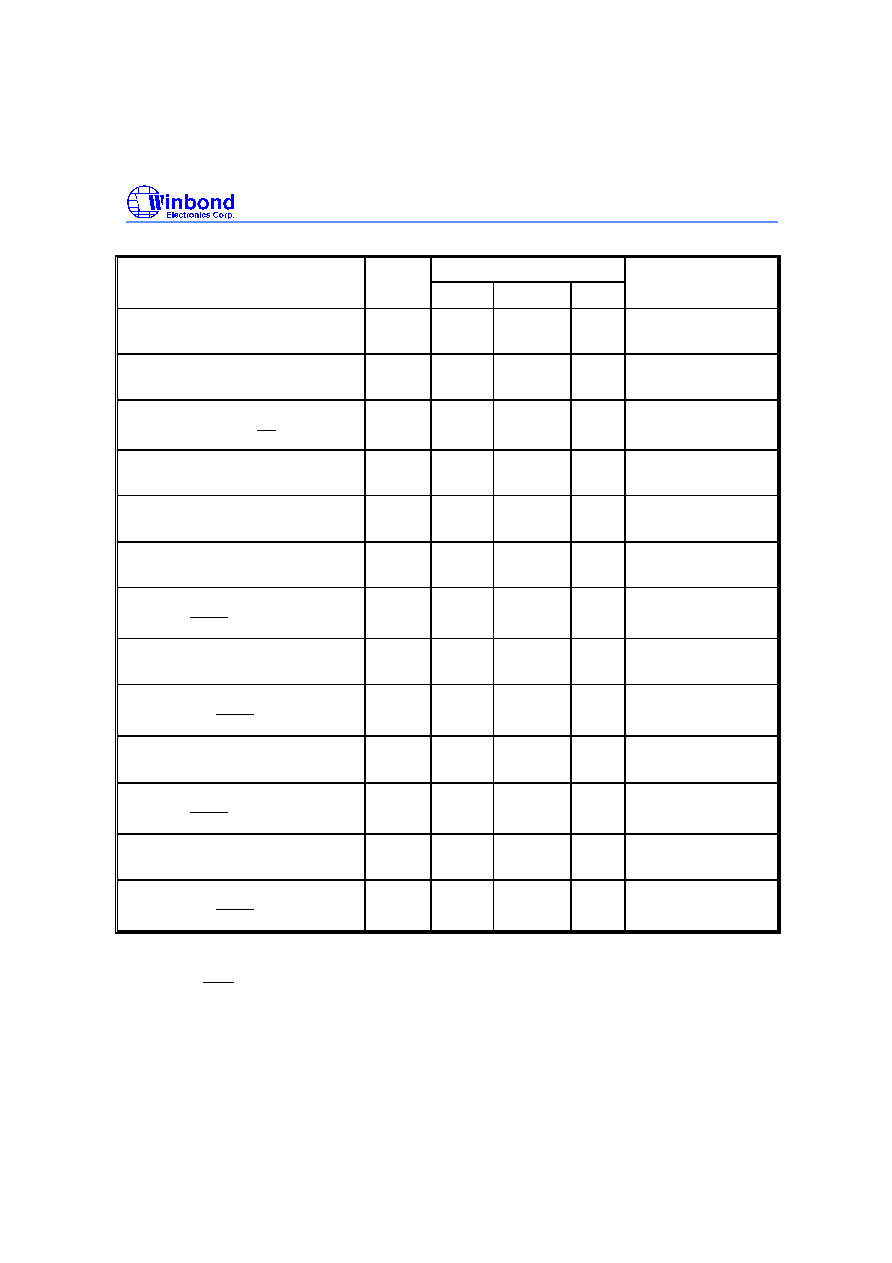

D.C. Electrical Characteristics, continued

PARAMETER

SYM.

SPECIFICATION

TEST CONDITIONS

MIN.

MAX.

UNIT

Input Low Voltage

RST

V

IL2

0

0.8

V

V

DD

= 4.5V

Input Low Voltage

XTAL1

[*4]

V

IL3

0

0.8

V

V

DD

= 4.5V

Input High Voltage

P0, P1, P2,

P3, P4, EA

V

IH1

2.4

V

DD

+0.2

V

V

DD

= 5.5V

Input High Voltage

RST

V

IH2

3.5

V

DD

+0.2

V

V

DD

= 5.5V

Input High Voltage

XTAL1

[*4]

V

IH3

3.5

V

DD

+0.2

V

V

DD

= 5.5V

Output Low Voltage

P1, P2, P3, P4

V

OL1

-

0.45

V

V

DD

= 4.5V

I

OL

= +2 mA

Output Low Voltage

P0, ALE, PSEN

[*3]

V

OL2

-

0.45

V

V

DD

= 4.5V

I

OL

= +4 mA

Sink Current

P1, P3, P4

Isk1

4

12

mA

V

DD

= 4.5V

V

IN

= 0.45V

Sink Current

P0, P2, ALE, PSEN

Isk2

10

20

mA

V

DD

= 4.5V

V

IN

= 0.45V

Output High Voltage

P1, P2, P3, P4

V

OH1

2.4

-

V

V

DD

= 4.5V

I

OH

= -100

µ

A

Output High Voltage

P0, ALE, PSEN

[*3]

V

OH2

2.4

-

V

V

DD

= 4.5V

I

OH

= -400

µ

A

Source Current

P1, P2, P3, P4

Isr1

-120

-250

µ

A

V

DD

= 4.5V

V

IN

= 2.4V

Source Current

P0, P2, ALE, PSEN

Isr2

-8

-20

mA

V

DD

= 4.5V

V

IN

= 2.4V

Notes:

*1. RST pin is a Schmitt trigger input.

*3. P0, ALE and PSEN are tested in the external access mode.

*4. XTAL1 is a CMOS input.

*5. Pins of P1, P2, P3 , P4 can source a transition current when they are being externally driven from 1 to 0. The transition current

reaches its maximum value when V

IN

approximates to 2V.

W78E516B

Publication Release Date: February 2000

- 15 - Revision A3

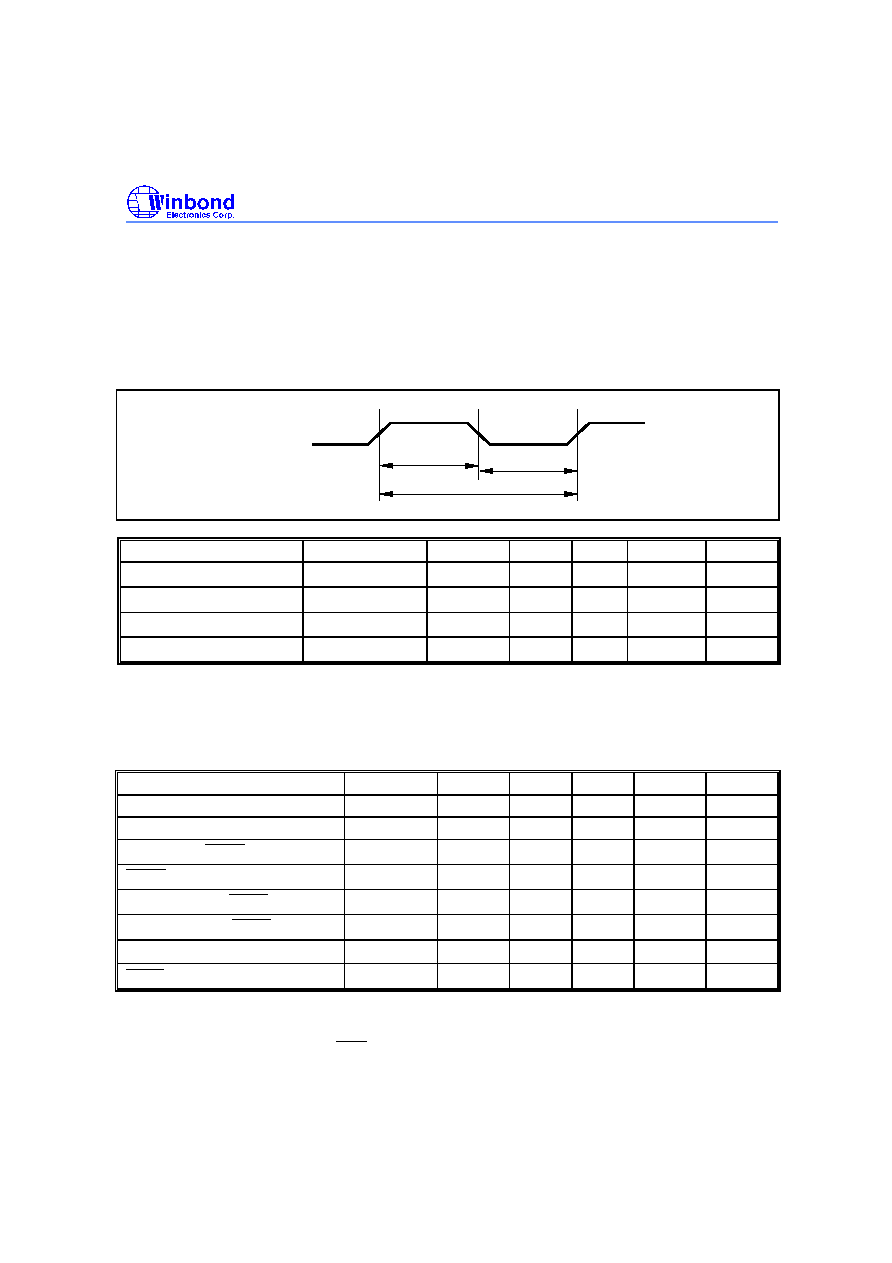

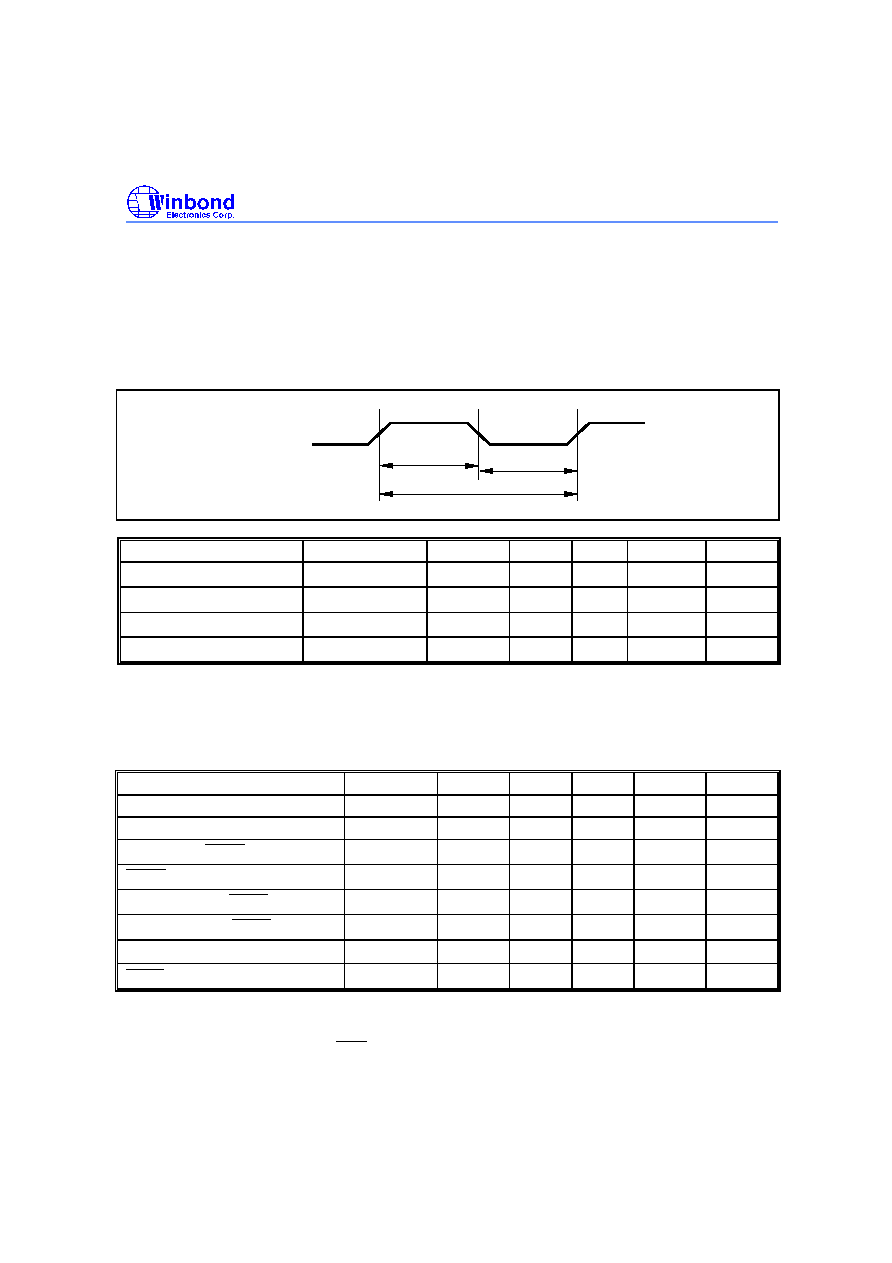

AC CHARACTERISTICS

The AC specifications are a function of the particular process used to manufacture the part, the

ratings of the I/O buffers, the capacitive load, and the internal routing capacitance. Most of the

specifications can be expressed in terms of multiple input clock periods (T

CP

), and actual parts will

usually experience less than a

±

20 nS variation. The numbers below represent the performance

expected from a 0.6 micron CMOS process when using 2 and 4 mA output buffers.

Clock Input Waveform

T

T

XTAL1

F

CH

CL

OP,

T

CP

PARAMETER

SYMBOL

MIN.

TYP. MAX.

UNIT

NOTES

Operating Speed

Fop

0

-

40

MHz

1

Clock Period

TCP

25

-

-

nS

2

Clock High

Tch

10

-

-

nS

3

Clock Low

Tcl

10

-

-

nS

3

Notes:

1. The clock may be stopped indefinitely in either state.

2. The T

CP

specification is used as a reference in other specifications.

3. There are no duty cycle requirements on the XTAL1 input.

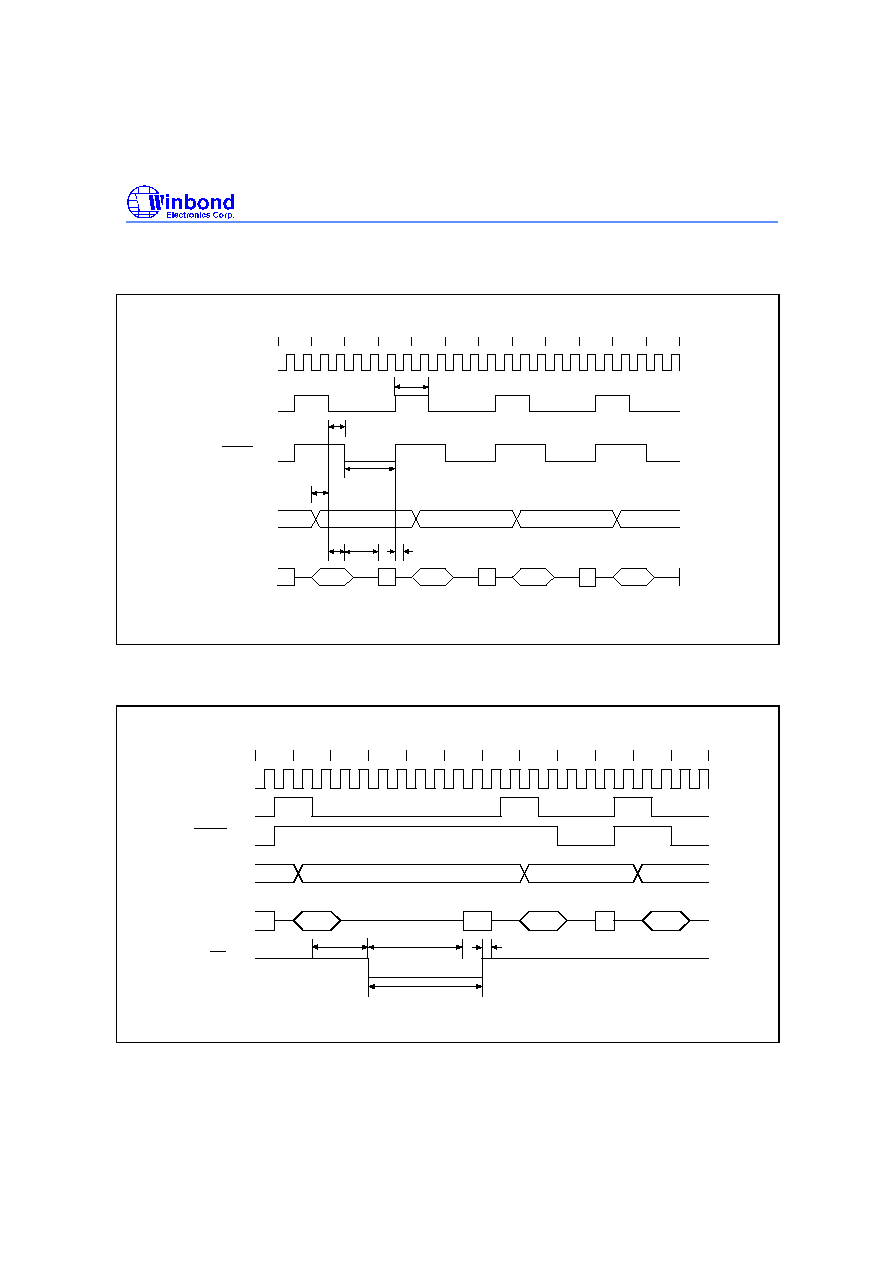

Program Fetch Cycle

PARAMETER

SYMBOL

MIN.

TYP.

MAX.

UNIT

NOTES

Address Valid to ALE Low

T

AAS

1 T

CP

-

-

-

nS

4

Address Hold from ALE Low

T

AAH

1 T

CP

-

-

-

nS

1, 4

ALE Low to

PSEN

Low

T

APL

1 T

CP

-

-

-

nS

4

PSEN

Low to Data Valid

T

PDA

-

-

2 T

CP

nS

2

Data Hold after PSEN High

T

PDH

0

-

1 T

CP

nS

3

Data Float after PSEN High

T

PDZ

0

-

1 T

CP

nS

ALE Pulse Width

T

ALW

2 T

CP

-

2 T

CP

-

nS

4

PSEN Pulse Width

T

PSW

3 T

CP

-

3 T

CP

-

nS

4

Notes:

1. P0.0

-

P0.7, P2.0

-

P2.7 remain stable throughout entire memory cycle.

2. Memory access time is 3 T

CP

.

3. Data have been latched internally prior to PSEN going high.

4. "

" (due to buffer driving delay and wire loading) is 20 nS.

W78E516B

- 16 -

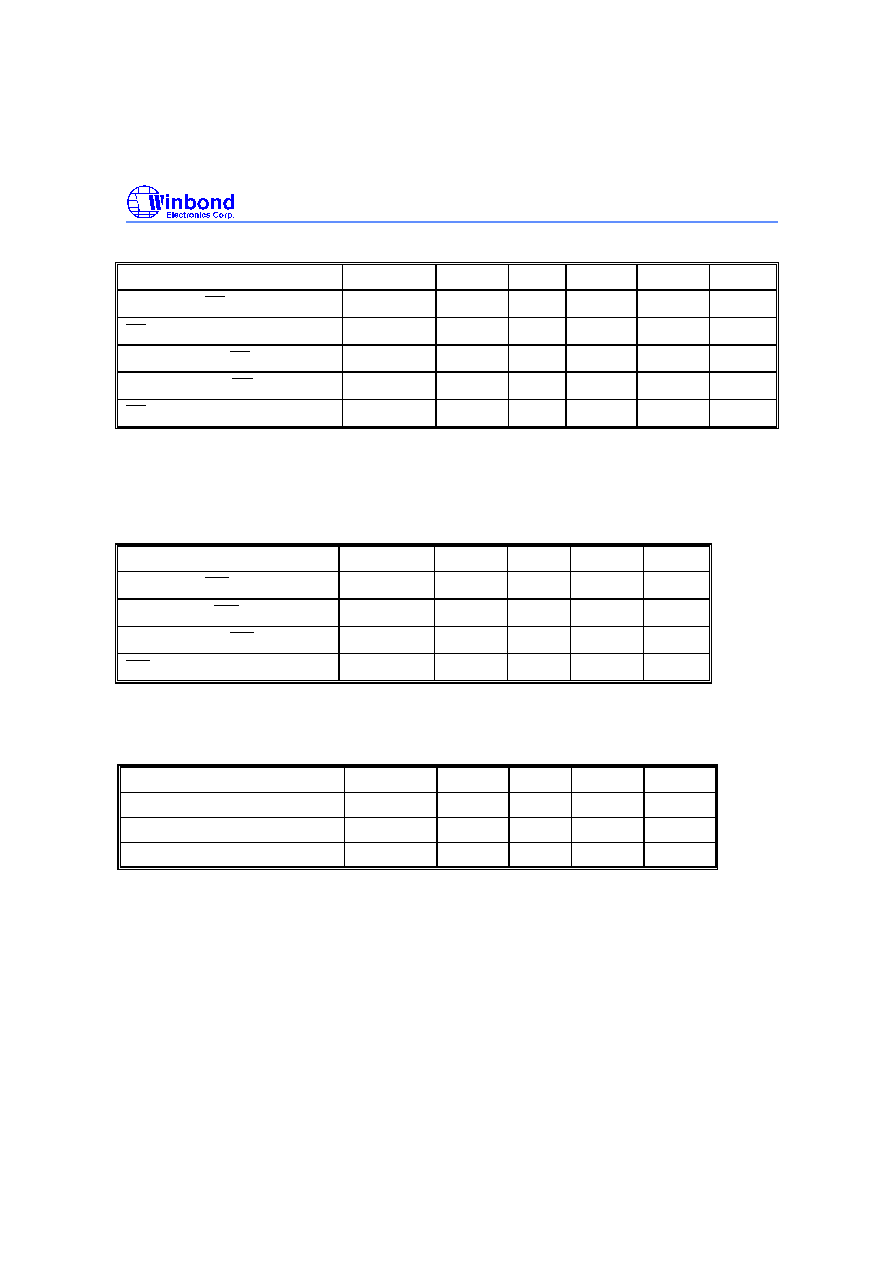

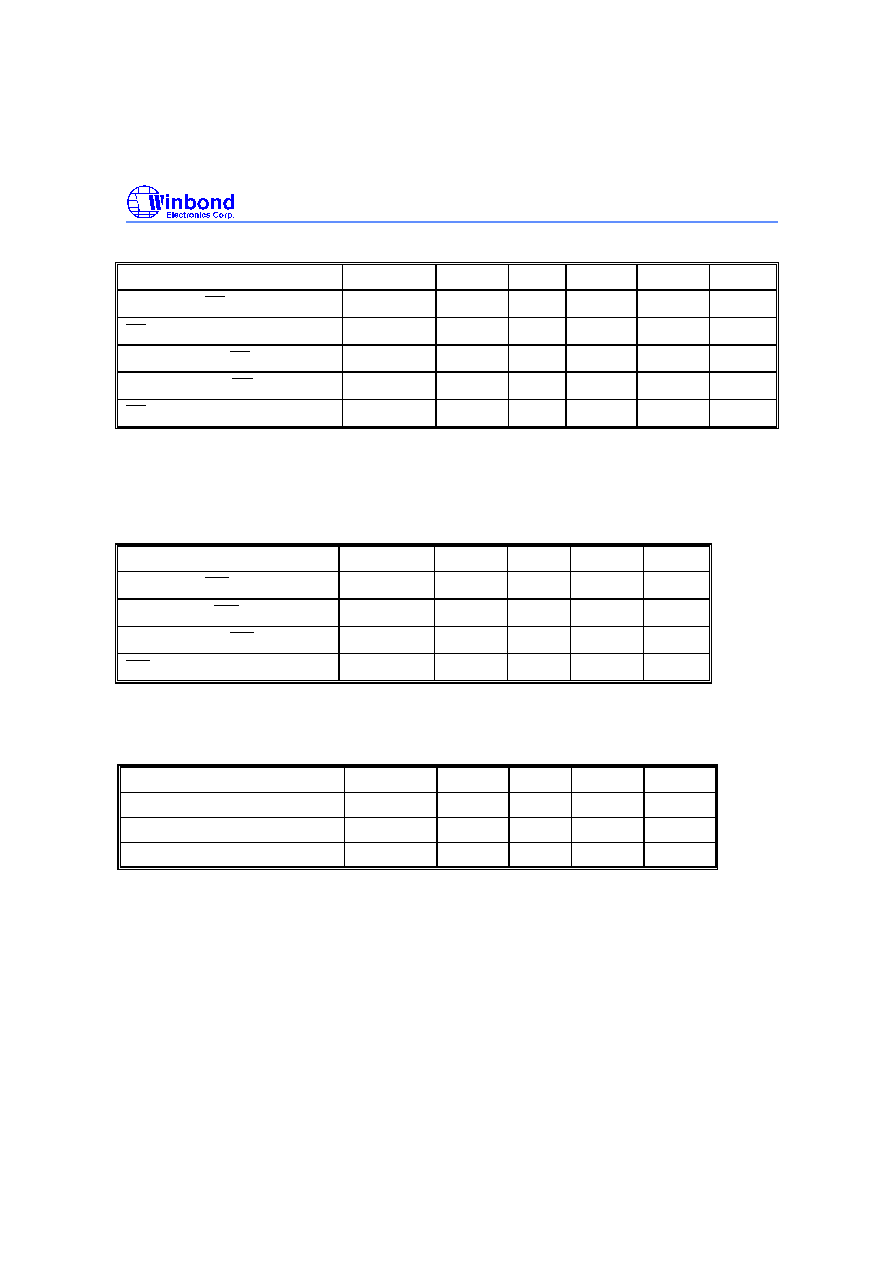

Data Read Cycle

PARAMETER

SYMBOL

MIN.

TYP.

MAX.

UNIT

NOTES

ALE Low to RD Low

T

DAR

3 T

CP

-

-

3 T

CP+

nS

1, 2

RD Low to Data Valid

T

DDA

-

-

4 T

CP

nS

1

Data Hold from RD High

T

DDH

0

-

2 T

CP

nS

Data Float from RD High

T

DDZ

0

-

2 T

CP

nS

RD Pulse Width

T

DRD

6 T

CP

-

6 T

CP

-

nS

2

Notes:

1. Data memory access time is 8 T

CP

.

2. "

" (due to buffer driving delay and wire loading) is 20 nS.

Data Write Cycle

PARAMETER

SYMBOL

MIN.

TYP.

MAX.

UNIT

ALE Low to WR Low

T

DAW

3 T

CP

-

-

3 T

CP

+

nS

Data Valid to WR Low

T

DAD

1 T

CP

-

-

-

nS

Data Hold from WR High

T

DWD

1 T

CP

-

-

-

nS

WR Pulse Width

T

DWR

6 T

CP

-

6 T

CP

-

nS

Note: "

" (due to buffer driving delay and wire loading) is 20 nS.

Port Access Cycle

PARAMETER

SYMBOL

MIN.

TYP.

MAX.

UNIT

Port Input Setup to ALE Low

T

PDS

1 TCP

-

-

nS

Port Input Hold from ALE Low

T

PDH

0

-

-

nS

Port Output to ALE

T

PDA

1 TCP

-

-

nS

Note: Ports are read during S5P2, and output data becomes available at the end of S6P2. The timing data are referenced to

ALE, since it provides a convenient reference.

W78E516B

Publication Release Date: February 2000

- 17 - Revision A3

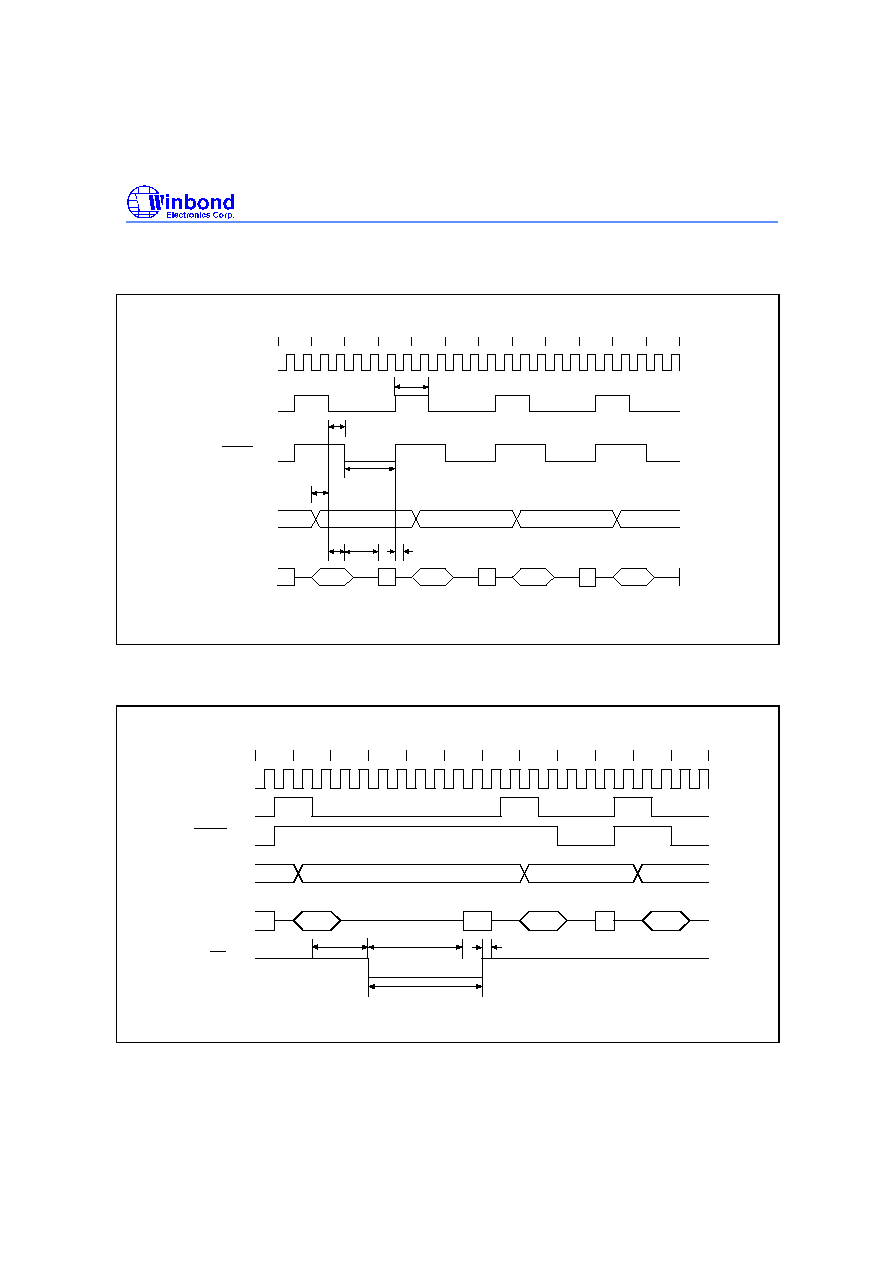

TIMING WAVEFORMS

Program Fetch Cycle

S1

XTAL1

S2

S3

S4

S5

S6

S1

S2

S3

S4

S5

S6

ALE

PORT 2

A0-A7

A0-A7

Data

A0-A7

Code

T

A0-A7

Data

Code

PORT 0

PSEN

PDH,

T

PDZ

T

PDA

T

AAH

T

AAS

T

PSW

T

APL

T

ALW

Data Read Cycle

S2

S3

S5

S6

S1

S2

S3

S4

S5

S6

S1

S4

XTAL1

ALE

PSEN

DATA

A8-A15

PORT 2

PORT 0

A0-A7

RD

T

DDH,

T

DDZ

T

DDA

T

DRD

T

DAR

W78E516B

- 18 -

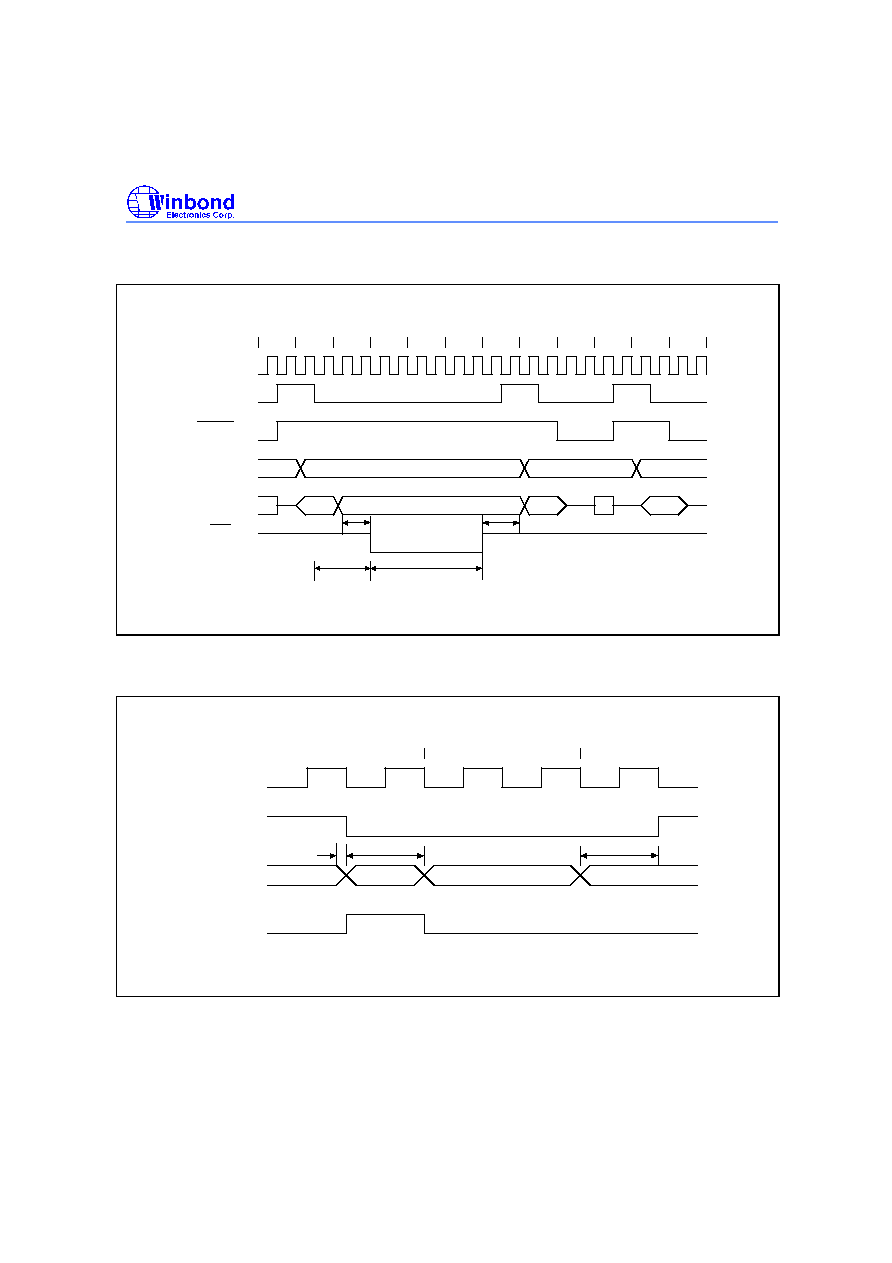

Timing Waveforms, continued

Data Write Cycle

S2

S3

S5

S6

S1

S2

S3

S4

S1

S5

S6

S4

XTAL1

ALE

PSEN

A8-A15

DATA OUT

PORT 2

PORT 0

A0-A7

WR

T

T

DAW

DAD

T

DWR

T

DWD

Port Access Cycle

XTAL1

ALE

S5

S6

S1

DATA OUT

T

T

PORT

INPUT

T

SAMPLE

PDA

PDH

PDS

W78E516B

Publication Release Date: February 2000

- 19 - Revision A3

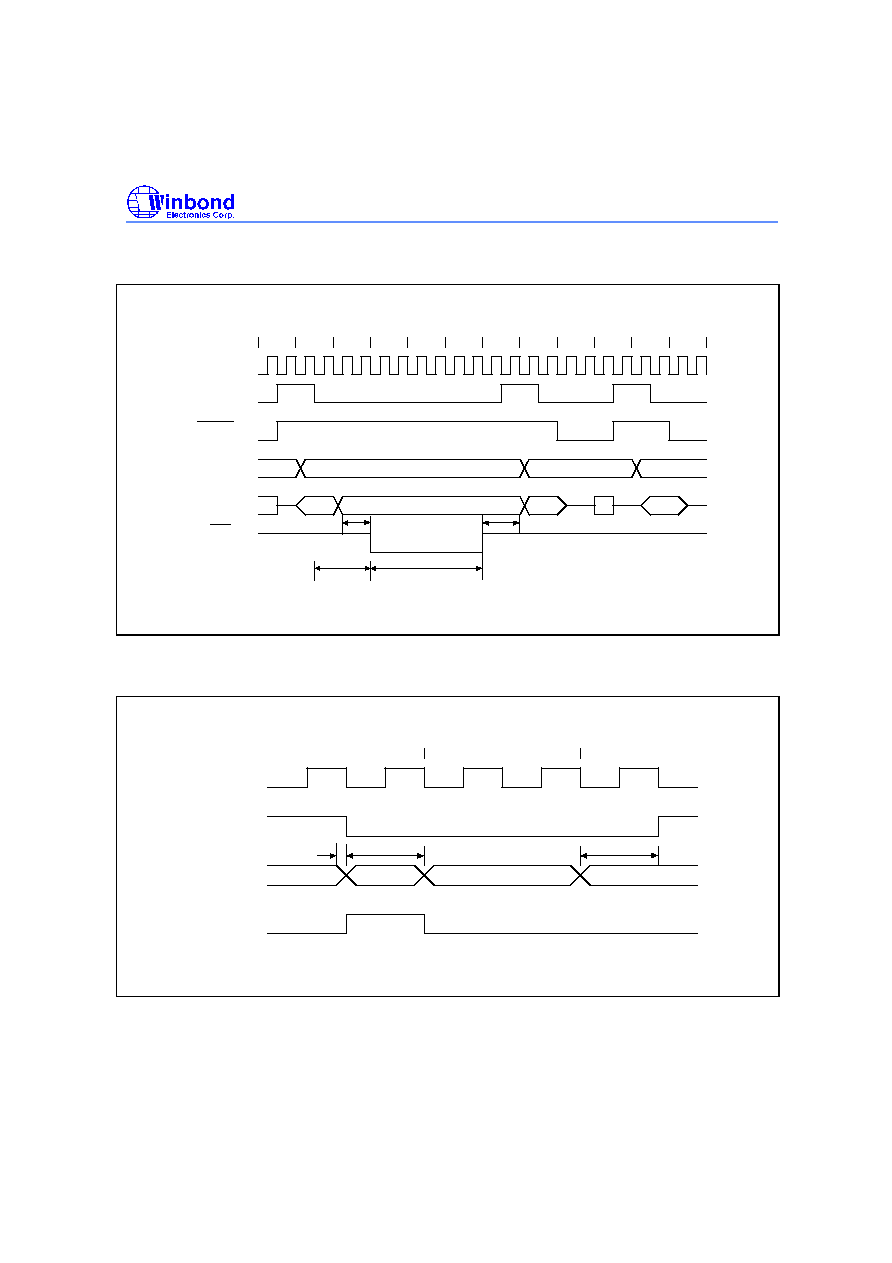

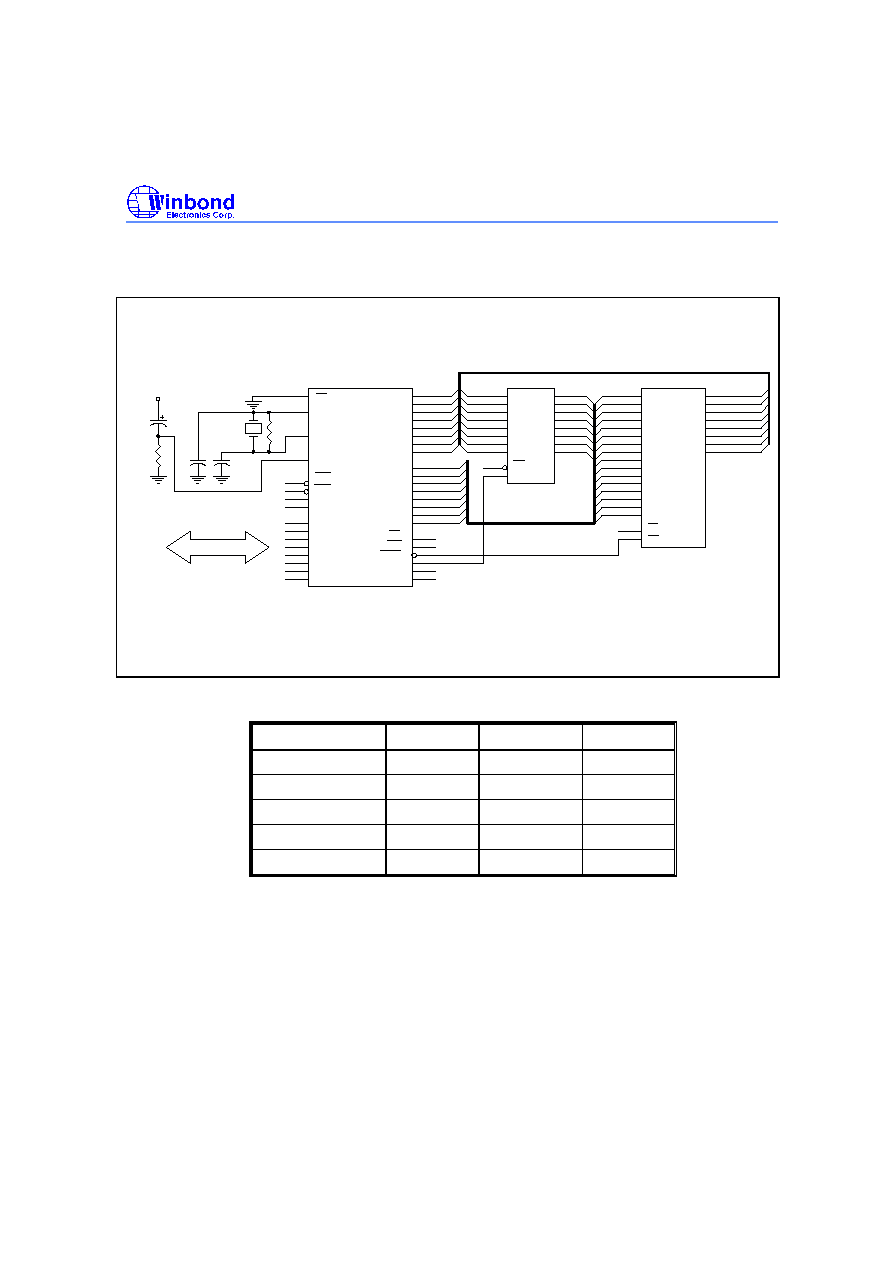

TYPICAL APPLICATION CIRCUIT

Expanded External Program Memory and Crystal

AD0

A0

A0

A0

10

A1

9

A2

8

A3

7

A4

6

A5

5

A6

4

A7

3

A8

25

A9

24

A10

21

A11

23

A12

2

A13

26

A14

27

A15

1

CE

20

OE

22

O0

11

O1

12

O2

13

O3

15

O4

16

O5

17

O6

18

O7

19

27512

AD0

D0

3

Q0

2

D1

4

Q1

5

D2

7

Q2

6

D3

8

Q3

9

D4

13

Q4

12

D5

14

Q5

15

D6

17

Q6

16

D7

18

Q7

19

OC

1

G

11

74LS373

AD0

EA

31

XTAL1

19

XTAL2

18

RST

9

INT0

12

INT1

13

T0

14

T1

15

P1.0

1

P1.1

2

P1.2

3

P1.3

4

P1.4

5

P1.5

6

P1.6

7

P1.7

8

39

38

37

36

35

34

33

32

21

22

23

24

25

26

27

28

17

WR

P0.0

P0.1

P0.2

P0.3

P0.4

P0.5

P0.6

P0.7

P2.0

P2.1

P2.2

P2.3

P2.4

P2.5

P2.6

P2.7

RD

16

PSEN

29

ALE

30

TXD

11

RXD

10

W78E516B

10 u

8.2 K

V

CRYSTAL

C1

C2

R

AD1

AD2

AD3

AD4

AD5

AD6

AD7

A8

AD1

AD2

AD3

AD4

AD5

AD6

AD7

GND

A1

A2

A3

A4

A5

A6

A7

A1

A2

A3

A4

A5

A6

A7

A8

A9

AD1

AD2

AD3

AD4

AD5

AD6

AD7

A10

A11

A12

A13

A14

A15

GND

A9

A10

A11

A12

A13

A14

A15

DD

Figure A

CRYSTAL

C1

C2

R

6 MHz

47P

47P

-

16 MHz

30P

30P

-

24 MHz

15P

10P

-

32 MHz

10P

10P

6.8K

40 MHz

5P

5P

4.7K

Above table shows the reference values for crystal applications.

Notes:

1. C1, C2, R components refer to Figure A

2. Crystal layout must get close to XTAL1 and XTAL2 pins on user's application board.

W78E516B

- 20 -

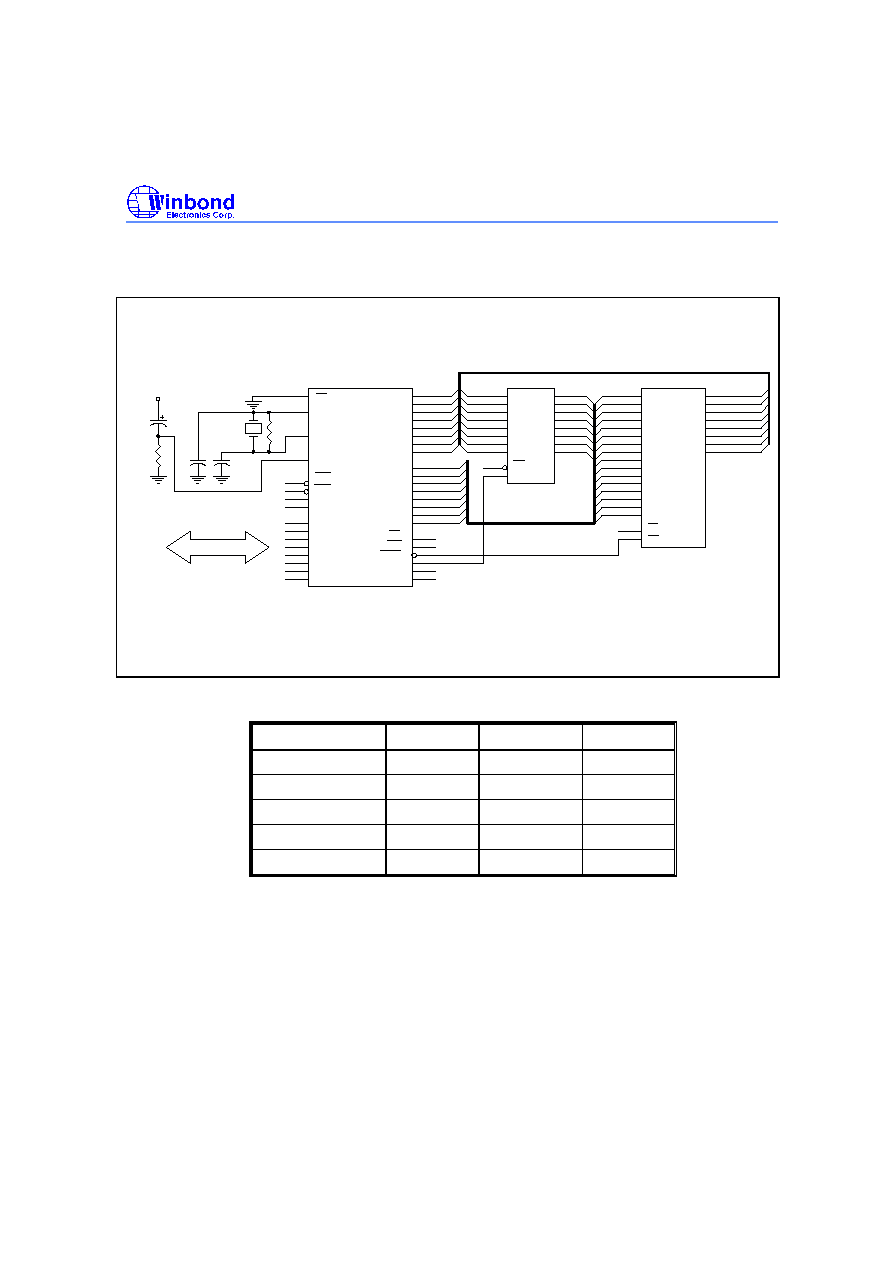

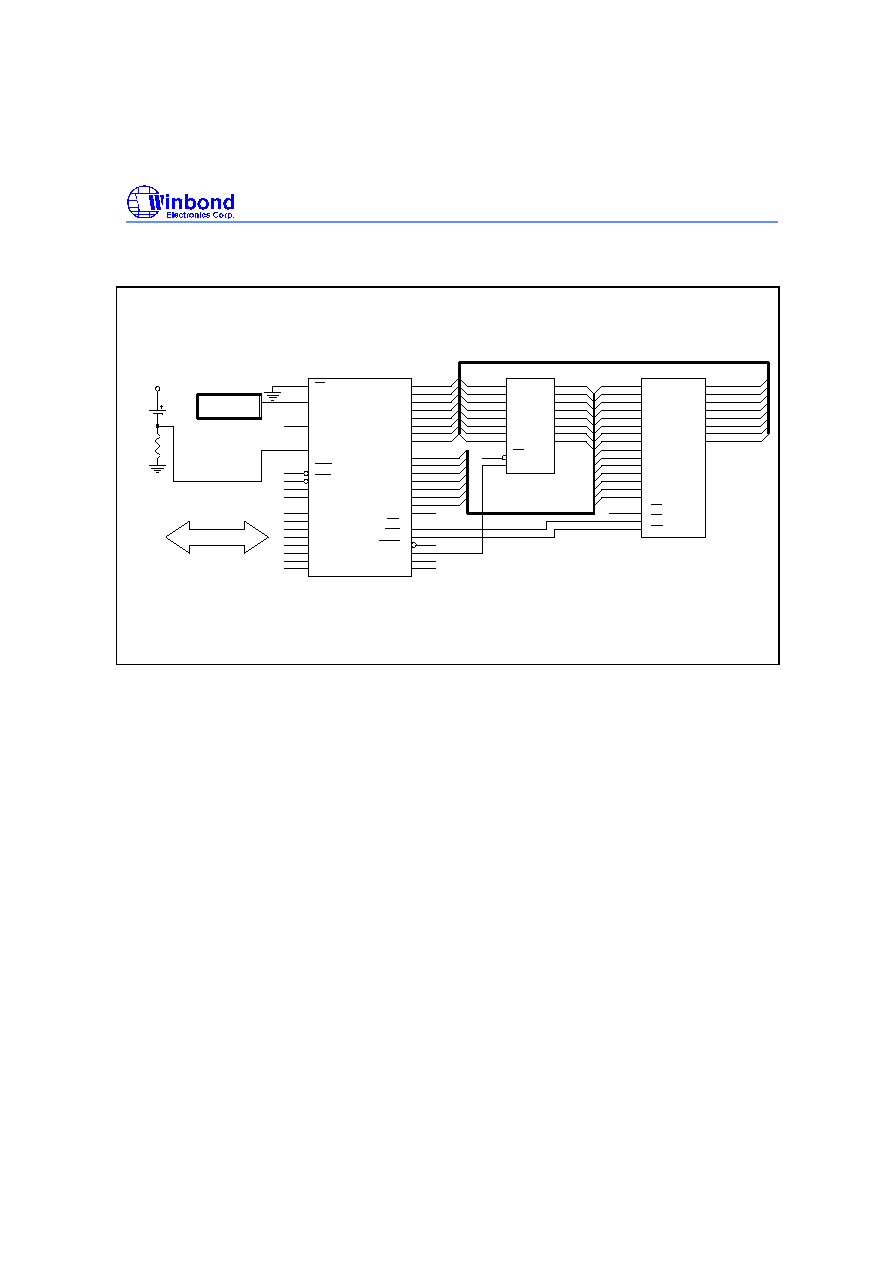

Tipical Application Circuit, continued

Expanded External Data Memory and Oscillator

10 u

8.2 K

V

OSCILLATOR

EA

31

XTAL1

19

XTAL2

18

RST

9

INT0

12

INT1

13

T0

14

T1

15

P1.0

1

P1.1

2

P1.2

3

P1.3

4

P1.4

5

P1.5

6

P1.6

7

P1.7

8

P0.0

39

P0.1

38

P0.2

37

P0.3

36

P0.4

35

P0.5

34

P0.6

33

P0.7

32

P2.0

21

P2.1

22

P2.2

23

P2.3

24

P2.4

25

P2.5

26

P2.6

27

P2.7

28

RD

17

WR

16

PSEN

29

ALE

30

TXD

11

RXD

10

W78E516B

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

A0

A1

A2

A3

A4

A5

A6

A7

D0

3

Q0

2

D1

4

Q1

5

D2

7

Q2

6

D3

8

Q3

9

D4

13

Q4

12

D5

14

Q5

15

D6

17

Q6

16

D7

18

Q7

19

OC

1

G

11

74LS373

A0

A1

A2

A3

A4

A5

A6

A7

10

9

8

7

6

5

4

3

A0

A1

A2

A3

A4

A5

A6

A7

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

11

12

13

15

16

17

18

19

D0

D1

D2

D3

D4

D5

D6

D7

A8

A9

A10

A11

A12

A13

A14

25

24

21

23

26

1

20

2

A8

A9

A10

A11

A12

A13

A14

CE

GND

A8

A9

A10

A11

A12

A13

A14

GND

22

27

OE

WR

20256

DD

Figure B

W78E516B

Publication Release Date: February 2000

- 21 - Revision A3

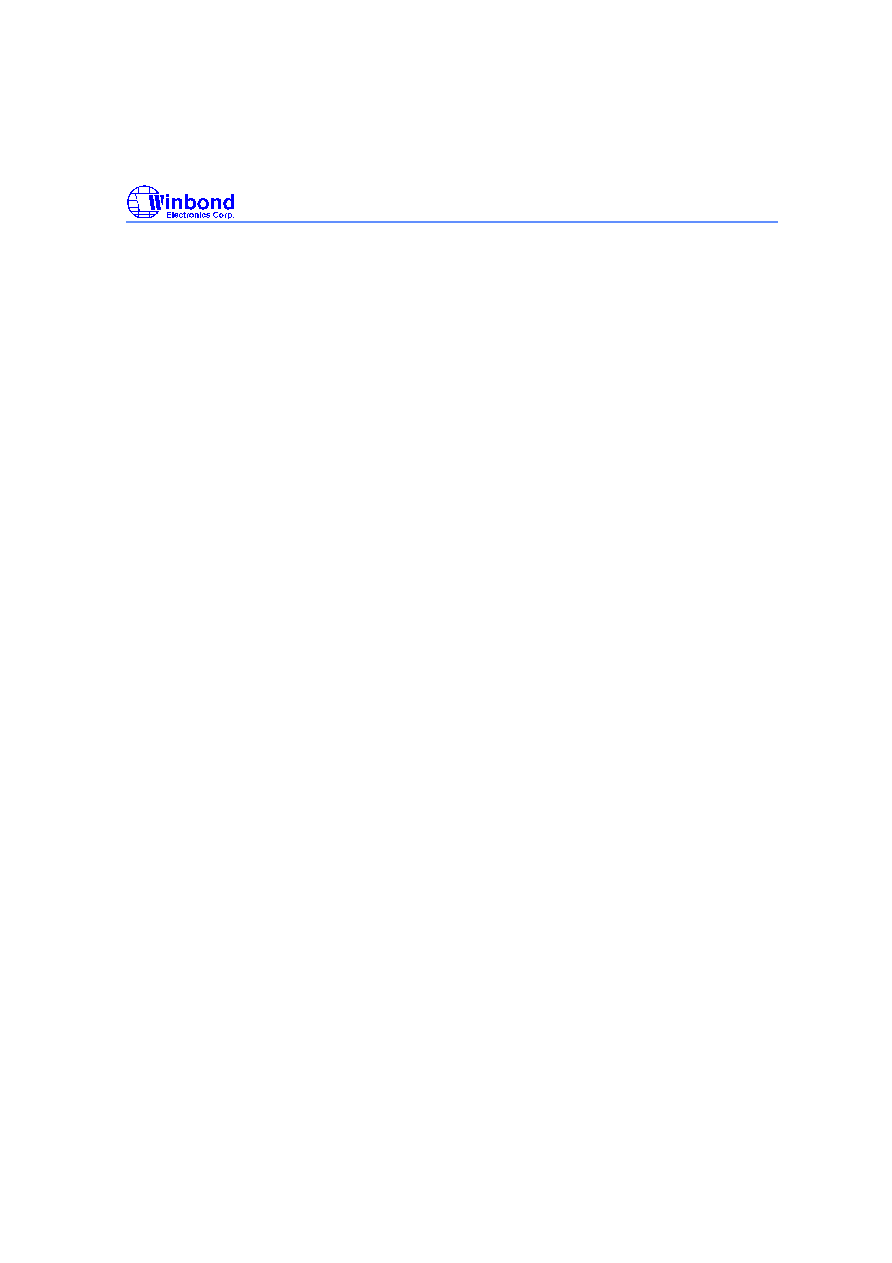

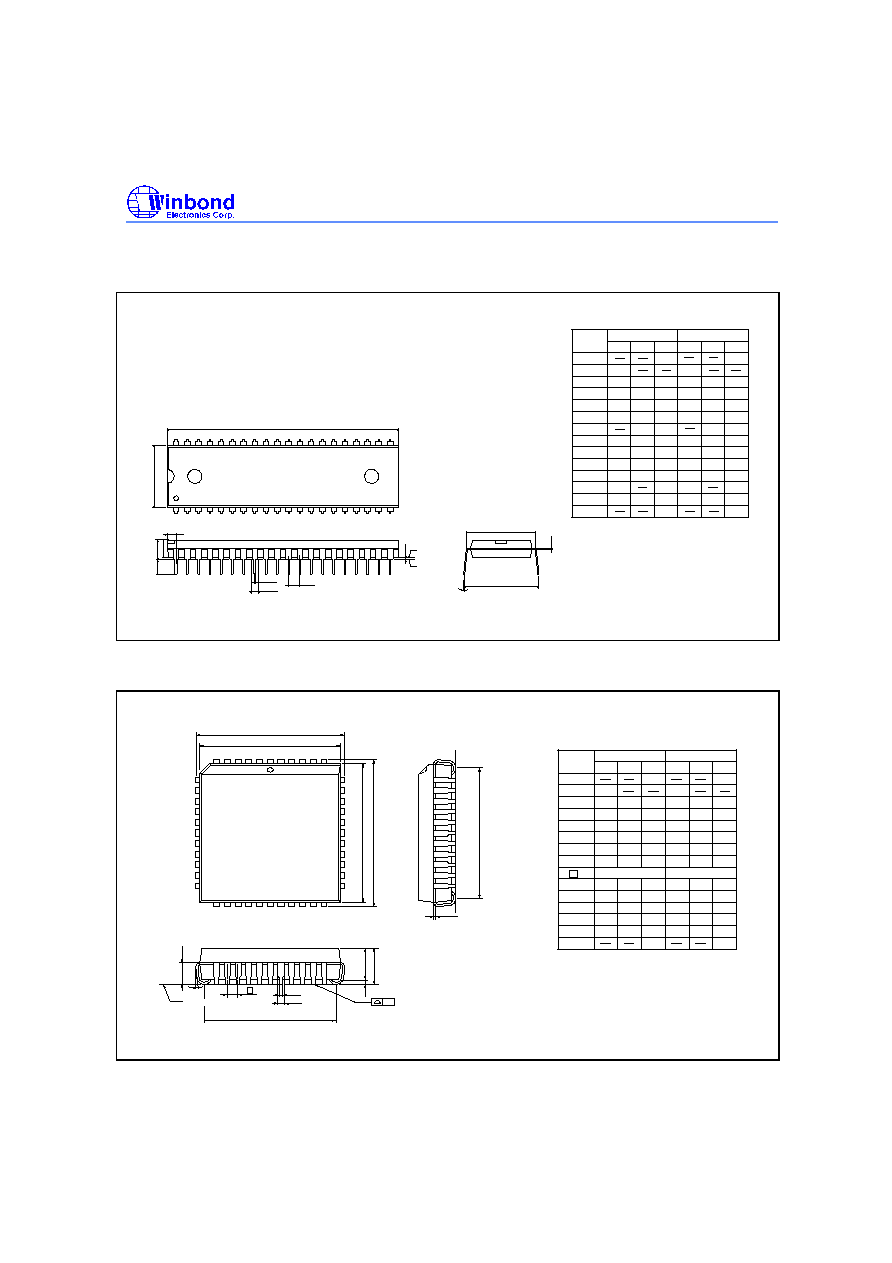

PACKAGE DIMENSIONS

40-pin DIP

Seating Plane

1. Dimension D Max. & S include mold flash or

tie bar burrs.

2. Dimension E1 does not include interlead flash.

3. Dimension D & E1 include mold mismatch and

are determined at the mold parting line.

6. General appearance spec. should be based on

final visual inspection spec.

.

1.372

1.219

0.054

0.048

Notes:

Symbol

Min. Nom.

Max.

Max.

Nom.

Min.

Dimension in inch

Dimension in mm

0.050

1.27

0.210

5.334

0.010

0.150

0.016

0.155

0.018

0.160

0.022

3.81

0.406

0.254

3.937

0.457

4.064

0.559

0.008

0.120

0.670

0.010

0.130

0.014

0.140

0.203

3.048

0.254

3.302

0.356

3.556

0.540

0.550

0.545

13.72

13.97

13.84

17.01

15.24

14.986

15.494

0.600

0.590

0.610

2.286

2.54

2.794

0.090

0.100

0.110

A

B

c

D

e

A

L

S

A

A

1

2

E

B

1

1

e

E

1

a

2.055

2.070

52.20

52.58

0

15

0.090

2.286

0.650

0.630

16.00

16.51

protrusion/intrusion.

4. Dimension B1 does not include dambar

5. Controlling dimension: Inches.

15

0

e

A

A

a

c

E

Base Plane

1

A

1

e

L

A

S

1

E

D

1

B

B

40

21

20

1

2

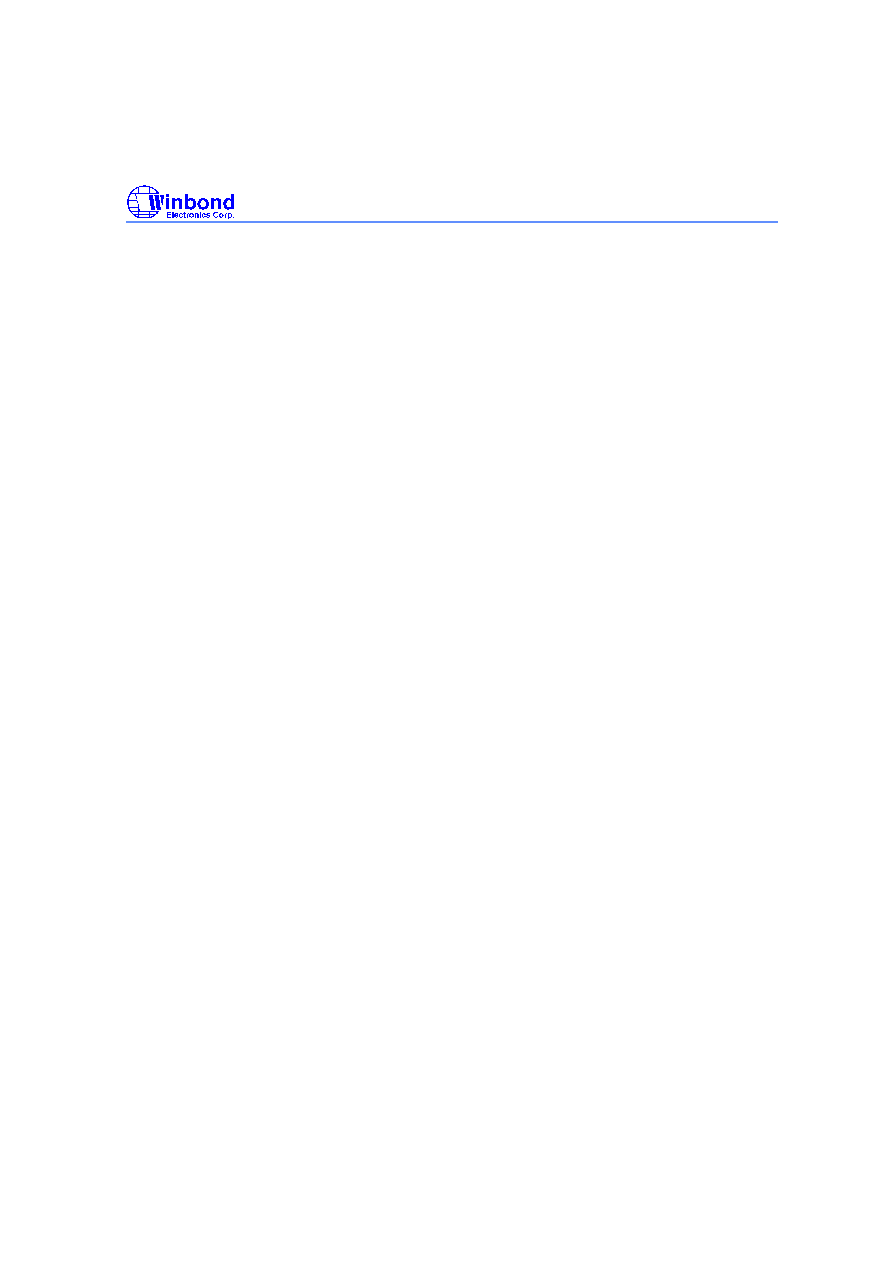

44-pin PLCC

44

40

39

29

28

18

17

7

6

1

L

c

1

b

2

A

H

D

D

e

b

E

H

E

y

A

A

1

Seating Plane

D

G

G

E

Symbol

Min. Nom.

Max.

Max.

Nom.

Min.

Dimension in inch

Dimension in mm

A

b

c

D

e

H

E

L

y

A

A

1

2

E

b

1

H

D

G

G

D

E

Notes:

on final visual inspection spec.

4. General appearance spec. should be based

3. Controlling dimension: Inches

protrusion/intrusion.

2. Dimension b1 does not include dambar

flash.

1. Dimension D & E do not include interlead

0.020

0.145

0.026

0.016

0.008

0.648

0.590

0.680

0.090

0.150

0.028

0.018

0.010

0.653

0.610

0.690

0.100

0.050

BSC

0.185

0.155

0.032

0.022

0.014

0.658

0.630

0.700

0.110

0.004

0.508

3.683

0.66

0.406

0.203

16.46

14.99

17.27

2.296

3.81

0.711

0.457

0.254

16.59

15.49

17.53

2.54

1.27

4.699

3.937

0.813

0.559

0.356

16.71

16.00

17.78

2.794

0.10

BSC

16.71

16.59

16.46

0.658

0.653

0.648

16.00

15.49

14.99

0.630

0.610

0.590

17.78

17.53

17.27

0.700

0.690

0.680

W78E516B

- 22 -

Application Note: In-system Programming Software Examples

This application note illustrates the in-system programmability of the Winbond W78E516B MTP-ROM

microcontroller. In this example, microcontroller will boot from 64 KB APROM bank and waiting for a

key to enter in-system programming mode for re-programming the contents of 64 KB APROM. While

entering in-system programming mode, microcontroller executes the loader program in 4KB LDROM

bank. The loader program erases the 64 KB APROM then reads the new code data from external

SRAM buffer (or through other interfaces) to update the 64KB APROM.

EXAMPLE 1:

;*******************************************************************************************************************

;* Example of 64K APROM program: Program will scan the P1.0. if P1.0 = 0, enters in-system

;* programming mode for updating the content of APROM code else executes the current ROM code.

;* XTAL = 40 MHz

;*******************************************************************************************************************

.chip 8052

.RAMCHK OFF

.symbols

CHPCON EQU BFH

CHPENR EQU F6H

SFRAL EQU C4H

SFRAH EQU C5H

SFRFD EQU C6H

SFRCN EQU C7H

ORG 0H

LJMP 100H ; JUMP TO MAIN PROGRAM

;************************************************************************

;* TIMER0 SERVICE VECTOR ORG = 000BH

;************************************************************************

ORG 00BH

CLR TR0 ; TR0 = 0, STOP TIMER0

MOV TL0,R6

MOV TH0,R7

RETI

;************************************************************************

;* 64K APROM MAIN PROGRAM

;************************************************************************

ORG 100H

MAIN_64K:

MOV A,P1 ; SCAN P1.0

ANL A,#01H

CJNE A,#01H,PROGRAM_64K ; IF P1.0 = 0, ENTER IN-SYSTEM PROGRAMMING MODE

JMP NORMAL_MODE

PROGRAM_64K:

MOV CHPENR,#87H ; CHPENR = 87H, CHPCON REGISTER WRTE ENABLE

MOV CHPENR,#59H ; CHPENR = 59H, CHPCON REGISTER WRITE ENABLE

MOV CHPCON,#03H ; CHPCON = 03H, ENTER IN-SYSTEM PROGRAMMING MODE

MOV TCON,#00H ; TR = 0 TIMER0 STOP

MOV IP,#00H ; IP = 00H

MOV IE,#82H ; TIMER0 INTERRUPT ENABLE FOR WAKE-UP FROM IDLE MODE

MOV R6,#FEH ; TL0 = FEH

W78E516B

Publication Release Date: February 2000

- 23 - Revision A3

MOV R7,#FFH ; TH0 = FFH

MOV TL0,R6

MOV TH0,R7

MOV TMOD,#01H ; TMOD = 01H, SET TIMER0 A 16-BIT TIMER

MOV TCON,#10H ; TCON = 10H, TR0 = 1,GO

MOV PCON,#01H ; ENTER IDLE MODE FOR LAUNCHING THE IN-SYSTEM

; PROGRAMMABILITY

;********************************************************************************

;* Normal mode 64KB APROM program: depending user's application

;********************************************************************************

NORMAL_MODE:

. ; User's application program

.

.

.

EXAMPLE 2:

;*****************************************************************************************************************************

;* Example of 4KB LDROM program: This lorder program will erase the 64KB APROM first, then reads the new

;* code from external SRAM and program them into 64KB APROM bank. XTAL = 40 MHz

;*****************************************************************************************************************************

.chip 8052

.RAMCHK OFF

.symbols

CHPCON EQU BFH

CHPENR EQU F6H

SFRAL EQU C4H

SFRAH EQU C5H

SFRFD EQU C6H

SFRCN EQU C7H

ORG 000H

LJMP 100H ; JUMP TO MAIN PROGRAM

;************************************************************************

;* 1. TIMER0 SERVICE VECTOR ORG = 0BH

;************************************************************************

ORG 000BH

CLR TR0 ; TR0 = 0, STOP TIMER0

MOV TL0,R6

MOV TH0,R7

RETI

;************************************************************************

;* 4KB LDROM MAIN PROGRAM

;************************************************************************

ORG 100H

W78E516B

- 24 -

MAIN_4K:

MOV CHPENR,#87H ; CHPENR = 87H, CHPCON WRITE ENABLE.

MOV CHPENR,#59H ; CHPENR = 59H, CHPCON WRITE ENABLE.

MOV A,CHPCON

ANL A,#80H

CJNE A,#80H,UPDATE_64K ; CHECK F04KBOOT MODE ?

MOV CHPCON,#03H ; CHPCON = 03H, ENABLE IN-SYSTEM PROGRAMMING.

MOV CHPENR,#00H ; DISABLE CHPCON WRITE ATTRIBUTE

MOV TCON,#00H ; TCON = 00H, TR = 0 TIMER0 STOP

MOV TMOD,#01H ; TMOD = 01H, SET TIMER0 A 16BIT TIMER

MOV IP,#00H ; IP = 00H

MOV IE,#82H ; IE = 82H, TIMER0 INTERRUPT ENABLED

MOV R6,#FEH

MOV R7,#FFH

MOV TL0,R6

MOV TH0,R7

MOV TCON,#10H ; TCON = 10H, TR0 = 1, GO

MOV PCON,#01H ; ENTER IDLE MODE

UPDATE_64K:

MOV CHPENR,#00H ; DISABLE CHPCON WRITE-ATTRIBUTE

MOV TCON,#00H ; TCON = 00H , TR = 0 TIM0 STOP

MOV IP,#00H ; IP = 00H

MOV IE,#82H ; IE = 82H, TIMER0 INTERRUPT ENABLED

MOV TMOD,#01H ; TMOD = 01H, MODE1

MOV R6,#3CH ; SET WAKE-UP TIME FOR ERASE OPERATION, ABOUT 15 mS. DEPENDING

; ON USER'S SYSTEM CLOCK RATE.

MOV R7,#B0H

MOV TL0,R6

MOV TH0,R7

ERASE_P_4K:

MOV SFRCN,#22H ; SFRCN(C7H) = 22H ERASE 64K

MOV TCON,#10H ; TCON = 10H, TR0 = 1,GO

MOV PCON,#01H ; ENTER IDLE MODE (FOR ERASE OPERATION)

;*********************************************************************

;* BLANK CHECK

;*********************************************************************

MOV SFRCN,#0H ; READ 64KB APROM MODE

MOV SFRAH,#0H ; START ADDRESS = 0H

MOV SFRAL,#0H

MOV R6,#FBH ; SET TIMER FOR READ OPERATION, ABOUT 1.5

µ

S.

MOV R7,#FFH

MOV TL0,R6

MOV TH0,R7

BLANK_CHECK_LOOP:

SETB TR0 ; ENABLE TIMER 0

MOV PCON,#01H ; ENTER IDLE MODE

MOV A,SFRFD ; READ ONE BYTE

CJNE A,#FFH,BLANK_CHECK_ERROR

W78E516B

Publication Release Date: February 2000

- 25 - Revision A3

INC SFRAL ; NEXT ADDRESS

MOV A,SFRAL

JNZ BLANK_CHECK_LOOP

INC SFRAH

MOV A,SFRAH

CJNE A,#0H,BLANK_CHECK_LOOP ; END ADDRESS = FFFFH

JMP PROGRAM_64KROM

BLANK_CHECK_ERROR:

MOV P1,#F0H

MOV P3,#F0H

JMP $

;*******************************************************************************

;* RE-PROGRAMMING 64KB APROM BANK

;*******************************************************************************

PROGRAM_64KROM:

MOV DPTR,#0H ; THE ADDRESS OF NEW ROM CODE

MOV R2,#00H ; TARGET LOW BYTE ADDRESS

MOV R1,#00H ; TARGET HIGH BYTE ADDRESS

MOV DPTR,#0H ; EXTERNAL SRAM BUFFER ADDRESS

MOV SFRAH,R1 ; SFRAH, TARGET HIGH ADDRESS

MOV SFRCN,#21H ; SFRCN(C7H) = 21 (PROGRAM 64K)

MOV R6,#5AH ; SET TIMER FOR PROGRAMMING, ABOUT 50

µ

S.

MOV R7,#FFH

MOV TL0,R6

MOV TH0,R7

PROG_D_64K:

MOV SFRAL,R2 ; SFRAL(C4H) = LOW BYTE ADDRESS

MOVX A,@DPTR ; READ DATA FROM EXTERNAL SRAM BUFFER

MOV SFRFD,A ; SFRFD(C6H) = DATA IN

MOV TCON,#10H ; TCON = 10H, TR0 = 1,GO

MOV PCON,#01H ; ENTER IDLE MODE (PRORGAMMING)

INC DPTR

INC R2

CJNE R2,#0H,PROG_D_64K

INC R1

MOV SFRAH,R1

CJNE R1,#0H,PROG_D_64K

;*****************************************************************************

; * VERIFY 64KB APROM BANK

;*****************************************************************************

MOV R4,#03H ; ERROR COUNTER

MOV R6,#FBH ; SET TIMER FOR READ VERIFY, ABOUT 1.5

µ

S.

MOV R7,#FFH

MOV TL0,R6

MOV TH0,R7

MOV DPTR,#0H ; The start address of sample code

MOV R2,#0H ; Target low byte address

MOV R1,#0H ; Target high byte address

MOV SFRAH,R1 ; SFRAH, Target high address

MOV SFRCN,#00H ; SFRCN = 00 (Read ROM CODE)

W78E516B

- 26 -

READ_VERIFY_64K:

MOV SFRAL,R2 ; SFRAL(C4H) = LOW ADDRESS

MOV TCON,#10H ; TCON = 10H, TR0 = 1,GO

MOV PCON,#01H

INC R2

MOVX A,@DPTR

INC DPTR

CJNE A,SFRFD,ERROR_64K

CJNE R2,#0H,READ_VERIFY_64K

INC R1

MOV SFRAH,R1

CJNE R1,#0H,READ_VERIFY_64K

;******************************************************************************

;* PROGRAMMING COMPLETLY, SOFTWARE RESET CPU

;******************************************************************************

MOV CHPENR,#87H ; CHPENR = 87H

MOV CHPENR,#59H ; CHPENR = 59H

MOV CHPCON,#83H ; CHPCON = 83H, SOFTWARE RESET.

ERROR_64K:

DJNZ R4,UPDATE_64K ; IF ERROR OCCURS, REPEAT 3 TIMES.

. ; IN-SYSTEM PROGRAMMING FAIL, USER'S PROCESS TO DEAL WITH IT.

.

.

.

Headquarters

No. 4, Creation Rd. III,

Science-Based Industrial Park,

Hsinchu, Taiwan

TEL: 886-3-5770066

FAX: 886-3-5792766

http://www.winbond.com.tw/

Voice & Fax-on-demand: 886-2-27197006

Taipei Office

11F, No. 115, Sec. 3, Min-Sheng East Rd.,

Taipei, Taiwan

TEL: 886-2-27190505

FAX: 886-2-27197502

Winbond Electronics (H.K.) Ltd.

Rm. 803, World Trade Square, Tower II,

123 Hoi Bun Rd., Kwun Tong,

Kowloon, Hong Kong

TEL: 852-27513100

FAX: 852-27552064

Winbond Electronics North America Corp.

Winbond Memory Lab.

Winbond Microelectronics Corp.

Winbond Systems Lab.

2727 N. First Street, San Jose,

CA 95134, U.S.A.

TEL: 408-9436666

FAX: 408-5441798

Note: All data and specifications are subject to change without notice.