| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: WM2331CDT | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

WM2331

10-bit 30MSPS ADC with PGA and Clamp

WOLFSON MICROELECTRONICS LTD

www.wolfsonmicro.com

Production Data, July 2001, Rev 1.5.

Copyright

2001 Wolfson Microelectronics Ltd.

DESCRIPTION

The WM2331 is a high speed, 10-bit pipeline analogue-to-

digital converter (ADC) with on-chip programmable gain

amplifier (PGA) and clamp circuit, and internal voltage

references. Conversion is controlled by a single clock input.

The device has a high bandwidth differential sample and

hold input, which gives excellent common-mode noise

immunity and low distortion. Alternatively, it can be driven

in single ended fashion with an optional voltage clamp for

DC restoration that can take its reference from an on-chip

10-bit DAC or an external source.

The WM2331 provides internal reference voltages for

setting the ADC full-scale range without the requirement for

external circuitry. However, it can also accept external

references for applications where common or high-precision

references are required.

A bidirectional 10-bit parallel interface is used both to

control the device and to read ADC conversion data. ADC

data can be output in unsigned binary or two's complement

format. An out-of-range output pin indicates when the input

signal is outside the converter's range.

The WM2331 operates with independent analogue and

digital supplies of 3V to 5.5V and is supplied in a 28-pin

TSSOP package.

FEATURES

∑

10-bit

resolution

ADC

∑

30MSPS

conversion

rate

∑

Programmable Gain Amplifier (PGA)

∑

Built in clamp function (DC restore) with 10-bit DAC

∑

Adjustable internal voltage references

∑

Wide Input Bandwidth - 150MHz

∑

Unsigned Binary or Two's complement output format

∑

Programmable via parallel interface

∑

Independent analogue and digital supplies, 3V to 5.5V

∑

Low power - 92mW typical at 3.0V supplies

∑

Powerdown mode to 3mW typical

∑

28-pin TSSOP package

APPLICATIONS

∑

Composite Video Digitisation

∑

Digital

Copiers

∑

Digital Video Cameras

∑

Set Top Box (STB)

∑

IF and Baseband Digitisation

∑

Medical

Imaging

∑

High Speed Data Acquisition

BLOCK DIAGRAM

AIN

ON-CHIP

REFERENCE

GENERATOR

ADC

Core

S/H

PGA

REFTS

DIO[9:0]

INPUT/

OUTPUT

BUFFERS

OVR

REFBS

MODE

REFSENSE

AGND

AVDD

REFBF REFTF

CLAMP

LEVEL

DAC

CLAMP

AMPLIFIER

OEB

DGND

DVDD

CONTROL

REGISTERS

CLAMP

CLAMPIN

M

U

X

WR

TIMING

CONTROL

CLK

VREF

WM2331

WM2331

Production Data

PD Rev 1.5 July 2001

2

PIN CONFIGURATION

ORDERING INFORMATION

DEVICE

TEMP. RANGE

PACKAGE

WM2331CDT/V

0 to +70

o

C

28-pin TSSOP

WM2331IDT/V

-40 to +85

o

C

28-pin TSSOP

16

15

14

20

19

18

17

5

6

7

1

2

3

4

13

12

11

8

9

10

DIO0

OVR

OEB

AGND

DVDD

REFTS

REFBS

REFBF

REFTF

MODE

VREF

AIN

AVDD

DIO8

REFSENSE

DIO2

DIO3

DIO1

DIO7

CLAMP

DIO6

DIO5

CLAMPIN

DIO4

21

22

23

24

25

26

27

28

DIO9

DGND

WR

CLK

PIN DESCRIPTION

PIN

NAME

TYPE

DESCRIPTION

1

AGND

Ground

Negative Analogue Supply

2

DVDD

Supply

Positive Digital Supply

3

DIO0

Digital Input/Output

Digital input/output bit 0 (LSB)

4

DIO1

Digital Input/Output

Digital input/output bit 1

5

DIO2

Digital Input/Output

Digital input/output bit 2

6

DIO3

Digital Input/Output

Digital input/output bit 3

7

DIO4

Digital Input/Output

Digital input/output bit 4

8

DIO5

Digital Input/Output

Digital input/output bit 5

9

DIO6

Digital Input/Output

Digital input/output bit 6

10

DIO7

Digital Input/Output

Digital input/output bit 7

11

DIO8

Digital Input/Output

Digital input/output bit 8

12

DIO9

Digital Input/Output

Digital input/output bit 9 (MSB)

13

OVR

Digital Output

Overrange output (tri-state)

14

DGND

Ground

Negative Digital Supply

15

CLK

Analogue Input

Clock input

16

OEB

Digital Input

Output enable bar ≠ low to enable DIO[9:0] and OVR

17

WR

Digital Input

Write strobe

18

REFSENSE

Analogue Input

VREF mode control

19

CLAMP

Digital Input

Clamp control ≠ high to enable clamp amplifier

20

CLAMPIN

Analogue Input

Clamp reference input

21

REFTS

Analogue Input/Output

Top reference sense

22

REFTF

Analogue Input/Output

Top reference force

23

MODE

Analogue Input

Input mode select

24

REFBF

Analogue Input/Output

Bottom reference force

25

REFBS

Analogue Input/Output

Bottom reference sense

26

VREF

Analogue Input/Output

Reference voltage

27

AIN

Analogue Input

Analog Input

28

AVDD

Supply

Positive Analogue Supply

Production Data

WM2331

PD Rev 1.5 July 2001

3

ABSOLUTE MAXIMUM RATINGS

Absolute Maximum Ratings are stress ratings only. Permanent damage to the device may be caused by continuously operating at

or beyond these limits. Device functional operating limits and guaranteed performance specifications are given under Electrical

Characteristics at the test conditions specified.

ESD Sensitive Device. This device is manufactured on a CMOS process. It is therefore generically susceptible

to damage from excessive static voltages. Proper ESD precautions must be taken during handling and storage

of this device.

As per JEDEC specifications A112 and A113, this product requires specific storage conditions prior to surface mount assembly. It

has been classified as having a Moisture Sensitivity Level of 2 and as such will be supplied in vacuum-sealed moisture barrier

bags.

CONDITION

MIN

MAX

Digital supply voltage, DVDD to DGND

-0.3V

+6.5V

Analogue supply voltage, AVDD to AGND

-0.3V

+6.5V

Supply voltage difference, AVDD to DVDD

-6.5V

+6.5V

Ground difference, AGND to DGND

-0.3V

+0.3V

Voltage range digital inputs (DIO[9:0], WR, CLAMP, OEB)

DGND - 0.3V

DVDD + 0.3V

Voltage range analogue inputs (REFTS, REFBS, REFTF, REFBF, AIN,

VREF, REFSENSE, CLK, MODE)

AGND - 0.3V

AVDD + 0.3V

WM2331CDT

0∞C

+70∞C

Operating temperature range, T

A

WM2331IDT

-40

∞

C

+85

∞

C

Storage temperature

-65

∞

C

+150

∞

C

Lead temperature (1.6mm from package body for 10 seconds)

+300

∞

C

RECOMMENDED OPERATING CONDITIONS

PARAMETER

SYMBOL

TEST CONDITIONS

MIN

NOM

MAX

UNIT

Digital supply range

DVDD

3.0

3.0

5.5

V

Analogue supply range

AVDD

3.0

3.0

5.5

V

Ground

DGND,AGND

0

V

Clock frequency

f

CLK

5

30

MHz

Clock duty cycle

45

50

55

%

WM2331C

0

70

∞

C

Operating Free Air Temperature

T

A

WM2331I

-40

85

∞

C

WM2331

Production Data

PD Rev 1.5 July 2001

4

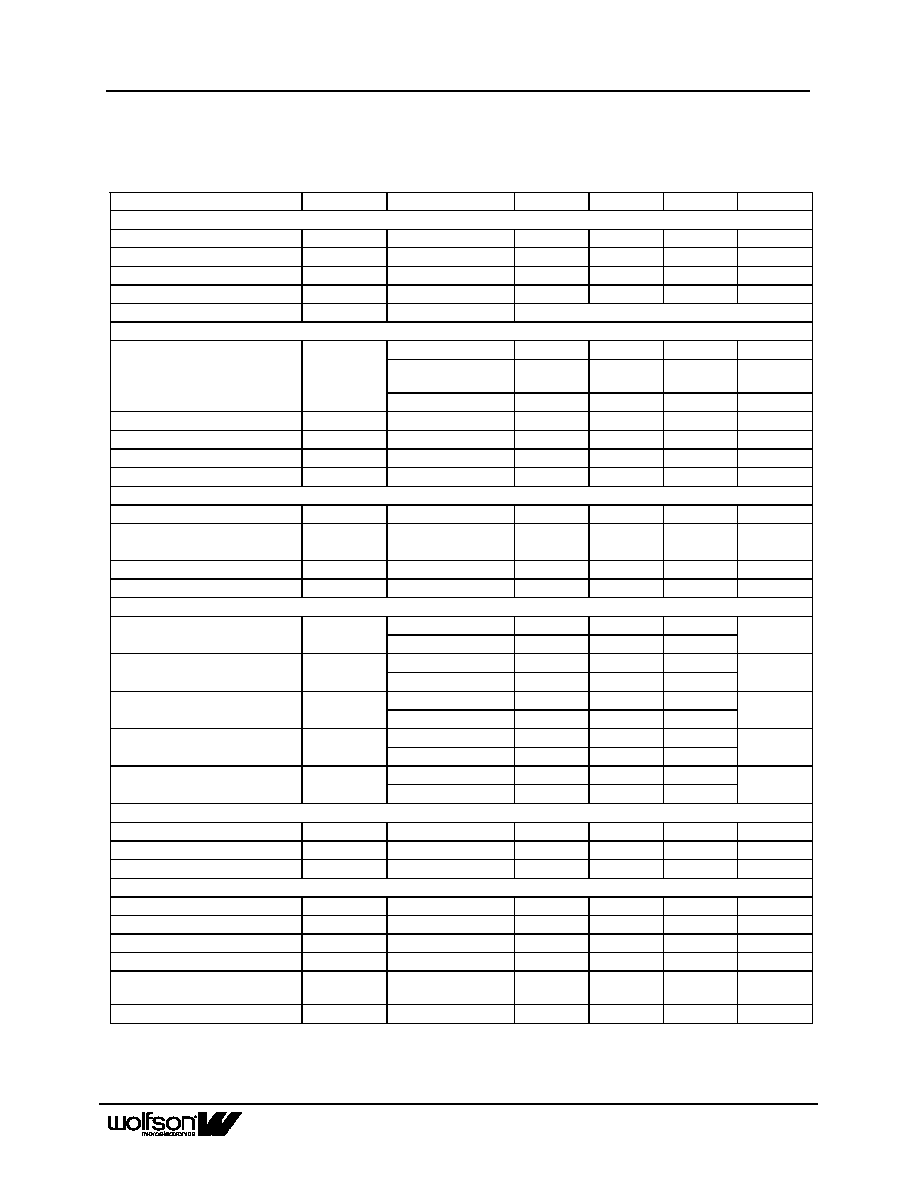

ELECTRICAL CHARACTERISTICS

Test Conditions:

AVDD = DVDD = 3.0V, f

CLK

= 30MHz, 50% duty cycle, MODE = AVDD, REFTS = 2.5V, REFBS = 0.5V, PGA gain = 1.0,

T

A

= T

MIN

to T

MAX

, unless otherwise stated.

PARAMETER

SYMBOL

TEST CONDITIONS

MIN

TYP

MAX

UNIT

DC Accuracy

Integral nonlinearity

INL

±

1.0

±

2.0

LSB

Differential nonlinearity

DNL

±

0.3

±

1.0

LSB

Offset error

0.4

2.0

% of FS

Gain error

1.4

3.5

% of FS

Missing codes

No missing codes guaranteed

Analogue Input Signal to AIN pin

MODE = AGND

REFBS

REFTS

MODE = AVDD / 2,

V

CMCS

fixed

V

CMCS

-

VREF/2

V

CMCS

+

VREF/2

V

Input signal range for unity PGA

gain (see Note 1)

MODE = AVDD

REFBS

REFTS

AIN voltage limits

AGND

AVDD

V

Switched input capacitance

1.2

pF

Analogue input bandwidth

-3dB amplitude

150

MHz

DC leakage current

±

Full-scale input

±

100

µ

A

Conversion Characteristics

Conversion frequency

f

CLK

5

30

MHz

Pipeline delay

3

cycles of

CLK

Aperture delay

t

A

4.0

ns

Aperture jitter

2.0

ps rms

Dynamic Performance

f

IN

= 3.5MHz

8.2

9.0

Effective number of bits

ENOB

f

IN

= 15MHz

7.7

bits

f

IN

= 3.5MHz

55

60

Spurious free dynamic range

SFDR

f

IN

= 15MHz

48

dB

f

IN

= 3.5MHz

-58

-54.7

Total harmonic distortion

THD

f

IN

= 15MHz

-47

dB

f

IN

= 3.5MHz

51.2

56

Signal to noise ratio

SNR

f

IN

= 15MHz

53

dB

f

IN

= 3.5MHz

51.1

56

Signal to noise and distortion

ratio

SNDR

f

IN

= 15MHz

48

dB

PGA

Gain range (linear scale)

0.5

4

V/V

Gain step size (linear scale)

0.5

V/V

Gain error from nominal

3

%

Clamp

Clamp DAC resolution

10

bits

Clamp DAC output voltage

REFBF

REFTF

V

Clamp DAC DNL

-1

1

LSB

Clamp DAC DNL

±1

LSB

External clamp reference on

CLAMPIN

0.1

AVDD - 0.1

V

Clamp output voltage error

-40

40

mV

Production Data

WM2331

PD Rev 1.5 July 2001

5

Test Conditions:

AVDD = DVDD = 3.0V, f

CLK

= 30MHz, 50% duty cycle, MODE = AVDD, REFTS = 2.5V, REFBS = 0.5V, PGA gain = 1.0,

T

A

= T

MIN

to T

MAX

, unless otherwise stated.

PARAMETER

SYMBOL

TEST CONDITIONS

MIN

TYP

MAX

UNIT

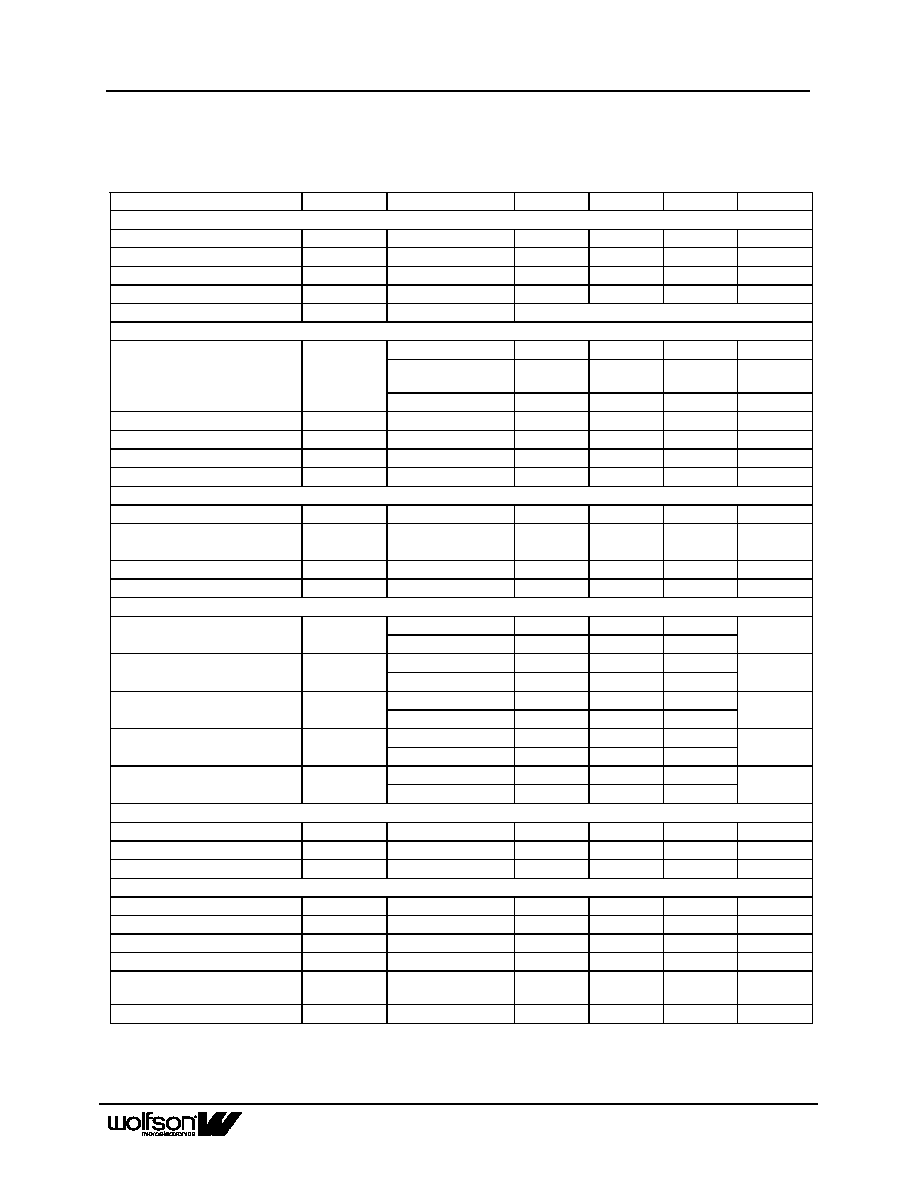

Analogue Reference Inputs / Outputs in Top/Bottom Mode (MODE=AVDD)

Bottom reference voltage

applied to REFBS

0

AVDD - 1

V

Top reference voltage applied to

REFTS

1

AVDD

V

Differential reference input

(REFTS ≠ REFBS)

V

TB

1

2

V

Reference input common mode

(REFTS + REFBS) / 2

V

CMTB

0.5

AVDD - 0.5

V

Switched input capacitance on

REFBS

0.6

pF

Switched input capacitance on

REFTS

0.6

pF

REFBF output voltage

(AVDD -

V

TB

)/2

V

REFTF output voltage

(AVDD +

V

TB

)/2

V

Analogue Reference Inputs / Outputs in Centre-Span Mode (MODE=AVDD/2)

Reference voltage derived or

applied to VREF

1

2

V

REFBF output voltage

(AVDD -

VREF)/2

V

REFTF output voltage

(AVDD +

VREF)/2

V

Non-AIN side of differential input

applied to REFTS and REFBS

V

CMCS

(Note 2)

0.5

AVDD - 0.5

V

Analogue Reference Inputs / Outputs in Full External Reference Mode (MODE=AGND) (Note 3)

Differential reference voltage

applied (REFTF ≠ REFBF)

1

2

V

AVDD = 3.0V

1.3

1.5

1.7

V

Reference input common mode

(REFTF + REFBF) / 2

AVDD = 5.0V

2.0

2.5

3.0

V

Reference input resistance

680

VREF Input / Output specifications

Internal 1V reference to VREF

REFSENSE = VREF

0.95

1.0

1.05

V

Internal 2V reference to VREF

REFSENSE = AGND

1.9

2.0

2.1

V

External reference applied to

VREF pin in centre-span mode

REFSENSE = AVDD,

MODE = AVDD / 2

1

2

V

Input impedance in centre-span

mode

REFSENSE = AVDD,

MODE = AVDD / 2

18

k