Document Outline

- WM8198

- (8 +8)Bit Output 16-bit CIS/CCD AFE/Digitiser

- DESCRIPTION

- FEATURES

- APPLICATIONS

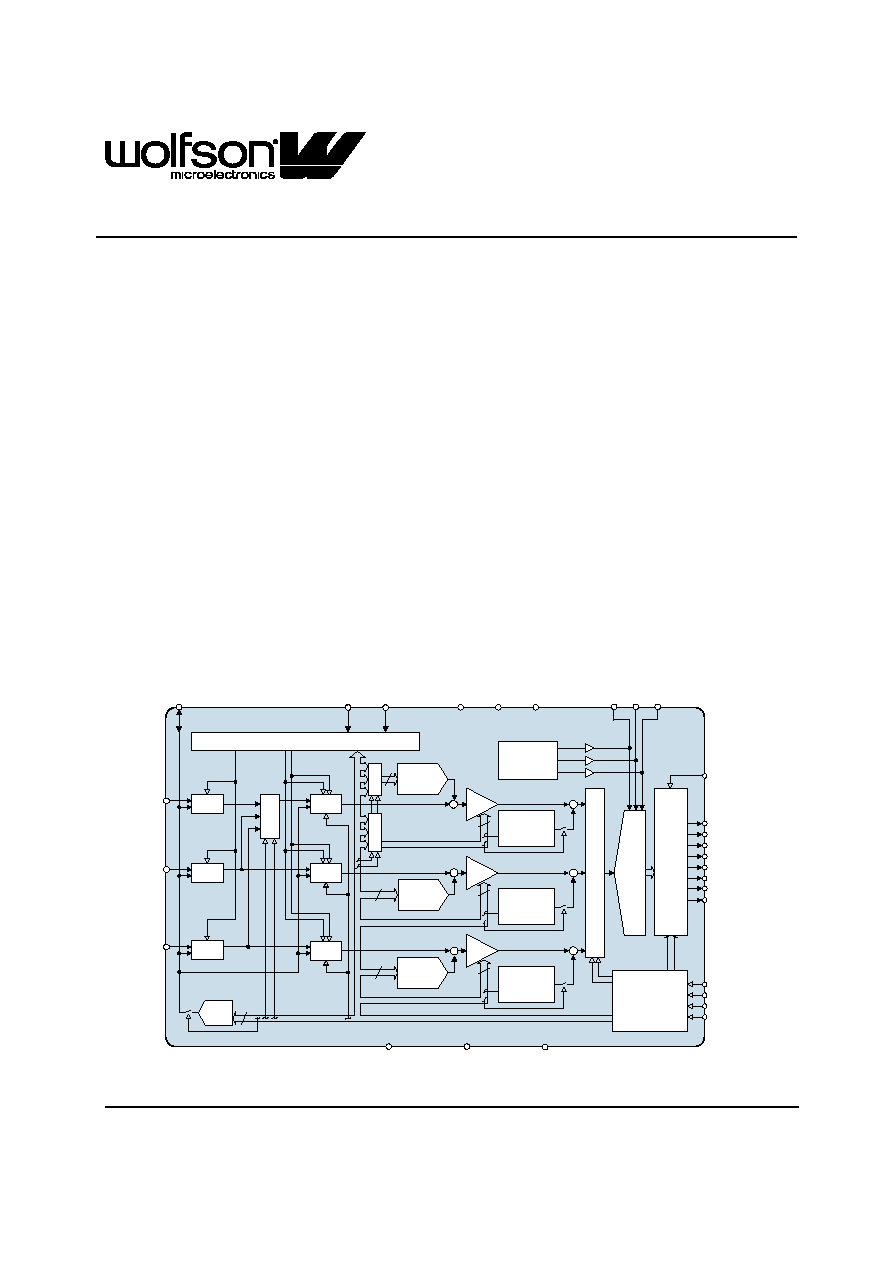

- BLOCK DIAGRAM

- PIN CONFIGURATION

- ORDERING INFORMATION

- PIN DESCRIPTION

- ABSOLUTE MAXIMUM RATINGS

- RECOMMENDED OPERATING CONDITIONS

- ELECTRICAL CHARACTERISTICS

- INPUT VIDEO SAMPLING

- OUTPUT DATA TIMING

- SERIAL INTERFACE

- DEVICE DESCRIPTION

- INTRODUCTION

- INPUT SAMPLING

- RESET LEVEL CLAMPING (RLC)

- CDS/NON-CDS PROCESSING

- OFFSET ADJUST AND PROGRAMMABLE GAIN

- ADC INPUT BLACK LEVEL ADJUST

- OVERALL SIGNAL FLOW SUMMARY

- CALCULATING OUTPUT FORANY GIVEN INPUT

- OUTPUT FORMATS

- CONTROL INTERFACE

- TIMING REQUIREMENTS

- PROGRAMMABLE VSMP DETECT CIRCUIT

- REFERENCES

- POWER SUPPLY

- POWER MANAGEMENT

- LINE-BY-LINE OPERATION

- OPERATING MODES

- DEVICE CONFIGURATION

- REGISTER MAP

- REGISTER MAP DESCRIPTION

- RECOMMENDED EXTERNAL COMPONENTS

- PACKAGE DIMENSIONS

- IMPORTANT NOTICE

WM8198

(8 + 8) Bit Output 16-bit CIS/CCD AFE/Digitiser

WOLFSON MICROELECTRONICS plc

w :: www.wolfsonmicro.com

Production Data, November 2002, Rev 3.0

Copyright

2002 Wolfson Microelectronics plc

DESCRIPTION

The WM8198 is a 16-bit analogue front end/digitiser IC

which processes and digitises the analogue output signals

from CCD sensors or Contact Image Sensors (CIS) at pixel

sample rates of up to 6MSPS.

The device includes three analogue signal processing

channels each of which contains Reset Level Clamping,

Correlated Double Sampling and Programmable Gain and

Offset adjust functions. Three multiplexers allow single

channel processing. The output from each of these

channels is time multiplexed into a single high-speed 16-bit

Analogue to Digital Converter. The digital output data is

available in 8 or 4-bit wide multiplexed format.

An internal 4-bit DAC is supplied for internal reference level

generation. This may be used during CDS to reference CIS

signals or during Reset Level Clamping to clamp CCD

signals. An external reference level may also be supplied.

ADC references are generated internally, ensuring optimum

performance from the device.

Using an analogue supply voltage of 5V and a digital

interface supply of either 5V or 3.3V, the WM8198 typically

only consumes 195mW when operating from a single

5V supply.

FEATURES

∑

16-bit ADC

∑

6MSPS conversion rate

∑

Low power ≠ 212mW typical

∑

5V single supply or 5V/3.3V dual supply operation

∑

Single or 3 channel operation

∑

Correlated double sampling

∑

Dual Range Programmable Gain Amplifier (9-bit resolution)

∑

Programmable offset adjust (8-bit resolution)

∑

Programmable clamp voltage

∑

8 or 4-bit wide multiplexed data output formats

∑

Internally generated voltage references

∑

28-pin SSOP package

∑

Serial control interface

APPLICATIONS

∑

Flatbed and sheetfeed scanners

∑

USB compatible scanners

∑

Multi-function peripherals

∑

High-performance CCD sensor interface

BLOCK DIAGRAM

RINP

DATA

I/O

PORT

SEN

VSMP

MCLK

VRLC/VBIAS

SDI

SCK

DVDD2

TIMING CONTROL

CL

RLC/ACYC

RLC

V

S

R

S

BINP

GINP

VRX

VRT

OEB

M

U

X

VRB

RLC

RLC

CDS

CDS

CDS

4

CONFIGURABLE

SERIAL

CONTROL

INTERFACE

ADC

AGND1

DGND

AVDD

DVDD1

OP[0]

OP[1]

OP[2]

OP[3]

OP[4]

OP[5]

OP[6]

OP[7]/SDO

AGND2

M

U

X

VREF/BIAS

M

U

X

R

G

B

M

U

X

R

G

B

+

PGA

I/P SIGNAL

POLARITY

ADJUST

9

8

PGA

9

8

PGA

9

8

+

+

+

+

+

I/P SIGNAL

POLARITY

ADJUST

I/P SIGNAL

POLARITY

ADJUST

OFFSET

DAC

OFFSET

DAC

OFFSET

DAC

RLC

DAC

w

WM8198

WM8198

Production Data

w

PD Rev 3.0 November 2002

2

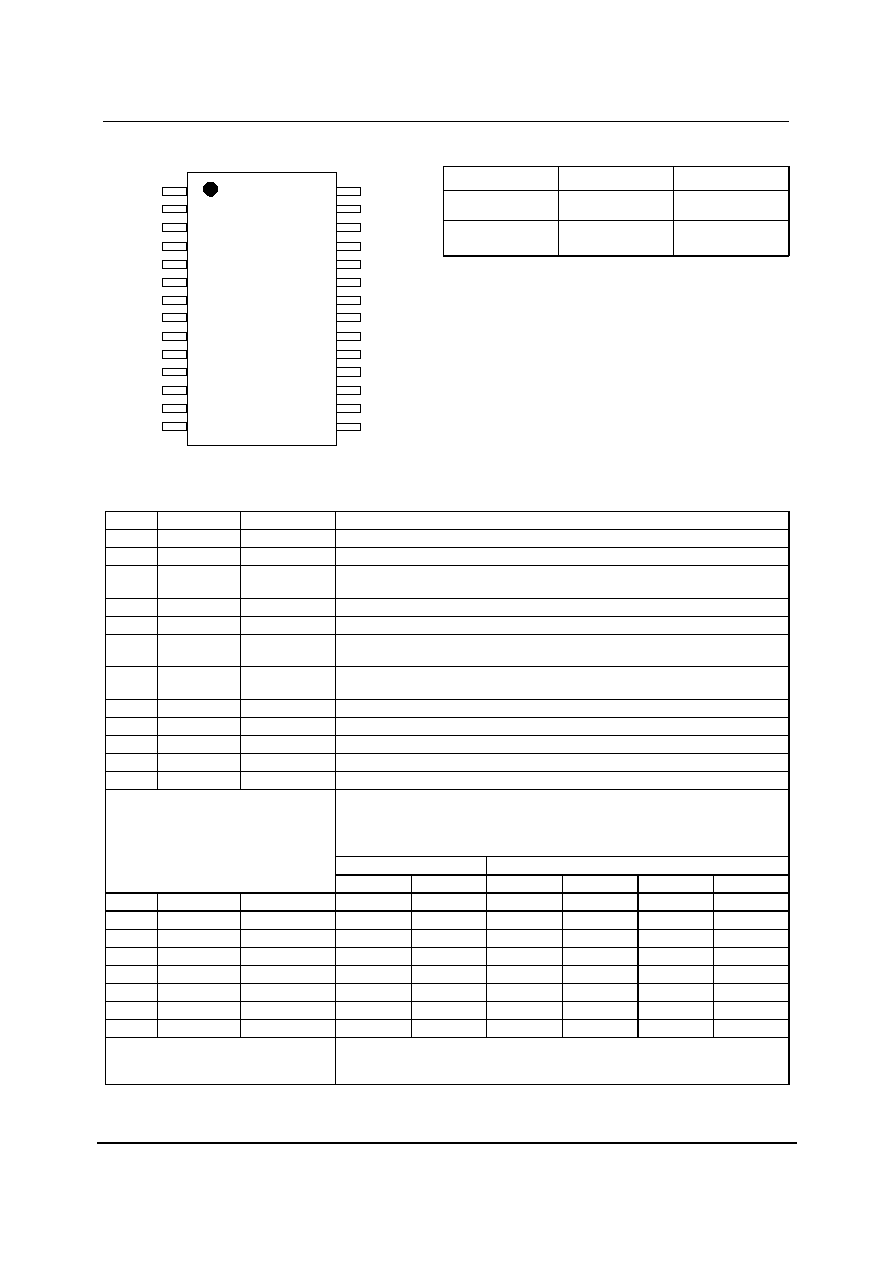

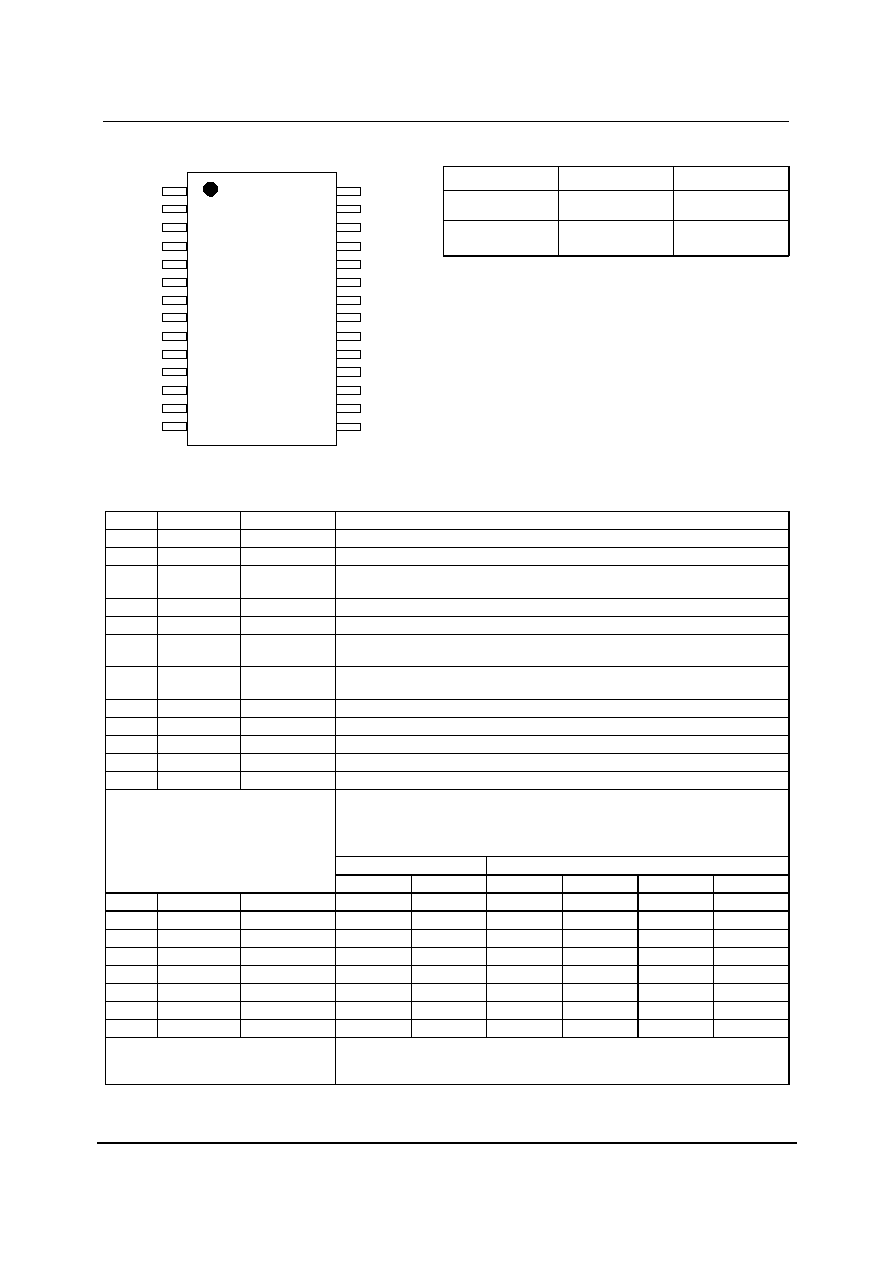

PIN CONFIGURATION

ORDERING INFORMATION

DEVICE

TEMP. RANGE

PACKAGE

WM8198CDS

0 to 70

o

C

28-pin SSOP

WM8198CDS/R

0 to 70

o

C

28-pin SSOP

(tape and reel)

SEN

OP[1]

OP[0]

SCK

SDI

DVDD2

OP[7]/SDO

OP[2]

OP[3]

OP[4]

OP[5]

OP[6]

GINP

AGND1

VRB

VRT

VRX

VRLC/VBIAS

BINP

AVDD

DGND

AGND2

DVDD1

OEB

VSMP

RLC/ACYC

MCLK

RINP

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

Note:

Reel quantity = 2,000

PIN DESCRIPTION

PIN

NAME

TYPE

DESCRIPTION

1

RINP

Analogue input

Red channel input video.

2

AGND2

Supply

Analogue ground (0V).

3

DVDD1

Supply

Digital supply (5V) for logic and clock generator. This must be operated at the same

potential as AVDD.

4

OEB

Digital input

Output Hi-Z control, all digital outputs disabled when OEB = 1.

5

VSMP

Digital input

Video sample synchronisation pulse.

6

RLC/ACYC

Digital input

RLC (active high) selects reset level clamp on a pixel-by-pixel basis ≠ tie high if

used on every pixel. ACYC autocycles between R, G, B inputs.

7

MCLK

Digital input

Master clock. This clock is applied at N times the input pixel rate (N = 2, 3, 6, 8 or

any multiple of 2 thereafter depending on input sample mode).

8

DGND

Supply

Digital ground (0V).

9

SEN

Digital input

Enables the serial interface when high.

10

DVDD2

Supply

Digital supply (5V/3.3V), all digital I/O pins.

11

SDI

Digital input

Serial data input.

12

SCK

Digital input

Serial clock.

Digital multiplexed output data bus.

ADC output data (d15:d0) is available in two multiplexed formats as shown, under

the control of register MUXOP [1:0]

See `Output Formats' description in Device Description section for further details.

8+8-bit

4+4+4+4-bit

A

B

A

B

C

D

13

OP[0]

Digital output

d8

d0

14

OP[1]

Digital output

d9

d1

15

OP[2]

Digital output

d10

d2

16

OP[3]

Digital output

d11

d3

17

OP[4]

Digital output

d12

d4

d12

d8

d4

d0

18

OP[5]

Digital output

d13

d5

d13

d9

d5

d1

19

OP[6]

Digital output

d14

d6

d14

d10

d6

d2

20

OP[7]

Digital output

d15

d7

d15

d11

d7

d3

Alternatively, pin OP[7]/SDO may be used to output register read-back data when

OEB = 0 and SEN has been pulsed high. See Serial Interface description in Device

Description section for further details.

WM8198

Production Data

w

PD Rev 3.0 November 2002

3

PIN

NAME

TYPE

DESCRIPTION

21

AVDD

Supply

Analogue supply (5V). This must be operated at the same potential as DVDD1.

22

AGND1

Supply

Analogue ground (0V).

23

VRB

Analogue output

Lower reference voltage.

This pin must be connected to AGND via a decoupling capacitor.

24

VRT

Analogue output

Upper reference voltage.

This pin must be connected to AGND via a decoupling capacitor.

25

VRX

Analogue output

Input return bias voltage.

This pin must be connected to AGND via a decoupling capacitor.

26

VRLC/VBIAS

Analogue I/O

Selectable analogue output voltage for RLC or single-ended bias reference.

This pin would typically be connected to AGND via a decoupling capacitor.

VRLC can be externally driven if programmed Hi-Z.

27

BINP

Analogue input

Blue channel input video.

28

GINP

Analogue input

Green channel input video.

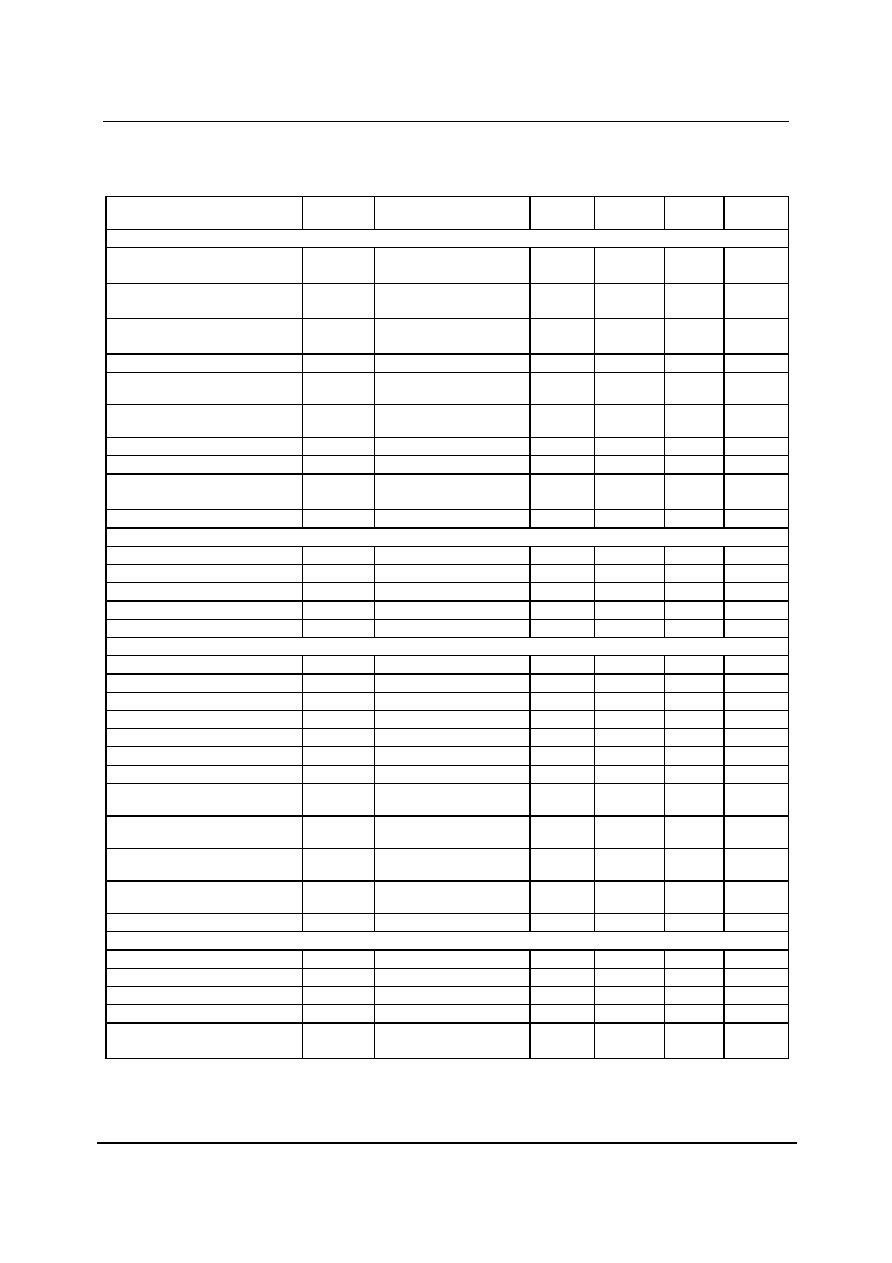

ABSOLUTE MAXIMUM RATINGS

Absolute Maximum Ratings are stress ratings only. Permanent damage to the device may be caused by continuously operating at

or beyond these limits. Device functional operating limits and guaranteed performance specifications are given under Electrical

Characteristics at the test conditions specified.

ESD Sensitive Device. This device is manufactured on a CMOS process. It is therefore generically susceptible

to damage from excessive static voltages. Proper ESD precautions must be taken during handling and storage

of this device.

The WM8198 has been classified as MSL1, which has an unlimited floor life at <30

o

C / 85% Relative Humidity and therefore will

not be supplied in moisture barrier bags.

CONDITION

MIN

MAX

Analogue supply voltage: AVDD

GND - 0.3V

GND + 7V

Digital supply voltages: DVDD1

-

2

GND - 0.3V

GND + 7V

Digital ground: DGND

GND - 0.3V

GND + 0.3V

Analogue grounds: AGND1

-

2

GND - 0.3V

GND + 0.3V

Digital inputs, digital outputs and digital I/O pins

GND - 0.3V

DVDD2 + 0.3V

Analogue inputs (RINP, GINP, BINP)

GND - 0.3V

AVDD + 0.3V

Other pins

GND - 0.3V

AVDD + 0.3V

Operating temperature range: T

A

0

∞

C

+70

∞

C

Storage prior to soldering

30

∞

C max / 85% RH max

Storage temperature after soldering

-65

∞

C

+150

∞

C

Package body temperature (soldering, 10 seconds)

+260

∞

C

Package body temperature (soldering, 2 minutes)

+183

∞

C

Notes:

1.

GND denotes the voltage of any ground pin.

2.

AGND1, AGND2 and DGND pins are intended to be operated at the same potential. Differential voltages

between these pins will degrade performance.

RECOMMENDED OPERATING CONDITIONS

CONDITION

SYMBOL

MIN

TYP

MAX

UNITS

Operating temperature range

T

A

0

70

∞

C

Analogue supply voltage

AVDD

4.75

5.0

5.25

V

Digital core supply voltage

DVDD1

4.75

5.0

5.25

V

5V I/O

DVDD2

4.75

5.0

5.25

V

Digital I/O supply voltage

3.3V I/O

DVDD2

2.97

3.3

3.63

V

WM8198

Production Data

w

PD Rev 3.0 November 2002

4

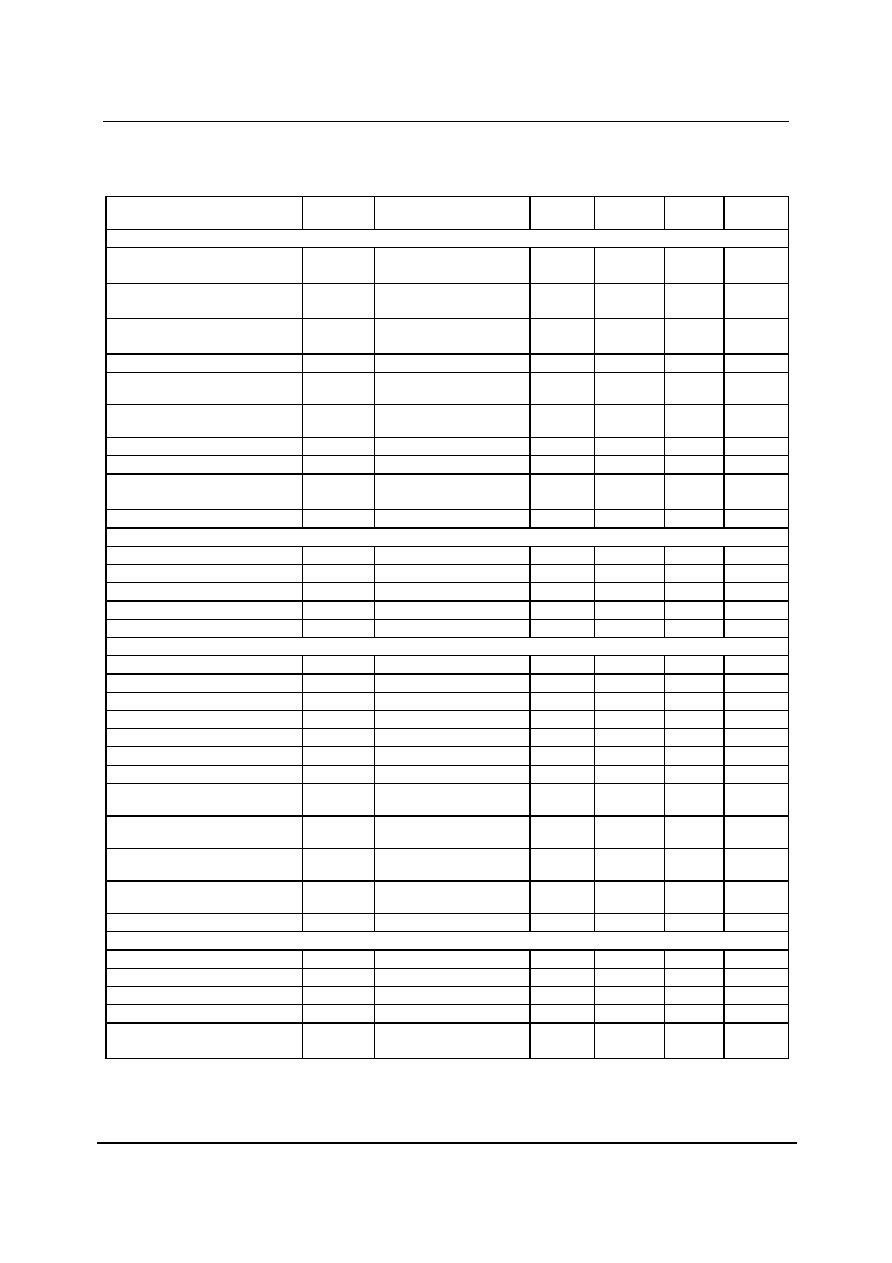

ELECTRICAL CHARACTERISTICS

Test Conditions

AVDD = DVDD1 = 5.0, DVDD2 = 3.3, AGND = DGND = 0V, T

A

= 25

∞

C, MCLK = 12MHz unless otherwise stated.

PARAMETER

SYMBOL

TEST

CONDITIONS

MIN

TYP

MAX

UNIT

Overall System Specification (including 16-bit ADC, PGA, Offset and CDS functions)

Conversion Rate

HIGHSPEED =0,

HIGHSPEED= 1, MCLK = 24MHz

6

12

MSPS

MSPS

Full-scale input voltage range,

PGAMODE=0. (see Note 1)

Max Gain

Min Gain

0.4

4.08

Vp-p

Vp-p

Full-scale input voltage range,

PGAMODE=1. (see Note 1)

Max Gain

Min Gain

0.6

3

Vp-p

Vp-p

Input signal limits (see Note 2)

V

IN

0

AVDD

V

Full-scale transition error

Gain = 0dB;

PGA[8:0] = 96(hex)

20

mV

Zero-scale transition error

Gain = 0dB;

PGA[8:0] = 96(hex)

20

mV

Differential non-linearity

DNL

1.25

LSB

Integral non-linearity

INL

20

LSB

Total output noise

Min Gain

Max Gain

3.9

11

LSB rms

LSB rms

Channel to channel gain matching

1

%

References

Upper reference voltage

VRT

2.85

V

Lower reference voltage

VRB

1.35

V

Input return bias voltage

VRX

1.65

V

Diff. reference voltage (VRT-VRB)

V

RTB

1.4

1.5

1.6

V

Output resistance VRT, VRB, VRX

1

VRLC/Reset-Level Clamp (RLC)

RLC switching impedance

50

VRLC short-circuit current

2

mA

VRLC output resistance

2

VRLC Hi-Z leakage current

VRLC = 0 to AVDD

1

µ

A

RLCDAC resolution

4

bits

RLCDAC step size, RLCDAC = 0

V

RLCSTEP

AVDD = 5.0V

0.25

V/step

RLCDAC step size, RLCDAC = 1

V

RLCSTEP

0.17

V/step

RLCDAC output voltage at

code 0(hex), RLCDACRNG = 0

V

RLCBOT

AVDD = 5.0V

0.39

V

RLCDAC output voltage at

code 0(hex), RLCDACRNG = 1

V

RLCBOT

0.26

V

RLCDAC output voltage at

code F(hex) RLCDACRNG, = 0

V

RLCTOP

AVDD = 5.0V

4.14

V

RLCDAC output voltage at

code F(hex), RLCDACRNG = 1

V

RLCTOP

2.81

V

VRLC deviation

25

mV

Offset DAC, Monotonicity Guaranteed

Resolution

8

bits

Differential non-linearity

DNL

0.1

0.5

LSB

Integral non-linearity

INL

0.25

1

LSB

Step size

2.04

mV/step

Output voltage

Code 00(hex)

Code FF(hex)

-260

+260

mV

mV

Notes:

1.

Full-scale input voltage denotes the maximum amplitude of the input signal at the specified gain.

2.

Input signal limits are the limits within which the full-scale input voltage signal must lie.

WM8198

Production Data

w

PD Rev 3.0 November 2002

5

Test Conditions

AVDD = DVDD1 = 5.0, DVDD2 = 3.3, AGND = DGND = 0V, T

A

= 25

∞

C, MCLK = 12MHz unless otherwise stated.

PARAMETER

SYMBOL

TEST

CONDITIONS

MIN

TYP

MAX

UNIT

Programmable Gain Amplifier

Resolution (PGAMODE=0)

9

bits

Gain (PGAMODE=0)

0]

:

PGA[8

566

416

-

V/V

Max gain, eachchannel

(PGAMODE=0)

G

MAX

7.5

V/V

Min gain, eachchannel

(PGAMODE=0)

G

MIN

0.74

V/V

Gain error, eachchannel

(PGAMODE=0)

1

%

Resolution (PGAMODE=1)

9

bits

Gain (PGAMODE=1)

511

4

0]

:

PGA[8

1

◊

+

V/V

Max gain, eachchannel

(PGAMODE=1)

G

MAX

5

V/V

Min gain, eachchannel

(PGAMODE=1)

G

MIN

1

V/V

Gain error, eachchannel

(PGAMODE=1)

1

%

Analogue to Digital Converter

Resolution

16

bits

Speed

6

MSPS

Full-scale input range

(2*(VRT-VRB))

3

V

DIGITAL SPECIFICATIONS

Digital Inputs

Highlevel input voltage

V

IH

0.8

DVDD2

V

Low level input voltage

V

IL

0.2

DVDD2

V

Highlevel input current

I

IH

1

µ

A

Low level input current

I

IL

1

µ

A

Input capacitance

C

I

5

pF

Digital Outputs

Highlevel output voltage

V

OH

I

OH

= 1mA

DVDD2 - 0.5

V

Low level output voltage

V

OL

I

OL

= 1mA

0.5

V

Highimpedance output current

I

OZ

1

µ

A

Digital IO Pins

Applied high level input voltage

V

IH

0.8

DVDD2

V

Applied low level input voltage

V

IL

0.2

DVDD2

V

Highlevel output voltage

V

OH

I

OH

= 1mA

DVDD2 - 0.5

V

Low level output voltage

V

OL

I

OL

= 1mA

0.5

V

Low level input current

I

IL

1

µ

A

Highlevel input current

I

IH

1

µ

A

Input capacitance

C

I

5

pF

Highimpedance output current

I

OZ

1

µ

A