| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: X1243 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

©

Xicor, Inc. 1994, 1995, 1996 Patents Pending

9900-3003.1 4/1/99

1

Characteristics subject to change without notice

16K

2-Wire

TM

RTC

Real Time Clock/Calendar/Alarm with EEPROM

FEATURES

∑ 2 Alarms--Interrupt Output

--Settable on the Second, 10s of Seconds,

Minute, 10s of Minutes, Hour, Day, Month, or

Day of the Week

--Repeat alarm for time base generation

∑ 2 Wire Interface interoperable with I

2

C.

--400kHz data transfer rate

∑ Secondary Power Supply Input with internal

switch-over circuitry.

∑ Year 2000 Compliant

∑ 2K bytes of EEPROM

--64 Byte Page Write Mode

--3 bit Block Lock

∑ Low Power CMOS

--<1

µ

A Operating Current

--<3mA Active Current during Program

--<400

µ

A Active Current during Data Read

∑ Single Byte Write Capability

∑ Typical Nonvolatile Write Cycle Time: 5ms

∑ High Reliability

--100,000 Endurance Cycles

--Guaranteed Data Retention: 100 Years

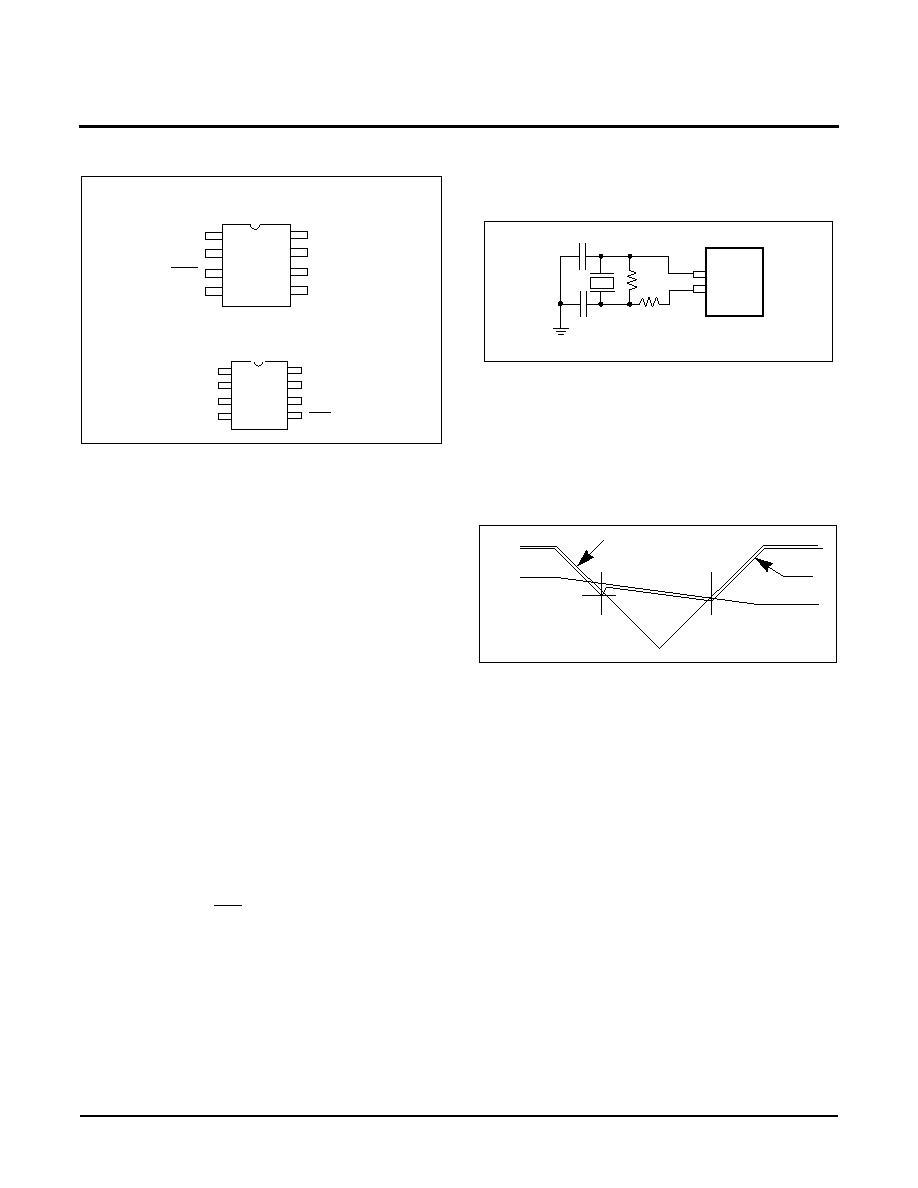

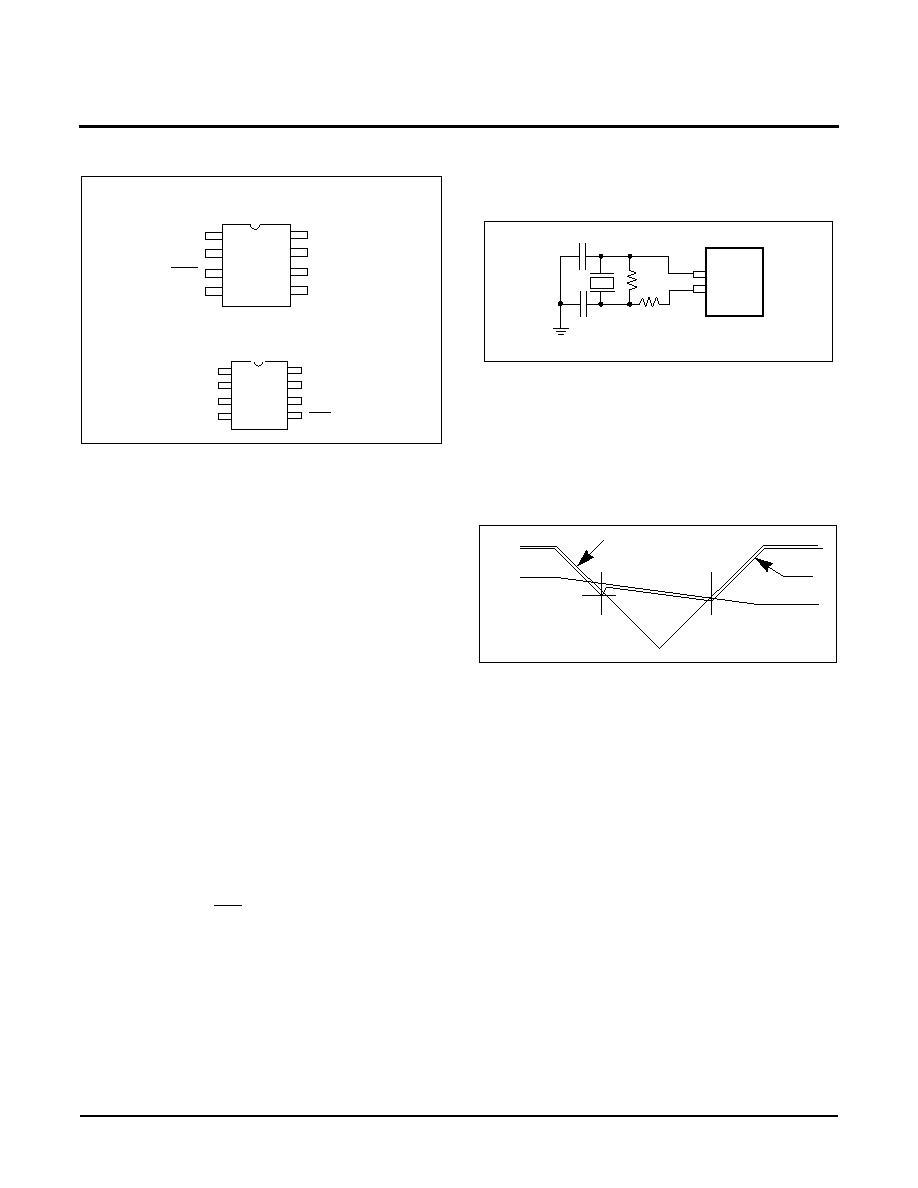

∑ Small Package Options

--8-Lead SOIC Package, 8L TSSOP Package

DESCRIPTION

The X1243 is a Real Time Clock with clock/calendar

circuits and two alarms. The dual port clock and alarm

registers allow the clock to operate, without loss of

accuracy, even during read and write operations.

The clock/calendar provides functionality that is con-

trollable and readable through a set of registers. The

clock, using a low cost 32.768kHz crystal input, accu-

rately tracks the time in seconds, minutes, hours, date,

day, month and years. It has leap year correction,

automatic adjustment for the year 2000 and months

with less than 31 days.

An alarm match of the RTC sets an interrupt flag and

activates an interrupt pin. An alternative alarm function

provides a pulsed interrupt for long time constant time-

bases.

The device offers a backup power input pin. This

Vback pin allows the device to be backed up by a non-

rechargeable battery. The RTC is fully operational

from 1.8 to 5.5 volts.

The X1243 provides a 2K byte EEPROM array, giving

a safe, secure memory for critical user and configura-

tion data. This memory is unaffected by complete fail-

ure of the main and backup supplies.

BLOCK DIAGRAM

X1

X2

Oscillator

Frequency

Timer

Logic

Divider

Calendar

8

32.768kHz

Control

Registers

1Hz

Time

Keeping

Registers

Alarm Regs

Compare

Mask

IRQ

Control

Decode

Logic

Alarm

(EEPROM)

(EEPROM)

(SRAM)

SCL

SDA

Serial

Interface

Decoder

Interrupt Enable

16K

EEPROM

Array

Register

Status

(SRAM)

Alarm

Alarm

X1243

X1243

2

PIN DESCRIPTIONS

Serial Clock (SCL)

The SCL input is used to clock all data into and out of

the device. The input buffer on this pin is always active

(not gated).

Serial Data (SDA)

SDA is a bidirectional pin used to transfer data into

and out of the device. It has an open drain output and

may be wire ORed with other open drain or open col-

lector outputs. The input buffer is always active (not

gated).

An open drain output requires the use of a pull-up

resistor. The output circuitry controls the fall time of

the output signal with the use of a slope controlled

pull-down. The circuit is designed for 400kHz 2-wire

interface speeds.

V

BACK

This input provides a backup supply voltage to the

device. V

BACK

supplies power to the device in the

event the V

CC

supply fails.

Interrupt Output-- IRQ

This is an interrupt signal output. This signal notifies a

host processor that alarm has occurred and requests

action. It is an open drain active LOW output.

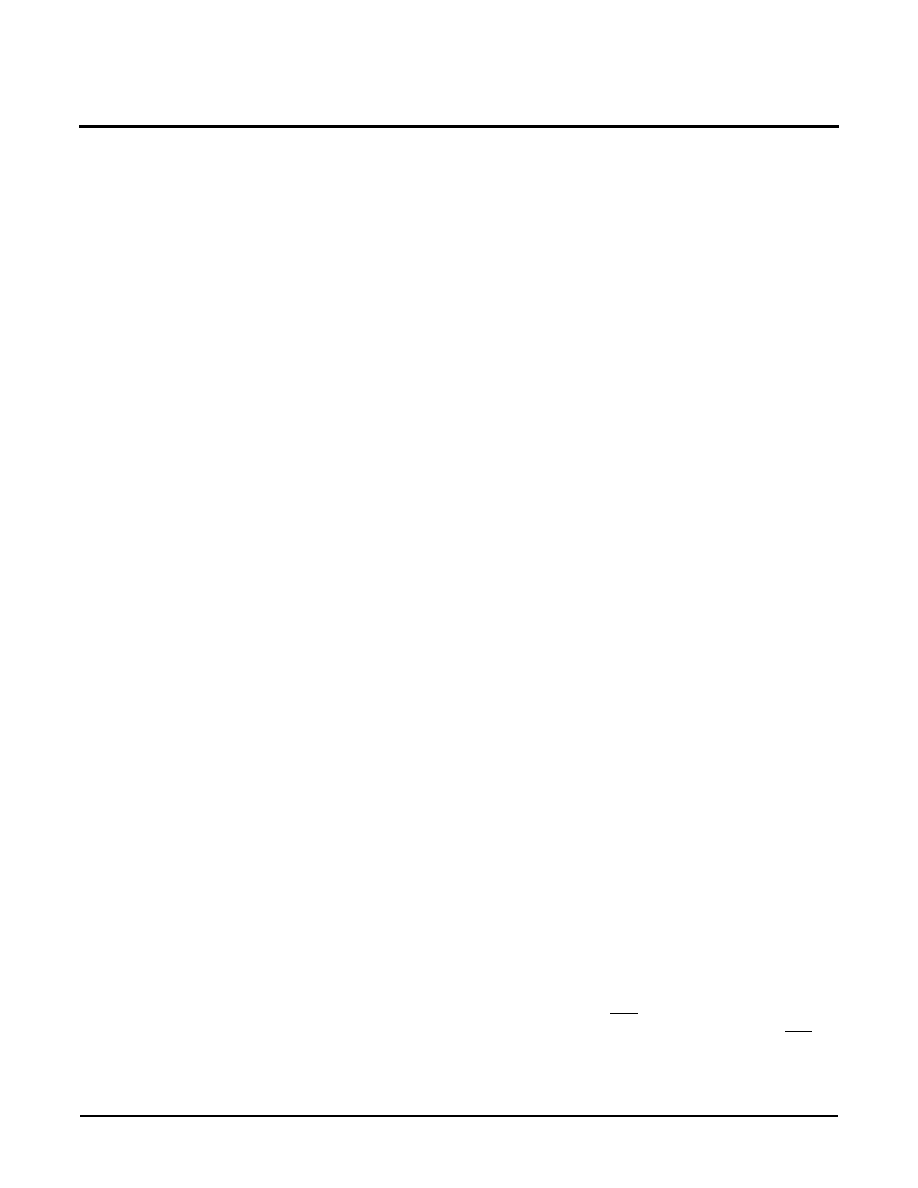

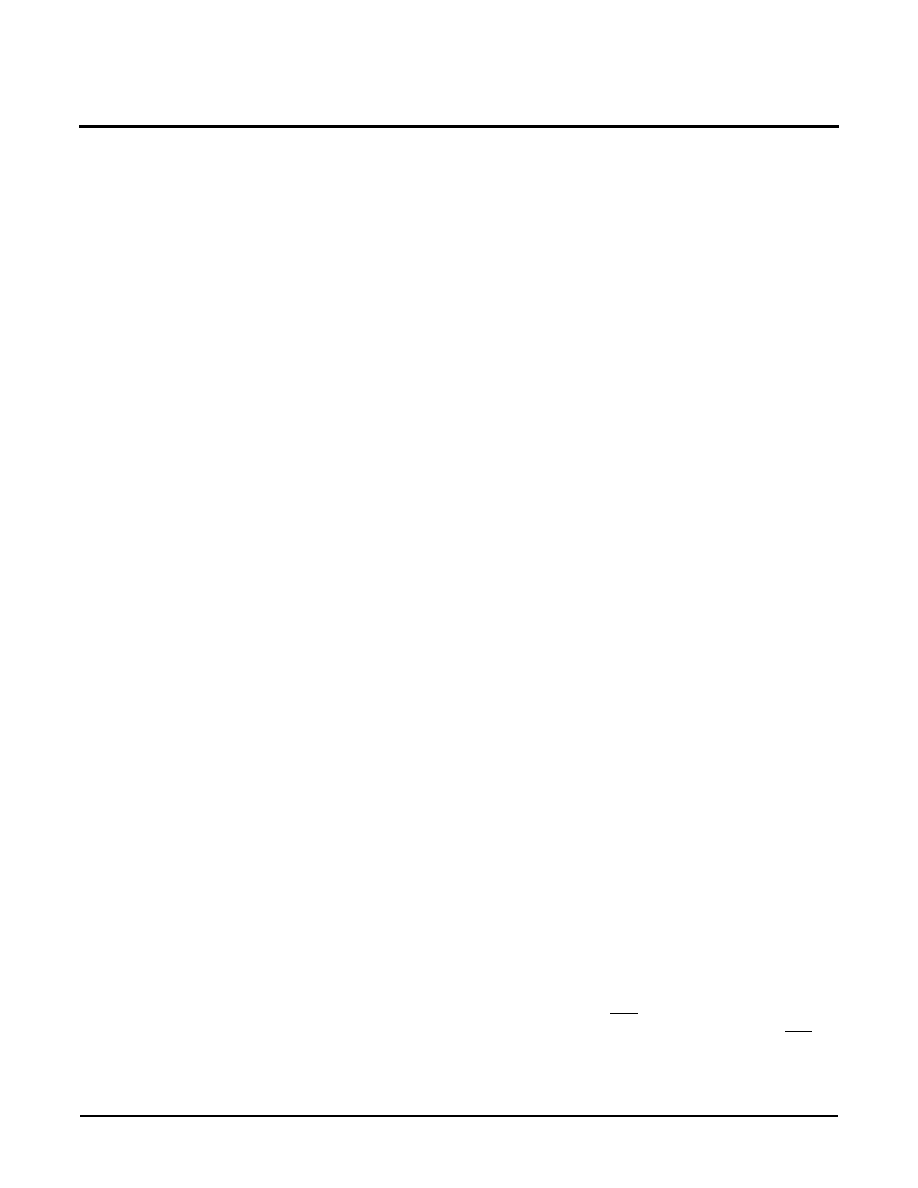

X1, X2

The X1 and X2 pins are the input and output, respec-

tively, of an inverting amplifier that can be configured

for use as an on-chip oscillator. A 32.768kHz quartz

crystal is used. Recommeded crystals are Sieko VT-200

or Epson C-002RX. The crystal supplies a timebase

for a clock/oscillator. The internal clock can be driven

by an external signal on X1, with X2 left unconnected.

Figure 1. Recommended Crystal connection

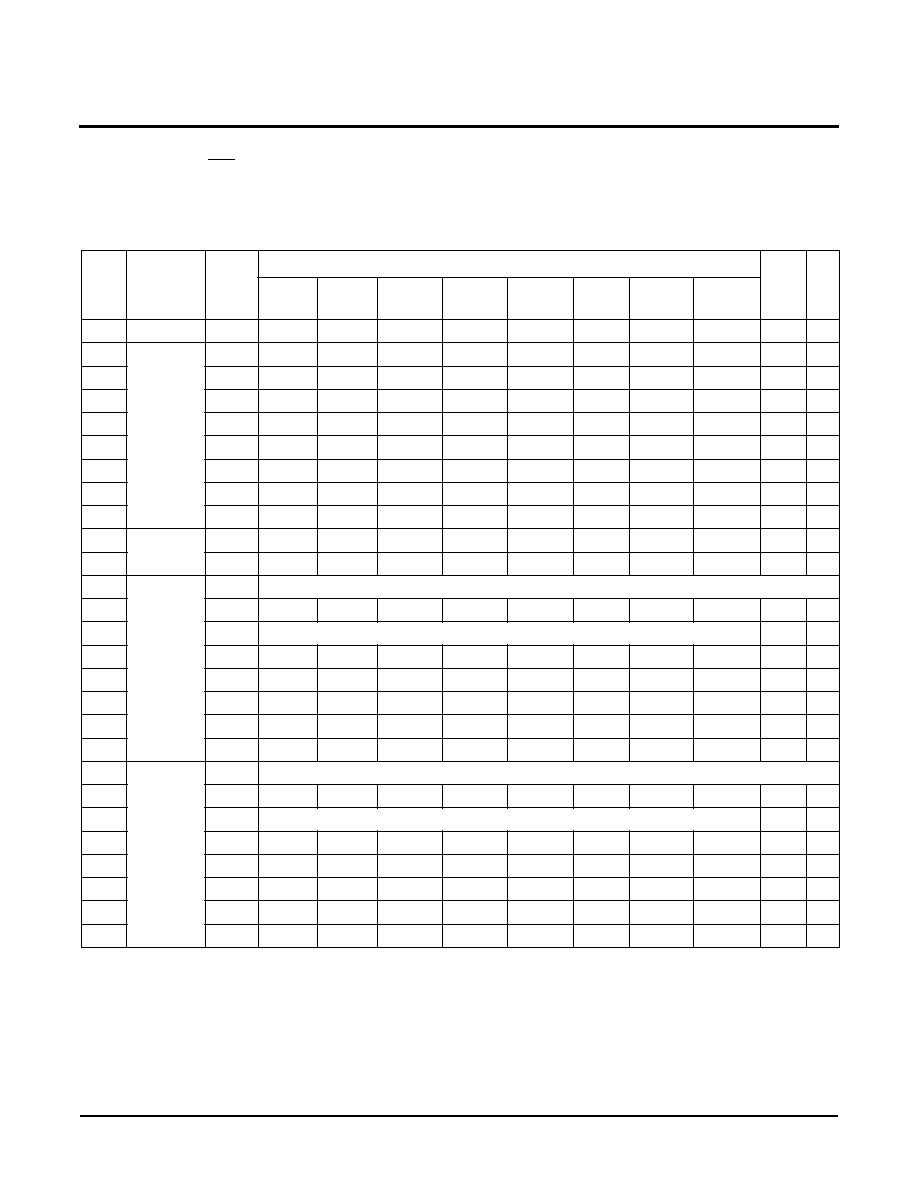

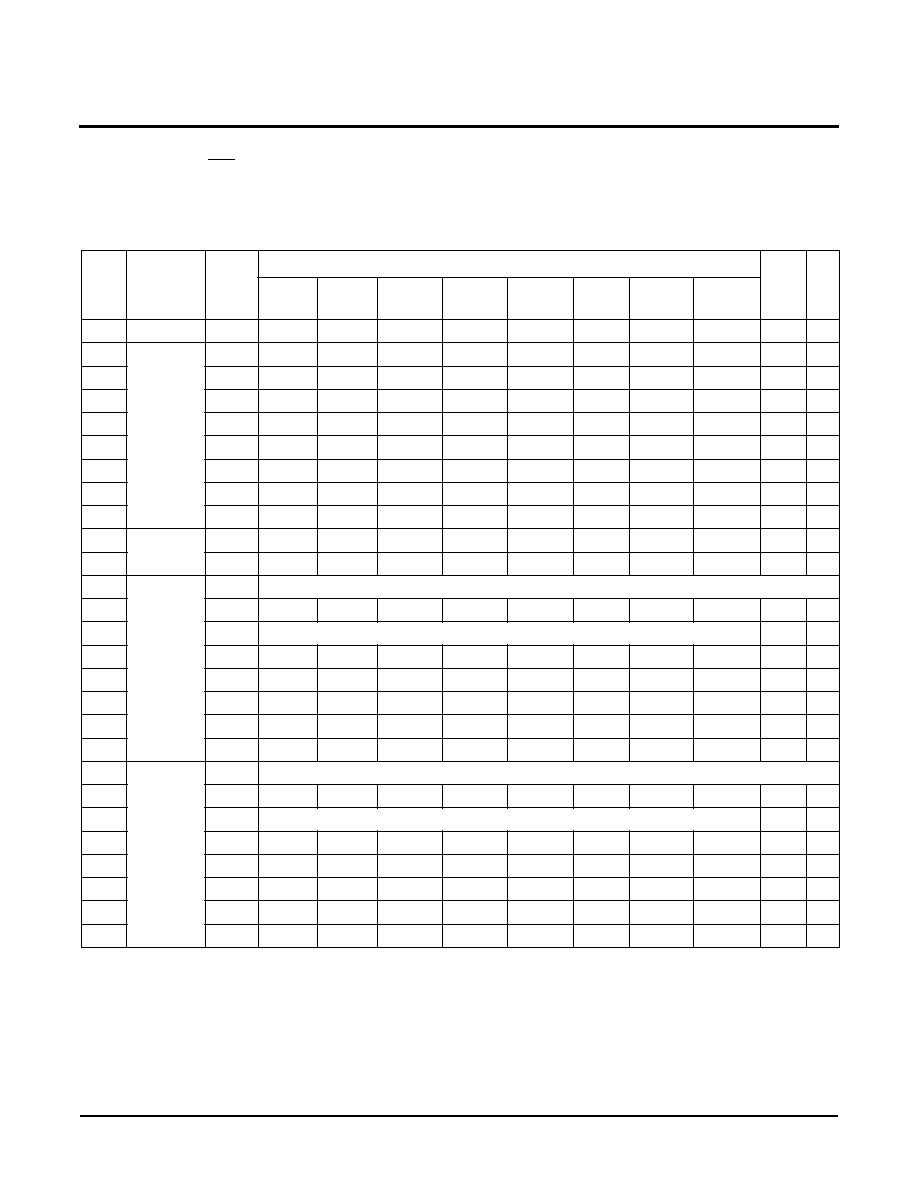

POWER CONTROL OPERATION

The Power control circuit accepts a V

CC

and a V

BACK

input. The power control circuit will switch to V

BACK

when V

CC

< V

BACK

- 0.2V. It will switch back to V

CC

when V

CC

exceeds V

BACK

.

Figure 2. Power Control

REAL TIME CLOCK OPERATION

The Real Time Clock (RTC) uses an external, 32.768KHz

quartz crystal to maintain an accurate internal repre-

sentation of the year, month, day, date, hour, minute,

and seconds. The RTC has leap-year correction and a

century byte. The clock will also correct for months hav-

ing fewer than 31 days and will have a bit that controls

24 hour or AM/PM format. When the X1243 powers up

after the loss of both V

CC

and V

BACK

, the clock will not

increment until at least one byte is written to the clock

register.

Reading the Real Time Clock

The RTC is read by initiating a Read command and

specifying the address corresponding to the register of

the Real Time Clock. The RTC Registers can then be

read in a Sequential Read Mode. Since the clock runs

continuously and a read takes a finite amount of time,

there is the possibility that the clock could change dur-

ing the course of a read operation. In this device, the

time is latched by the read command (falling edge of

X1243

X1

X2

V

Back

V

CC

IRQ

SCL

SDA

V

SS

1

2

3

4

7

8

6

5

8 pin TSSOP

X1243

X1

X2

V

Back

V

CC

IRQ

SCL

SDA

V

SS

1

2

3

4

7

8

6

5

8 pin SOIC

X1

X2

43pF

18pF

220K

10M

V

BACK

V

CC

= V

BACK

-0.2V

Internal

Voltage

V

CC

X1243

3

the clock on the ACK bit prior to RTC data output) into

a separate latch to avoid time changes during the read

operation. The clock continues to run. Alarms occuring

during a read are unaffected by the read operation.

Writing to the Real Time Clock

The time and date may be set by writing to the RTC

registers. To avoid changing the current time by an

uncompleted write operation, the current time value is

loaded into a seperate buffer at the falling edge of the

clock on the ACK bit before the RTC data input bytes,

the clock continues to run. The new serial input data

replaces the values in the buffer. This new RTC value

is loaded back into the RTC Register by a stop bit at

the end of a valid write sequence. An invalid write

operation aborts the time update procedure and the

contents of the buffer are discarded. After a valid write

operation the RTC will reflect the newly loaded data

beginning with the first "one second" clock cycle after

the stop bit. The RTC continues to update the time

while an RTC register write is in progress and the RTC

continues to run during any nonvolatile write sequences.

A single byte may be written to the RTC without affect-

ing the other bytes.

CLOCK/CONTROL REGISTERS (CCR)

The Control/Clock Registers are located in an area

logically separated from the array and are only acces-

sible following a slave byte of "1101111x" and reads or

writes to addresses [0000h:003Fh].

CCR access

The contents of the CCR can be modified by performing

a byte or a page write operation directly to any address in

the CCR. Prior to writing to the CCR (except the status

register), however, the WEL and RWEL bits must be

set using a two step process (See section "Writing to

the Clock/Control Registers.")

The CCR is divided into 5 sections. These are:

1. Alarm 0 (8 bytes)

2. Alarm 1 (8 bytes)

3. Control (2 bytes)

4. Real Time Clock (8 bytes)

5. Status (1 byte)

Sections 1) through 3) are nonvolatile and Sections 4)

and 5) are volatile. Each register is read and written

through buffers. The non-volatile portion (or the counter

portion of the RTC) is updated only if RWEL is set and

only after a valid write operation and stop bit. A sequen-

tial read or page write operation provides access to the

contents of only one section of the CCR per operation.

Access to another section requires a new operation.

Continued reads or writes, once reaching the end of a

section, will wrap around to the start of the section. A

read or page write can begin at any address in the CCR.

Section 5) is a volatile register. It is not necessary to set

the RWEL bit prior to writing the status register. Section 5)

supports a single byte read or write only. Continued reads

or writes from this section terminates the operation.

The state of the CCR can be read by performing a ran-

dom read at any address in the CCR at any time. This

returns the contents of that register location. Additional

registers are read by performing a sequential read.

The read instruction latches all Clock registers into a

buffer, so an update of the clock does not change the

time being read. A sequential read of the CCR will not

result in the output of data from the memory array. At

the end of a read, the master supplies a stop condition

to end the operation and free the bus. After a read of

the CCR, the address remains at the previous address

+1 so the user can execute a current address read of

the CCR and continue reading the next Register.

ALARM REGISTERS

There are two alarm registers whose contents mimic

the contents of the RTC register, but add enable bits

and exclude the 24 hour time selection bit. The enable

bits specify which registers to use in the comparison

between the Alarm and Real Time Registers. For

example:

--The user can set the X1242 to alarm every Wednes-

day at 8:00 AM by setting the EDWn, the EHRn and

EMNn enable bits to `0' and setting the DWAn,

HRAn and MNAn Alarm registers to 8:00 AM

Wednesday.

--A daily alarm for 9:30PM results when the EHRn

and EMNn enable bits are set to `0' and the HRAn

and MNAn registers set 9:30 PM.

--Setting the EMOn bit in combination with other

enable bits and a specific alarm time, the user can

establish an alarm that triggers at the same time

once a year.

When there is a match, an alarm flag is set. The occur-

ance of an alarm can be determined by polling the AL0

and AL1 bits, or by setting the AL0E and AL1E bits to `1'

and monitoring the IRQ output. The AL0E and AL1E

bits enable the circuit that triggers the output IRQ pin

when an alarm occurs. Writing a `0' to one of the bits

X1243

4

disables the output IRQ for that alarm condition, but the

alarm condition can still be checked by polling the

alarm flag.

The alarm enable bits are located in the MSB of the

particular register. When all enable bits are set to `0',

there are no alarms.

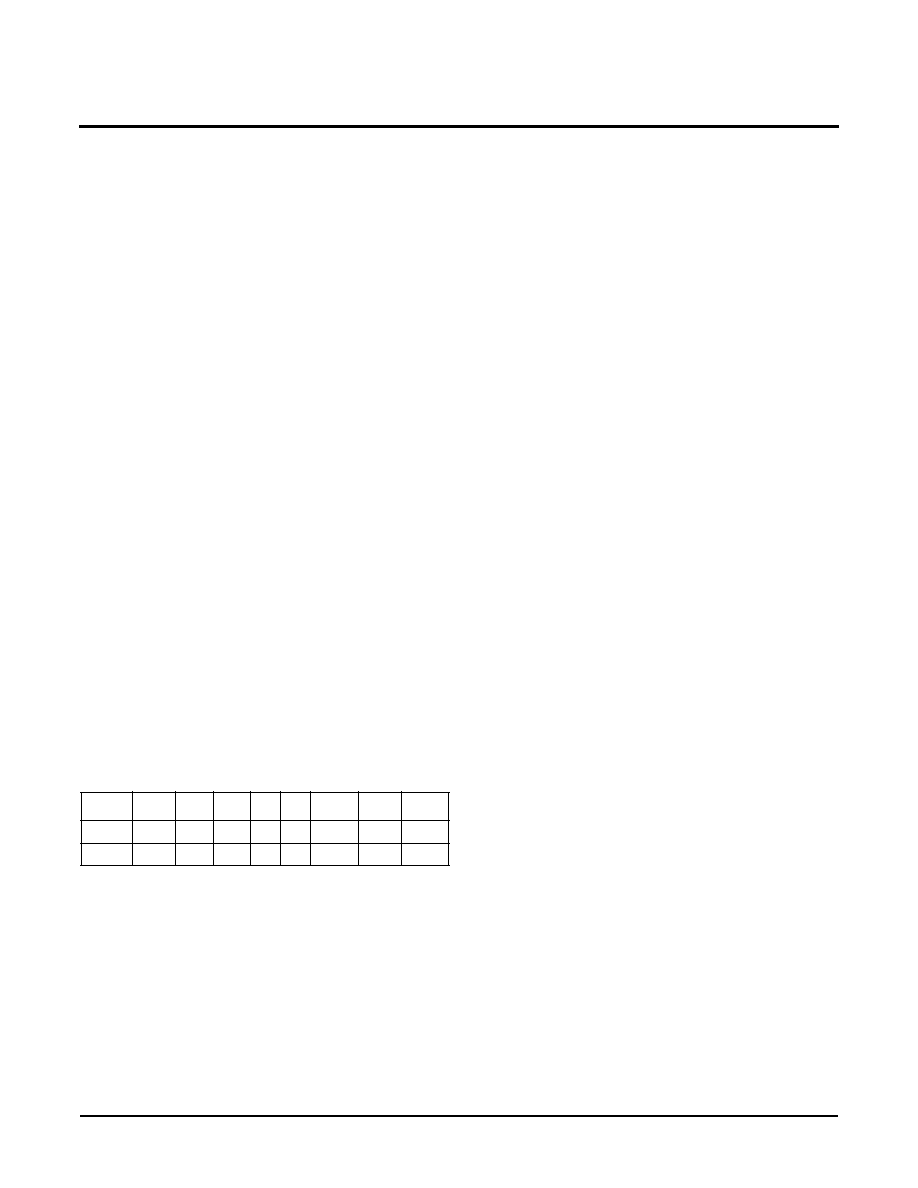

Table 1. Clock/Control Memory Map

Addr.

Type

Reg

Name

Bit

Range

Factroy

Settings

7

6

5

4

3

2

1

0

(optional)

003F

Status

SR

BAT

AL1

AL0

0

0

RWEL

WEL

RTCF

0037

RTC

(SRAM)

Y2K

0

0

Y2K21

Y2K20

Y2K13

0

0

Y2K10

19/20

0036

DW

0

0

0

0

0

DY2

DY1

DY0

0-6

0035

YR

Y23

Y22

Y21

Y20

Y13

Y12

Y11

Y10

0-99

0034

MO

0

0

0

G20

G13

G12

G11

G10

1-12

0033

DT

0

0

D21

D20

D13

D12

D11

D10

1-31

0032

HR

T24

0

H21

H20

H13

H12

H11

H10

0-23

0031

MN

0

M22

M21

M20

M13

M12

M11

M10

0-59

0030

SC

0

S22

S21

S20

S13

S12

S11

S10

0-59

0011

Control

(E2PROM)

INT

IM

AL1E

AL0E

0

0

0

0

0

00h

0010

BL

BP2

BP1

BP0

0

0

0

0

0

00h

000F

Alarm1

(E2PROM)

unused

000E

DWA1

EDW1

0

0

0

0

DY2

DY1

DY0

0-6

0h

000D

YRA1

Unused - Default = RTC Year value

000C

MOA1

EMO1

0

0

A1G20

A1G13

A1G12

A1G11

A1G10

1-12

0h

000B

DTA1

EDT1

0

A1D21

A1D20

A1D13

A1D12

A1D11

A1D10

1-31

0h

000A

HRA1

EHR1

0

A1H21

A1H20

A1H13

A1H12

A1H11

A1H10

0-23

0h

0009

MNA1

EMN1

A1M22

A1M21

A1M20

A1M13

A1M12

A1M11

A1M10

0-59

0h

0008

SCA1

ESC1

A1S22

A1S21

A1S20

A1S13

A1S12

A1S11

A1S10

0-59

0h

0007

Alarm0

(E2PROM)

unused

0006

DWA1

EDW0

0

0

0

0

DY2

DY1

DY0

0-6

0h

0005

YRA0

Unused - Default = RTC Year value

0004

MOA0

EMO0

0

0

A0G20

A0G13

A0G12

A0G11

A0G10

1-12

0h

0003

DTA0

EDT0

0

A0D21

A0D20

A0D13

A0D12

A0D11

A0D10

1-31

0h

0002

HRA0

EHR0

0

A0H21

A0H20

A0H13

A0H12

A0H11

A0H10

0-23

0h

0001

MNA0

EMN0

A0M22

A0M21

A0M20

A0M13

A0M12

A0M11

A0M10

0-59

0h

0000

SCA0

ESC0

A0S22

A0S21

A0S20

A0S13

A0S12

A0S11

A0S10

0-59

0h

REAL TIME CLOCK REGISTERS

Year 2000 (Y2K)

The X1243 has a century byte that "rolls over" from 19

to 20 when the years byte changes from 99 to 00. The

Y2K byte can contain only the values of 19 or 20.

Day of the Week Register (DW)

This register provides a Day of the Week status and

uses three bits DY2 to DY0 to represent the seven

days of the week. The counter advances in the cycle

0-1-2-3-4-5-6-0-1-2-... The assignment of a numerical

X1243

5

value to a specific day of the week is arbitrary and may

be decided by the system software designer. The Clock

Default values define 0=Sunday.

Clock/Calendar Registers (YR, MO, DT, HR, MN, SC)

These registers depict BCD representations of the time.

As such, SC (Seconds) and MN (Minutes) range from

00 to 59, HR (Hour) is 1 to 12 with an AM or PM indica-

tor (H21 bit) or 0 to 23 (with T24=1), DT (Date) is 1 to

31, MO (Month) is 1 to 12, YR (year) is 0 to 99.

24 Hour Time

If the T24 bit of the HR register is 1, the RTC will use a

24-hour format. If the T24 bit is 0, the RTC will use 12-

hour format and bit H21 will function as an AM/PM indi-

cator with a `1' representing PM. The clock defaults to

Standard Time with H21=0.

Leap Years

Leap years add the day February 29 and are defined as

those years that are divisible by 4. Years divisible by

100 are not leap years, unless they are also divisible by

400. This means that the year 2000 is a leap year, the

year 2100 is not. The X1243 does not correct for the

leap year in the year 2100.

STATUS REGISTER (SR)

The Status Register is located in the RTC area at

address 003FH. This is a volatile register only and is

used to control the WEL and RWEL write enable

latches, read an optional Low Voltage Sense bit, and

read the two alarm bits. This register is logically seper-

ated from both the array and the Clock/Control Regis-

ters (CCR).

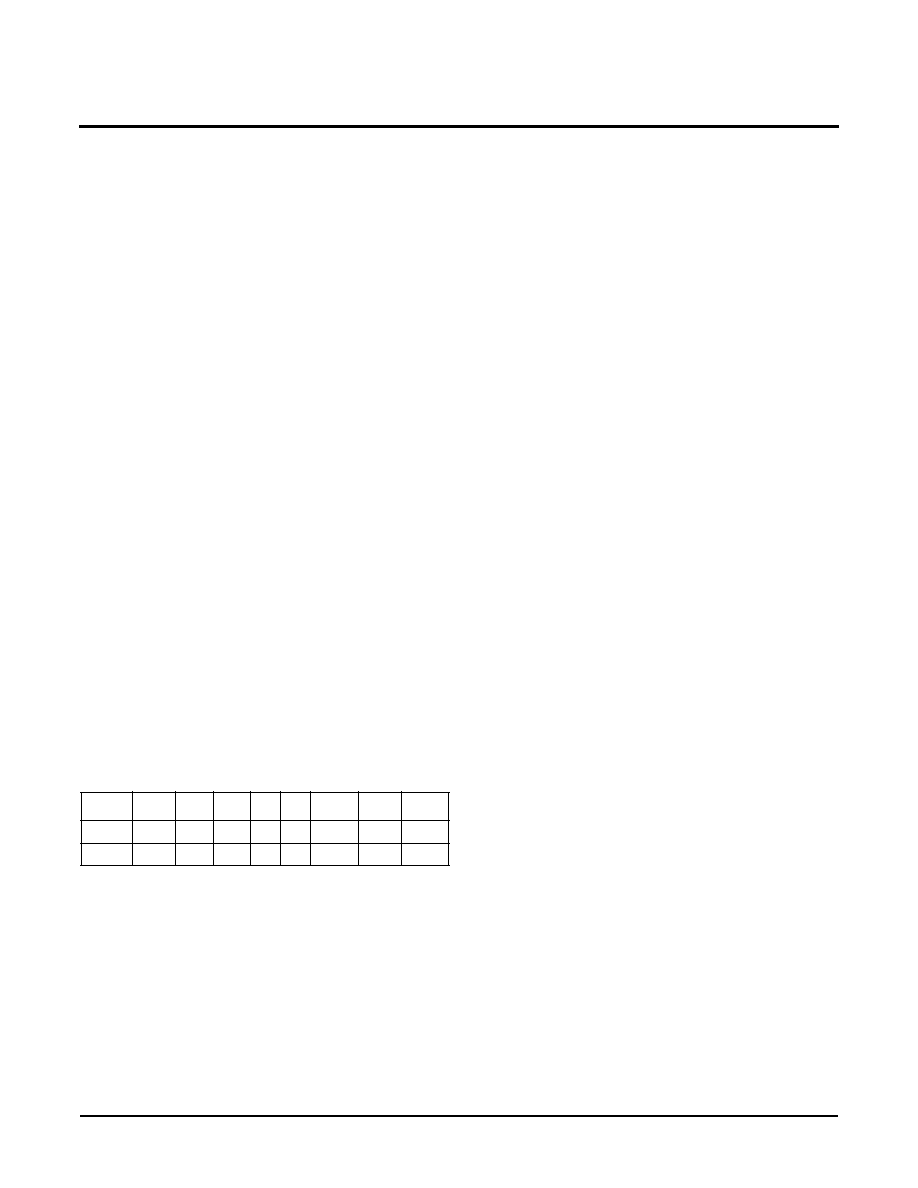

Table 2. Status Register (SR)

BAT: Battery Supply--Volatile

This bit set to "1" indicates that the device is operating

from V

BACK

, not V

CC

. It is a read only bit and is set/

reset by hardware.

AL1, AL0: Alarm bits--Volatile

These bits announce if either alarm 1 or alarm 2 match

the real time clock. If there is a match, the respective bit

is set to `1'. The falling edge of the last data bit in a SR

Read operation resets the flags. Note: Only the AL bits

that are set when an SR read starts will be reset. An

alarm bit that is set by an alarm occuring during an SR

read operation will remain set after the read operation

is complete.

RWEL: Register Write Enable Latch--Volatile

This bit is a volatile latch that powers up in the LOW

(disabled) state. The RWEL bit must be set to "1" prior

to any writes to the Clock/Control Registers. Writes to

RWEL bit do not cause a nonvolatile write cycle, so the

device is ready for the next operation immediately after

the stop condition. A write to the CCR requires both the

RWEL and WEL bits to be set in a specific sequence.

WEL: Write Enable Latch--Volatile

The WEL bit controls the access to the CCR and mem-

ory array during a write operation. This bit is a volatile

latch that powers up in the LOW (disabled) state. While

the WEL bit is LOW, writes to the CCR or any array

address will be ignored (no acknowledge will be issued

after the Data Byte). The WEL bit is set by writing a "1"

to the WEL bit and zeroes to the other bits of the Status

Register. Once set, WEL remains set until either reset

to 0 (by writing a "0" to the WEL bit and zeroes to the

other bits of the Status Register) or until the part pow-

ers up again. Writes to WEL bit do not cause a non-vol-

atile write cycle, so the device is ready for the next

operation immediately after the stop condition.

RTCF: Real Time Clock Fail Bit--Volatile

This bit is set to a `1' after a total power failure. This is a

read only bit that is set by hardware when the device

powers up after having lost all power to the device. The

bit is set regardless of whether V

CC

or V

BACK

is applied

first. The loss of one or the other supplies does not

result in setting the RTCF bit. The first valid write to the

RTC (writing one byte is sufficient) resets the RTCF bit

to `0'.

Unused Bits:

These devices do not use bits 3 or 4, but must have a

zero in these bit positions. The Data Byte output during

a SR read will contain zeros in these bit locations.

Addr

7

6

5

4

3

2

1

0

003Fh

BAT

AL1

AL0

0

0

RWEL

WEL

RTCF

Default

0

0

0

0

0

0

0

0