| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: ARM60 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

ARM60

Data Sheet

Zarlink Part Number: P60ARM-B/IG/GP1N

Notes

1) The original P60ARM/CG/GPFR is obsolete

2) This datasheet includes the performance data previously supplied in supplement

MS4396 - Jan 1996

Preface-ii

Preface

The ARM60 is a low power, general purpose 32-bit RISC microprocessor. It is an implementation of the

ARM6 macrocell, packaged in a 100 pin Metric Quad Flat Pack. Its simple, elegant and fully static design is

particularly suitable for cost and power sensitive applications .

Applications:

The ARM60 is ideally suited to those applications requiring RISC performance from a compact, power

efficient processor. These include:

Telecomms

- eg GSM terminal controller

Datacomms

- eg protocol conversion

Portable Computing

- eg palmtop computer

Portable Instruments

- eg handheld data acquisition unit

Automotive

- eg engine management unit

Consumer Multimedia

- low cost controller

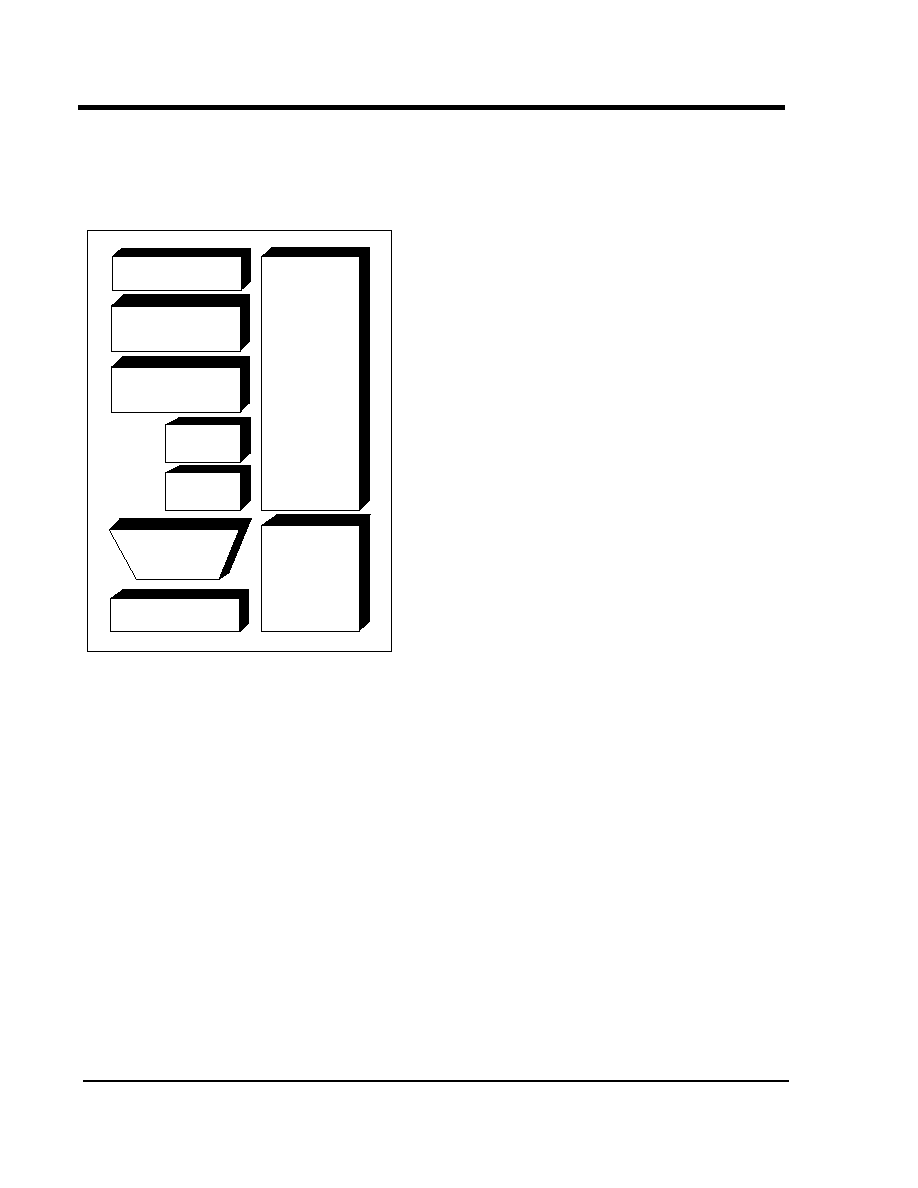

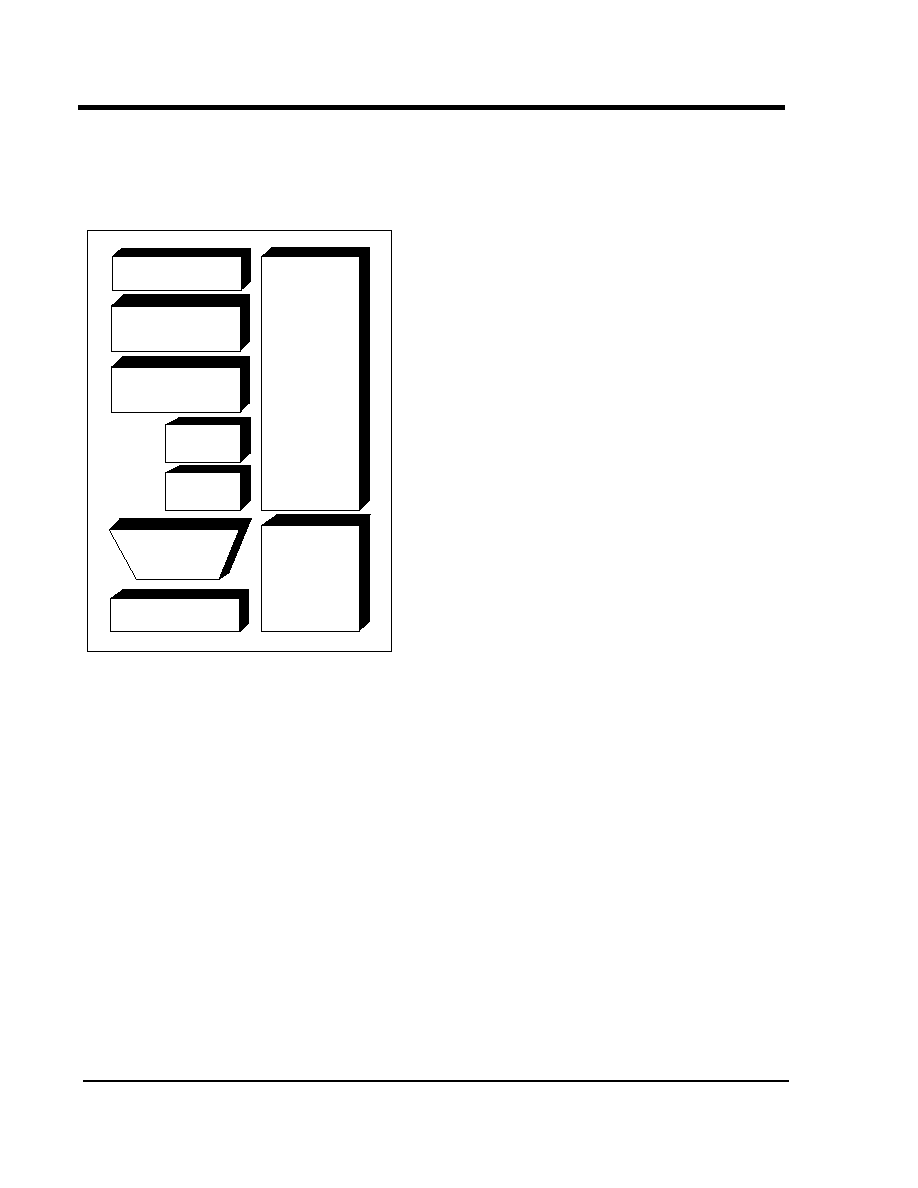

Instruction

Decoder

&

Logic

Control

Address Register

Address

Incrementer

Register Bank

Multiplier

Barrel

Shifter

32 bit ALU

Write Data Register

Instruction

Pipeline &

Read Data

Register

Booth's

t 32 bit RISC processor

t 32 bit data bus

t 32 bit address bus

t Big and Little Endian operating modes

t High performance RISC

21 MIPS sustained @ 30MHz (30 MIPS peak) @ 5V

t Low power consumption

1.5mA/MHz @ 5V fabricated in 1

µ

m CMOS

t Fully static operation

ideal for power sensitive applications

t Fast interrupt response

for real-time applications

t Virtual Memory System Support

t Excellent high-level language support

t Simple but powerful instruction set

t IEEE 1149.1 (JTAG) Boundary Scan

to ease testing

iii

Table of Contents

1.0

Introduction

1

1.1

ARM60 Block diagram

2

1.2

ARM60 Functional Diagram

3

2.0

Signal Description

5

3.0

Programmer's Model

9

3.1

Hardware Configuration

9

3.2

Operating Mode Selection

9

3.3

Registers

10

3.4

Exceptions

13

3.5

Reset

17

4.0

Instruction Set

19

4.1

Instruction Set Summary

19

4.2

The Condition Field

20

4.3

Branch and Branch with link (B, BL)

21

4.4

Data processing

23

4.5

PSR Transfer (MRS, MSR)

30

4.6

Multiply and Multiply-Accumulate (MUL, MLA)

34

4.7

Single data transfer (LDR, STR)

36

4.8

Block data transfer (LDM, STM)

41

4.9

Single data swap (SWP)

48

4.10

Software interrupt (SWI)

50

4.11

Coprocessor data operations (CDP)

52

4.12

Coprocessor data transfers (LDC, STC)

54

4.13

Coprocessor register transfers (MRC, MCR)

57

4.14

Undefined instruction

59

4.15

Instruction Set Examples

60

5.0

Memory Interface

65

5.1

Cycle types

65

5.2

Byte addressing

66

5.3

Address timing

68

5.4

Memory management

68

5.5

Locked operations

69

5.6

Stretching access times

69

6.0

Coprocessor Interface

71

6.1

Interface signals

71

6.2

Data transfer cycles

72

6.3

Register transfer cycle

72

6.4

Privileged instructions

72

6.5

Idempotency

72

6.6

Undefined instructions

73

7.0

Instruction Cycle Operations

75

7.1

Branch and branch with link

75

7.2

Data Operations

75

7.3

Multiply and multiply accumulate

77

7.4

Load register

77

7.5

Store register

78

P60ARM-B

iv

7.6

Load multiple registers

79

7.7

Store multiple registers

81

7.8

Data swap

81

7.9

Software interrupt and exception entry

82

7.10

Coprocessor data operation

83

7.11

Coprocessor data transfer (from memory to coprocessor)

83

7.12

Coprocessor data transfer (from coprocessor to memory)

85

7.13

Coprocessor register transfer (Load from coprocessor)

86

7.14

Coprocessor register transfer (Store to coprocessor)

86

7.15

Undefined instructions and coprocessor absent

87

7.16

Unexecuted instructions

87

7.17

Instruction Speed Summary

88

8.0

Boundary Scan Test Interface

89

8.1

Overview

89

8.2

Reset

90

8.3

Pullup Resistors

90

8.4

Instruction Register

90

8.5

Public Instructions

90

8.6

Test Data Registers

94

8.7

Boundary Scan Interface Signals

97

9.0

DC Parameters

101

9.1

Absolute Maximum Ratings

101

9.2

DC Operating Conditions

101

10.0

AC Parameters

105

10.1

Notes on AC Parameters

112

11.0

Physical Details

113

12.0

Pinout

115

13.0

Appendix - Backward Compatibility

117

Introduction

1

1.0 Introduction

The ARM60 is part of the Advanced RISC Machines (ARM) family of general purpose 32-bit

microprocessors, which offer very low power consumption and price for high performance devices. The

architecture is based on Reduced Instruction Set Computer (RISC) principles, and the instruction set and

related decode mechanism are much simpler in comparison with microprogrammed Complex Instruction

Set Computers. This results in a high instruction throughput and impressive real-time interrupt response

from a small and cost-effective chip.

The instruction set comprises eleven basic instruction types:

•

Two of these make use of the on-chip arithmetic logic unit, barrel shifter and multiplier to perform

high-speed operations on the data in a bank of 31 registers, each 32 bits wide;

•

Three classes of instruction control data transfer between memory and the registers, one optimised

for flexibility of addressing, another for rapid context switching and the third for swapping data;

•

Three instructions control the flow and privilege level of execution; and

•

Three types are dedicated to the control of external coprocessors which allow the functionality of

the instruction set to be extended off-chip in an open and uniform way.

The ARM instruction set is a good target for compilers of many different high-level languages. Where

required for critical code segments, assembly code programming is also straightforward, unlike some RISC

processors which depend on sophisticated compiler technology to manage complicated instruction

interdependencies.

Pipelining is employed so that all parts of the processing and memory systems can operate continuously.

Typically, while one instruction is being executed, its successor is being decoded, and a third instruction is

being fetched from memory.

The memory interface has been designed to allow the performance potential to be realised without

incurring high costs in the memory system. Speed critical control signals are pipelined to allow system

control functions to be implemented in standard low-power logic, and these control signals facilitate the

exploitation of the fast access modes offered by industry standard dynamic RAMs.

ARM60 has a 32 bit address bus. All ARM processors share the same instruction set, and ARM60 can be

configured to use a 26 bit address bus for backwards compatibility with earlier processors.

ARM60 is a fully static CMOS implementation of the ARM which allows the clock to be stopped in any part

of the cycle with extremely low residual power consumption and no loss of state.

Notation:

0x

- marks a Hexadecimal quantity

BOLD

- external signals are shown in bold capital letters

binary

- where it is not clear that a quantity is binary it is followed by the word binary