Document Outline

- Features

- QoS Support

- Description

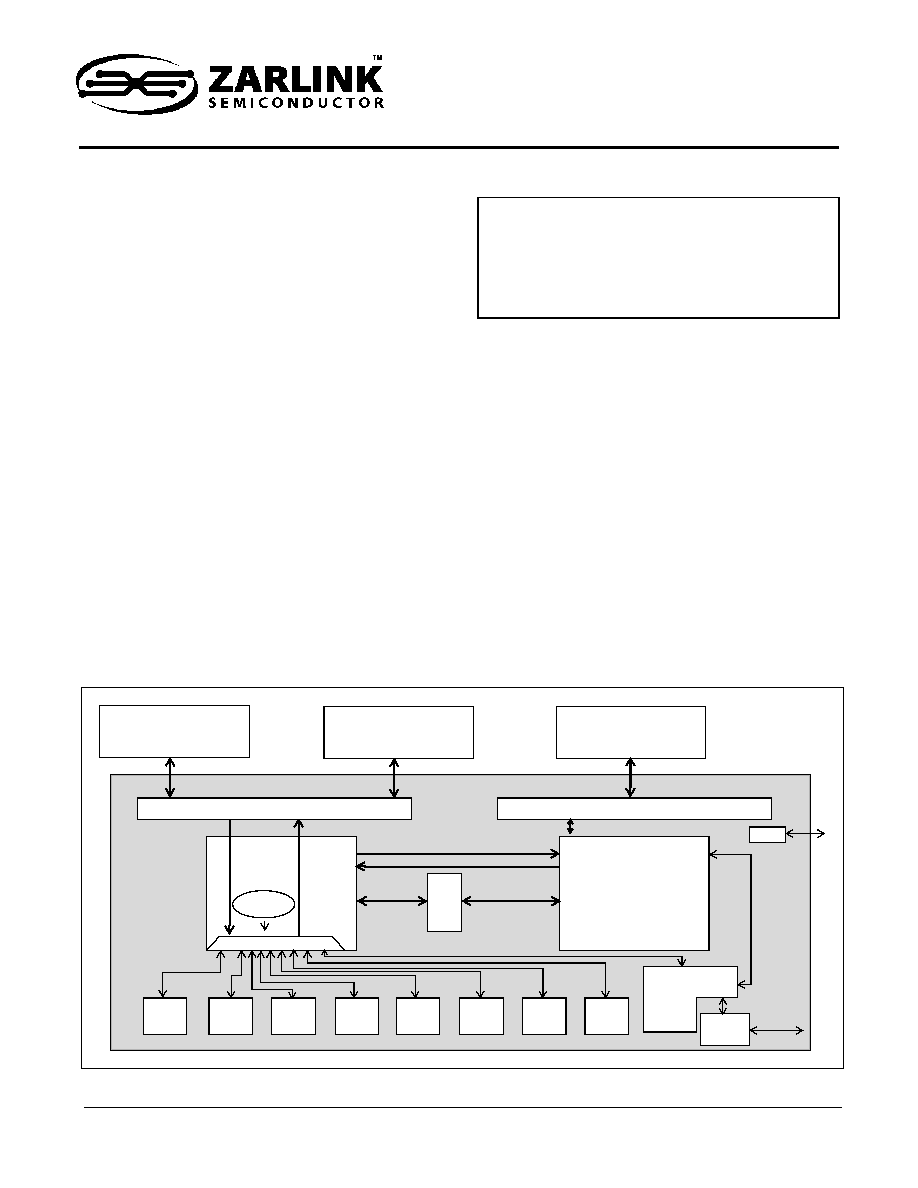

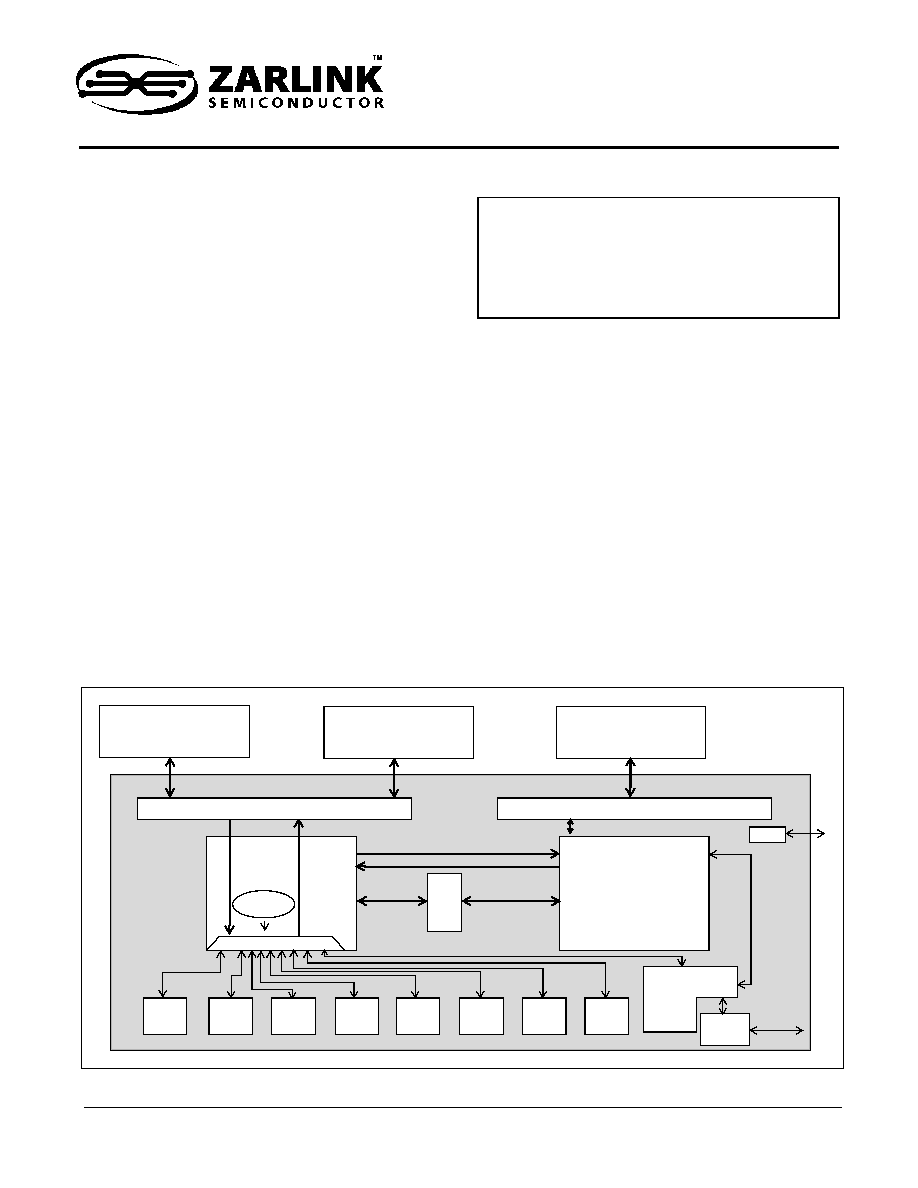

- Figure 1 - MVTX2804AG Functional Block Diagram

- 1.0 Block Functionality

- 1.1 Frame Data Buffer (FDB) Interfaces

- 1.2 Switch Database (SDB) Interface

- 1.3 GMII/PCS MAC Module (GMAC)

- 1.4 CPU Interface Module

- 1.5 Management Module

- 1.6 Frame Engine

- 1.7 Search Engine

- 1.8 LED Interface

- 1.9 Internal Memory

- 2.0 System Configuration

- 2.1 Management and Configuration

- 2.2 Managed Mode

- Figure 2 - Overview of the MTVTX2804AG CPU Interface

- 2.3 Register Configuration, Frame Transmission, and Frame Reception

- 2.3.1 Ethernet Frames

- 2.3.2 Control Frames

- 2.4 Unmanaged Mode

- 2.5 I2C Interface

- Figure 3 - Data Transfer Format for I2C Interface

- 2.5.1 Start Condition

- 2.5.2 Address

- 2.5.3 Data Direction

- 2.5.4 Acknowledgment

- 2.5.5 Data

- 2.5.6 Stop Condition

- 2.6 Synchronous Serial Interface

- 2.6.1 Write Command

- 2.6.2 Read Command

- 3.0 Data Forwarding Protocol

- 3.1 Unicast Data Frame Forwarding

- 3.2 Multicast Data Frame Forwarding

- 3.3 Frame Forwarding To and From CPU

- 4.0 Memory Interface

- 4.1 Overview

- Figure 4 - MVTX2804 SRAM Interface Block Diagram (DMAs for Gigaport Ports)

- 4.2 Detailed Memory Information

- 5.0 Search Engine

- 5.1 Search Engine Overview

- 5.2 Basic Flow

- 5.3 Search, Learning, and Aging

- 5.3.1 MAC Search

- 5.3.2 Learning

- 5.3.3 Aging

- 5.3.4 Data Structure

- 5.3.5 VLAN Port Association Table

- 6.0 Frame Engine

- 6.1 Data Forwarding Summary

- 6.2 Frame Engine Details

- 6.2.1 FCB Manager

- 6.2.2 Rx Interface

- 6.2.3 RxDMA

- 6.2.4 TxQ Manager

- 6.3 Port Control

- 6.4 TxDMA

- 7.0 Quality of Service and Flow Control

- 7.1 Model

- Table 1 - Two-dimensional World Traffic�

- 7.2 Four QoS Configurations

- Table 2 - Four QoS configurations per port

- 7.3 Delay Bound

- 7.4 Strict Priority and Best Effort

- 7.5 Weighted Fair Queuing

- 7.6 Shaper

- 7.7 WRED Drop Threshold Management Support

- Table 3 - WRED Dropping Scheme

- 7.8 Buffer Management

- Figure 5 - Buffer Partition Scheme Used in the MVTX2804

- 7.8.1 Dropping When Buffers Are Scarce

- 7.9.1 Unicast Flow Control

- 7.9.2 Multicast Flow Control

- 7.10 Mapping to IETF Diffserv Classes

- Table 4 - Mapping between MVTX2804 and IETF Diffserv Classes for Gigabit Ports

- Figure 6 - MVTX2804 Features Enabling IETF Diffserv Standards

- 8.0 Port Trunking

- 8.1 Features and Restrictions

- 8.2 Unicast Packet Forwarding

- 8.3 Multicast Packet Forwarding

- 8.4 Preventing Multicast Packets from Looping Back to the Source Trunk

- 9.0 LED Interface

- 9.1 Introduction

- 9.2 Serial Mode

- Figure 7 - Timing diagram for serial mode in LED interface

- 9.3 Parallel Mode

- 9.4 LED Control Registers

- 10.0 Hardware Statistics Counter

- 10.1 Hardware Statistics Counters List

- 10.2 IEEE 802.3 HUB Management (RFC 1213)

- 10.2.1 Event Counters

- 10.2.1.1 READABLEOCTET

- 10.2.1.2 READABLEFRAME

- 10.2.1.3 FCSERRORS

- 10.2.1.4 ALIGNMENTERRORS

- 10.2.1.5 FRAMETOOLONGS

- 10.2.1.6 SHORTEVENTS

- 10.2.1.7 RUNTS

- 10.2.1.8 COLLISIONS

- 10.2.1.9 LATEEVENTS

- 10.2.1.10 VERYLONGEVENTS

- 10.2.1.11 DATARATEMISATCHES

- 10.2.1.12 AUTOPARTITIONS

- 10.2.1.13 TOTALERRORS

- 10.3 IEEE - 802.1 Bridge Management (RFC 1286)

- 10.3.0.1 Event Counters

- 10.3.0.3 OUTFRAMES

- 10.3.0.4 INDISCARDS

- 10.3.0.5 DELAYEXCEEDEDDISCARDS

- 10.3.0.6 MTUEXCEEDEDDISCARDS

- 10.4 RMON - Ethernet Statistic Group (RFC 1757)

- 10.4.1 Event Counters

- 10.4.1.1 DROP EVENTS

- 10.4.1.2 OCTETS

- 10.4.1.3 BROADCASTPKTS

- 10.4.1.4 MULTICASTPKTS

- 10.4.1.5 CRCALIGNERRORS

- 10.4.1.6 UNDERSIZEPKTS

- 10.4.1.7 OVERSIZEPKTS

- 10.4.1.8 FRAGMENTS

- 10.4.1.9 JABBERS

- 10.4.1.10 COLLISIONS

- 10.4.1.11 PACKET COUNT FOR DIFFERENT SIZE GROUPS

- 11.0 Register Definition

- 11.1 Register Description

- Register Description Table (continued)

- 11.2 Directly Accessed Registers

- 11.2.1 INDEX_REG0

- 11.2.2 INDEX_REG1 (only needed for CPU 8-bit bus mode)

- 11.2.3 DATA_FRAME_REG

- 11.2.4 CONTROL_FRAME_REG

- 11.2.5 COMMAND & STATUS

- 11.2.6 Interrupt Register

- 11.2.7 Control Frame Buffer1 Access Register

- 11.2.8 Control Frame Buffer2 Access Register

- 11.3 Group 0 Address

- 11.3.1 MAC Ports Group

- 11.3.1.1 ECR1PN: PORT N CONTROL REGISTER

- 11.3.1.2 ECR2PN: PORT N CONTROL REGISTER

- 11.3.1.3 ECRMISC1 - CPU PORT CONTROL REGISTER MISC1

- 11.3.1.4 ECRMISC2 - CPU PORT CONTROL REGISTER MISC2

- 11.3.1.5 GGCONTROL 0- EXTRA GIGA PORT CONTROL

- 11.3.1.6 GGCONTROL 1- EXTRA GIGA PORT CONTROL

- 11.3.1.7 GGCONTROL 2- EXTRA GIGA PORT CONTROL

- 11.3.1.8 GGCONTROL 3- EXTRA GIGA PORT CONTROL

- 11.4 Group 1 Address

- 11.4.1 VLAN Group

- 11.4.1.1 AVTCL - VLAN TYPE CODE REGISTER LOW

- 11.4.1.2 AVTCH - VLAN TYPE CODE REGISTER HIGH

- 11.4.1.3 PVMAP00_0 - PORT 00 CONFIGURATION REGISTER 0

- 11.4.1.4 PVMAP00_1 - PORT 00 CONFIGURATION REGISTER 1

- 11.4.1.5 PVMAP00_3 - PORT 00 CONFIGURATION REGISTER 3

- 11.5 Port VLAN Map

- 11.6 Group 2 Address

- 11.6.1 Port Trunking Group

- 11.6.1.1 TRUNK0 - TRUNK GROUP 0 MEMBER (MANAGED MODE ONLY)

- 11.6.1.2 TRUNK1 - TRUNK GROUP 1 MEMBER (MANAGED MODE ONLY)

- 11.6.1.3 TRUNK2- TRUNK GROUP 2 MEMBER (MANAGED MODE ONLY)

- 11.6.1.4 TRUNK3- TRUNK GROUP 3 MEMBER (MANAGED MODE ONLY)

- 11.6.1.5 TRUNK_HASH_MODE - TRUNK HASH MODE

- 11.6.1.6 TRUNK0_MODE - TRUNK GROUP 0 MODE (UNMANAGED MODE)

- 11.6.1.7 TRUNK0_HASH0 - TRUNK GROUP 0 HASH RESULT 0,1,2 DESTINATION PORT NUMBER

- 11.6.1.8 TRUNK0_HASH1 - TRUNK GROUP 0 HASH RESULT 2,3,4,5 DESTINATION PORT NUMBER

- 11.6.1.9 TRUNK0_HASH2 - TRUNK GROUP 0 HASH RESULT 5,6,7 DESTINATION PORT NUMBER

- 11.6.1.10 TRUNK0_HASH3 - TRUNK GROUP 0 HASH RESULT 8,9,10 DESTINATION PORT NUMBER

- 11.6.1.11 TRUNK0_HASH4 - TRUNK GROUP 0 HASH RESULT 10,11,12,13 DESTINATION PORT NUMBER

- 11.6.1.12 TRUNK0_HASH5 - TRUNK GROUP 0 HASH RESULT 13,14,15 DESTINATION PORT NUMBER

- 11.6.1.13 TRUNK1_MODE - TRUNK GROUP 1 MODE (UNMANAGED MODE)

- 11.6.1.14 TRUNK1_HASH0 - TRUNK GROUP 1 HASH RESULT 0, 1, 2 DESTINATION PORT NUMBER

- 11.6.1.15 TRUNK1_HASH1 - TRUNK GROUP 1 HASH RESULT 2, 3, 4, 5 DESTINATION PORT NUMBER

- 11.6.1.16 TRUNK1_HASH2 - TRUNK GROUP 1 HASH RESULT 5, 6, 7 DESTINATION PORT NUMBER

- 11.6.1.17 TRUNK1_HASH3 - TRUNK GROUP 1 HASH RESULT 8, 9, 10 DESTINATION PORT NUMBER

- 11.6.1.18 TRUNK1_HASH4- TRUNK GROUP 1 HASH RESULT 11, 12, 13 DESTINATION PORT NUMBER

- 11.6.1.19 TRUNK1_HASH5 - TRUNK GROUP 1 HASH RESULT 13, 14, 15 DESTINATION PORT NUMBER

- 11.6.1.20 TRUNK2_HASH0 - TRUNK GROUP 2 HASH RESULT 0, 1, 2 DESTINATION PORT NUMBER

- 11.6.1.21 TRUNK2_HASH1 - TRUNK GROUP 2 HASH RESULT 2, 3, 4, 5 DESTINATION PORT NUMBER

- 11.6.1.22 TRUNK2_HASH2 - TRUNK GROUP 2 HASH RESULT 5, 6, 7 DESTINATION PORT NUMBER

- 11.6.1.23 TRUNK2_HASH3 - TRUNK GROUP 2 HASH RESULT 8, 9, 10 DESTINATION PORT NUMBER

- 11.6.1.24 TRUNK0_HASH3 - TRUNK GROUP 0 HASH RESULT 8,9,10 DESTINATION PORT NUMBER

- 11.6.1.25 TRUNK0_HASH4 - TRUNK GROUP 0 HASH RESULT 10,11,12,13 DESTINATION PORT NUMBER

- 11.6.1.26 TRUNK0_HASH5 - TRUNK GROUP 0 HASH RESULT 13,14,15 DESTINATION PORT NUMBER

- 11.6.1.27 TRUNK1_MODE - TRUNK GROUP 1 MODE (UNMANAGED MODE)

- 11.6.1.28 TRUNK1_HASH0 - TRUNK GROUP 1 HASH RESULT 0, 1, 2 DESTINATION PORT NUMBER

- 11.6.1.29 TRUNK1_HASH1 - TRUNK GROUP 1 HASH RESULT 2, 3, 4, 5 DESTINATION PORT NUMBER

- 11.6.1.30 TRUNK1_HASH2 - TRUNK GROUP 1 HASH RESULT 5, 6, 7 DESTINATION PORT NUMBER

- 11.6.1.31 TRUNK1_HASH3 - TRUNK GROUP 1 HASH RESULT 8, 9, 10 DESTINATION PORT NUMBER

- 11.6.1.32 TRUNK1_HASH4- TRUNK GROUP 1 HASH RESULT 11, 12, 13 DESTINATION PORT NUMBER

- 11.6.1.33 TRUNK1_HASH5 - TRUNK GROUP 1 HASH RESULT 13, 14, 15 DESTINATION PORT NUMBER

- 11.6.1.34 TRUNK2_HASH0 - TRUNK GROUP 2 HASH RESULT 0, 1, 2 DESTINATION PORT NUMBER

- 11.6.1.35 TRUNK2_HASH1 - TRUNK GROUP 2 HASH RESULT 2, 3, 4, 5 DESTINATION PORT NUMBER

- 11.6.1.36 TRUNK2_HASH2 - TRUNK GROUP 2 HASH RESULT 5, 6, 7 DESTINATION PORT NUMBER

- 11.6.1.37 TRUNK2_HASH3 - TRUNK GROUP 2 HASH RESULT 8, 9, 10 DESTINATION PORT NUMBER

- 11.6.1.38 TRUNK2_HASH4 - TRUNK GROUP 2 HASH RESULT 10, 11, 12, 13 DESTINATION PORT NUMBER

- 11.6.1.39 TRUNK2_HASH5 - TRUNK GROUP 2 HASH RESULT 13, 14, 15 DESTINATION PORT NUMBER

- 11.6.1.40 TRUNK3_HASH0 - TRUNK GROUP 3 HASH RESULT 0, 1, 2 DESTINATION PORT NUMBER

- 11.6.1.41 TRUNK3_HASH1 - TRUNK GROUP 3 HASH RESULT 2, 3, 4, 5 DESTINATION PORT NUMBER

- 11.6.1.42 TRUNK3_HASH2 - TRUNK GROUP 3 HASH RESULT 5, 6, 7 DESTINATION PORT NUMBER

- 11.6.1.43 TRUNK3_HASH3 - TRUNK GROUP 3 HASH RESULT 8, 9, 10 DESTINATION PORT NUMBER

- 11.6.1.44 TRUNK3_HASH4 - TRUNK GROUP 3 HASH RESULT 10, 11, 12, 13 DESTINATION PORT NUMBER

- 11.6.1.45 TRUNK3_HASH5 - TRUNK GROUP 3 HASH RESULT 13, 14, 15 DESTINATION PORT NUMBER

- 11.6.2 Multicast Hash Registers

- 11.6.2.1 MULTICAST_HASH00 - MULTICAST HASH RESULT0 MASK BYTE [7:0]

- 11.6.2.2 MULTICAST_HASH01 - MULTICAST HASH RESULT1 MASK BYTE [7:0]

- 11.6.2.3 MULTICAST_HASH02 - MULTICAST HASH RESULT2 MASK BYTE [7:0]

- 11.6.2.4 MULTICAST_HASH03 - MULTICAST HASH RESULT3 MASK BYTE [7:0]

- 11.6.2.5 MULTICAST_HASH04 - MULTICAST HASH RESULT4 MASK BYTE [7:0]

- 11.6.2.6 MULTICAST_HASH05 - MULTICAST HASH RESULT5 MASK BYTE [7:0]

- 11.6.2.7 MULTICAST_HASH06 - MULTICAST HASH RESULT6 MASK BYTE [7:0]

- 11.6.2.8 MULTICAST_HASH07 - MULTICAST HASH RESULT7 MASK BYTE [7:0]

- 11.6.2.9 MULTICAST_HASH08 - MULTICAST HASH RESULT8 MASK BYTE [7:0]

- 11.6.2.10 MULTICAST_HASH09 - MULTICAST HASH RESULT9 MASK BYTE [7:0]

- 11.6.2.11 MULTICAST_HASH10 - MULTICAST HASH RESULT10 MASK BYTE [7:0]

- 11.6.2.12 MULTICAST_HASH11 - MULTICAST HASH RESULT11 MASK BYTE [7:0]

- 11.6.2.13 MULTICAST_HASH12 - MULTICAST HASH RESULT12 MASK BYTE [7:0]

- 11.6.2.14 MULTICAST_HASH13 - MULTICAST HASH RESULT13 MASK BYTE [7:0]

- 11.6.2.15 MULTICAST_HASH14 - MULTICAST HASH RESULT14 MASK BYTE [7:0]

- 11.6.2.16 MULTICAST_HASH15 - MULTICAST HASH RESULT15 MASK BYTE [7:0]

- 11.6.2.17 MULTICAST_HASHML - MULTICAST HASH BIT[8] FOR RESULT7-0

- 11.6.2.18 MULTICAST_HASHML - MULTICAST HASH BIT[8] FOR RESULT 15-8

- 11.7 Group 3 Address

- 11.7.1 CPU Port Configuration Group

- 11.7.1.1 MAC0 - CPU MAC ADDRESS BYTE 0

- 11.7.1.2 MAC1 - CPU MAC ADDRESS BYTE 1

- 11.7.1.3 MAC2 - CPU MAC ADDRESS BYTE 2

- 11.7.1.4 MAC3 - CPU MAC ADDRESS BYTE 3

- 11.7.1.5 MAC4 - CPU MAC ADDRESS BYTE 4

- 11.7.1.6 MAC5 - CPU MAC ADDRESS BYTE 5

- 11.7.1.7 INT_MASK0 - INTERRUPT MASK 0

- 11.7.1.8 INT_MASK1 - INTERRUPT MASK 1

- 11.7.1.9 INT_STATUS0 - MASKED INTERRUPT STATUS REGISTER0

- 11.7.1.10 INT_STATUS1 - MASKED INTERRUPT STATUS REGISTER1

- 11.7.1.11 INTP_MASK0 - INTERRUPT MASK FOR MAC PORT 0,1

- 11.7.1.12 INTP_MASK1 - INTERRUPT MASK FOR MAC PORT 2,3

- 11.7.1.13 INTP_MASK4 - INTERRUPT MASK FOR MAC PORT 4,5

- 11.7.1.14 INTP_MASK5 - INTERRUPT MASK FOR MAC PORT 6,7

- 11.7.2 RQS - Receive Queue Select

- 11.7.3 RQSS - Receive Queue Status

- 11.7.4 TX_AGE - Tx Queue Aging timer

- 11.8 Group 4 Address

- 11.8.1 Search Engine Group

- 11.8.1.1 AGETIME_LOW - MAC ADDRESS AGING TIME LOW

- 11.8.1.2 AGETIME_HIGH -MAC ADDRESS AGING TIME HIGH

- 11.8.1.3 V_AGETIME - VLAN TO PORT AGING TIME

- 11.8.1.4 SE_OPMODE - SEARCH ENGINE OPERATION MODE

- 11.8.1.5 SCAN - SCAN CONTROL REGISTER

- 11.9 Group 5 Address

- 11.9.1 Buffer Control/QOS Group

- 11.9.1.1 FCBAT - FCB AGING TIMER

- 11.9.1.2 QOSC - QOS CONTROL

- 11.9.1.3 FCR - FLOODING CONTROL REGISTER

- 11.9.1.4 AVPML - VLAN PRIORITY MAP

- 11.9.1.5 AVPMM - VLAN PRIORITY MAP

- 11.9.1.6 AVPMH - VLAN PRIORITY MAP

- 11.9.1.7 TOSPML - TOS PRIORITY MAP

- 11.9.1.8 TOSPMM - TOS PRIORITY MAP

- 11.9.1.9 TOSPMH - TOS PRIORITY MAP

- 11.9.1.10 AVDM - VLAN DISCARD MAP

- 11.9.1.11 TOSDML - TOS DISCARD MAP

- 11.9.2 BMRC - Broadcast/Multicast Rate Control

- 11.9.3 UCC - Unicast Congestion Control

- 11.9.4 MCC - Multicast Congestion Control

- 11.9.5 PRG - Port Reservation for Giga ports

- 11.9.6 FCB Reservation

- 11.9.6.1 SFCB - SHARE FCB SIZE

- 11.9.6.2 C2RS - CLASS 2 RESERVED SIZE

- 11.9.6.3 C3RS - CLASS 3 RESERVED SIZE

- 11.9.6.4 C4RS - CLASS 4 RESERVED SIZE

- 11.9.6.5 C5RS - CLASS 5 RESERVED SIZE

- 11.9.6.6 C6RS - CLASS 6 RESERVED SIZE

- 11.9.6.7 C7RS - CLASS 7 RESERVED SIZE

- 11.9.7 Classes Byte Gigabit Port 0

- 11.9.7.1 QOSC00 - BYTE_C2_G0

- 11.9.7.2 QOSC01 - BYTE_C3_G0

- 11.9.7.3 QOSC02 - BYTE_C4_G0

- 11.9.7.4 QOSC03 - BYTE_C5_G0

- 11.9.7.5 QOSC04 - BYTE_C6_G0

- 11.9.7.6 QOSC05 - BYTE_C7_G0

- 11.9.8 Classes Byte Gigabit Port 1

- 11.9.8.1 QOSC06 - BYTE_C2_G1

- 11.9.8.2 QOSC07 - BYTE_C3_G1

- 11.9.8.3 QOSC08 - BYTE_C4_G1

- 11.9.8.4 QOSC09 - BYTE_C5_G1

- 11.9.8.5 QOSC0A - BYTE_C6_G1

- 11.9.8.6 QOSC0B - BYTE_C7_G1

- 11.9.9 Classes Byte Gigabit Port 2

- 11.9.9.1 QOSC0C - BYTE_C2_G2

- 11.9.9.2 QOSC0D - BYTE_C3_G2

- 11.9.9.3 QOSC0E - BYTE_C4_G2

- 11.9.9.4 QOSC0F - BYTE_C5_G2

- 11.9.9.5 QOSC10 - BYTE_C6_G2

- 11.9.9.6 QOSC11 - BYTE_C7_G2

- 11.9.10 Classes Byte Gigabit Port 3

- 11.9.10.1 QOSC12 - BYTE_C2_G3

- 11.9.10.2 QOSC13 - BYTE_C3_G3

- 11.9.10.3 QOSC14 - BYTE_C4_G3

- 11.9.10.4 QOSC15 - BYTE_C5_G3

- 11.9.10.5 QOSC16 - BYTE_C6_G3

- 11.9.10.6 QOSC17 - BYTE_C7_G3

- 11.9.11 Classes Byte Gigabit Port 4

- 11.9.11.1 QOSC18 - BYTE_C2_G4

- 11.9.11.2 QOSC019 - BYTE_C3_G4

- 11.9.11.3 QOSC1A - BYTE_C4_G4

- 11.9.11.4 QOSC1B - BYTE_C5_G4

- 11.9.11.5 QOSC1C - BYTE_C6_G4

- 11.9.11.6 QOSC1D- BYTE_C7_G4

- 11.9.12 Classes Byte Gigabit Port 5

- 11.9.12.1 QOSC1E- BYTE_C2_G5

- 11.9.12.2 QOSC1F - BYTE_C3_G5

- 11.9.12.3 QOSC20 - BYTE_C4_G5

- 11.9.12.4 QOSC21 - BYTE_C5_G5

- 11.9.12.5 QOSC22 - BYTE_C6_G5

- 11.9.12.6 QOSC23 - BYTE_C7_G5

- 11.9.13 Classes Byte Gigabit Port 6

- 11.9.13.1 QOSC24 - BYTE_C2_G6

- 11.9.13.2 QOSC25 - BYTE_C3_G6

- 11.9.13.3 QOSC26 - BYTE_C4_G6

- 11.9.13.4 QOSC27 - BYTE_C5_G6

- 11.9.13.5 QOSC28 - BYTE_C6_G6

- 11.9.13.6 QOSC29 - BYTE_C7_G6

- 11.9.14 Classes Byte Gigabit Port 7

- 11.9.14.1 QOSC2A - BYTE_C2_G7

- 11.9.14.2 QOSC2B - BYTE_C3_G7

- 11.9.14.3 QOSC2C - BYTE_C4_G7

- 11.9.14.4 1QOSC2D - BYTE_C5_G7

- 11.9.14.5 QOSC2E - BYTE_C6_G7

- 11.9.14.6 QOSC2F - BYTE_C7_G7

- 11.9.15 Classes Byte Limit CPU

- 11.9.15.1 QOSC30 - BYTE_C01

- 11.9.15.2 QOSC31 - BYTE_C02

- 11.9.15.3 QOSC32 - BYTE_C03

- 11.9.16 Classes WFQ Credit Set 0

- 11.9.16.1 QOSC33 - CREDIT_C0_G0

- 11.9.16.2 QOSC34 - CREDIT_C1_G0

- 11.9.16.3 QOSC35 - CREDIT_C2_G0

- 11.9.16.4 QOSC36 - CREDIT_C3_G0

- 11.9.16.5 QOSC37 - CREDIT_C4_G0

- 11.9.16.6 QOSC38 - CREDIT_C5_G0

- 11.9.16.7 QOSC39- CREDIT_C6_G0

- 11.9.16.8 QOSC3A- CREDIT_C7_G0

- 11.9.17 Classes WFQ Credit Port G1

- 11.9.17.1 QOSC3B - CREDIT_C0_G1

- 11.9.17.2 QOSC3C - CREDIT_C1_G1

- 11.9.17.3 QOSC3D - CREDIT_C2_G1

- 11.9.17.4 QOSC3E - CREDIT_C3_G1

- 11.9.17.5 QOSC3F - CREDIT_C4_G1

- 11.9.17.6 QOSC40 - CREDIT_C5_G1

- 11.9.17.7 QOSC41- CREDIT_C6_G1

- 11.9.17.8 QOSC42- CREDIT_C7_G1

- 11.9.18 Classes WFQ Credit Port G2

- 11.9.18.1 QOSC43 - CREDIT_C0_G2

- 11.9.18.2 QOSC44 - CREDIT_C1_G2

- 11.9.18.3 QOSC45 - CREDIT_C2_G2

- 11.9.18.4 QOSC46 - CREDIT_C3_G2

- 11.9.18.5 QOSC47 - CREDIT_C4_G2

- 11.9.18.6 QOSC48 - CREDIT_C5_G2

- 11.9.18.7 QOSC49- CREDIT_C6_G2

- 11.9.18.8 QOSC4A- CREDIT_C7_G2

- 11.9.19 Classes WFQ Credit Port G3

- 11.9.19.1 QOSC4B - CREDIT_C0_G3

- 11.9.19.2 QOSC4 - CREDIT_C1_G3

- 11.9.19.3 QOSC4D - CREDIT_C2_G3

- 11.9.19.4 QOSC4E - CREDIT_C3_G3

- 11.9.19.5 QOSC4F - CREDIT_C4_G3

- 11.9.19.6 QOSC50 - CREDIT_C5_G3

- 11.9.19.7 QOSC51- CREDIT_C6_G3

- 11.9.19.8 QOSC52- CREDIT_C7_G3

- 11.9.20 Classes WFQ Credit Port G4

- 11.9.20.1 QOSC53 - CREDIT_C0_G4

- 11.9.20.2 QOSC54 - CREDIT_C1_G4

- 11.9.20.3 QOSC55 - CREDIT_C2_G4

- 11.9.20.4 QOSC56 - CREDIT_C3_G4

- 11.9.20.5 QOSC57 - CREDIT_C4_G4

- 11.9.20.6 QOSC58 - CREDIT_C5_G4

- 11.9.20.7 QOSC59- CREDIT_C6_G4

- 11.9.20.8 QOSC5A- CREDIT_C7_G4

- 11.9.20.9 Classes WFQ Credit Port G5

- 11.9.20.10 QOSC5B - CREDIT_C0_G5

- 11.9.20.11 QOSC5C - CREDIT_C1_G5

- 11.9.20.12 QOSC5D - CREDIT_C2_G5

- 11.9.20.13 QOSC5E - CREDIT_C3_G5

- 11.9.20.14 QOSC5F - CREDIT_C4_G5

- 11.9.20.15 QOSC60 - CREDIT_C5_G5

- 11.9.20.16 QOSC61- CREDIT_C6_G5

- 11.9.20.17 QOSC62- CREDIT_C7_G5

- 11.9.21 Classes WFQ Credit Port G6

- 11.9.21.1 QOSC63 - CREDIT_C0_G6

- 11.9.21.2 QOSC64 - CREDIT_C1_G6

- 11.9.21.3 QOSC65 - CREDIT_C2_G6

- 11.9.21.4 QOSC66 - CREDIT_C3_G6

- 11.9.21.5 QOSC67 - CREDIT_C4_G6

- 11.9.21.6 QOSC68 - CREDIT_C5_G6

- 11.9.21.7 QOSC69- CREDIT_C6_G6

- 11.9.21.8 QOSC6A- CREDIT_C7_G6

- 11.9.22 Classes WFQ Credit Port G7

- 11.9.22.1 QOSC6B - CREDIT_C0_G7

- 11.9.22.2 QOSC6C - CREDIT_C1_G7

- 11.9.22.3 QOSC6D - CREDIT_C2_G7

- 11.9.22.4 QOSC6E - CREDIT_C3_G7

- 11.9.22.5 QOSC6F - CREDIT_C4_G7

- 11.9.22.6 QOSC70 - CREDIT_C5_G7

- 11.9.22.7 QOSC71- CREDIT_C6_G7

- 11.9.22.8 QOSC72- CREDIT_C7_G7

- 11.9.23 Class 6 Shaper Control Port G0

- 11.9.23.1 QOSC73 - TOKEN_RATE_G0

- 11.9.23.2 QOSC74 - TOKEN_LIMIT_G0

- 11.9.23.3 Class 6 Shaper Control Port G1

- 11.9.23.4 QOSC75 - TOKEN_RATE_G1

- 11.9.23.5 QOSC76 - TOKEN_LIMIT_G1

- 11.9.24 Class 6 Shaper Control Port G2

- 11.9.24.1 QOSC77 - TOKEN_RATE_G2

- 11.9.24.2 QOSC78 - TOKEN_LIMIT_G2

- 11.9.25 Class 6 Shaper Control Port G3

- 11.9.25.1 QOSC79 - TOKEN_RATE_G3

- 11.9.25.2 QOSC7A - TOKEN_LIMIT_G3

- 11.9.26 Class 6 Shaper Control Port G4

- 11.9.26.1 QOSC7B - TOKEN_RATE_G4

- 11.9.26.2 QOSC7C - TOKEN_LIMIT_G4

- 11.9.27 Class 6 Shaper Control Port G5

- 11.9.27.1 QOSC7D - TOKEN_RATE_G5

- 11.9.27.2 QOSC7E - TOKEN_LIMIT_G5

- 11.9.28 Class 6 Shaper Control Port G6

- 11.9.28.1 Accessed by CPU only

- 11.9.28.2 QOSC7F - TOKEN_RATE_G6

- 11.9.28.3 QOSC80 - TOKEN_LIMIT_G6

- 11.9.29 Class 6 Shaper Control Port G7

- 11.9.29.1 QOSC81 - TOKEN_RATE_G7

- 11.9.29.2 QOSC82 - TOKEN_LIMIT_G7

- 11.9.30 RDRC0 - WRED Rate Control 0

- 11.9.31 RDRC1 - WRED Rate Control 1

- 11.10 Group 6 Address

- 11.10.1 MISC Group

- 11.10.1.1 MII_OP0 - MII REGISTER OPTION 0

- 11.10.1.2 MII_OP1 - MII REGISTER OPTION 1

- 11.10.1.3 FEN - FEATURE REGISTER

- 11.10.1.4 MIIC0 - MII COMMAND REGISTER 0

- 11.10.1.5 MIIC1 - MII COMMAND REGISTER 1

- 11.10.1.6 MIIC2 - MII COMMAND REGISTER 2

- 11.10.1.7 MIIC3 - MII COMMAND REGISTER 3

- 11.10.1.8 MIID0 - MII DATA REGISTER 0

- 11.10.1.9 MIID1 - MII DATA REGISTER 0

- 11.10.1.10 LED MODE - LED CONTROL

- 11.10.2 CHECKSUM - EEPROM Checksum

- 11.10.3 LED User

- 11.10.3.1 LEDUSER0

- 11.10.3.2 LEDUSER1

- 11.10.3.3 LEDUSER2/LEDSIG2

- 11.10.3.4 LEDUSER3/LEDSIG3

- 11.10.3.5 LEDUSER4/LEDSIG4

- 11.10.3.6 LEDUSER5/LEDSIG5

- 11.10.3.7 LEDUSER6/LEDSIG6

- 11.10.3.8 LEDUSER7/LEDSIG1_0

- 11.10.4 MIINP0 - MII Next Page Data Register 0

- 11.10.5 MIINP1 - MII Next Page Data Register 1

- 11.11 Group F Address

- 11.11.1 CPU Access Group

- 11.11.1.1 GCR-GLOBAL CONTROL REGISTER

- 11.11.1.2 DCR-DEVICE STATUS AND SIGNATURE REGISTER

- 11.11.1.3 DCR01-GIGA PORT STATUS

- 11.11.1.4 DCR23-GIGA PORT STATUS

- 11.11.1.5 DCR45-GIGA PORT STATUS

- 11.11.1.6 DCR67-GIGA PORT STATUS

- 11.11.1.7 DPST - DEVICE PORT STATUS REGISTER

- 11.11.1.8 DTST - Data Read Back Register

- 12.0 BGA and Ball Signal Description

- 12.1 BGA Views (Top-View)

- 12.2 Ball-Signal Descriptions

- 12.2.1 Ball Signal Description in Managed Mode

- 12.2.2 Ball - Signal Description in Unmanaged Mode

- 12.3 Ball Signal Name

- 12.4 Characteristics and Timing

- 12.4.1 Absolute Maximum Ratings

- 12.4.2 DC Electrical Characteristics

- 12.4.3 Recommended Operating Conditions

- 12.5 AC Characteristics and Timing

- 12.5.1 Typical Reset & Bootstrap Timing Diagram

- Figure 8 - Typical Reset & Bootstrap Timing Diagram

- Table 5 - Reset & Bootstrap Timing

- 12.5.2 Typical CPU Timing Diagram for a CPU Write Cycle

- Table 6 - CPU Write Cycle

- Figure 9 - Typical CPU Timing Diagram for a CPU Write Cycle

- 12.5.3 Typical CPU Timing Diagram for a CPU Read Cycle

- Figure 10 - Typical CPU Timing Diagram for a CPU Read Cycle

- Table 7 - CPU Read Cycle

- 12.5.4 Local Frame Buffer ZBT SRAM Memory Interface

- 12.5.4.1 Local ZBT SRAM Memory Interface A

- Figure 11 - Local Memory Interface � Input setup and hold timing

- Figure 12 - Local Memory Interface - Output valid delay timing

- Table 8 - AC Characteristics � Local frame buffer ZBT-SRAM Memory Interface A

- 12.5.4.2 Local ZBT SRAM Memory Interface B

- Figure 13 - Local Memory Interface � Input setup and hold timing

- Figure 14 - Local Memory Interface - Output valid delay timing

- Table 9 - AC Characteristics � Local frame buffer ZBT-SRAM Memory Interface B

- 12.5.5 Local Switch Database SBRAM Memory Interface

- 12.5.5.1 Local SBRAM Memory Interface

- Figure 15 - Local Memory Interface � Input setup and hold timing

- Figure 16 - Local Memory Interface - Output valid delay timing

- Table 10 - AC Characteristics � Local Switch Database SBRAM Memory Interface

- 12.5.6 Media Independent Interface

- Figure 17 - AC Characteristics � Media Independent Interface

- Figure 18 - AC Characteristics � Media Independent Interface

- Table 11 - AC Characteristics � Media Independent Interface

- 12.5.7 Gigabit Media Independent Interface

- Figure 19 - AC Characteristics - GMII

- Figure 20 - AC Characteristics � Gigabit Media Independent Interface

- Table 12 - AC Characteristics � Gigabit Media Independent Interface (continued)

- 12.5.8 PCS Interface

- Figure 21 - AC Characteristics � PCS Interface

- Figure 22 - AC Characteristics � PCS Interface

- Table 13 - AC Characteristics � PCS Interface (continued)

- 12.5.9 LED Interface

- Figure 23 - AC Characteristics � LED Interface

- Table 14 - AC Characteristics � LED Interface

- 12.5.10 MDIO Input Setup and Hold Timing

- Figure 24 - MDIO Input Setup and Hold Timing

- Figure 25 - MDIO Output Delay Timing

- Table 15 - MDIO Timing

- 12.5.11 I2C Input Setup Timing

- Figure 26 - I2C Input Setup Timing

- Figure 27 - I2C Output Delay Timing

- Table 16 - I2C Timing

- 12.5.12 Serial Interface Setup Timing

- Figure 28 - Serial Interface Setup Timing

- Figure 29 - Serial Interface Output Delay Timing

- Table 17 - Serial Interface Timing

1

Zarlink Semiconductor Inc.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright 2003, Zarlink Semiconductor Inc. All Rights Reserved.

Features

� 8 Gigabit Ports with GMII and PCS interface

- Gigabit Port can also support 100/10 Mbps MII

interface

- Provide Hot plug support for GMII/PCS module

- 2 Gigabit ports can be aggregated into 2Gbps

Stacking port working with VTX2600 in stacking

mode

� High Performance Layer 2 Packet Forwarding

(11.904M packets per second) and Filtering at

Full-Wire Speed

� Maximum throughput is 8 Gbps non-blocking

� Centralized shared-memory architecture

� Consists of two Memory Domains at 133 MHz

- Frame Buffer Domain: Two banks of ZBT-SRAM

with 2M/4MB total

- Switch Database Domain with 256K/512K

SRAM

� Up to 64K MAC addresses to provide large node

aggregation in wiring closet switches

� Provides Port based and ID Tagged VLAN

(IEEE802.1Q) up to 4K VLAN

� Support IP Multicast with IGMP snooping up to

64K groups.

� Traffic Classification

� Classify traffic into 8 transmission priorities per

port

� Supports Delay Bounded, Strict Priority, and WFQ

� Provides 2 level dropping precedence with WRED

mechanism

- User controlled thresholds for WRED

� Classification based on layer 2, 3 markings

- VLAN Priority field in VLAN tagged frame

- DS/TOS field in IP packet

� The precedence of above two classifications can

be programmable

October 2003

Ordering Information

MVTX2804AG

596 Pin HSBGA

-40

�C to +85�C

MVTX2804

8-Port 1000 Mbps Ethernet

Distributed Switch

Data Sheet

Figure 1 - MVTX2804AG Functional Block Diagram

Frame Data Buffer A

ZBT-SRAM (1M/2MB)

Frame Data Buffer B

ZBT-SRAM (1M/2MB)

SRAM 256/512K

SW Database

MAC Table

Frame

Engine

Scheduler

FDB Interface

SDB Interface

Search

Engine

64bit

64bit

32bit

NM

D

a

tabase

GMII

/PCS

Port 0

GMII

/PCS

Port 1

GMII

/PCS

Port 2

GMII

/PCS

Port 3

GMII

/PCS

Port 4

GMII

/PCS

Port 5

GMII

/PCS

Port 6

GMII

/PCS

Port 7

16/8bit-

Bus/

Serial

Management

Module

CPU

VTX2804

LED

MVTX2804

Data Sheet

2

Zarlink Semiconductor Inc.

QoS Support

Description

The MVTX2800AG family is a group of 8-port 1000 Mbps non-blocking Ethernet switch chips with on-chip address

memory. A single chip provides a maximum of eight 1000 Mbps ports and a dedicated CPU interface with a 16/8-bit

bus for managed and unmanaged switch applications. The VTX2800 family consists of the following four products:

� VTX2804 8 Gigabit ports Managed

� VTX2803 8 Gigabit ports Unmanaged

� VTX2802 4 Gigabit ports Managed

� VTX2801 4 Gigabit ports Unmanaged

The MVTX2804AG supports up to 64K MAC addresses to aggregate traffic from multiple wiring closet stacks. The

centralized shared-memory architecture allows a very high performance packet-forwarding rate of 11.904M packets

per second at full wire speed. The chip is optimized to provide a low-cost, high performance workgroup, and wiring

closet, layer 2 switching solution with 8 Gigabit Ethernet ports.

Two Frame Buffer Memory domains utilize cost effective, high-performance ZBT-SRAM with aggregated bandwidth

of 16Gbps to support full wire speed on all external ports simultaneously.

With Strict priority, Delay Bounded, and WRR transmission scheduling, plus WRED memory congestion scheme,

the chip provides powerful QoS functions for convergent network multimedia and mission-critical applications. The

chip provides 8 transmission priorities and 2 level drop precedence. Traffic is assigned its transmission priority and

dropping precedence based on the frame VLAN Tag priority or DS/TOS fields in IP packets.

IP multicast snooping provides up to 64k simultaneous IP Multicast groups. With 4K IEEE 802.1Q VLANs, the

MVTX2804AG provides the ability to logically group users to control multicast traffic.

�

Supports IEEE 802.1p/Q Quality of Service with

8 Priority

�

Buffer Management: reserve buffers on per class

and per port basis

�

Port-based Priority: VLAN Priority with Tagged

frame can be overwritten by the priority of PVID

�

QoS features can be configured on a per port

basis

�

Packet Filtering and Port Security

�

Static addressing filtering for source and/or

destination MAC address

�

Static learned MAC addresses will not be aged

out

�

Secure mode per port: Prevent learning for port

in a secure mode

�

Support per MAC per Port filtering

�

Full Duplex Ethernet IEEE 802.3x Flow Control

�

Provides Ethernet Multicast and Broadcast

Control

�

4 Port Trunking groups, 8 ports per group

(Trunking can be based on source MAC and/or

destination MAC and source port)

�

LED signals provided by a serial or parallel

interface

�

CPU interface supports 16/8-bit CPU bus in

managed mode and a synchronous Serial Interface

and I

2

C interface in unmanaged mode

�

SNMP/RMON support with CPU

�

Built-in MIB counter

�

Spanning tree with CPU

�

Multiple Spanning trees (Per Spanning Tree Per

VLAN)

�

Hardware auto-negotiation through serial

management interface (MDIO) for Gigabit Ethernet

ports, supports 10/100/1000 Mbps

�

BIST for internal and external SRAM-ZBT

�

I

2

C EEPROM or synchronous serial port for

configuration

�

Packaged in 596-pin BGA

MVTX2804

Data Sheet

3

Zarlink Semiconductor Inc.

The MVTX2804AG supports port trunking/load sharing on the 1000 Mbps ports with fail-over capability. The port

trunking/load sharing can be used to group ports between interlinked switches to increase the effective network

bandwidth.

In full-duplex mode, IEEE 802.3x flow control is provided. The Physical Coding Sublayer (PCS) is integrated on-

chip to provide a direct 10-bit GMII interface, or the PCS can be bypassed to provide an interface to existing fiber-

based Gigabit Ethernet transceivers.

Statistical information for Etherstat SNMP and Remote Monitoring Management Information Base (RMON MIB) are

collected independently for each of the eight ports. Access to these statistical counter/registers is provided via the

CPU interface. SNMP Management frames can be received and transmitted via the CPU interface, creating a

complete network management solution.

The MVTX2804AG is fabricated using 0.25mm technology. Inputs, however, are 3.3V tolerant and the outputs are

capable of directly interfacing to LVTTL levels. The MVTX2804AG is packaged in a 596-pin Ball Grid Array

package.

MVTX2804

Data Sheet

Table of Contents

4

Zarlink Semiconductor Inc.

1.0 Block Functionality . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

1.1 Frame Data Buffer (FDB) Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

1.2 Switch Database (SDB) Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

1.3 GMII/PCS MAC Module (GMAC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

1.4 CPU Interface Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

1.5 Management Module. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

1.6 Frame Engine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

1.7 Search Engine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

1.8 LED Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

1.9 Internal Memory. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2.0 System Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2.1 Management and Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2.2 Managed Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2.3 Register Configuration, Frame Transmission, and Frame Reception . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

2.3.1 Ethernet Frames . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

2.3.2 Control Frames . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

2.4 Unmanaged Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

2.5 I

2

C Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

2.5.1 Start Condition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

2.5.2 Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

2.5.3 Data Direction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

2.5.4 Acknowledgment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

2.5.5 Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

2.5.6 Stop Condition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

2.6 Synchronous Serial Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

2.6.1 Write Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

2.6.2 Read Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

3.0 Data Forwarding Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

3.1 Unicast Data Frame Forwarding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

3.2 Multicast Data Frame Forwarding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.3 Frame Forwarding To and From CPU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

4.0 Memory Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

4.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

4.2 Detailed Memory Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

5.0 Search Engine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

5.1 Search Engine Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

5.2 Basic Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

5.3 Search, Learning, and Aging . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

5.3.1 MAC Search. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

5.3.2 Learning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

5.3.3 Aging . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

5.3.4 Data Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

5.3.5 VLAN Port Association Table. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

6.0 Frame Engine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

6.1 Data Forwarding Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

6.2 Frame Engine Details . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

6.2.1 FCB Manager. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

6.2.2 Rx Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

6.2.3 RxDMA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

6.2.4 TxQ Manager . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

6.3 Port Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

6.4 TxDMA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

MVTX2804

Data Sheet

Table of Contents

5

Zarlink Semiconductor Inc.

7.0 Quality of Service and Flow Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

7.1 Model. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

7.2 Four QoS Configurations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

7.3 Delay Bound . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

7.4 Strict Priority and Best Effort . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

7.5 Weighted Fair Queuing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

7.6 Shaper . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

7.7 WRED Drop Threshold Management Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

7.8 Buffer Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

7.8.1 Dropping When Buffers Are Scarce . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

7.9.1 Unicast Flow Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

7.9.2 Multicast Flow Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

7.10 Mapping to IETF Diffserv Classes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

8.0 Port Trunking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

8.1 Features and Restrictions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

8.2 Unicast Packet Forwarding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

8.3 Multicast Packet Forwarding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

8.4 Preventing Multicast Packets from Looping Back to the Source Trunk. . . . . . . . . . . . . . . . . . . . . . . . . . . 36

9.0 LED Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

9.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

9.2 Serial Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

9.3 Parallel Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

9.4 LED Control Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

10.0 Hardware Statistics Counter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

10.1 Hardware Statistics Counters List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

10.2 IEEE 802.3 HUB Management (RFC 1213) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

10.2.1 Event Counters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

10.2.1.1 READABLEOCTET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

10.2.1.2 READABLEFRAME . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

10.2.1.3 FCSERRORS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

10.2.1.4 ALIGNMENTERRORS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

10.2.1.5 FRAMETOOLONGS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

10.2.1.6 SHORTEVENTS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

10.2.1.7 RUNTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

10.2.1.8 COLLISIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

10.2.1.9 LATEEVENTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

10.2.1.10 VERYLONGEVENTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

10.2.1.11 DATARATEMISATCHES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

10.2.1.12 AUTOPARTITIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

10.2.1.13 TOTALERRORS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

10.3 IEEE - 802.1 Bridge Management (RFC 1286) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

10.3.0.1 Event Counters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

10.3.0.3 OUTFRAMES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

10.3.0.4 INDISCARDS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

10.3.0.5 DELAYEXCEEDEDDISCARDS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

10.3.0.6 MTUEXCEEDEDDISCARDS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

10.4 RMON - Ethernet Statistic Group (RFC 1757) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

10.4.1 Event Counters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

10.4.1.1 DROP EVENTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

10.4.1.2 OCTETS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

10.4.1.3 BROADCASTPKTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

10.4.1.4 MULTICASTPKTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43