# TECHNICAL MANUAL

# LSI53C770 Ultra SCSI I/O Processor

Version 2.1 March 2001

This document contains proprietary information of LSI Logic Corporation. The information contained herein is not to be used by or disclosed to third parties without the express written permission of an officer of LSI Logic Corporation.

LSI Logic products are not intended for use in life-support appliances, devices, or systems. Use of any LSI Logic product in such applications without written consent of the appropriate LSI Logic officer is prohibited.

Document DB14-000161-00, First Edition (March 2001) This document describes the LSI Logic LSI53C770 Ultra SCSI I/O Processor and will remain the official reference source for all revisions/releases of this product until rescinded by an update.

#### To receive product literature, visit us at http://www.lsilogic.com.

LSI Logic Corporation reserves the right to make changes to any products herein at any time without notice. LSI Logic does not assume any responsibility or liability arising out of the application or use of any product described herein, except as expressly agreed to in writing by LSI Logic; nor does the purchase or use of a product from LSI Logic convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of LSI Logic or third parties.

Copyright © 1995–2001 by LSI Logic Corporation. All rights reserved.

#### TRADEMARK ACKNOWLEDGMENT

The LSI Logic logo design, SCRIPTS, and TolerANT are trademarks or registered trademarks of LSI Logic Corporation. All other brand and product names may be trademarks of their respective companies.

# Preface

This technical manual provides reference information on the LSI53C770 Ultra SCSI I/O Processor. It contains a complete functional description for the product and includes complete physical and electrical specifications for it.

#### Audience

This manual assumes some prior knowledge of current and proposed SCSI and PCI standards.

#### Organization

This document has the following chapters and appendix:

- Chapter 1, General Description

- Chapter 2, Functional Description

- Chapter 3, Signal Descriptions

- Chapter 4, **Registers**

- Chapter 5, Instruction Set of the I/O Processor

- Chapter 6, Electrical Characteristics

- Appendix A, Register Summary

#### **Related Publications**

For background information, please contact:

#### ANSI

11 West 42nd Street New York, NY 10036 (212) 642-4900 Ask for document number X3.131-199X (SCSI-2)

#### **Global Engineering Documents**

15 Inverness Way East Englewood, CO 80112 (800) 854-7179 or (303) 397-7956 (outside U.S.) FAX (303) 397-2740 Ask for document number X3.131-1994 (SCSI-2) or X3.253 (SCSI-3 Parallel Interface)

#### **ENDL** Publications

14426 Black Walnut Court

Saratoga, CA 95070

(408) 867-6642

Document names: SCSI Bench Reference, SCSI Encyclopedia, SCSI Tutor

#### **Prentice Hall**

113 Sylvan Avenue

Englewood Cliffs, NJ 07632

(800) 947-7700

Ask for document number ISBN 0-13-796855-8, SCSI: Understanding the Small Computer System Interface

#### LSI Logic World Wide Web Home Page

www.lsil.com

#### **PCI Special Interest Group**

2575 N. E. Katherine Hillsboro, OR 97214 (800) 433-5177; (503) 693-6232 (International); FAX (503) 693-8344

#### **Conventions Used in This Manual**

The first time a word or phrase is defined in this manual, it is *italicized*.

The word *assert* means to drive a signal true or active. The word *deassert* means to drive a signal false or inactive. Signals that are active LOW end in a "/."

Hexadecimal numbers are indicated by the prefix "0x" —for example, 0x32CF. Binary numbers are indicated by the prefix "0b" —for example, 0b0011.0010.1100.1111.

#### **Revision Record**

| Version | Date | Remarks                                            |

|---------|------|----------------------------------------------------|

| 1.0     | 9/94 | Preliminary.                                       |

| 2.0     | 7/96 | Changed Fast-20 to Ultra SCSI throughout document. |

| 2.1     | 3/01 | All product names changed from SYM to LSI.         |

# Contents

| Chapter 1 | Gen  | eral Des  | cription                             |      |  |  |

|-----------|------|-----------|--------------------------------------|------|--|--|

|           | 1.1  | Benefit   | s of Ultra SCSI                      | 1-2  |  |  |

|           |      | 1.1.1     | TolerANT <sup>®</sup> Technology     | 1-2  |  |  |

|           | 1.2  | LSI530    | C770 Features Summary                | 1-3  |  |  |

|           |      | 1.2.1     | Performance                          | 1-3  |  |  |

|           |      | 1.2.2     | Integration                          | 1-4  |  |  |

|           |      | 1.2.3     | Ease of Use                          | 1-4  |  |  |

|           |      | 1.2.4     | Flexibility                          | 1-5  |  |  |

|           |      | 1.2.5     | Reliability                          | 1-5  |  |  |

|           |      | 1.2.6     | Testability                          | 1-6  |  |  |

|           | 1.3  | Summa     | ary of New Features in the LSI53C770 | 1-8  |  |  |

| Chapter 2 | Fund | ctional D | escription                           |      |  |  |

|           | 2.1  | SCSI (    | 2-1                                  |      |  |  |

|           |      | 2.1.1     | DMA Core                             | 2-2  |  |  |

|           | 2.2  | SCRIP     | SCRIPTS Processor                    |      |  |  |

|           |      | 2.2.1     | Internal SCRIPTS RAM                 | 2-3  |  |  |

|           |      | 2.2.2     | Designing an Ultra SCSI System       | 2-4  |  |  |

|           |      | 2.2.3     | Using the SCSI Clock Doubler         | 2-5  |  |  |

|           |      | 2.2.4     | Big/Little Endian Support            | 2-6  |  |  |

|           |      | 2.2.5     | Big Endian Mode                      | 2-7  |  |  |

|           |      | 2.2.6     | Little Endian Mode                   | 2-7  |  |  |

|           |      | 2.2.7     | Loopback Mode                        | 2-7  |  |  |

|           |      | 2.2.8     | Parity Options                       | 2-8  |  |  |

|           | 2.3  | DMA F     | IFO                                  | 2-12 |  |  |

|           |      | 2.3.1     | Data Path                            | 2-12 |  |  |

|           |      | 2.3.2     | DMA FIFO                             | 2-13 |  |  |

|           |      | 2.3.3     | Asynchronous SCSI Send               | 2-14 |  |  |

|           |      | 2.3.4     | Synchronous SCSI Send                | 2-14 |  |  |

|           | 0.2        | 5.2.1                     | First Dword                                     | 5-3          |

|-----------|------------|---------------------------|-------------------------------------------------|--------------|

|           | 5.1<br>5.2 |                           | SCRIPTS<br>Move Instruction                     | 5-1<br>5-3   |

| Chapter 5 |            |                           | et of the I/O Processor                         | F 4          |

| Chapter 4 | -          | i <b>sters</b><br>Registe | er Descriptions                                 | 4-1          |

| Chapter 3 | Sign       | al Descr                  | iptions                                         |              |

|           |            | 2.7.7                     | Sample Interrupt Service Routine                | 2-34         |

|           |            | 2.7.6                     | Halting in an Orderly Fashion                   | 2-33         |

|           |            | 2.7.5                     | Stacked Interrupts                              | 2-32         |

|           |            | 2.7.4                     | Enabling Interrupts                             | 2-31         |

|           |            | 2.7.3                     | Fatal vs. Nonfatal Interrupts                   | 2-31         |

|           |            | 2.7.2                     | Registers                                       | 2-29         |

|           |            | 2.7.1                     | Polling vs. Hardware Interrupts                 | 2-29         |

|           | 2.7        |                           | ot Handling                                     | 2-29         |

|           |            | 2.6.5                     | Ultra SCSI Synchronous Data Transfers           | 2-28         |

|           |            | 2.6.4                     |                                                 | 2-27         |

|           |            | 2.6.3                     | Synchronous Operation                           | 2-26         |

|           |            | 2.6.2                     | Select/Reselect During Selection/Reselection    | 2-26         |

|           | 2.0        | 2.6.1                     | SCSI Termination                                | 2-23         |

|           | 2.6        |                           | Bus Interface                                   | 2-23         |

|           | 2.5        |                           | tional STERM/-TA/-ReadyIn/                      | 2-21         |

|           |            | 2.4.0                     | Using the Back Off Signal to Relinquish the Bus | 2-19         |

|           |            | 2.4.7                     | Cache Line Burst                                | 2-19         |

|           |            | 2.4.0                     | Bus Retry<br>Noncache Line Burst                | 2-19         |

|           |            | 2.4.5<br>2.4.6            | Functionality of BERR/_TEA/ in Slave Mode       | 2-18<br>2-19 |

|           |            | 2.4.4                     | Functionality of BERR/_TEA/ in Master Mode      | 2-18         |

|           |            | 2.4.3                     | BERR/_TEA/ Pin Function                         | 2-18         |

|           |            | 2.4.2                     | Transfer Size Throttling                        | 2-15         |

|           |            | 2.4.1                     | Misaligned Transfers                            | 2-15         |

|           | 2.4        |                           | terface                                         | 2-15         |

|           |            | 2.3.6                     | Synchronous SCSI Receive                        | 2-15         |

|           |            | 2.3.5                     | Asynchronous SCSI Receive                       | 2-14         |

|           |       | 5.2.2                    | Second Dword                         | 5-9  |  |  |

|-----------|-------|--------------------------|--------------------------------------|------|--|--|

|           | 5.3   | I/O Inst                 | ructions                             | 5-10 |  |  |

|           |       | 5.3.1                    | First Dword                          | 5-10 |  |  |

|           |       | 5.3.2                    | Second Dword                         | 5-17 |  |  |

|           | 5.4   | Read/V                   | Vrite Instructions                   | 5-18 |  |  |

|           |       | 5.4.1                    | First Dword                          | 5-18 |  |  |

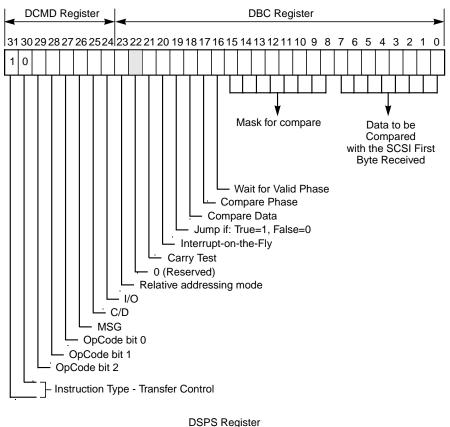

|           | 5.5   | Transfe                  | r Control Instructions               | 5-22 |  |  |

|           |       | 5.5.1                    | First Dword                          | 5-22 |  |  |

|           |       | 5.5.2                    | Second Dword                         | 5-29 |  |  |

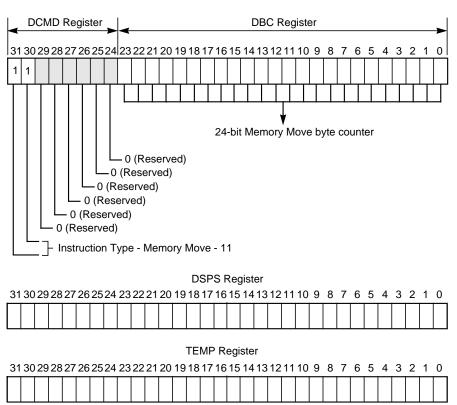

|           | 5.6   | Memor                    | y Move Instructions                  | 5-30 |  |  |

|           |       | 5.6.1                    | First Dword                          | 5-31 |  |  |

|           |       | 5.6.2                    | Second Dword                         | 5-32 |  |  |

| Chapter 6 | Elect | rical Ch                 | aracteristics                        |      |  |  |

|           | 6.1   | DC Ch                    | aracteristics                        | 6-2  |  |  |

|           | 6.2   | LSI Log                  | gic TolerANT Technology              | 6-6  |  |  |

|           | 6.3   | AC Cha                   | aracteristics                        | 6-10 |  |  |

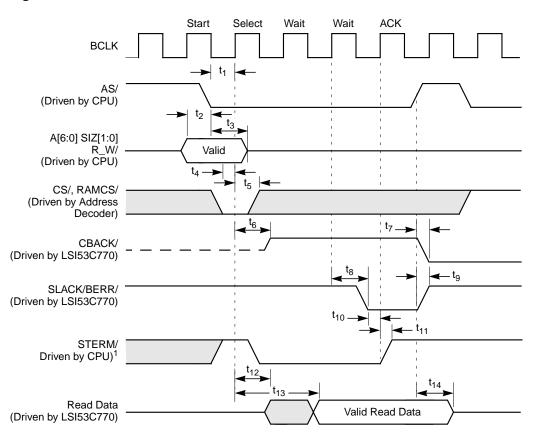

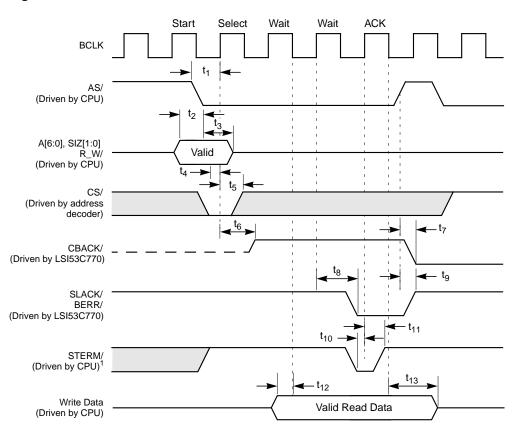

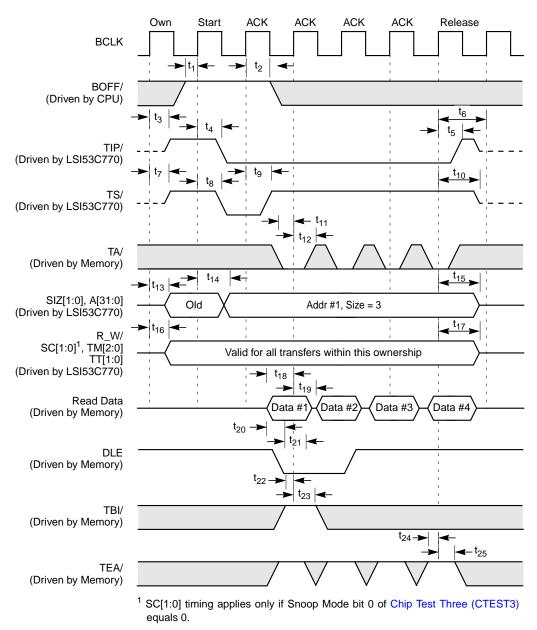

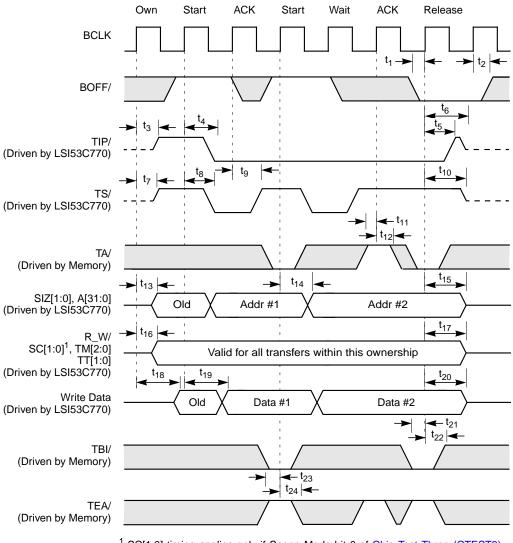

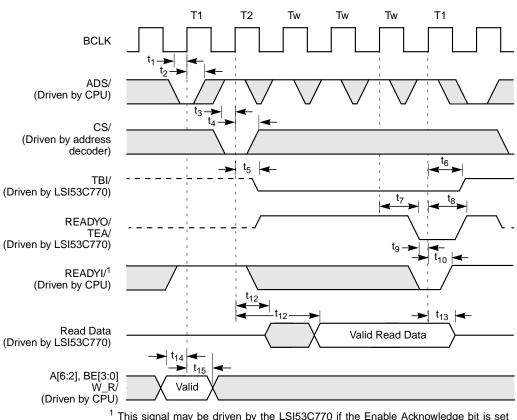

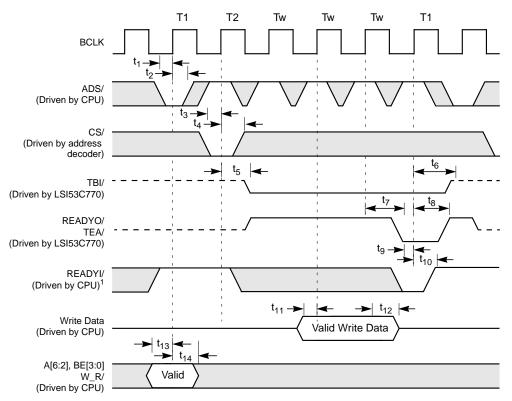

|           | 6.4   | 4 Bus Mode 1 Slave Cycle |                                      |      |  |  |

|           |       | 6.4.1                    | Bus Mode 1 Slave Read Sequence       | 6-12 |  |  |

|           |       | 6.4.2                    | Bus Mode 1 Slave Write Sequence      | 6-15 |  |  |

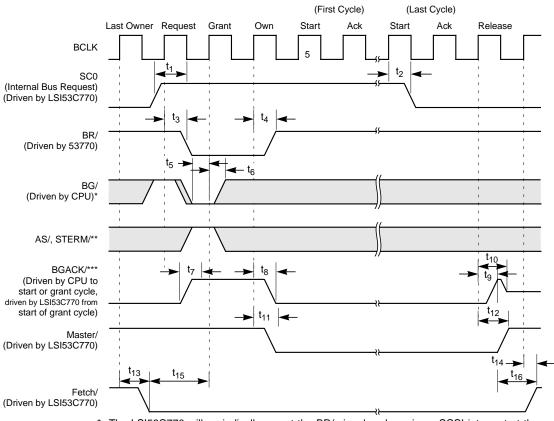

|           | 6.5   | Bus Mo                   | ode 1 Host Bus Arbitration           | 6-18 |  |  |

|           |       | 6.5.1                    | Bus Arbitration Sequence             | 6-18 |  |  |

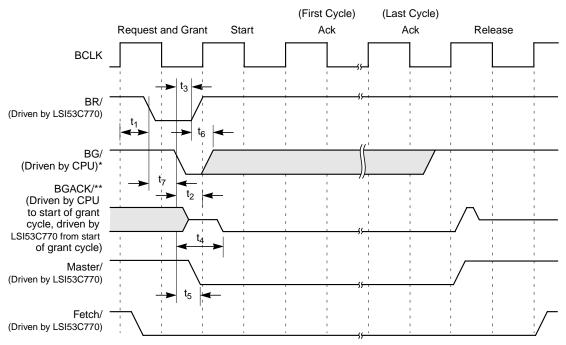

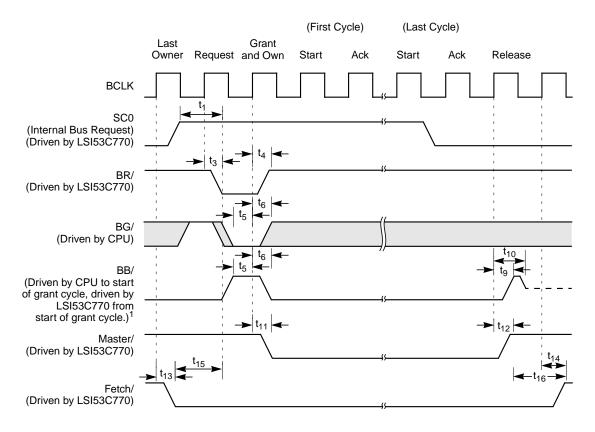

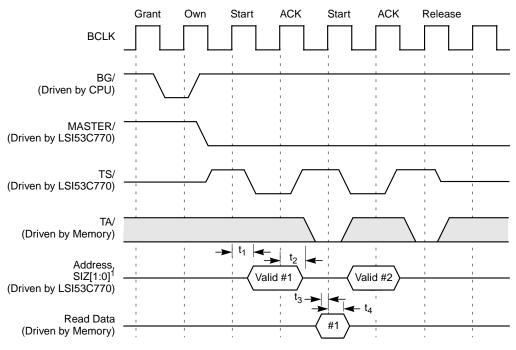

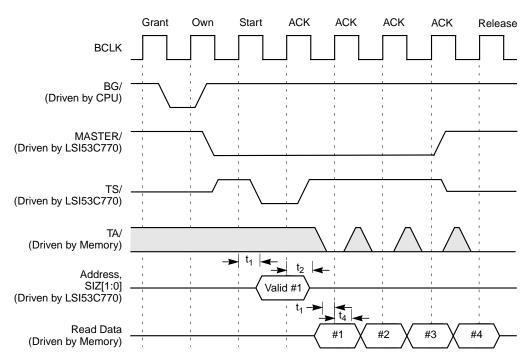

|           | 6.6   | Bus Mo                   | ode 1 Fast Arbitration               | 6-21 |  |  |

|           |       | 6.6.1                    | Fast Arbitration Sequence            | 6-21 |  |  |

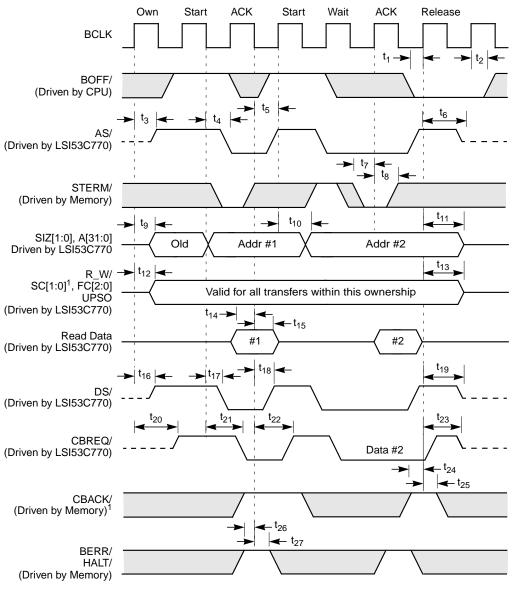

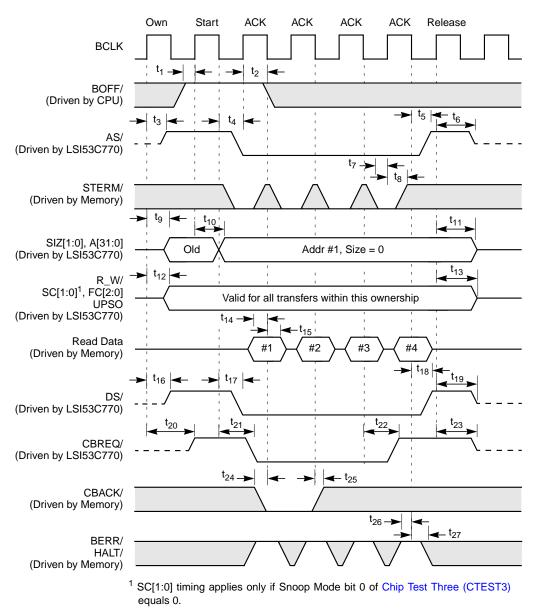

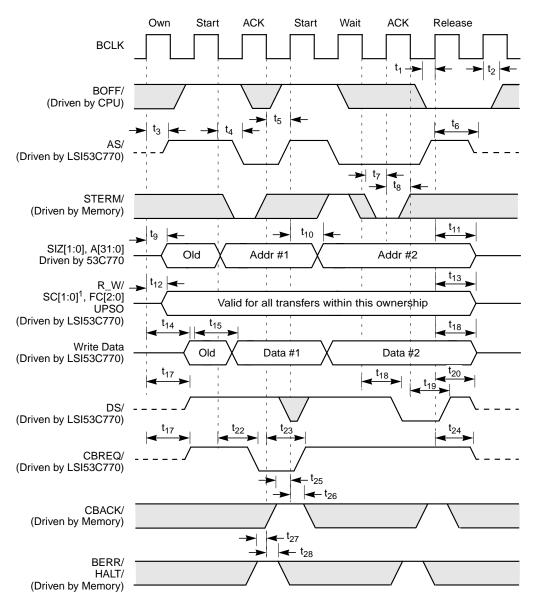

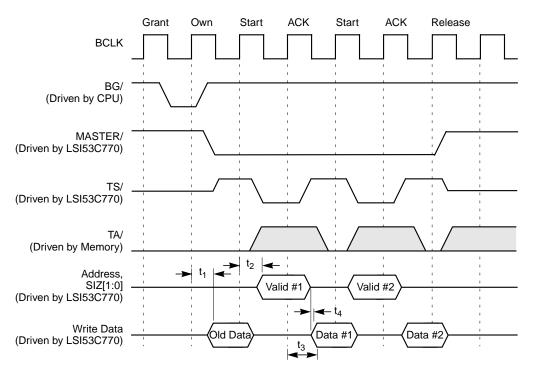

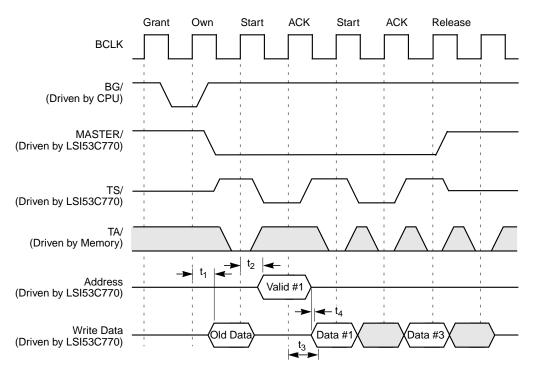

|           | 6.7   | Bus Mo                   | ode 1 Master Cycle                   | 6-24 |  |  |

|           |       | 6.7.1                    | Bus Mode 1 Master Read Sequence      | 6-24 |  |  |

|           |       | 6.7.2                    | Bus Mode 1 Bus Master Write Sequence | 6-28 |  |  |

|           | 6.8   | Bus Mo                   | ode 2 Slave Cycle                    | 6-32 |  |  |

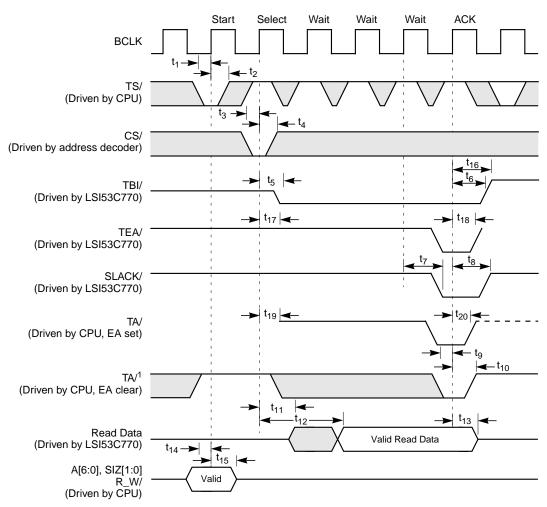

|           |       | 6.8.1                    | Bus Mode 2 Slave Read Sequence       | 6-32 |  |  |

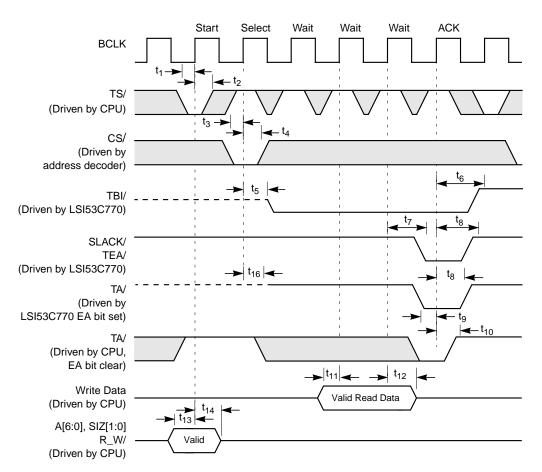

|           |       | 6.8.2                    | Bus Mode 2 Slave Write Sequence      | 6-35 |  |  |

|           | 6.9   | Bus Mo                   | ode 2 Host Bus Arbitration           | 6-38 |  |  |

|           |       | 6.9.1                    | Bus Mode 2 Bus Arbitration Sequence  | 6-38 |  |  |

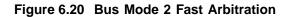

|           | 6.10  | Bus Mo                   | ode 2 Fast Arbitration               | 6-41 |  |  |

|           |       | 6.10.1                   | Bus Mode 2 Fast Arbitration Sequence | 6-41 |  |  |

|           | 6.11  | Bus Mo                   | ode 2 Master Cycle                   | 6-43 |  |  |

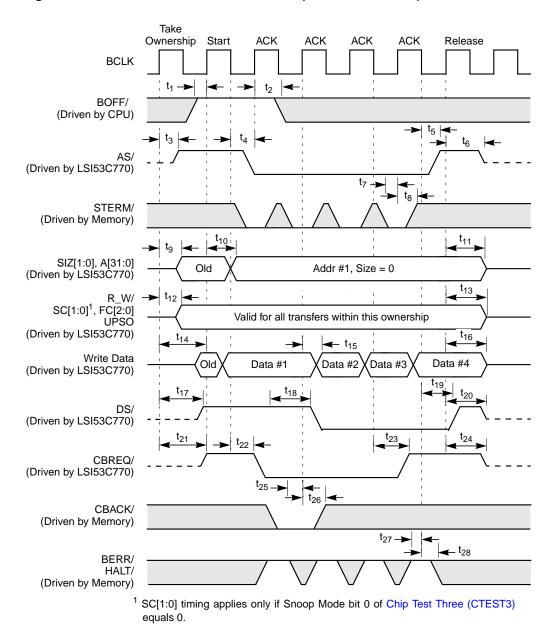

|           |       | 6.11.1                   | Bus Mode 2 Master Read Sequence      | 6-43 |  |  |

|           |       | 6.11.2                   | Bus Mode 2 Bus Master Write Sequence | 6-47 |  |  |

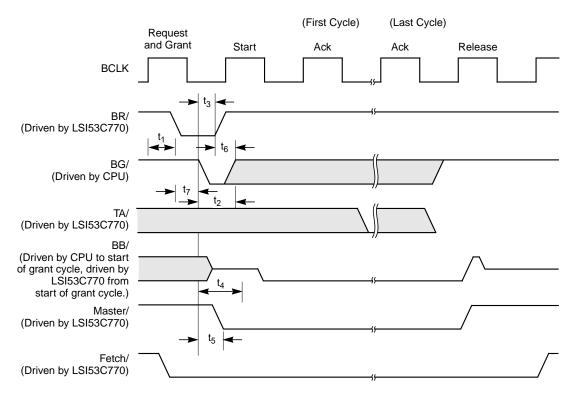

| 6 | 6.12 | Bus Mod  | le 2 Mux Mode Cycle                        | 6-50 |

|---|------|----------|--------------------------------------------|------|

|   |      | 6.12.1   | Mux Mode Read Sequence                     | 6-50 |

|   |      | 6.12.2   | Mux Mode Write Sequence                    | 6-54 |

| 6 | 6.13 | Bus Mo   | de 3 and 4 Slave Cycle                     | 6-57 |

|   |      | 6.13.1   | Bus Mode 3 and 4 Slave Read Sequence       | 6-57 |

|   |      | 6.13.2   | Bus Mode 3 and 4 Slave Write Sequence      | 6-61 |

| 6 | 6.14 | Bus Mod  | le 3 and 4 Host Bus Arbitration            | 6-64 |

|   |      | 6.14.1   | Bus Arbitration Sequence                   | 6-64 |

| 6 | 6.15 | Bus Mod  | le 3 and 4 Fast Arbitration                | 6-67 |

|   |      | 6.15.1   | Fast Arbitration Sequence                  | 6-67 |

| 6 | 6.16 | Bus Mod  | le 3 and 4 Master Cycle                    | 6-70 |

|   |      | 6.16.1   | Bus Mode 3 and 4 Bus Master Read Sequence  | 6-70 |

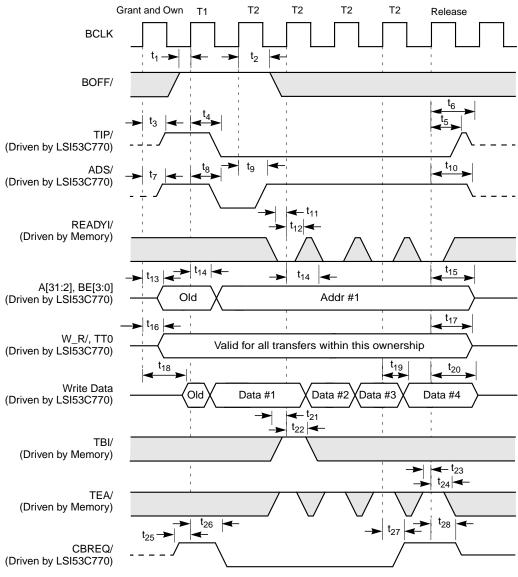

|   |      | 6.16.2   | Bus Mode 3 and 4 Bus Master Write Sequence | 6-76 |

| 6 | 6.17 | SCSI Tir | ning Diagrams                              | 6-82 |

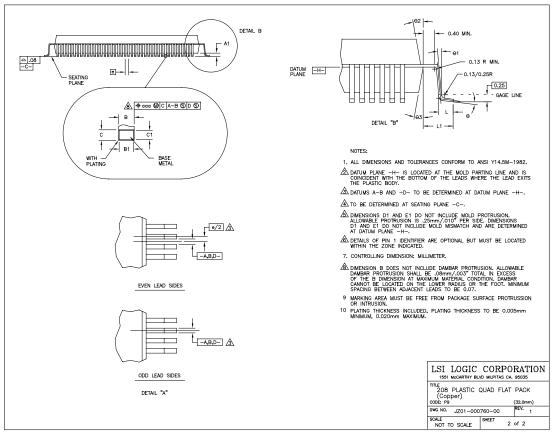

| 6 | 6.18 | Package  | Drawings                                   | 6-89 |

|   |      |          |                                            |      |

Appendix A Register Summary

Index

#### **Customer Feedback**

## Figures

| 1.1 | LSI53C770 Block Diagram                        | 1-7  |

|-----|------------------------------------------------|------|

| 2.1 | DMA FIFO Byte Lanes                            | 2-12 |

| 2.2 | LSI53C770 Data Paths                           | 2-13 |

| 2.3 | Transfer Size Throttling                       | 2-17 |

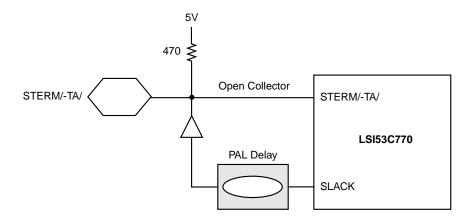

| 2.4 | SLACK/ Tied Back to STERM/, EA Bit Not Set     | 2-22 |

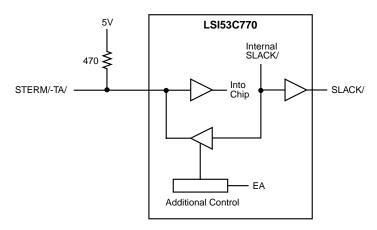

| 2.5 | Bidirectional STERM/, EA Bit Set               | 2-22 |

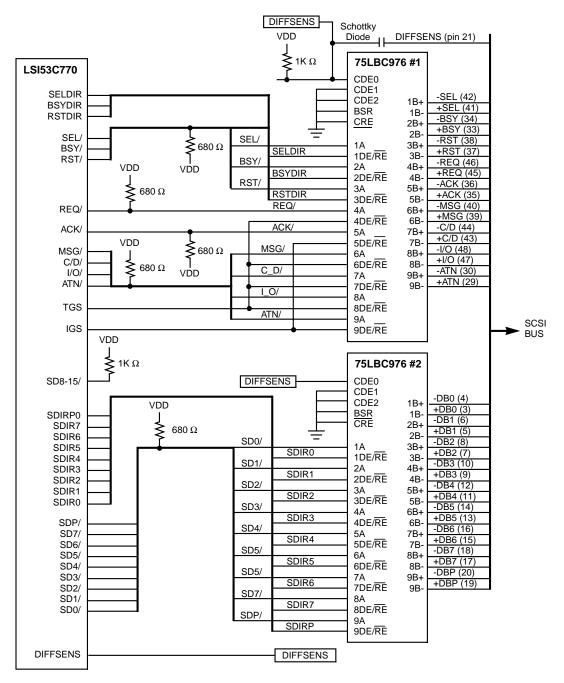

| 2.6 | LSI53C770 Differential Wiring Diagram          | 2-24 |

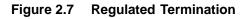

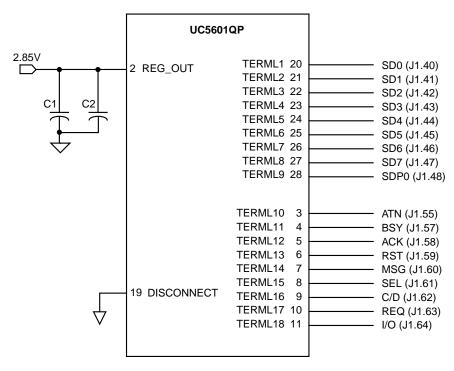

| 2.7 | Regulated Termination                          | 2-25 |

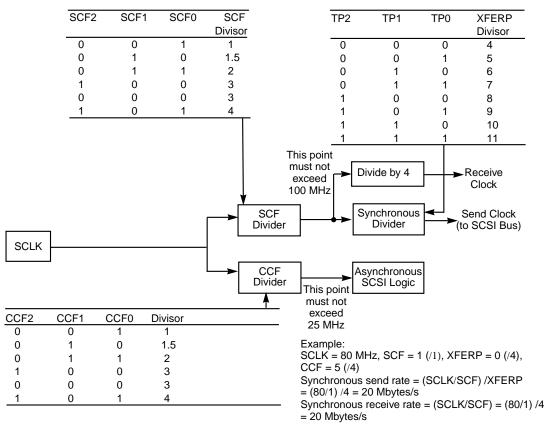

| 2.8 | Determining the Synchronous Transfer Rate      | 2-27 |

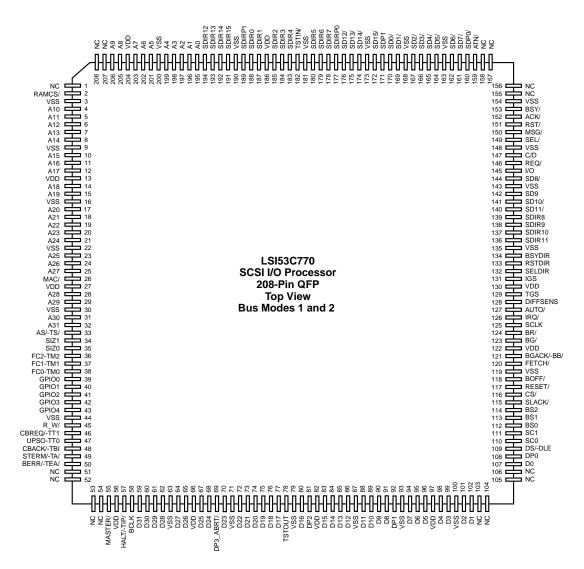

| 3.1 | LSI53C770 Pin Diagram, Bus Modes 1 and 2       | 3-2  |

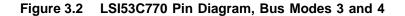

| 3.2 | LSI53C770 Pin Diagram, Bus Modes 3 and 4       | 3-3  |

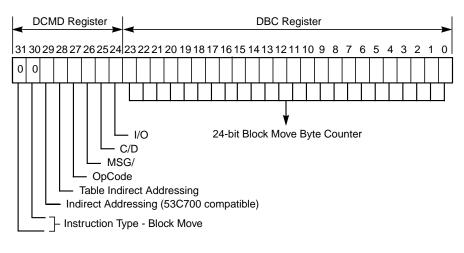

| 5.1 | Block Move Instruction Register                | 5-3  |

| 5.2 | Block Move and Chained Block Move Instructions | 5-9  |

|     |                                                |      |

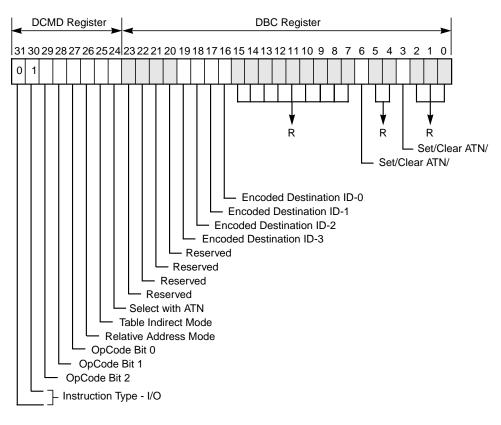

| 5.3  | I/O Instruction Register                        | 5-11 |

|------|-------------------------------------------------|------|

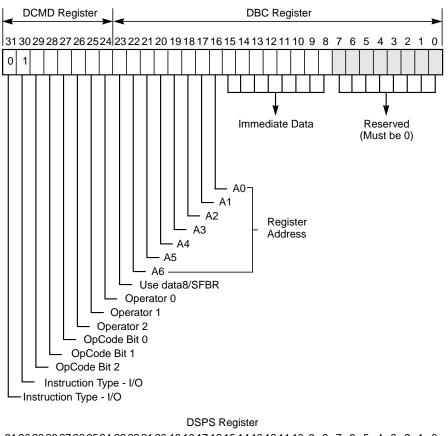

| 5.4  | Read/Write Instruction Register                 | 5-19 |

| 5.5  | Transfer Control Instruction Register           | 5-24 |

| 5.6  | Memory Move Instruction Register                | 5-31 |

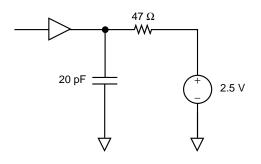

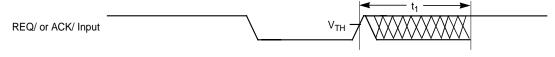

| 6.1  | Rise and Fall Time Test Conditions              | 6-8  |

| 6.2  | SCSI Input Filtering                            | 6-8  |

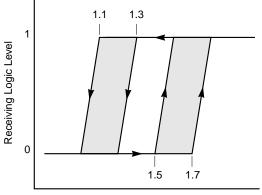

| 6.3  | Hysteresis of SCSI Receiver                     | 6-8  |

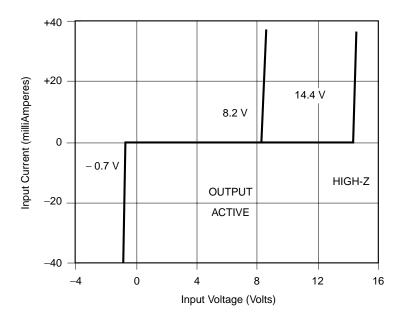

| 6.4  | Input Current as a Function of Input Voltage    | 6-9  |

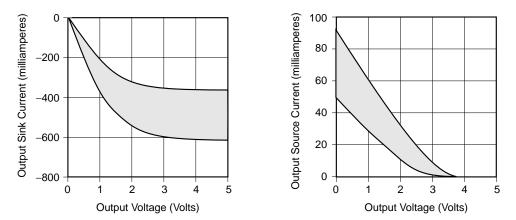

| 6.5  | Output Current as a Function of Output Voltage  | 6-9  |

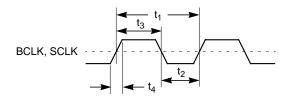

| 6.6  | Clock Waveform                                  | 6-10 |

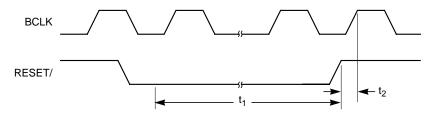

| 6.7  | Reset Input Waveforms                           | 6-11 |

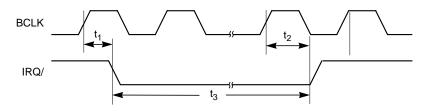

| 6.8  | Interrupt Output Waveforms                      | 6-11 |

| 6.9  | Bus Mode 1 Slave Read Waveforms                 | 6-13 |

| 6.10 | Bus Mode 1 Slave Write Waveforms                | 6-16 |

| 6.11 | Bus Mode 1 Host Bus Arbitration                 | 6-19 |

| 6.12 | Bus Mode 1 Fast Arbitration                     | 6-22 |

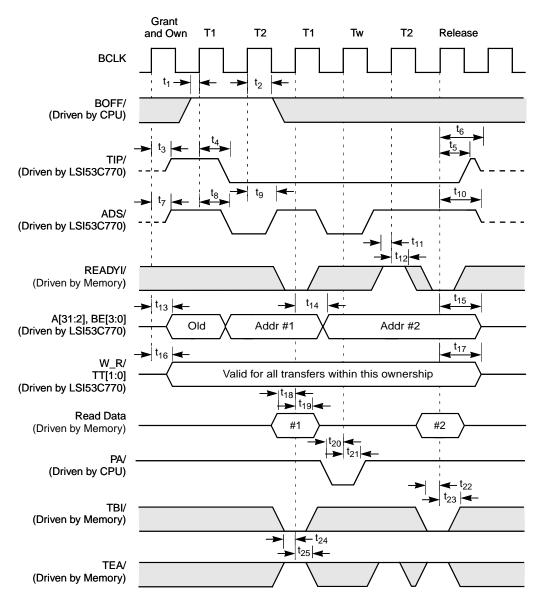

| 6.13 | Bus Mode 1 Bus Master Read (Cache Line Burst    |      |

|      | Requested but not Acknowledged)                 | 6-25 |

| 6.14 | Bus Mode 1 Bus Master Read (Cache Line Burst)   | 6-26 |

| 6.15 | Bus Mode 1 Bus Master Write (Cache Line Burst   |      |

|      | Requested but not Acknowledged)                 | 6-29 |

| 6.16 | Bus Mode 1 Bus Master Write (Cache Line Burst)  | 6-30 |

| 6.17 | Bus Mode 2 Slave Read Waveforms                 | 6-33 |

| 6.18 | Bus Mode 2 Slave Write Waveforms                | 6-36 |

| 6.19 | Bus Mode 2 Host Bus Arbitration                 | 6-39 |

| 6.20 | Bus Mode 2 Fast Arbitration                     | 6-42 |

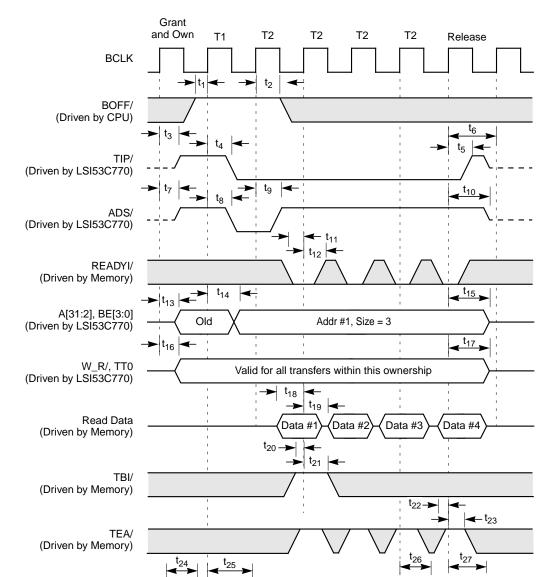

| 6.21 | Bus Mode 2 Bus Master Read (Cache Line Burst    |      |

|      | Requested but not Acknowledged)                 | 6-44 |

| 6.22 | Bus Mode 2 Bus Master Read (Cache Line Burst)   | 6-45 |

| 6.23 | Bus Mode 2 Bus Master Write (Cache Line Burst   |      |

|      | Requested but not Acknowledged)                 | 6-48 |

| 6.24 | Mux Mode Read Cycle (Cache Line Burst Requested |      |

|      | but not Acknowledged)                           | 6-51 |

| 6.25 | Mux Mode Read Cycle (Cache Line Burst)          | 6-52 |

| 6.26 | Mux Mode Write Cycle (Noncache Line Burst)      | 6-55 |

| 6.27 | Mux Mode Write Cycle (Cache Line Burst)         | 6-56 |

| 6.28 | Bus Mode 3 and 4 Slave Read Cycle               | 6-59 |

| 6.29 | Bus Mode 3 and 4 Slave Write Cycle              | 6-62 |

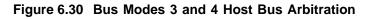

| 6.30 | Bus Modes 3 and 4 Host Bus Arbitration              | 6-65 |

|------|-----------------------------------------------------|------|

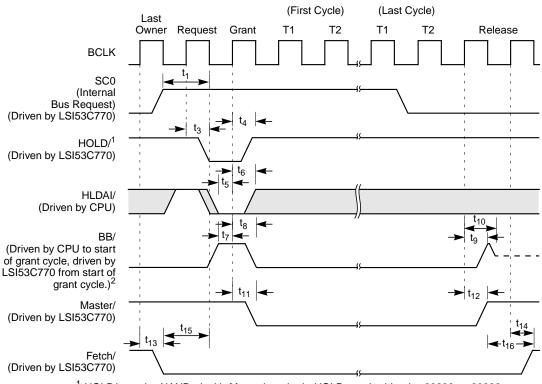

| 6.31 | Bus Mode 3 and 4 Fast Arbitration                   | 6-68 |

| 6.32 | Bus Mode 3 and 4 Bus Master Read                    |      |

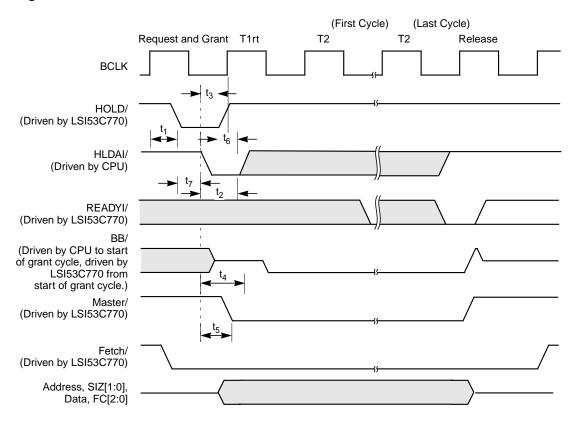

|      | (Nonpreview of Address)                             | 6-71 |

| 6.33 | Bus Mode 3 and 4 Bus Master Read                    |      |

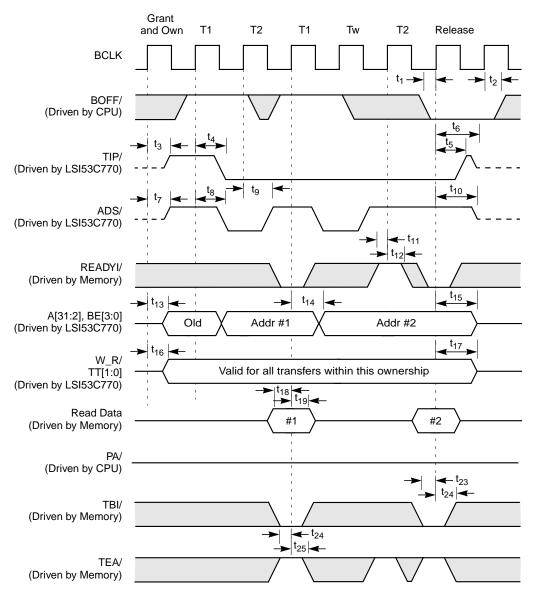

|      | (Preview of Address)                                | 6-72 |

| 6.34 | Bus Mode 4 Bus Master Read (Cache Line Burst)       | 6-74 |

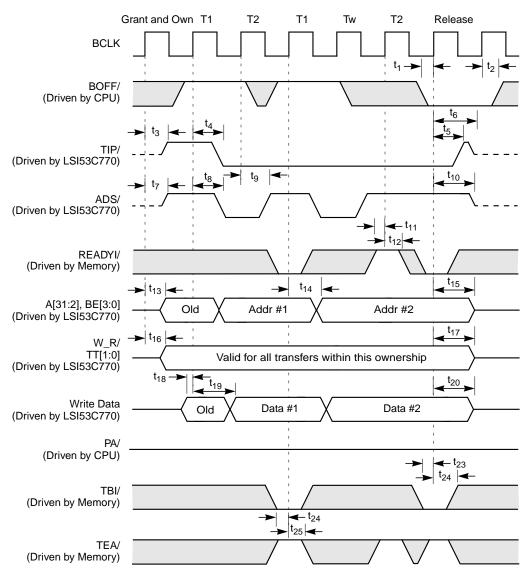

| 6.35 | Bus Mode 3 and 4 Bus Master Write                   |      |

|      | (Nonpreview of Address)                             | 6-77 |

| 6.36 | Bus Mode 3 and 4 Bus Master Write                   |      |

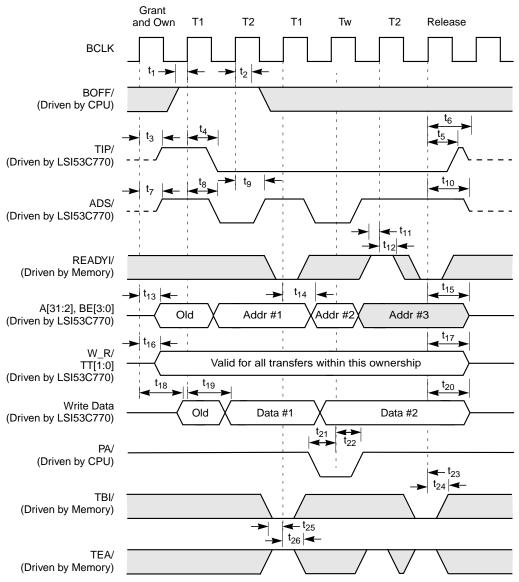

|      | (Preview of Address)                                | 6-78 |

| 6.37 | Bus Mode 4 Bus Master Write (Cache Line Burst)      | 6-80 |

| 6.38 | Initiator Asynchronous Send                         | 6-82 |

| 6.39 | Initiator Asynchronous Receive                      | 6-82 |

| 6.40 | Target Asynchronous Send                            | 6-83 |

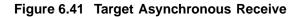

| 6.41 | Target Asynchronous Receive                         | 6-83 |

| 6.42 | Initiator and Target Synchronous Transfers          | 6-84 |

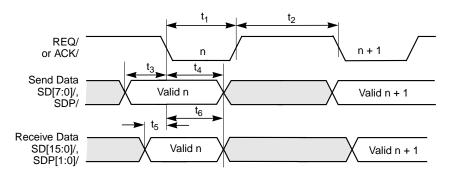

| 6.43 | 208-Pin PQFP (P9) Mechanical Drawing (Sheet 1 of 2) | 6-89 |

## Tables

| 2.1 | Big and Little Endian Addressing                | 2-6  |

|-----|-------------------------------------------------|------|

| 2.2 | Bits Used in Parity Control and Generation      | 2-8  |

| 2.3 | SCSI Parity Control                             | 2-10 |

| 2.4 | Parity Errors and Interrupts                    | 2-11 |

| 3.1 | Power and Ground Signals                        | 3-4  |

| 3.2 | Address and Data Signals                        | 3-4  |

| 3.3 | Arbitration Signals                             | 3-6  |

| 3.4 | System Signals                                  | 3-7  |

| 3.5 | Interface Control Signals                       | 3-9  |

| 3.6 | Additional Interface Signals                    | 3-12 |

| 3.7 | SCSI Signals                                    | 3-14 |

| 4.1 | LSI53C770 Register Address Map                  | 4-2  |

| 4.2 | Examples of Synchronous Transfer Periods and    |      |

|     | Rates for SCSI-1                                | 4-17 |

| 4.3 | Examples of Transfer Periods and Rates for Fast |      |

|     | SCSI and Ultra SCSI                             | 4-18 |

| 4.4 | SCSI Synchronous Data FIFO Word Count           | 4-27 |

| 4.5 | SCRIPTS RAM Access                              | 4-43 |

| 4.6  | FC[2:1], TM[2:1] Pin Function                                                               | 4-49 |

|------|---------------------------------------------------------------------------------------------|------|

| 4.7  | FC0_TM0 Pin Function                                                                        | 4-51 |

| 5.1  | SCSI Information Transfer Phase                                                             | 5-8  |

| 5.2  | Read/Write Instructions                                                                     | 5-20 |

| 5.3  | Transfer Control Instructions                                                               | 5-23 |

| 5.4  | SCSI Phase Comparisons                                                                      | 5-26 |

| 6.1  | Absolute Maximum Stress Ratings                                                             | 6-2  |

| 6.2  | Operating Conditions                                                                        | 6-2  |

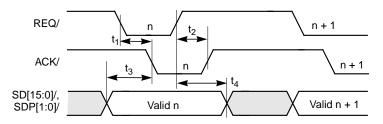

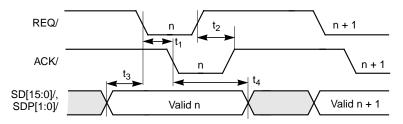

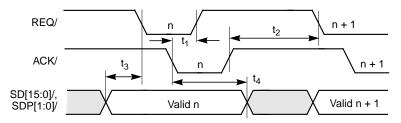

| 6.3  | SCSI Signals SD[15:0], SDP0/, REQ/, MSG/, I_O/,<br>C_D/, ATN/, ACK/, BSY/, SEL/, RST/, SDP1 | 6-3  |

| 6.4  | Input Signals—BG/-HLDAI/, BOFF/, RESET/, CS/,                                               | 00   |

| 0.4  | BS[2:0]/, BCLK, SCLK, AUTO/, DIFFSENS                                                       | 6-3  |

| 6.5  | Input Signal—TSTIN/                                                                         | 6-3  |

| 6.6  | Output Signals—SDIR[15:0], SDIRP0, BSYDIR,                                                  |      |

|      | SELDIR, RSTDIR, TGS, IGS, SDIRP1                                                            | 6-4  |

| 6.7  | Output Signals—FETCH/, IRQ/, TSTOUT                                                         | 6-4  |

| 6.8  | Output Signal—SLACK/-READYO/, MASTER/, MAC/                                                 | 6-4  |

| 6.9  | 3-State Output Signals—A[31:7], FC[2:0]-TM[2:0],                                            |      |

|      | SC[1:0], UPSO-TT0/, CBREQ/-TT1/, BR/-HOLD/                                                  | 6-5  |

| 6.10 | Bidirectional Signals—A[6:0], D[31:0], DP[3:0],                                             |      |

|      | DS/-DLE/, AS/-TS/-ADS/, R_W/, BE0, BE1/, SIZ[1:0],                                          |      |

|      | BHE/-BE2, SIZ1-BE3, BERR/-TEA/, HALT/-TIP/,<br>BGACK-BB/, CBACK/-TBI/, STERM/-TA/-READYI/,  |      |

|      | GPIO[4:0]                                                                                   | 6-5  |

| 6.11 | Capacitance                                                                                 | 6-5  |

| 6.12 | TolerANT Active Negation Technology Electrical                                              | 00   |

|      | Characteristics                                                                             | 6-7  |

| 6.13 | Clock Timing                                                                                | 6-10 |

| 6.14 | Reset Input Timing                                                                          | 6-11 |

| 6.15 | Interrupt Output Timing                                                                     | 6-11 |

| 6.16 | Bus Mode 1 Slave Read Timing                                                                | 6-14 |

| 6.17 | Bus Mode 1 Slave Write Timing                                                               | 6-17 |

| 6.18 | Bus Mode 1 Host Bus Arbitration Timing                                                      | 6-20 |

| 6.19 | Bus Mode 1 Fast Arbitration Timing                                                          | 6-23 |

| 6.20 | Bus Mode 1 Master Read Timing                                                               | 6-27 |

| 6.21 | Bus Mode 1 Master Write Timing                                                              | 6-31 |

| 6.22 | Bus Mode 2 Slave Read Timing                                                                | 6-34 |

| 6.23 | Bus Mode 2 Slave Write Timing                                                               | 6-37 |

| 6.24 | Bus Mode 2 Host Bus Arbitration Timing                 | 6-40 |

|------|--------------------------------------------------------|------|

| 6.25 | Bus Mode 2 Fast Arbitration Timing                     | 6-42 |

| 6.26 | Bus Mode 2 Bus Master Read Timing                      | 6-46 |

| 6.27 | Bus Mode 2 Bus Master Write Timing                     | 6-49 |

| 6.28 | Bus Mode 2 Mux Mode Read Timing                        | 6-53 |

| 6.29 | Bus Mode 2 Mux Mode Write Timing                       | 6-57 |

| 6.30 | Bus Mode 3 and 4 Slave Read Timing                     | 6-60 |

| 6.31 | Bus Mode 3 and 4 Slave Write Timing                    | 6-63 |

| 6.32 | Bus Mode 3 and 4 Bus Arbitration Timing                | 6-66 |

| 6.33 | Bus Mode 3 and 4 Fast Arbitration                      | 6-69 |

| 6.34 | Bus Mode 3 and 4 Bus Master Read Timing                | 6-73 |

| 6.35 | Bus Mode 4 Bus Master Read Timing                      |      |

|      | (Cache Line Burst)                                     | 6-75 |

| 6.36 | Bus Mode 3 and 4 Bus Master Write Timing               | 6-79 |

| 6.37 | Bus Mode 4 Bus Master Write Timing                     |      |

|      | (Cache Line Burst)                                     | 6-81 |

| 6.38 | Initiator Asynchronous Send Timing                     | 6-82 |

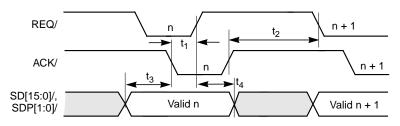

| 6.39 | Initiator Asynchronous Receive Timing                  | 6-83 |

| 6.40 | Target Asynchronous Send Timing                        | 6-83 |

| 6.41 | Target Asynchronous Receive Timing                     | 6-84 |

| 6.42 | SCSI-1 Transfers (SE 5.0 Mbytes/s)                     | 6-84 |

| 6.43 | SCSI-1 Transfers (Differential, 4.17 Mbytes/s)         | 6-85 |

| 6.44 | SCSI-2 Fast Transfers (10.0 Mbytes/s, 40 MHz Clock)    | 6-85 |

| 6.45 | SCSI-2 Fast Transfers (10.0 Mbytes/s, 50 MHz Clock)    | 6-86 |

| 6.46 | Ultra SCSI SE Transfers (20.0 Mbytes/s                 |      |

|      | (8-Bit Transfers) or 40.0 Mbytes/s (16-Bit Transfers), |      |

|      | 80 or 100 MHz Clock)                                   | 6-87 |

| 6.47 | Ultra SCSI Differential Transfers (20.0 Mbytes/s       |      |

|      | (8-Bit Transfers) or 40.0 Mbytes/s (16-Bit Transfers), |      |

|      | 80 or 100 MHz Clock)                                   | 6-88 |

| A.1  | LSI53C770 Register Summary                             | A-1  |

|      |                                                        |      |

# Chapter 1 General Description

This chapter contains the following sections:

- Section 1.1, "Benefits of Ultra SCSI"

- Section 1.2, "LSI53C770 Features Summary"

- Section 1.3, "Summary of New Features in the LSI53C770"

The LSI53C770 Ultra SCSI I/O Processor is a member of the LSI53C7XX family of intelligent, single chip, third generation SCSI host adapters. A high-performance SCSI core and an intelligent 16- or 32-bit bus master DMA core are integrated with a SCSI SCRIPTS<sup>™</sup> processor to accommodate the flexibility requirements of not only SCSI-1, SCSI-2, and future SCSI standards. The LSI53C770 solves the protocol overhead problems that have plagued all previous intelligent and nonintelligent adapter designs.

The LSI53C770 is designed to completely implement a multithreaded I/O algorithm in either a workstation or file server environment, completely free of processor intervention except at the end of an I/O transfer. In addition, the LSI53C770 provides automatic relocation of SCRIPTS, and requires no dynamic alteration of SCRIPTS instructions at the start of an I/O operation. All of the SCRIPTS code may be placed on a PROM. The LSI53C770 allows easy firmware upgrades and is SCRIPTS compatible with the LSI53C710 and the LSI53C8XX family.

The LSI53C770 supports four different host processor interfaces, or bus modes. Bus Mode 1 closely resembles the Motorola 68030 interface, and Bus Mode 2 closely resembles the Motorola 68040 interface. Bus Mode 3 closely resembles the Intel 80386SX interface; the 16-bit host interface should be enabled in this mode. Finally, Bus Mode 4 closely resembles the 80386DX interface. Bus Modes 1, 2, and 4 support both the big and

little endian byte ordering schemes and Bus Mode 3 supports little endian byte ordering, for a total of seven operating modes. Select the modes by using the bus mode select pins (BS[2:0]).

The LSI53C770 is a pin-for-pin replacement of the LSI53C720. It performs Ultra SCSI data transfers at 20 Mbytes/s (8-bit) or 40 Mbytes/s (16-bit). It is packaged in a 208-pin quad flat pack, and performs both Single-Ended (SE) and differential transfers.

# 1.1 Benefits of Ultra SCSI

Ultra SCSI is an extension of the SCSI-3 standard that expands the bandwidth of the SCSI bus and allows faster synchronous SCSI transfer rates. When enabled, Ultra SCSI performs 20 megatransfers during an I/O operation, resulting in approximately twice the synchronous transfer rates of fast SCSI-2. The LSI53C770 can perform 8-bit, Ultra SCSI synchronous transfers as fast as 20 Mbytes/s. This advantage is most noticeable in heavily loaded systems or large block size requirements, such as video on-demand and image processing.

An advantage of Ultra SCSI is that it significantly improves SCSI bandwidth while preserving existing hardware and software investments. The LSI53C770 is compatible with all existing LSI53C720 and LSI53C720SE software; the only changes required are to enable the chip to perform synchronous negotiations for Ultra SCSI rates. The LSI53C770 can use the same board socket as an LSI53C720, with the addition of an 80/100 MHz SCLK or internal SCSI clock doubler (clock doubler works at 40 to 50 MHz input) which provides the correct frequency when transferring synchronous SCSI data at 50 ns transfer rates. Some changes to existing cabling or system designs may be needed to maintain signal integrity at Ultra SCSI synchronous transfer rates. These design issues are discussed in Chapter 2.

# 1.1.1 TolerANT<sup>®</sup> Technology

The LSI53C770 features TolerANT technology, which includes active negation on the SCSI drivers and input signal filtering on the SCSI receivers. Active negation actively drives SCSI REQ, ACK, Data, and Parity signals HIGH by transistors on each pin. The 48 mA drivers actively force the SCSI bus signal to the HIGH (negated) state faster than

passive pull-up drivers. TolerANT receivers filter SCSI bus signals to eliminate unwanted transitions, without the long signal delay associated with RC-type input filters. This improved driver and receiver technology helps eliminate the double clocking of data, the single biggest reliability issue with SCSI operations. TolerANT technology improves data integrity in unreliable cabling environments where other devices would be subject to data corruption. The benefits of TolerANT technology include increased immunity to noise when the signal is going HIGH, increased performance due to balanced duty cycles, and improved Fast SCSI transfer rates. Setting bit 7 in the SCSI Test Register Three (STEST3) register enables active negation. It can be used in both SE and differential mode. TolerANT technology is compatible with both the Alternative One and Alternative Two termination schemes proposed by the American National Standards Institute.

# 1.2 LSI53C770 Features Summary

This section provides an overview of the LSI53C770 features and benefits. It contains information on Performance, Integration, Ease of Use, Flexibility, Reliability, and Testability.

### 1.2.1 Performance

To improve performance, the LSI53C770:

- Performs Ultra SCSI synchronous transfers as fast as 40 Mbytes/s (with wide SCSI)

- Includes 4 Kbytes internal RAM for SCRIPTS instruction storage

- Supports variable block size and scatter/gather data transfers

- Supports 16- and 32-bit data bursts with variable burst lengths

- Performs memory-to-memory DMA transfers in excess of 44 Mbytes/s

- Minimizes SCSI I/O start latency

- Performs complex bus sequences without interrupts, including restore data pointers

- Reduces ISR overhead with unique interrupt status reporting

- Performs memory transfers in excess of 100 Mbytes/s (@ 33 MHz)

- Uses a 96-byte DMA FIFO to support cache line bursting

- Uses up to 16 levels of synchronous SCSI offset for optimum speed matching during Ultra SCSI transfers

- Provides an additional 32 scratch registers

## 1.2.2 Integration

Features of the LSI53C770 which ease integration include:

- Full 16- or 32-bit DMA bus master

- High-performance wide SCSI core

- RISC-based SCSI SCRIPTS processor

- Allows intelligent host adapter performance on a mainboard

### 1.2.3 Ease of Use

The LSI53C770:

- Reduces SCSI development effort

- Supports big and little endian environments

- Uses existing LSI53C720 SCRIPTS

- Includes development tools and sample SCSI SCRIPTS

- Supports maskable and pollable interrupts

- Supports wide SCSI, A or P cable, and up to 16 devices

- Interfaces with seven different host processor buses, including Motorola (680X0 family) and Intel (80X86 family)

- Supports odd byte block sizes in conjunction with wide SCSI

- Provides three programmable SCSI timers: Select/Reselect, Handshake-to-Handshake, and General Purpose. The time-out period is programmable from 100 μs to greater than 1.6 seconds.

- The handshake-to-handshake and general purpose timers use a scale factor to increase the amount of time before expiration.

- The handshake-to-handshake timer has an optional mode that allows it to operate as a bus activity timer for all SCSI transfers.

## 1.2.4 Flexibility

The LSI53C770 provides:

- A high level programming interface (SCSI SCRIPTS)

- Tailored SCSI sequences to be executed from main memory or from a host adapter board's local memory

- Use of flexible sequences to tune I/O performance or to adapt to unique SCSI devices

- Changes in the logical I/O interface definition

- Low level programmability (register oriented)

- A target to disconnect and later reselect with no interrupt to the system processor

- A multithreaded I/O algorithm to be executed in SCSI SCRIPTS with fast I/O context switching

- Relative jumps

- Indirect fetching of DMA address and byte counts so that SCRIPTS can be placed in a PROM

- Separate SCSI and system clocks

- Double the SCSI clock input during Ultra SCSI transfer modes

- A new SSAID (SCSI Selected as ID) register

#### 1.2.5 Reliability

Enhanced reliability features of the LSI53C770 include:

- TolerANT SCSI driver and receiver technology

- 2 kV ESD protection on SCSI signals

- Typical 350 mV SCSI bus hysteresis

- Protection against bus reflections due to impedance mismatches

- Controlled bus assertion times (reduces RFI, improves reliability, and eases FCC certification)

- Latch-up protection greater than 150 mA

- Voltage feed-through protection (minimum leakage current through SCSI pads)

- 20% of pins power and ground

- Ground isolation of I/O pads and chip logic

## 1.2.6 Testability

The LSI53C770 provides improved testability through:

- Access to all SCSI signals through programmed I/O

- SCSI loopback diagnostics

- Self-selection capability

- SCSI bus signal continuity checking

- Support for single step mode operation

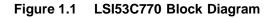

Figure 1.1 illustrates the LSI53C770 Block Diagram.

# 1.3 Summary of New Features in the LSI53C770

For more information on enabling or using these new features, please refer to the chapter indicated with each topic.

- Support for Ultra SCSI data transfers (Chapter 2, Chapter 4, and Chapter 6)

- DMA FIFO increased to 96 bytes (Chapter 2)

- SCSI offset increased to 16 levels (Chapter 4, SCSI Transfer (SXFER) register description)

- Internal SCRIPTS RAM (Chapter 2, Chapter 4)

- Expanded timers (Chapter 4, SCSI Timer Register 0 (STIME0) and SCSI Timer Register One (STIME1) register descriptions)

- Expanded SCSI Longitudinal Parity (SLPAR) register (Chapter 4, SCSI Longitudinal Parity (SLPAR) register description)

- Additional Read-Modify-Write Instructions (Chapter 5, Read/Write instructions)

- SCSI Clock Doubler (Chapter 2, Chapter 4)

- SCSI Selector ID Register (SSID) register (Chapter 4)

- Fairness timer update (Chapter 4, DMA Mode (DMODE) register description)

- Additional 32 Scratch registers (Chapter 4)

- Vendor unique enhancements (Chapter 4, SCSI Control Register Two (SCNTL2) register description)

- DIFFSENSE Sense bit to detect a differential System (Chapter 5, SCSI Status Two (SSTAT2) register description)

# Chapter 2 Functional Description

The LSI53C770 is composed of three interrelated functional blocks: the SCSI Core, the DMA Core, and the SCRIPTS Processor.

This chapter contains the following sections:

- Section 2.1, "SCSI Core"

- Section 2.2, "SCRIPTS Processor"

- Section 2.3, "DMA FIFO"

- Section 2.4, "Host Interface"

- Section 2.5, "Bidirectional STERM/-TA/-ReadyIn/"

- Section 2.6, "SCSI Bus Interface"

- Section 2.7, "Interrupt Handling"

This chapter describes the major functional aspects of the chip. For detailed information on implementing or using specific features, refer to later chapters in this manual. Chapter 3 contains detailed information on the LSI53C770 pins. Chapter 4 describes all of the operating registers and bits. Chapter 5 describes the LSI53C770 instruction set, and Chapter 6 contains the chip electrical specifications and timing data.

# 2.1 SCSI Core

The SCSI core supports the SCSI-2 fast and wide bus. It supports synchronous transfer rates of up to 20 Mbytes/s or 40 Mbytes/s in Ultra SCSI, and asynchronous transfer rates up to 10 Mbytes/s. The programmable SCSI interface makes it easy to "fine tune" the system for specific mass storage devices or advanced SCSI requirements.

The SCSI core offers low level register access or a high level control interface. Like first generation SCSI devices, the LSI53C770 SCSI core can be accessed as a register oriented device. The ability to sample and/or assert any signal on the SCSI bus can be used in error recovery and diagnostic procedures. In support of loopback diagnostics, the SCSI core may perform a self-selection and operate as both an initiator and a target. This can test all data paths in the chip. The LSI53C770 uses an "AND tree" to test the SCSI pins for physical connection to the board or the SCSI bus.

Unlike previous generation devices, the SCSI core can be controlled by the SCRIPTS processor, a high level logical interface optimized for SCSI protocol. SCRIPTS routines controlling the SCSI core are fetched out of the main host memory or local PROM. These commands instruct the SCSI core to select, reselect, disconnect, wait for a disconnect, transfer information, change bus phases and in general, implement all aspects of the SCSI protocol.

#### 2.1.1 DMA Core

The DMA core is a bus master DMA device that is made to attach to Intel (80386SX and 80386DX), and Motorola (68030 and 68040) processors.

The LSI53C770 supports 16- or 32-bit memory and automatically supports misaligned DMA transfers. A 96-byte FIFO allows the LSI53C770 to burst two, four, eight, or 16 Dwords across the memory bus interface. This DMA interface does not support dynamic bus sizing.

The DMA core communicates with the SCSI core through the SCRIPTS processor, which supports uninterrupted scatter/gather memory operations.

# 2.2 SCRIPTS Processor

The SCSI SCRIPTS processor allows both DMA and SCSI commands to be fetched from host memory or internal SCRIPTS RAM. Algorithms written in SCSI SCRIPTS control the actions of the SCSI and DMA cores, which are executed from 16- or 32-bit system memory. The SCRIPTS processor executes complex SCSI bus sequences independently of the host CPU. The SCRIPTS processor can begin a SCSI I/O operation in approximately 500 ns. This compares with 2–8 ms required for traditional intelligent host adapters. The SCRIPTS processor supports customized algorithms to tune SCSI bus performance, adjust to new bus device types (i.e. scanners, communication gateways, etc.), or incorporate changes in the SCSI logical bus definitions without sacrificing I/O performance. SCSI SCRIPTS are hardware independent, so they can be used interchangeably on any host or CPU system bus.

### 2.2.1 Internal SCRIPTS RAM

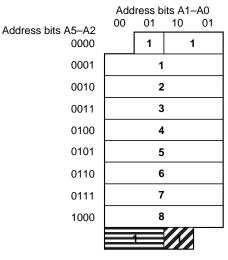

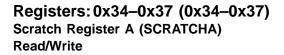

The LSI53C770 has 4 Kbytes (1000 x 32 bits) of internal, general purpose RAM. The RAM is designed for SCRIPTS program storage, but is not limited to this type of information. When the chip fetches SCRIPTS instructions or Table Indirect information from the internal RAM, these fetches remain internal to the chip and do not use the host bus. Other types of access to the RAM by the LSI53C770 use the host bus as if they were external accesses. When the internal RAM is enabled, the LSI53C770 uses the shadowed Scratch Register A (SCRATCHA) register as the base address of the RAM when bit 0 is set in the Chip Test Five (CTEST5) register.

The internal RAM can be enabled and used in the following ways:

- Register based through indexed addressing.

- Increased chip select address space that includes support for the chip registers and internal RAM with a single chip select pin.

- An additional chip select pin supporting only internal RAM with the original Chip Select pin supporting only the chip registers.

The register based method allows use of the SCRIPTS RAM in existing LSI53C720 designs without hardware changes. To use this method, clear Chip Test Five (CTEST5), bit 2 and set Chip Test Five (CTEST5), bit 1. The internal RAM is mapped into the chip registers using indexed addressing in a shadowed Scratch Register B (SCRATCHB) register. The RAM replaces the Scratch Registers C–J (SCRATCHC–J) registers, and may optionally be used as a block of scratchpad RAM. When the chip determines that a SCRIPTS address is in the internal RAM space, the opcode fetch sequence accesses the internal RAM without using the host bus. Indirect and table indirect functions also determine if the address is contained in internal RAM space and fetch data from the RAM

without host bus access. Read-Modify-Write operations or Memory Move instructions can be used to modify the RAM while SCRIPTS are running, but the host cannot access the RAM during SCRIPTS operation.

The increased chip select address space method defines 4 Kbyte address space for the chip registers and the 4 Kbyte space for the SCRIPTS RAM. To enable this mode, set Chip Test Five (CTEST5), bit 2 and clear Chip Test Five (CTEST5), bit 1. The registers are located at addresses 0x0000 through 0x007F, repeating at intervals of 128 bytes until the 4 K byte boundary. The RAM occupies addresses 0x1000 through 0x1FFF. The RAM is accessible by the host during SCRIPTS execution, but up to seven additional wait-states may be added to a slave read or write access if it occurs while an internal SCRIPTS access is in progress. Read-Modify-Write operations or Memory Move instructions can be used to modify the RAM while SCRIPTS are running.

An additional chip select pin, the RAMCS/ pin, can be used to define a 4 Kbyte address space for the internal RAM by setting bits 1 and 2 of the Chip Test Five (CTEST5) register. The RAM is accessible by the host during SCRIPTS execution, but up to seven additional wait-states may be added to a slave read or write access if it occurs while an internal SCRIPTS access is in progress. Read-Modify-Write operations or Memory Move instructions can be used to modify the RAM while SCRIPTS are running.

### 2.2.2 Designing an Ultra SCSI System

Migrating an existing SE SCSI design from SCSI-2 to Ultra SCSI requires minor software modifications as well as consideration for some hardware design guidelines. Since Ultra SCSI is based on existing SCSI standards, it can use existing software programs as long as the software is able to negotiate for Ultra SCSI synchronous transfer rates.

In the area of hardware, the primary area of concern in SE systems is to maintain signal integrity at high data transfer rates. To assure reliable operation at Ultra SCSI transfer speeds, follow the system design parameters recommended in the SCSI-3 Fast-20 Parallel Interface draft standard. Chapter 6 contains Ultra SCSI timing information. In addition to the guidelines in the draft standard, make the following software and hardware adjustments to accommodate Ultra SCSI transfers:

- Set the Ultra Enable bit to enable Ultra SCSI transfers. (SCSI Control Three (SCNTL3), bit 7).

- Set the TolerANT Enable bit, bit 7 in the SCSI Test Register Three (STEST3) register whenever the Ultra SCSI Enable bit is set.

- Do not extend the SREQ/SACK filtering period with SCSI Test Register Two (STEST2), bit 1.

- Use an 80/100 MHz SCSI clock or enable the SCSI clock doubler (clock doubler works at 40 to 50 MHz input) using bits 2 and 3 of the SCSI Test Register One (STEST1) register. Set the halt SCSI clock (HSC) bit in SCSI Test Register Three (STEST3) before switching to the doubled SCSI clock.

## 2.2.3 Using the SCSI Clock Doubler

The LSI53C770 can double the frequency of a 40–50 MHz SCSI clock, allowing the system to perform Ultra SCSI transfers in systems that do not have 80 MHz clock input. This option is user-selectable with bit settings in the SCSI Test Register One (STEST1), SCSI Test Register Three (STEST3), and SCSI Control Three (SCNTL3) registers. At power-on or reset, the doubler is disabled and powered down. Follow these steps to use the clock doubler:

- Set the SCLK Doubler Enable bit (SCSI Test Register One (STEST1), bit 3).

- 2. Wait 20 µs.

- 3. Halt the SCSI clock by setting the Halt SCSI Clock bit (SCSI Test Register Three (STEST3), bit 5).

- 4. Set the clock conversion factor using the SCF and CCF fields in the SCSI Control Three (SCNTL3) register.

- 5. Set the SCLK Doubler Select bit (SCSI Test Register One (STEST1), bit 2).

- 6. Clear the Halt SCSI Clock bit.

## 2.2.4 Big/Little Endian Support

The Bus Mode Select pin gives the LSI53C770 the flexibility of operating with either big or little endian byte orientation. Internally, in either mode, the byte lanes of the DMA FIFO and registers are not modified. The LSI53C770 supports byte, word, and Dword slave accesses in both big and little endian modes (word accesses must be word aligned).

When a Dword is accessed, no repositioning of the individual bytes is necessary, since Dwords are addressed by the address of the least significant byte. SCRIPTS always uses Dwords in 32-bit systems, so compatibility is maintained between systems using different byte orientations. When a word is accessed, individual bytes must be repositioned. Internally, the LSI53C770 adjusts the byte control logic of the DMA FIFO and register decodes to access the appropriate byte lanes. The registers always appear on the same byte lane, but the address of the register are repositioned. Words are addressed by the address of the least significant byte. Big/little endian mode selection has the most effect on individual byte access, as illustrated in Table 2.1.

| System Data Bus       | [31:24] | [23:16] | [15:8] | [7:0]  |

|-----------------------|---------|---------|--------|--------|

| LSI53C770 Pins        | [31:24] | [23:16] | [15:8] | [7:0]  |

| Register              | SCNTL3  | SCNTL2  | SCNTL1 | SCNTL0 |

| Little Endian Address | 0x03    | 0x02    | 0x01   | 0x00   |

| Big Endian Address    | 0x00    | 0x01    | 0x02   | 0x03   |

Table 2.1

Big and Little Endian Addressing

<u>Note:</u> The LSI53C770 supports big endian addressing in 16-bit systems with Bus Modes 1 and 2 only.

Data to be transferred between system memory and the SCSI bus always start at address zero and continue through address 'n' - there is no byte ordering in the chip. The first byte in from the SCSI bus goes to address 0, the second to address 1, etc. Going out onto the SCSI bus, address zero is the first byte out on the SCSI bus, address 1 is the second byte, etc. Correct SCRIPTS are generated if the SCRIPTS compiler is run on a system that has the same byte ordering as the target system. Any SCRIPTS patching in memory must patch the instruction in the order that the SCRIPTS processor expects it.

Software drivers for the LSI53C770 should access registers by their logical name (i.e., "SCNTL0") rather than by their address. The logical name should be equated to the register's big endian address in big endian mode (SCNTL0 = 0x03), and its little endian address in little endian mode (SCNTL0 = 0x00). This way, there is no change to the software when moving from one mode to the other; only the equate statement setting the operating modes needs to be changed. Addressing of registers from within a SCRIPTS instruction is independent of bus mode. Internally, the LSI53C770 always operates in little endian mode.

### 2.2.5 Big Endian Mode

Big endian addressing is used primarily in designs based on Motorola processors. The LSI53C770 treats D[31:24] as the lowest physical memory address. The register map is left justified (Address 0x03 = SCNTL0).

### 2.2.6 Little Endian Mode

Little endian is used primarily in designs based on Intel processors. This mode treats D[7:0] as the lowest physical memory address. The register map is right justified (Address 0x00 = SCNTL0) as detailed in Table 2.1.

### 2.2.7 Loopback Mode

The LSI53C770 loopback mode allows testing of both initiator and target functions and, in effect, lets the chip talk to itself. This allows diagnostic testing of the DMA and SCSI cores, the SCRIPTS processor, and all internal data paths. When the Loopback Enable bit is set in the SCSI Test Register Two (STEST2) register, the LSI53C770 allows control of all SCSI signals, whether it is operating in initiator or target mode.

## 2.2.8 Parity Options

The LSI53C770 implements a flexible parity scheme that allows control of the parity sense, allows parity checking to be turned on or off, and has the ability to deliberately send a byte with bad parity over the SCSI bus to test parity error recovery procedures. The following bits are involved in parity control and observation:

| Bit Name                                                                                                    | Location                            | Description                                                                                                                                                       |  |

|-------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Assert ATN/ on<br>Parity Errors SCSI Control Zero<br>(SCNTL0), bit 1                                        |                                     | Causes the LSI53C770 to automatically assert SCSI ATN/<br>when it detects a parity error (on either the SCSI or the data<br>bus) while operating as an initiator. |  |

| Enable Parity<br>Generation SCSI Control Zero<br>(SCNTL0), bit 2                                            |                                     | Determines whether the LSI53C770 generates parity sent to<br>the SCSI bus or allows parity to "flow through" the chip<br>to/from the SCSI bus and system bus.     |  |

| Enable Parity<br>Checking SCSI Control Zero<br>(SCNTL0), bit 3                                              |                                     | Enables the LSI53C770 to check for parity errors. The LSI53C770 checks for odd parity.                                                                            |  |

| Assert Even<br>SCSI Parity                                                                                  | SCSI Control One<br>(SCNTL1), bit 2 | Determines the SCSI parity sense generated by the LSI53C770 being sent to the host. Parity generation must be enabled.                                            |  |

| Disable Halt on<br>ATN/ or a Parity<br>Error (Target<br>Mode Only)<br>SCSI Control One<br>(SCNTL1), bit 5   |                                     | Causes the LSI53C770 to halt operations when a parity error is detected in target mode.                                                                           |  |

| Enable Parity<br>Error Interrupt SCSI Interrupt<br>Enable Zero<br>(SIEN0), bit 0                            |                                     | Determines whether the LSI53C770 will generate an interrupt when it detects a parity error.                                                                       |  |

| Parity Error SCSI Interrupt<br>Status Zero<br>(SIST0), bit 0                                                |                                     | This status bit is set whenever the LSI53C770 has detected<br>a parity error on either the SCSI bus or the system bus.                                            |  |

| Status of SCSI<br>Parity SignalSCSI Status Zero<br>(SSTAT0), bit 0 an<br>SCSI Status Two<br>(SSTAT2), bit 0 |                                     | These status bits represent the live SCSI Parity Signal (SDP0 and SDP1).                                                                                          |  |

#### Table 2.2 Bits Used in Parity Control and Generation

| Bit Name                       | Location                                                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Latched SCSI<br>Parity Signal  | SCSI Status One<br>(SSTAT1), bit 3 and<br>SCSI Status Two<br>(SSTAT2), bit 3 | These status bits contain the SCSI parity of the bytes latched in the SCSI Input Data Latch (SIDL).                                                                                                                                                                                                                                                                                                                                                        |

| DMA FIFO Parity                | Chip Test Two<br>(CTEST2), bit 3                                             | This status bit represents the parity bit in the DMA FIFO after data is read from the FIFO by reading the Chip Test Six (CTEST6) register.                                                                                                                                                                                                                                                                                                                 |

| DMA FIFO Parity                | Chip Test Zero<br>(CTEST0), bit 3                                            | This write only bit is written to the DMA FIFO after writing data to the DMA FIFO by writing the Chip Test Six (CTEST6) register.                                                                                                                                                                                                                                                                                                                          |

| SCSI FIFO Parity               | SCSI Test<br>Register One<br>(STEST1), bit 0                                 | This status bit represents the parity bit in the SCSI FIFO<br>after data is read from the FIFO by reading the SCSI Output<br>Data Latch (SODL) register, once bit 0 in SCSI Test Register<br>Three (STEST3) is asserted.                                                                                                                                                                                                                                   |

| Generate<br>Receive Parity     | Chip Test Zero<br>(CTEST0), bit 4                                            | When this bit is set and the LSI53C770 is in parity<br>pass-through mode (bit 2 in the SCSI Control Zero<br>(SCNTL0) register is clear), parity received on the SCSI bus<br>will not pass through the DMA FIFO. New parity will be<br>generated.<br>When this bit is cleared, and parity pass through mode is<br>enabled (Bit 2 of SCSI Control Zero (SCNTL0) is clear),<br>parity received on the SCSI bus will pass through the<br>LSI53C770 unmodified. |

| Enable Host<br>Parity Checking | Chip Test Four<br>(CTEST4), bit 3                                            | Setting this bit enables parity checking during slave write and DMA read execution, if the Enable Parity Generation bit is cleared (SCSI Control Zero (SCNTL0), bit 2).                                                                                                                                                                                                                                                                                    |

## Table 2.2 Bits Used in Parity Control and Generation (Cont.)

Table 2.3 **SCSI Parity Control**

| EPG <sup>1</sup> | EPC <sup>2</sup> | AESP <sup>3</sup> | Description                                                                                                                                                                                                                                                                      |

|------------------|------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                | 0                | 0                 | Does not check for parity errors. Parity flows from DP[3:0] through the chip to the SCSI bus when sending SCSI data. Parity flows from the SCSI bus to DP[3:0] when receiving SCSI data. Asserts odd parity when sending SCSI data.                                              |

| 0                | 0                | 1                 | Does not check for parity errors. Parity flows from DP[3:0] through the chip to the SCSI bus when sending SCSI data. Parity flows from the SCSI bus to DP[3:0] when receiving SCSI data. Asserts even parity when sending SCSI data.                                             |

| 0                | 1                | 0                 | Checks for odd parity on both host and SCSI data when received. Parity flows from DP[3:0] through the chip to the SCSI bus when sending SCSI data. Parity flows from the SCSI bus to DP[3:0] when receiving SCSI data. Asserts odd parity when sending SCSI data.                |

| 0                | 1                | 1                 | Checks for odd parity on both host and SCSI data when received. Parity flows from DP[3:0] through the chip to the SCSI bus when sending SCSI data. Parity flows from the SCSI bus to DP[3:0] when receiving SCSI data. Asserts even parity when sending SCSI data.               |

| 1                | 0                | 0                 | Does not check for parity errors. Parity on DP[3:0] is ignored. Parity is generated when sending SCSI data. Parity flows from the SCSI bus to the chip, but is not asserted on DP[3:0] when receiving SCSI data. Asserts odd parity when sending SCSI data.                      |

| 1                | 0                | 1                 | Does not check for parity errors. Parity on DP[3:0] is ignored. Parity is generated when sending SCSI data. Parity flows from the SCSI bus to the chip, but is not asserted on DP[3:0] when receiving SCSI data. Asserts even parity when sending SCSI data.                     |

| 1                | 1                | 0                 | Checks for odd parity on SCSI data received. Parity on DP[3:0] is ignored.<br>Parity is generated when sending SCSI data. Parity flows from the SCSI bus<br>to the chip, but is not asserted on DP[3:0] when receiving SCSI data.<br>Asserts odd parity when sending SCSI data.  |

| 1                | 1                | 1                 | Checks for odd parity on SCSI data received. Parity on DP[3:0] is ignored.<br>Parity is generated when sending SCSI data. Parity flows from the SCSI bus<br>to the chip, but is not asserted on DP[3:0] when receiving SCSI data.<br>Asserts even parity when sending SCSI data. |

Enable Parity Generation.

Enable Parity Checking.

Assert SCSI Even Parity.

Table 2.4 describes the options available when a parity error occurs.Table 2.4 only applies when the Enable Parity Checking bit is set.

| DHP | PAR | Description                                                                                                |

|-----|-----|------------------------------------------------------------------------------------------------------------|

| 0   | 0   | Does not halt when a parity error occurs in target or initiator mode.                                      |

| 0   | 1   | Does not halt when a parity error occurs in target or initiator mode. <sup>1</sup>                         |

| 1   | 0   | Does not halt when a parity error occurs in target or initiator mode.                                      |

| 1   | 1   | Halts when a parity error occurs in target mode and will generate an interrupt in target or initiator mode |

Table 2.4

Parity Errors and Interrupts

1. Initiator mode parity error interrupts are generated at the end of a block move.

# 2.3 DMA FIFO

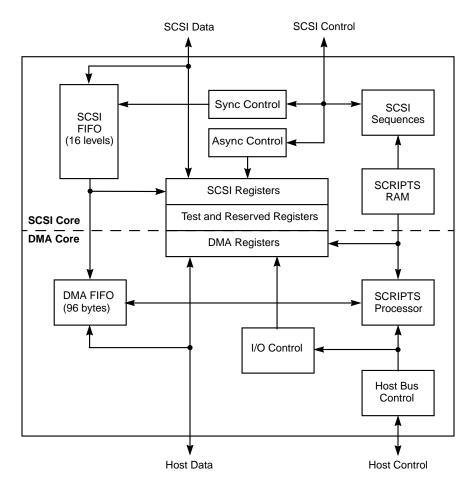

The LSI53C770 DMA FIFO is a 36 x 24 bit FIFO. It is divided into 4 byte lanes, each 9 bits wide and 24 transfers deep, as shown in Figure 2.1.

Figure 2.1 DMA FIFO Byte Lanes

## 2.3.1 Data Path

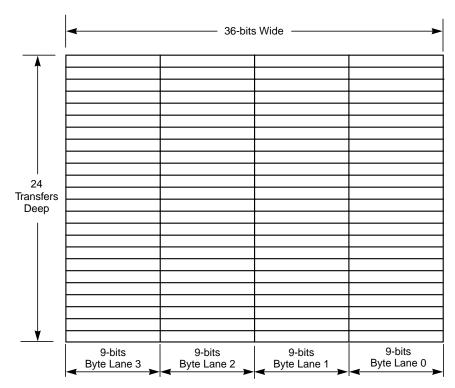

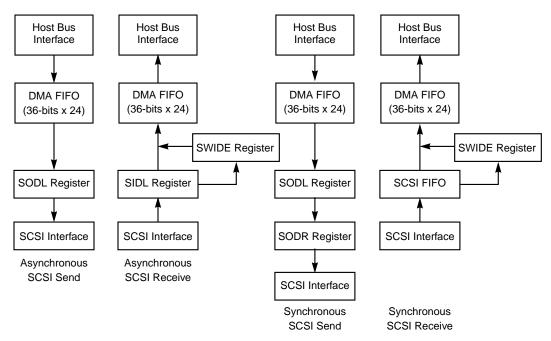

When the LSI53C770 halts a data transfer operation, check the data path to determine if any bytes remain that have not been transferred. The data path through the LSI53C770 is dependent on whether data is being moved into or out of the chip, and whether SCSI data is being transferred asynchronously or synchronously. Figure 2.2 shows how data is moved to/from the SCSI bus in each of the different modes.

## 2.3.2 DMA FIFO

In all types of transfers, the DMA FIFO is used in the data path. The DFE bit in the DMA Status (DSTAT) register indicates whether there is any data in the DMA FIFO. To check the DMA FIFO, use the following procedure. The other parts of the data path may contain data. To check the data path, follow the steps indicated for each type of transfer.

#### 2.3.2.1 Checking the Data Path

When transferring data from the host bus to the SCSI bus, subtract the seven least significant bits of the DMA Byte Counter (DBC) register from the 7-bit value of the DMA FIFO (DFIFO) register. AND the result with 0x7F for the byte count between zero and 96.

When transferring data from the SCSI bus to the host bus, subtract the seven least significant bits of the DMA Byte Counter (DBC) register from the 7-bit value of the DMA FIFO (DFIFO) register. AND the result with 0x7F and take the 2's complement to obtain the byte count between zero and 96.

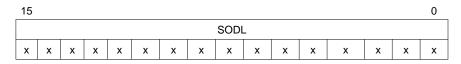

# 2.3.3 Asynchronous SCSI Send –

Read the SCSI Status Zero (SSTAT0) and SCSI Status Two (SSTAT2) registers to determine if any bytes are left in the SCSI Output Data Latch (SODL) register. If bit 5 is set in the SCSI Status Zero (SSTAT0) or SCSI Status Two (SSTAT2), then the least significant byte or the most significant byte in the SCSI Output Data Latch (SODL) register is full, respectively. Checking this bit also reveals bytes left in the SCSI Output Data Latch (SODL) register from a Chained Move operation with an odd byte count.

## 2.3.4 Synchronous SCSI Send –

- Read bit 5 in the SCSI Status Zero (SSTAT0) and SCSI Status Two (SSTAT2) registers to determine if any bytes are left in the SCSI Output Data Latch (SODL) register. If bit 5 is set in the SCSI Status Zero (SSTAT0) or SCSI Status Two (SSTAT2), then the least significant byte or the most significant byte in the SCSI Output Data Latch (SODL) register is full, respectively. Checking this bit also reveals bytes left in the SCSI Output Data Latch (SODL) register from a Chained Move operation with an odd byte count.

- Read bit 6 in the SCSI Status Zero (SSTAT0) and SCSI Status Two (SSTAT2) registers to determine if any bytes are left in the SODR register. If bit 6 is set in the SCSI Status Zero (SSTAT0) or SCSI Status Two (SSTAT2), then the least significant byte or the most significant byte in the SODR register is full, respectively.

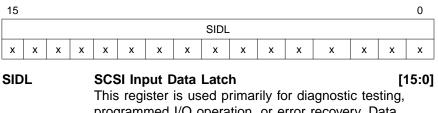

## 2.3.5 Asynchronous SCSI Receive -

- Read bit 7 in the SCSI Status Zero (SSTAT0) and SCSI Status Two (SSTAT2) register to determine if any bytes are left in the SCSI Input Data Latch (SIDL) register. If bit 7 is set in the SCSI Status Zero (SSTAT0) or SCSI Status Two (SSTAT2), then the least significant byte or the most significant byte is full, respectively.

- If any wide transfers have been performed using the Chained Move instruction, read the Wide SCSI Receive bit (SCSI Control Register Two (SCNTL2), bit 0) to determine whether a byte is left in the SCSI Wide Residue Data (SWIDE) register.

## 2.3.6 Synchronous SCSI Receive -

- Read the SCSI Status Zero (SSTAT0) and SCSI Status Two (SSTAT2) registers and examine bits [7:4], the binary representation of the number of valid bytes in the SCSI FIFO, to determine if any bytes are left in the SCSI FIFO.

- If any wide transfers have been performed using the Chained Move instruction, read the Wide SCSI Receive bit (SCSI Control Register Two (SCNTL2), bit 0) to determine whether a byte is left in the SCSI Wide Residue Data (SWIDE) register.

## 2.4 Host Interface

The LSI53C770 can be interfaced with both 680X0-type and 80X86-type host processors using big or little endian byte ordering, for a total of seven host bus interface modes. The modes are selected with the Bus Mode Select pins, defined in Chapter 3.

## 2.4.1 Misaligned Transfers

The LSI53C770 accommodates block data transfers beginning or ending on odd byte or odd word addresses in system memory. Such addresses are termed "misaligned." An odd byte is defined as one in which the address contains A0 = 1; an odd word is defined as one in which the address contains A1 = 1. Misaligned transfers differ depending on the type of transfer and whether they occur at the start or end of the transfer. The LSI53C770 does not perform 24-bit transfers.

## 2.4.2 Transfer Size Throttling

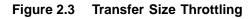

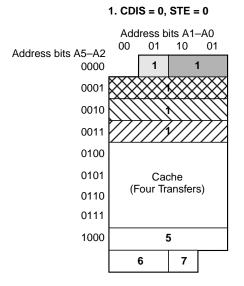

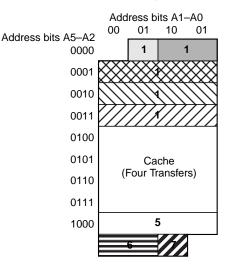

The burst control logic in the LSI53C770 includes an optional throttling technique which does not allow a size change to occur within a bus ownership. When size throttling is enabled, a new bus ownership occurs each time the transfer changes size. When size throttling is enabled, bit 0 (Snoop Pins Mode) of the Chip Test Three (CTEST3) register should be clear. Size throttling can be enabled or disabled using the Size Throttle Enable bit, bit 7 in the DMA Control (DCNTL) register. Cache line bursting is controlled with the Cache Burst Disable bit, bit 7 in the Chip Test Zero (CTEST0) register.

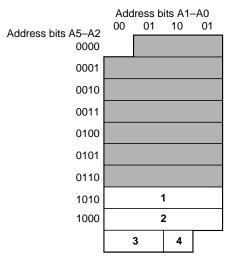

Figure 2.3 illustrates the function of the CDIS and STE bits. In Item 1, cache line bursting is enabled and size throttling is disabled. Since the starting address is at an odd byte boundary, the LSI53C770 lines up to a word boundary by performing a single byte transfer in a single bus ownership. Then, since the address is at an odd word boundary (bit A1 = 1), the LSI53C770 lines up to a Dword boundary by performing a single bus ownership. At this point, one Dword transfer is performed per bus ownership until the address bits line up to a cache line boundary A(3) = A(2) = A(1) = A(0) = 0. Once aligned, the cache line, Dword, word, and byte are transferred in a single bus ownership to complete the transfer.

In Item 2, cache line bursting and size throttling are enabled. The LSI53C770 lines up to a cache line boundary as described for Figure 2.3. Once aligned, the cache line and Dword are transferred in the same bus ownership since the two are considered the same size. The remaining word and byte are transferred in two separate bus ownerships to complete the transfer.

In Item 3, cache line bursting and size throttling are disabled. The LSI53C770 completes eight transfers in one bus ownership, since the burst length is set to eight. The remaining four transfers are transferred in one bus ownership to complete the transfer.

In Item 4, cache line bursting is disabled and size throttling is enabled. The LSI53C770 lines up to a Dword boundary. Since the address starts on an odd byte boundary, the LSI53C770 lines up to a word boundary by performing a single byte transfer in a single bus ownership. Then, since the address is at an odd word boundary, the LSI53C770 lines up to a Dword boundary by performing a single word transfer in a single bus ownership. Once aligned, Dwords are transferred in the same bus ownership. The remaining word and byte are transferred in separate bus ownerships to complete the transfer.

2. CDIS = 0, STE = 1

3. CDIS = 1, STE = 0

4. CDIS = 1, STE = 1

#### Note:

- 1. CDIS Cache Burst Disable bit; STE = Size Throttle Enable bit.

- 2. At the start of the diagram, 38 bytes remain to be transferred.

- 3. The programmable burst length is 8.

- 4. Each of the shaded areas represents a new bus ownership.

- 5. The numbers within the shaded areas represent the number of transfers performed in the bus ownership.

- 6. For each alignment and bursting to be attempted, the entire transfer must be at least 31 bytes, this is dictated by chip architecture.

## 2.4.3 BERR/\_TEA/ Pin Function

This section describes the function of the BERR/\_TEA/ pin on the LSI53C770 SCSI I/O Processor.

#### 2.4.4 Functionality of BERR/\_TEA/ in Master Mode

In Master Mode, BERR/\_TEA/ is used in conjunction with TA/ to indicate to the LSI53C770 that one of the following conditions has occurred:

| TEA/ | TA/ | Condition <sup>1</sup>                                           |  |

|------|-----|------------------------------------------------------------------|--|

| 1    | 1   | Execute a wait-state                                             |  |

| 1    | 0   | Normal cycle acknowledge                                         |  |

| 0    | 1   | Bus error condition has occurred                                 |  |

| 0    | 0   | Retry the current cycle after relinquishing the bus <sup>2</sup> |  |

1. In Bus Mode 1, the chip attempts a bus retry operation only if BERR/ asserts in conjunction with HALT/.

2. In Bus Mode 2, the chip attempts a bus retry operation if TEA/ asserts in conjunction with TA/.

## 2.4.5 Functionality of BERR/\_TEA/ in Slave Mode

In Slave Mode the LSI53C770 responds to requests from an external master in one of the following ways:

| TEA/ | SLACK/ | TA/ <sup>1</sup> | Condition                                      |  |

|------|--------|------------------|------------------------------------------------|--|

| 1    | 1      | 1                | Requests the bus master to insert a wait-state |  |

| 1    | 0      | 0                | Normal cycle acknowledge                       |  |

| 0    | 1      | 1                | Access exception has occurred                  |  |

| 0    | 0      | 0                | Reserved                                       |  |

1. TA/ does not assert during slave cycles unless the Enable Ack bit in the DMA Control (DCNTL) register is set.

Address exceptions are:

| Bus Mode 1:       | All of the cases mentioned above plus any 3 byte transfer.                                                                                                        |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bus Mode 2:       | <ul> <li>any misaligned 2-byte transfer (A0 = 1)</li> <li>any misaligned Dword (A1–A0 not equal to 00)</li> <li>any 2-byte transfer in big endian mode</li> </ul> |

| Bus Mode 3 and 4: | No bus exceptions will occur and the TEA/ pin will never<br>be asserted. One-, two-, three-, and four-byte operations<br>are allowed.                             |

#### 2.4.6 Bus Retry

Bus Retry allows the LSI53C770 to retry the previous cycle using the same address, size, and other information. Bus retry occurs when an external device asserts the appropriate bus signals, forcing the chip to release the host bus. It tries to regain control of the host bus immediately, without a fairness delay. Once the chip regains control of the host bus, it retries the previous cycle.

#### 2.4.7 Noncache Line Burst

In Bus Mode 1, an external device initiates a bus retry by asserting the HALT/ and BERR/ signals. In Bus Mode 2, the TA/ and TEA/ signals are used to initiate a bus retry. In Bus Modes 3 and 4, a bus retry is initiated by asserting the TEA/ and READYI/ signals. When an external device asserts these signals, the LSI53C770 asserts the Bus Request (BR/) signal (Bus Modes 1 and 2) or the HOLD/ signal (Bus Modes 3 and 4). This is done without a fairness delay to try to regain control of the host bus. This repeats indefinitely (as long as the signals remain asserted) until the cycle completes normally, or a bus error occurs. During a noncache line burst, a bus retry can be executed in any cycle.

#### 2.4.8 Cache Line Burst

During a cache line burst, the bus retry must be executed during the first cycle for the Bus Retry to execute properly in all bus modes.

In Bus Mode 1, if the LSI53C770 is attempting a cache line burst, it will retry the bus cycle and assert Cache Burst Request (CBREQ/) again. If a bus retry is attempted during one of the subsequent cycles of the

cache line burst, the LSI53C770 halts the transfer until the HALT/ signal is deasserted. If the Bus Error (BERR/) signal is still asserted at this time, the transfer will abort.

In Bus Mode 2, if the LSI53C770 is attempting a cache line burst, it will retry the bus cycle and asserts SIZ0 and SIZ1 again. If a bus retry is attempted during one of the subsequent cycles of the cache line burst, the transfer will abort. If the Transfer Error (TEA/) signal is still asserted at this time, the LSI53C770 will abort the transfer.